JP2004140344A - 半導体集積回路 - Google Patents

半導体集積回路 Download PDFInfo

- Publication number

- JP2004140344A JP2004140344A JP2003320862A JP2003320862A JP2004140344A JP 2004140344 A JP2004140344 A JP 2004140344A JP 2003320862 A JP2003320862 A JP 2003320862A JP 2003320862 A JP2003320862 A JP 2003320862A JP 2004140344 A JP2004140344 A JP 2004140344A

- Authority

- JP

- Japan

- Prior art keywords

- sense amplifier

- channel

- channel mos

- mos transistor

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 45

- 239000011159 matrix material Substances 0.000 claims abstract description 6

- 238000010586 diagram Methods 0.000 description 41

- 238000009792 diffusion process Methods 0.000 description 20

- 239000013256 coordination polymer Substances 0.000 description 6

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 4

- 229910052721 tungsten Inorganic materials 0.000 description 4

- 239000010937 tungsten Substances 0.000 description 4

- 230000004913 activation Effects 0.000 description 3

- 238000003491 array Methods 0.000 description 3

- 239000003990 capacitor Substances 0.000 description 3

- 230000000295 complement effect Effects 0.000 description 3

- 238000007599 discharging Methods 0.000 description 3

- 238000000034 method Methods 0.000 description 3

- 238000004904 shortening Methods 0.000 description 2

- 230000003213 activating effect Effects 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 239000000758 substrate Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/50—Peripheral circuit region structures

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/4076—Timing circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/409—Read-write [R-W] circuits

- G11C11/4091—Sense or sense/refresh amplifiers, or associated sense circuitry, e.g. for coupled bit-line precharging, equalising or isolating

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/409—Read-write [R-W] circuits

- G11C11/4097—Bit-line organisation, e.g. bit-line layout, folded bit lines

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2207/00—Indexing scheme relating to arrangements for writing information into, or reading information out from, a digital store

- G11C2207/22—Control and timing of internal memory operations

- G11C2207/2281—Timing of a read operation

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Semiconductor Memories (AREA)

- Dram (AREA)

Abstract

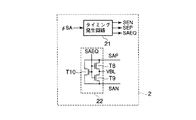

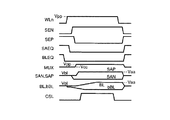

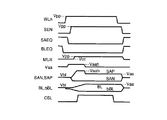

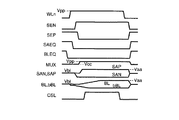

【解決手段】メモリセルMCがマトリクス状に配置されたメモリセルアレイ5と、メモリセルMCから読み出された信号を増幅する、NチャネルMOSトランジスタから構成されたNチャネルセンスアンプとPチャネルMOSトランジスタから構成されたPチャネルセンスアンプとを含むセンスアンプ6と、センスアンプ6に隣接して配置され、センスアンプ6が含むNチャネルセンスアンプ及びPチャネルセンスアンプをそれぞれ駆動するNチャネルMOSトランジスタを有するセンスアンプ駆動回路10、11Aと、これらセンスアンプ駆動回路が有する各々のNチャネルMOSトランジスタのゲート電極に共通の制御信号を供給するセンスアンプ制御回路2Aとを有する。

【選択図】 図6

Description

Claims (16)

- メモリセルがマトリクス状に配置されたメモリセルアレイと、

前記メモリセルから読み出された信号を増幅する、NチャネルMOSトランジスタから構成されたNチャネルセンスアンプとPチャネルMOSトランジスタから構成されたPチャネルセンスアンプとを含むセンスアンプと、

前記センスアンプに隣接して配置され、前記センスアンプが含む前記Nチャネルセンスアンプ及びPチャネルセンスアンプをそれぞれ駆動するNチャネルMOSトランジスタを有する第1、第2の駆動回路と、

前記第1、第2の駆動回路が有する各々の前記NチャネルMOSトランジスタのゲート電極に共通の制御信号を供給するセンスアンプ制御回路と、

を具備することを特徴とする半導体集積回路。 - メモリセルが行方向及び列方向にマトリクス状に配置され、ビット線対に接続されたメモリセルアレイと、

前記列方向に連続して配置され、前記メモリセルから読み出され前記ビット線対間に現われた微小信号を増幅する、PチャネルMOSトランジスタから構成されたPチャネルセンスアンプを含むセンスアンプと、

前記センスアンプに隣接して前記列方向に連続して配置され、前記センスアンプが含む前記Pチャネルセンスアンプを駆動するNチャネルMOSトランジスタを有する駆動回路と、

前記駆動回路が有する前記NチャネルMOSトランジスタのゲート電極に制御信号を供給するセンスアンプ制御回路と、

を具備することを特徴とする半導体集積回路。 - メモリセルが行方向及び列方向にマトリクス状に配置され、ビット線対に接続されたメモリセルアレイと、

前記列方向に連続して配置され、前記メモリセルから読み出され前記ビット線対間に現われた微小信号を増幅する、NチャネルMOSトランジスタから構成されたNチャネルセンスアンプとPチャネルMOSトランジスタから構成されたPチャネルセンスアンプとを含むセンスアンプと、

前記センスアンプに隣接して前記列方向に連続して配置され、前記センスアンプが含む前記Nチャネルセンスアンプ及びPチャネルセンスアンプをそれぞれ駆動するNチャネルMOSトランジスタを有する第1、第2の駆動回路と、

前記第1、第2の駆動回路が有する各々の前記NチャネルMOSトランジスタのゲート電極に共通の制御信号を供給するセンスアンプ制御回路と、

を具備することを特徴とする半導体集積回路。 - 前記Nチャネルセンスアンプを駆動する前記第1の駆動回路が有するNチャネルMOSトランジスタと、前記Pチャネルセンスアンプを駆動する前記第2の駆動回路が有するNチャネルMOSトランジスタとが、前記列方向に一列に配置されていることを特徴とする請求項3に記載の半導体集積回路。

- 前記第1の駆動回路が有するNチャネルMOSトランジスタのゲート長と、前記第2の駆動回路が有するNチャネルMOSトランジスタのゲート長が等しいことを特徴とする請求項4に記載の半導体集積回路。

- 前記第1の駆動回路が有するNチャネルMOSトランジスタのしきい値電圧と、前記第2の駆動回路が有するNチャネルMOSトランジスタのしきい値電圧が等しいことを特徴とする請求項4に記載の半導体集積回路。

- 前記列方向に連続して配置された前記センスアンプのうち、2個のセンスアンプ毎に、前記Pチャネルセンスアンプを駆動する駆動回路が1個ずつ配置されていることを特徴とする請求項2に記載の半導体集積回路。

- 前記列方向に連続して配置された前記センスアンプのうち、2個のセンスアンプ毎に、前記Nチャネルセンスアンプを駆動する前記第1の駆動回路と、前記Pチャネルセンスアンプを駆動する第2の駆動回路とが1個ずつ配置されていることを特徴とする請求項3に記載の半導体集積回路。

- 前記第1の駆動回路が有するNチャネルMOSトランジスタと、前記第2の駆動回路が有するNチャネルMOSトランジスタとが、前記列方向に伸びる共通のゲート電極を有することを特徴とする請求項4に記載の半導体集積回路。

- 前記第1の駆動回路が有するNチャネルMOSトランジスタのソースに接続されたソースコンタクトと、前記第2の駆動回路が有するNチャネルMOSトランジスタのソースに接続されたソースコンタクトとが、前記列方向に伸びる共通のゲート電極に対して、互いに反対側に配置されることを特徴とする請求項9に記載の半導体集積回路。

- 前記Pチャネルセンスアンプを構成する前記PチャネルMOSトランジスタはNウェル領域上に形成されており、前記Nウェル領域のウェル電位は、前記Pチャネルセンスアンプを駆動する前記駆動回路が有するNチャネルMOSトランジスタのドレイン電圧に等しいことを特徴とする請求項2に記載の半導体集積回路。

- 前記Pチャネルセンスアンプを構成する前記PチャネルMOSトランジスタはNウェル領域上に形成されており、前記Nウェル領域のウェル電位は、前記Pチャネルセンスアンプを駆動する前記第2の駆動回路が有するNチャネルMOSトランジスタのドレイン電圧に等しいことを特徴とする請求項3に記載の半導体集積回路。

- 前記Pチャネルセンスアンプを構成する前記PチャネルMOSトランジスタはNウェル領域上に形成され、前記Nチャネルセンスアンプを構成する前記NチャネルMOSトランジスタは前記Nウェル領域に隣接するPウェル領域上に形成されており、前記駆動回路が有する前記NチャネルMOSトランジスタは前記Pウェル領域上に形成されていることを特徴とする請求項2に記載の半導体集積回路。

- 前記Pチャネルセンスアンプを構成する前記PチャネルMOSトランジスタはNウェル領域上に形成され、前記Nチャネルセンスアンプを構成する前記NチャネルMOSトランジスタは前記Nウェル領域に隣接するPウェル領域上に形成されており、前記第1、第2の駆動回路が有する前記NチャネルMOSトランジスタは前記Pウェル領域上に形成されていることを特徴とする請求項1または3に記載の半導体集積回路。

- 前記Nチャネルセンスアンプと前記Pチャネルセンスアンプを含む前記センスアンプ、及び前記Nチャネルセンスアンプを駆動する前記第1の駆動回路を含む第1回路群と、前記センスアンプ、及び前記Pチャネルセンスアンプを駆動する前記第2の駆動回路を含む第2回路群とを複数備えた前記半導体集積回路であって、

前記第1、第2回路群の配置数を変更して、第1、第2の駆動回路の数を変更することにより、前記第1の駆動回路が有するNチャネルMOSトランジスタと前記第2の駆動回路が有するNチャネルMOSトランジスタとのトランジスタサイズ比を設定することを特徴とする請求項1または3に記載の半導体集積回路。 - 前記Nチャネルセンスアンプを構成する前記NチャネルMOSトランジスタのソース電位と、前記Pチャネルセンスアンプを構成する前記PチャネルMOSトランジスタのソース電位とをイコライズするイコライズトランジスタをさらに具備し、

前記イコライズトランジスタは、前記第1、第2の駆動回路が連続して配置された列内に配置されていることを特徴とする請求項3に記載の半導体集積回路。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003320862A JP2004140344A (ja) | 2002-09-24 | 2003-09-12 | 半導体集積回路 |

| US10/668,027 US6973002B2 (en) | 2002-09-24 | 2003-09-22 | Semiconductor integrated circuit comprising sense amplifier activating circuit for activating sense amplifier circuit |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002278072 | 2002-09-24 | ||

| JP2003320862A JP2004140344A (ja) | 2002-09-24 | 2003-09-12 | 半導体集積回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2004140344A true JP2004140344A (ja) | 2004-05-13 |

| JP2004140344A5 JP2004140344A5 (ja) | 2005-09-29 |

Family

ID=32095395

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003320862A Pending JP2004140344A (ja) | 2002-09-24 | 2003-09-12 | 半導体集積回路 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US6973002B2 (ja) |

| JP (1) | JP2004140344A (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7474549B2 (en) | 2006-08-08 | 2009-01-06 | Samsung Electronics Co., Ltd. | Bit-line equalizer, semiconductor memory device including the same, and method for manufacturing bit-line equalizer |

| JP2010040903A (ja) * | 2008-08-07 | 2010-02-18 | Nec Electronics Corp | 半導体記憶装置 |

| JP2014116619A (ja) * | 2014-01-16 | 2014-06-26 | Renesas Electronics Corp | 半導体記憶装置 |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20060018972A (ko) * | 2004-08-26 | 2006-03-03 | 주식회사 하이닉스반도체 | 비트 라인 감지 증폭기 제어 회로 |

| KR100728571B1 (ko) * | 2006-02-09 | 2007-06-15 | 주식회사 하이닉스반도체 | 반도체 메모리의 데이터 센싱장치 |

| KR100753418B1 (ko) * | 2006-03-30 | 2007-08-30 | 주식회사 하이닉스반도체 | 로우 및 컬럼 어드레스를 이용하여 비트라인 감지 증폭동작을 제어하는 반도체 메모리 장치 |

| KR101171254B1 (ko) * | 2010-05-31 | 2012-08-06 | 에스케이하이닉스 주식회사 | 비트라인 센스앰프 제어 회로 및 이를 구비하는 반도체 메모리 장치 |

| US9361972B1 (en) * | 2015-03-20 | 2016-06-07 | Intel Corporation | Charge level maintenance in a memory |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR0133973B1 (ko) * | 1993-02-25 | 1998-04-20 | 기다오까 다까시 | 반도체 기억장치 |

| JP3694072B2 (ja) | 1995-08-18 | 2005-09-14 | 株式会社日立製作所 | 半導体装置 |

| JPH09128966A (ja) * | 1995-10-31 | 1997-05-16 | Nec Corp | ダイナミック型半導体記憶装置 |

| EP1039470A3 (en) * | 1999-03-25 | 2000-11-29 | SANYO ELECTRIC Co., Ltd. | Semiconductor memory device |

| JP4552258B2 (ja) * | 2000-03-29 | 2010-09-29 | エルピーダメモリ株式会社 | 半導体記憶装置 |

-

2003

- 2003-09-12 JP JP2003320862A patent/JP2004140344A/ja active Pending

- 2003-09-22 US US10/668,027 patent/US6973002B2/en not_active Expired - Fee Related

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7474549B2 (en) | 2006-08-08 | 2009-01-06 | Samsung Electronics Co., Ltd. | Bit-line equalizer, semiconductor memory device including the same, and method for manufacturing bit-line equalizer |

| JP2010040903A (ja) * | 2008-08-07 | 2010-02-18 | Nec Electronics Corp | 半導体記憶装置 |

| JP2014116619A (ja) * | 2014-01-16 | 2014-06-26 | Renesas Electronics Corp | 半導体記憶装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20040075104A1 (en) | 2004-04-22 |

| US6973002B2 (en) | 2005-12-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6944078B2 (en) | Semiconductor device | |

| US6477100B2 (en) | Semiconductor memory device with over-driving sense amplifier | |

| US7414907B2 (en) | Semiconductor memory device | |

| US10141047B2 (en) | Static random access memory | |

| JP3781270B2 (ja) | 半導体集積回路装置 | |

| JP4024975B2 (ja) | データ伝送回路 | |

| US8169847B2 (en) | Semiconductor memory apparatus and refresh control method of the same | |

| KR101026658B1 (ko) | 단일-종단 감지 증폭기를 갖는 반도체 디바이스 | |

| JP2003228981A (ja) | 半導体記憶装置 | |

| US6191990B1 (en) | Semiconductor integrated circuit device having stabilizing capacitors connected between power lines of main amplifiers | |

| JP2004152394A (ja) | 半導体記憶装置 | |

| US7085187B2 (en) | Semiconductor storage device | |

| JP2007035157A (ja) | 強誘電体メモリ装置 | |

| US7619939B2 (en) | Semiconductor storage apparatus | |

| WO2017145312A1 (ja) | 半導体記憶装置 | |

| US8279692B2 (en) | Semiconductor device having hierarchical data line structure and control method thereof | |

| JP2004140344A (ja) | 半導体集積回路 | |

| JP2007115337A (ja) | 半導体メモリ装置 | |

| US20070076500A1 (en) | Semiconductor memory device | |

| US7751268B2 (en) | Sense amplifier power supply circuit | |

| US8004916B2 (en) | Semiconductor circuit | |

| JP2008299928A (ja) | 半導体記憶装置 | |

| JP2001266569A (ja) | 半導体記憶装置 | |

| JP2008299932A (ja) | 半導体記憶装置 | |

| KR20010077137A (ko) | 반도체 메모리 장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050801 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050801 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080401 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090519 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20090929 |