EP1484879A2 - Zweidrahtdatenvermittlung - Google Patents

Zweidrahtdatenvermittlung Download PDFInfo

- Publication number

- EP1484879A2 EP1484879A2 EP04013011A EP04013011A EP1484879A2 EP 1484879 A2 EP1484879 A2 EP 1484879A2 EP 04013011 A EP04013011 A EP 04013011A EP 04013011 A EP04013011 A EP 04013011A EP 1484879 A2 EP1484879 A2 EP 1484879A2

- Authority

- EP

- European Patent Office

- Prior art keywords

- signal line

- storage device

- unit

- clock

- data storage

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B3/00—Line transmission systems

- H04B3/50—Systems for transmission between fixed stations via two-conductor transmission lines

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/02—Details ; arrangements for supplying electrical power along data transmission lines

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/02—Details ; arrangements for supplying electrical power along data transmission lines

- H04L25/08—Modifications for reducing interference; Modifications for reducing effects due to line faults ; Receiver end arrangements for detecting or overcoming line faults

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/0008—Synchronisation information channels, e.g. clock distribution lines

Definitions

- the present invention relates to a two-wire type data communication method and system between a data storage device and a controller in a contact type data storage system, a controller and a data storage device.

- a contact type data storage system is used in a parts control of OA devices or a schedule control in a factory or the like.

- a two-wire type data communication system has been employed in a communication between a data storage device and a controller forming the contact type data storage system to make the system compact (for instance, see JP-A-2003-69653).

- Fig. 13 is a voltage wave form diagram for explaining a usual two-wire type data communication method.

- Fig. 14 is a block diagram showing a structural example of a contact type data storage system using the usual two-wire type data communication method.

- the contact type data storage system comprises a controller 1201 and a data storage device 1202.

- the controller 1201 includes a clock generating circuit 1205 for forming a clock pulse and a pulse of an opposite phase thereto, a voltage level generating circuit 1203 for generating the amplitude level of the clock pulse, a first transmitting circuit 1204 for changing the amplitude of the clock pulse in accordance with a transmit signal and a first signal detecting circuit 1206 for detecting an amplitude difference appearing in the clock pulse and the pulse of the opposite phase thereto.

- the data storage device 1202 includes a rectifying circuit 1208 for full-wave rectifying voltage from the clock pulse and the pulse of the opposite phase thereto, a data demodulating circuit 1209 for detecting the amplitude difference of the clock pulses to reproduce the transmit signal, a second transmitting circuit 1210 for changing a load impedance between two-wire type communication terminals in accordance with the transmit signal to change a voltage amplitude and a clock detecting circuit 1211 for reproducing the clock pulse.

- the voltage level generating circuit 1203 includes a resistance R1 connected to a source voltage +V and a resistance R2 connected in series thereto to output the voltage Vout of a node of the resistance R1 and the resistance R2.

- the transmitting circuit 1204 is composed of a MOS transistor having a source and a drain respectively connected to the resistance R2 and a reference potential GND of the voltage level generating circuit 1203 and a gate to which the transmit signal is inputted to determine the output level Vout of the voltage level generating circuit 1203.

- the clock generating circuit 1205 includes two stages of inverters to output clock pulses of the same phase and the opposite phase relative to a clock-signal input.

- the electric power supply terminals of the inverters are respectively connected to the output Vout of the voltage level generating circuit 1203.

- the amplitudes of the clock pulses of the same phase and the opposite phase are changed in accordance with the output Vout to superimpose the transmit signal on the clock pulses and transmit the superimposed transmit signal to the data storage device 1202.

- the data demodulating circuit 1209 extracts a signal component superimposed on the voltage rectified by the rectifying circuit 1208.

- the clock detecting circuit 1211 is composed of an inverter to reproduce the clock pulse without depending on the superimposed signal component and use the clock pulse as the clock of the data storage device 1202.

- the second transmitting circuit 1210 includes a resistance and a switch connected in series between the two-wire type communication terminals of the data storage device 1202 and changes a load impedance between the terminals in accordance with the transmit signal.

- the second transmitting circuit changes the amplitude of the clock pulse received from the controller 1201.

- the signal detecting circuit 1206 is connected to either of the two-wire type communication terminals in the controller 1201 to detect the change of the amplitude of the clock pulse in these terminals as a receive signal.

- Fig. 15 is a circuit diagram showing the data demodulating circuit 1209 and an operation thereof is explained by using the voltage wave form diagram of Fig. 13.

- a voltage wave form on which the signal as shown in Fig. 13(e) as an output of the rectifying circuit of the data storage device is superimposed is inputted to remove noise generated due to skew or the like.

- a high-pass filter 1302 the leading and trailing edges of the signal are detected and the dc components of the signal are removed as shown in Fig. 13(f).

- a comparator 1303 with a hysteresis when the output of the high-pass filter 1302 exceeds a high hystresis level, as shown in Fig. 13(g), an internal source voltage level, that is, a logic "H” is outputted. Further, when the output of the high-pass filter is lower than a low hysteresis level, an internal reference voltage level, that is, a logic "L” is outputted. Finally, in a D flip flop 1304, the output of the comparator 1303 is detected at the trailing edge of the output of the clock detecting circuit and outputted as demodulated data.

- a transmit signal component is superimposed on a transmit clock as the change of an amplitude to perform a data communication.

- the signal is mutually transmitted and received and electric power and clocks are simultaneously supplied to the data storage device from the controller.

- the present invention solves the above-described usual problems and it is an object of the present invention to provide a two-wire type data communication method and system, a controller and a data storage device in which a stable communication can be realized without an erroneous data demodulation due to the influence of skew between signals and a burden for the controller in its design is decreased in a two-wire type data communication for performing a data communication and supplying clocks and electric power by first and second signal lines between the controller and the data storage device.

- a two-wire type data communication method in accordance with the present invention defined in claim 1 concerns a data communication method for performing a data communication and supplying clocks and electric power by a first signal line and a second signal line between a controller and a data storage device.

- a clock pulse of a positive phase is transmitted by the first signal line and a clock pulse of an opposite phase modulated in accordance with the logic of transmit data is transmitted by the second signal line.

- the clock pulse of the positive phase is extracted on the basis of the first signal line and a signal extracted from the modulated clock pulse of the opposite phase that is transmitted by the second signal line can be decided by using the clock pulse of the positive phase.

- a suitable modulation is carried out to perform a demodulation process by a logic circuit without using an edge detecting type demodulation method so that an erroneous demodulation due to a skew between signals can be avoided.

- the demodulation can be more simply performed than a related art, merit is large in view of cost.

- the structure of the controller does not need ternary voltage values like the related art, an adjustment that takes unevenness in an equivalent resistance of the data storage device into consideration is not necessary. Thus, a burden in design can be reduced.

- the clock pulse of the opposite phase transmitted by the second signal line is modulated and formed depending on the presence or absence of a pulse in accordance with the logic of the transmit data in the two-wire type data communication method according to claim 1.

- the modulated signal is a total amplitude signal representing a logical value by the presence or absence of the clock pulse

- a demodulationprocess canbe performed by a logic circuit without requiring an edge detecting type demodulation method.

- a data demodulation substantially having no erroneous demodulation due to the influence of a skew between signals can be carried out.

- the clock pulse of the opposite phase transmitted by the second signal line is modulated and formed by the change of a delay time relative to the clock pulse of the positive phase in accordance with the logic of the transmit data in the two-wire type data communication method according to claim 1.

- the modulated signal is a total amplitude signal representing a logical value by the change of the delay time of the clock pulse

- a demodulation process can be performed by a logic circuit without requiring an edge detecting type demodulation method.

- data can be extracted without receiving the influence of internal power source noise due to a timing skew between two-wire transmit signals.

- the clock pulse of the opposite phase transmitted by the second signal line is modulated and formed by the change of a duty ratio in accordance with the logic of the transmit data in the two-wire type data communication method according to claim 1.

- the modulated signal is a total amplitude signal representing a logical value by the change of a duty ratio of the clock pulse

- a demodulation process canbe performed by a logic circuit without requiring an edge detecting type demodulation method.

- data can be extracted without receiving the influence of internal power source noise due to a timing skew between two-wire transmit signals.

- the clock pulse of the opposite phase transmitted by the second signal line is modulated and formed at a position of a pulse signal superimposed by an opposite polarity in accordance with the logic of the transmit data in the two-wire type data communication method according to claim 1.

- the modulated signal is a total amplitude signal representing a logical value at the position of the pulse superimposed on the clock pulse of the opposite phase

- a demodulation process can be performed by a logic circuit without requiring an edge detecting type demodulation method.

- data can be extracted without receiving the influence of internal power source noise due to a timing skew between two-wire transmit signals.

- the clock pulse of the positive phase transmitted by the first signal line and the clock pulse of the opposite phase transmitted by the second signal line are modulated and formed by the change of a duty ratio in accordance with the logic of the transmit data in the two-wire type data communication method according to claim.

- the modulated signal is a total amplitude signal representing a logical value by the duty ratio of the clock pulse

- a demodulation process can be performed by a logic circuit without requiring an edge detecting type demodulation method.

- data can be extracted without receiving the influence of internal power source noise due to a timing skew between two-wire transmit signals.

- a two-wire type data communication system concerns a data communication system for performing a data communication and supplying clocks and electric power by a first signal line and a second signal line between a controller and a data storage device.

- the controller includes a unit for forming clock pulses of a positive phase and an opposite phase, a unit for transmitting the clock pulse of the positive phase to the first signal line and a unit for modulating the clock pulse of the opposite phase depending on the presence or absence of a pulse in accordance with the logic of transmit data and transmitting the modulated clock pulse to the second signal line.

- the data storage device includes a unit for rectifying the voltage of the first and second signal lines and supplying source voltage to the data storage device, a unit for extracting a clock in the device on the basis of the first signal line and a data demodulating unit for detecting the presence or absence of the clock pulse of the opposite phase transmitted by the second signal line using the clock in the device.

- the modulated signal is a total amplitude signal representing a logical value by the presence or absence of the clock pulse

- a demodulation process can be performed by a logic circuit without requiring an edge detecting type demodulation method and a data demodulation substantially having no erroneous demodulation due to the influence of a skew between signals can be achieved.

- the demodulating circuit of the data storage device can be more simply formed than that of a related art, merit is large in view of cost.

- the structure of the controller does not need ternary voltage values like the related art, an adjustment that takes unevenness in an equivalent resistance of the data storage device into consideration is not necessary. Thus, a burden in design can be reduced.

- a two-wire type data communication system concerns a data communication system for performing a data communication and supplying clocks and electric power by a first signal line and a second signal line between a controller and a data storage device.

- the controller includes a unit for forming clock pulses of a positive phase and an opposite phase, a unit for transmitting the clock pulse of the positive phase to the first signal line and a unit for modulating the clock pulse of the opposite phase depending on the change of a delay time relative to the clock pulse of the positive phase in accordance with the logic of transmit data and transmitting the modulated clock pulse to the second signal line.

- the data storage device includes a unit for rectifying the voltage of the first and second signal lines and supplying source voltage to the data storage device, a unit for extracting a clock in the device on the basis of the first signal line and a data demodulating unit for detecting the change of the delay time of the clock pulse of the oppositephase transmittedby the second signal line using the clock in the device.

- the modulated signal is a total amplitude signal representing a logical value by the change of the delay time of the clock pulse

- a demodulation process can be performed by a logic circuit without requiring an edge detecting type demodulation method.

- data can be extracted without receiving the influence of internal power source noise due to a timing skew between two-wire transmit signals.

- the demodulating circuit of the data storage device can be more simply formed than that of a related art, merit is large in view of cost.

- the structure of the controller does not need ternary voltage values like the related art, an adjustment that takes unevenness in an equivalent resistance of the data storage device into consideration is not necessary. Thus, a burden in design can be reduced.

- a two-wire type data communication system concerns a data communication system for performing a data communication and supplying clocks and electric power by a first signal line and a second signal line between a controller and a data storage device.

- the controller includes a unit for forming clock pulses of a positive phase and an opposite phase, a unit for transmitting the clock pulse of the positive phase to the first signal line and a unit for modulating the clock pulse of the opposite phase by the change of a duty ratio in accordance with the logic of transmit data and transmitting the modulated clock pulse to the second signal line.

- the data storage device includes a unit for rectifying the voltage of the first and second signal lines and supplying source voltage to the data storage device, a unit for extracting a clock in the device on the basis of the first signal line and a data demodulating unit for detecting the change of the duty ratio of the clock pulse transmitted by the second signal line using the clock in the device.

- the modulated signal is a total amplitude signal representing a logical value by the change of the duty ratio of the clock pulse

- a demodulation process can be performed by a logic circuit without requiring an edge detecting type demodulation method.

- data can be extracted without receiving the influence of internal power source noise due to a timing skew between two-wire transmit signals.

- the demodulating circuit of the data storage device can be more simply formed than that of a related art, merit is large in view of cost.

- the structure of the controller does not need ternary voltage values like the related art, an adjustment that takes unevenness in an equivalent resistance of the data storage device into consideration is not necessary. Thus, a burden in design can be reduced.

- a two-wire type data communication system concerns a data communication system for performing a data communication and supplying clocks and electric power by a first signal line and a second signal line between a controller and a data storage device.

- the controller includes a unit for forming clock pulses of a positive phase and an opposite phase, a unit for transmitting the clock pulse of the positive phase to the first signal line and a unit for modulating the clock pulse of the opposite phase at a position of a pulse superimposed by an opposite polarity in accordance with the logic of transmit data and transmitting the modulated clock pulse to the second signal line.

- the data storage device includes a unit for rectifying the voltage of the first and second signal lines and supplying source voltage to the data storage device, a unit for extracting a clock in the device on the basis of the first signal line and a data demodulating unit for detecting the position of the pulse superimposed by the opposite polarity that is transmitted to the second signal line using the clock in the device.

- the modulated signal is a total amplitude signal representing a logical value by the time position of the pulse with a narrow width superimposed on the clock pulse of the opposite phase

- a demodulation process can be performed by a logic circuit without requiring an edge detecting type demodulation method.

- data can be extracted without receiving the influence of internal power source noise due to a timing skew between two-wire transmit signals.

- the demodulating circuit of the data storage device can be more simply formed than that of a related art, merit is large in view of cost.

- the structure of the controller does not need ternary voltage values like the related art, an adjustment that takes unevenness in an equivalent resistance of the data storage device into consideration is not necessary. Thus, a burden in design can be reduced.

- a two-wire type data communication system concerns a data communication system for performing a data communication and supplying clocks and electric power by a first signal line and a second signal line between a controller and a data storage device.

- the controller includes a unit for forming clock pulses of a positive phase and an opposite phase and a unit for modulating the clock pulse of the positive phase and the clock pulse of the opposite phase by the change of a duty ratio in accordance with the logic of transmit data and transmitting the modulated clock pulses respectively to the first signal line and the second signal line.

- the data storage device includes a unit for rectifying the voltage of the first and second signal lines and supplying source voltage to the data storage device, a unit for extracting a clock in the device on the basis of the first signal line and a data demodulating unit for detecting the change of the duty ratio of the clock pulse of the opposite phase transmitted by the second signal line using. the clock in the device.

- the modulated signal is a total amplitude signal representing a logical value by the duty ratio of the clock pulse

- a demodulation process can be performed by a logic circuit without requiring an edge detecting type demodulation method.

- data can be extracted without receiving the influence of internal power source noise due to a timing skew between two-wire transmit signals.

- the demodulating circuit of the data storage device can be more simply formed than that of a related art, merit is large in view of cost.

- the structure of the controller does not need ternary voltage values like the related art, an adjustment that takes unevenness in an equivalent resistance of the data storage device into consideration is not necessary. Thus, a burden in design can be reduced.

- a controller for performing a data communication and supplying clocks and electric power by a first signal line and a second signal line between a data storage device and the controller.

- the controller includes a unit for forming clock pulses of a positive phase and an opposite phase, a unit for transmitting the clock pulse of the positive phase to the first signal line and a unit for modulating the clock pulse of the opposite phase depending on the presence or absence of a pulse in accordance with the logic of transmit data and transmitting the modulated clock pulse to the second signal line.

- the modulated signal is a total amplitude signal representing a logical value by the presence or absence of the clock pulse

- a demodulationprocess can be performed by a logic circuit without requiring an edge detecting type demodulation method and a data demodulation substantially having no erroneous demodulation due to the influence of a skew between signals can be achieved.

- ternary voltage values like the related art are not required, an adjustment that takes unevenness in an equivalent resistance of the data storage device into consideration is not necessary. Thus, a burden in design can be reduced.

- a controller for performing a data communication and supplying clocks and electric power by a first signal line and a second signal line between a data storage device and the controller.

- the controller includes a unit for forming clock pulses of a positive phase and an opposite phase, a. unit for transmitting the clock pulse of the positive phase to the first signal line and a unit for modulating the clock pulse of the opposite phase depending on the change of a delay time relative to the clock pulse of the positive phase in accordance with the logic of transmit data and transmitting the modulated clock pulse to the second signal line.

- the modulated signal is a total amplitude signal representing a logical value by change of the delay time of the clock pulse

- a demodulation process can be performed by a logic circuit without requiring an edge detecting type demodulation method.

- data can be extracted without receiving the influence of internal power source noise due to a timing skew between two-wire transmit signals.

- ternary voltage values like the related art are not required, an adjustment that takes unevenness in an equivalent resistance of the data storage device into consideration is not necessary. Thus, a burden in design can be reduced.

- a controller for performing a data communication and supplying clocks and electric power by a first signal line and a second signal line between a data storage device and the controller.

- the controller includes a unit for forming clock pulses of a positive phase and an opposite phase, a unit for transmitting the clock pulse of the positive phase to the first signal line and a unit for modulating the clock pulse of the opposite phase by the change of a duty ratio in accordance with the logic of transmit data and transmitting the modulated clock pulse to the second signal line.

- the modulated signal is a total amplitude signal representing a logical value by the change of the duty ratio of the clock pulse

- a demodulation process can be performed by a logic circuit without requiring an edge detecting type demodulation method.

- data can be extracted without receiving the influence of internal power source noise due to a timing skew between two-wire transmit signals.

- ternary voltage values like the related art are not required, an adjustment that takes unevenness in an equivalent resistance of the data storage device into consideration is not necessary. Thus, a burden in design can be reduced.

- a controller for performing a data communication and supplying clocks and electric power by a first signal line and a second signal line between a data storage device and the controller.

- the controller includes a unit for forming clock pulses of a positive phase and an opposite phase, a unit for transmitting the clock pulse of the positive phase to the first signal line and a unit for modulating the clock pulse of the opposite phase at a position of a pulse superimposed by an opposite polarity in accordance with the logic of transmit data and transmitting the modulated clock pulse to the second signal line.

- the modulated signal is a total amplitude signal representing a logical value by the time position of the pulse with a narrow width superimposed on the clock pulse of the opposite phase

- a demodulation process can be performed by a logic circuit without requiring an edge detecting type demodulation method.

- data can be extracted without receiving the influence of internal power source noise due to a timing skew between two-wire transmit signals.

- ternary voltage values like the related art are not required, an adjustment that takes unevenness in an equivalent resistance of the data storage device into consideration is not necessary. Thus, a burden in design can be reduced.

- a controller for performing a data communication and supplying clocks and electric power by a first signal line and a second signal line between a data storage device and the controller.

- the controller includes a unit for forming clock pulses of a positive phase and an opposite phase and a unit for modulating the clock pulse of the positive phase and the clock pulse of the opposite phase by the change of a duty ratio in accordance with the logic of transmit data and transmitting the modulated clock pulses respectively to the first signal line and the second signal line.

- the modulated signal is a total amplitude signal representing a logical value by the duty ratio of the clocks pulses

- a demodulation process can be performed by a logic circuit without requiring an edge detecting type demodulation method.

- data can be extracted without receiving the influence of internal power source noise due to a timing skew between two-wire transmit signals.

- ternary voltage values like the related art are not required, an adjustment that takes unevenness in an equivalent resistance of the data storage device into consideration is not necessary. Thus, a burden in design can be reduced.

- a data storage device concerns a data storage device for performing a data communication and supplying clocks and electric power by a first signal line and a second signal line between a controller and the data storage device.

- the data storage device includes a unit for rectifying the voltage of the first and second signal lines and supplying source voltage to the data storage device, a unit for extracting a clock in the device on the basis of the first signal line and a data demodulating unit for detecting the presence or absence of the clock pulse of the opposite phase transmitted by the second signal line using the clock in the device.

- the modulated signal is a total amplitude signal representing a logical value by the presence or absence of the clock pulse

- a demodulation process can be'performed by a logic circuit without requiring an edge detecting type demodulation method. Further, a data demodulation substantially having no erroneous demodulation due to the influence of a skew between signals can be realized. Further, since the demodulating circuit can be more simply formed than that of a related art, an advantage is high in view of cost.

- a data storage device for performing a data communication and supplying clocks and electric power by a first signal line and a second signal line between a controller and the data storage device.

- the data storage device includes a unit for rectifying the voltage of the first and second signal lines and supplying source voltage to the data storage device, a unit for extracting a clock in the device on the basis of the first signal line and a data demodulating unit for detecting the change of the delay time of the clock pulse of the oppositephase transmitted by the second signal line using the clock in the device.

- the modulated signal is a total amplitude signal representing a logical value by the change of the delay time of the clock pulse

- a demodulation process can be performed by a logic circuit without requiring an edge detecting type demodulation method.

- data can be extracted without receiving the influence of internal power source noise due to a timing skew between two-wire transmit signals.

- the demodulating circuit can be more simply formed than that of a related art, an advantage is high from the viewpoint of cost.

- a data storage device for performing a data communication and supplying clocks and electric power by a first signal line and a second signal line between a controller and the data storage device.

- the data storage device includes a unit for rectifying the voltage of the first and second signal lines and supplying source voltage to the data storage device, a unit for extracting a clock in the device on the basis of the first signal line and a data demodulating unit for detecting the change of the duty ratio of the clock pulse transmitted by the second signal line using the clock in the device.

- the modulated signal is a total amplitude signal representing a logical value by the change of the duty ratio of the clock pulse

- a demodulation process can be performed by a logic circuit without requiring an edge detecting type demodulation method.

- data can be extracted without receiving the influence of internal power source noise due to a timing skew between two-wire transmit signals.

- the demodulating circuit can be more simply formed than that of a related art, an advantage is high from the viewpoint of cost.

- a data storage device concerns a data storage device for performing a data communication and supplying clocks and electric power by a first signal line and a second signal line between a controller and the data storage device.

- the data storage device includes a unit for rectifying the voltages of the first and second signal lines and supplying source voltage to the data storage device, a unit for extracting a clock in the device on the basis of the first signal line and a data demodulating unit for detecting the pulse position superimposed by the opposite polarity that is transmitted to the second signal line using the clock in the device.

- the modulated signal is a total amplitude signal representing a logical value by the time position of the pulse with a narrow width superimposed on the clock pulse of the opposite phase

- a demodulation process can be performed by a logic circuit without requiring an edge detecting type demodulation method.

- data can be extracted without receiving the influence of internal power source noise due to a timing skew between two-wire transmit signals.

- the demodulating circuit can be more simply formed than that of a related art, an advantage is high from the viewpoint of cost.

- a data storage device concerns a data storage device for performing a data communication and supplying clocks and electric power by a first signal line and a second signal line between a controller and the data storage device.

- the data storage device includes a unit for rectifying the voltages of the first and second signal lines and supplying source voltage to the data storage device, a unit for extracting a clock in the device on the basis of the first signal line and a data demodulating unit for detecting the change of the duty ratio of the clock pulse of the opposite phase transmitted by the second signal line using the clock in the device.

- the modulated signal is a total amplitude signal representing a logical value by the duty ratio of the clock pulse

- a demodulation process can be performed by a logic circuit without requiring an edge detecting type demodulation method.

- data can be extracted without receiving the influence of internal power source noise due to a timing skew between two-wire transmit signals.

- the demodulating circuit can be more simply formed than that of a related art, merit is large in view of cost.

- Fig. 1 is a voltage wave form diagram showing a two-wire type data communication method according to a first embodiment of the present invention.

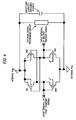

- Fig. 2 is a block diagram showing a structural example of a data storage device in a contact type data storage system using the two-wire type data communication method according to the first embodiment of the present invention.

- the two-wire type data communication method of this embodiment includes a first transmit signal as a stable clock pulse shown in Fig. 1(a) and a second transmit signal obtained by superimposing data on a clock pulse as shown in Fig. 1(b).

- transmit data has a specific logic (In Fig. 1, "1")

- the first transmit signal. and the second transmit signal have a relation of the clock pulses of opposite phases to each other.

- the transmit data has an opposite logic (In Fig. 1, "0")

- the clock pulse is not transmitted to the second transmit signal.

- the data storage device receiving the above-described transmit signals firstly forms internal operating voltage by a full-wave rectification of the first and second transmit signals and extracts a stable internal operating clock on the basis of the first transmit signal. Then, the data storage device detects the presence or absence of the clock pulse of the second transmit signal using the internal operating clock to simply demodulate the data as shown in Fig. 1(e).

- the data storage device shown in Fig. 2 includes a rectifying circuit 208 for forming internal source voltage from the first and second transmit signals, a data demodulating circuit 211 for extracting receive data from the controller, a smoothing capacity 212 for an internal power source and a second transmitting circuit 210 used when the data is transmitted from the data storage device to the controller.

- the stable clock pulse (Fig. 1(a)) is extracted on the basis of the first transmit signal and the second transmit-signal (Fig. 1(b)) is directly latched to a D flip flop by using the leading edge of the clock pulse as an operating clock to extract demodulated data (Fig. 1(e)).

- the first and second transmit signals are directly inputted to the D flip flop of the data demodulating circuit 211.

- an adjusting circuit is actually required for adjusting a voltage level and a polarity from the first and second transmit signals to reproduce a signal.

- a timing adjusting circuit may be possibly required so as not to generate a hold error due to a clock skew.

- the data demodulating circuit detects the presence or absence of the clock pulse of the second transmit signal as data by using the first transmit signal as the internal operating clock.

- a circuit structure may be formed that combined logical data such as an exclusive OR of the first and second transmit signals is used as an input signal to the D flip flop of the data demodulating circuit 211.

- the smoothing capacity 212 needs to be inserted into an internal power supply circuit to maintain the electric power in this block.

- a source voltage value VDD1 after time t0 passes is expressed by a following formula.

- VDD1 VDD x (exp (-t0/RC))

- the capacity value C may be determined so that the VDD1 is not lower than the minimum operating voltage of the internal circuit.

- this value is small, even if a capacity element is not specially inserted, only a parasitic capacity of the internal circuit may be sufficient.

- the data signal is a total amplitude signal represented by the presence or absence of the clock pulse, a demodulation process can be performed in a logic circuit without requiring an edge detecting type demodulation method.

- the erroneous demodulation due to the influence of the skew between the signals may not be substantially possibly generated.

- the demodulating circuit of the data storage device can be more simply formed than that of the related art, merit is large in view of cost.

- the second transmit signal can be formed in the simple logic circuit. Ternary voltage values like the related art are not necessary, so that an adjustment that takes unevenness in equivalent resistance of the data storage device into consideration is not required. Thus, a burden in design of the structure of the controller can be reduced.

- Fig. 3 is a voltage wave form diagram showing a two-wire type data communication method according to a second embodiment of the present invention.

- Fig. 6 is a block diagram showing a structural example of a controller in a contact type data storage system using the two-wire type data communication method according to the second embodiment of the present invention.

- the two-wire type data communication method of this embodiment includes a first transmit signal as a stable clock pulse shown in Fig. 3(a) and a second transmit signal obtained by superimposing data on a clock pulse as shown in Fig. 3(b).

- the first transmit signal and the second transmit signal have a relation of the clock pulses of opposite phases to each other.

- transmit data has a specific logic (In Fig. 3, "1")

- the "H" pulse of the second transmit signal advances by time of td1 relative to the "L" pulse of the first signal.

- the transmit data has an opposite logic

- the "H" pulse of the second transmit signal advances by time of td2.

- a data storage device receiving the above-described transmit signals firstly forms internal operating voltage by a full-wave rectification of the first and second transmit signals and extracts a stable internal operating clock on the basis of the first transmit signal. Then, the data storage device detects the change of the delay time of the second transmit signal as a data signal using the internal operating clock to simply perform a data modulation as shown in Fig. 3(e).

- Fig. 4 is one example of a full-wave rectifying circuit for forming the internal operating voltage from the first and second transmit signals.

- the full-wave rectifying circuit is composed of PchMOS transistors M1 to M4.

- Fig. 5 is a voltage wave form diagram for explaining an internal operation when an internal power source formed by using the full-wave rectifying circuit having a structure shown in Fig. 4.

- the applied voltage of the input terminal of the second transmit signal changes from "H” to "L"

- the potential of the internal VDD is clamped to the second transmit signal terminal through the M2.

- the voltages of the first and second transmit signal input terminals have substantially the same potential (there is a difference of voltage of about Vt of the M2 transistor between them).

- Voltage between the internal VDD and the internal Vss is held by a smoothing capacity in the power source for a prescribed period. Accordingly, the internal Vss potential is lowered in accordance with the change of the applied voltage of the second transmit signal input terminal.

- the internal VDD potential is clamped to the voltage of the first transmit signal input terminal through the M1 and remains to be substantially the same potential (there is a difference of voltage of about Vt of the M1 transistor).

- the wave form of the input of the second transmit signal when the internal Vss is considered to be the reference changes from “L” to "H” like the change of the voltage of the terminal.

- the wave form diagram in Fig. 5 When the internal Vss is considered to be the reference, the wave form (a) of the first transmit signal and the wave form (b) of the second transmit signal are respectively shown as wave forms (d) and (e) .

- an internal signal (d) is shaped to obtain an operating clock (g).

- a signal (f) obtained by delaying an internal signal (e) by ⁇ d is latched at a fall timing of the internal signal so that demodulated data (h) can be obtained.

- the delay time ⁇ d may be set so that td1 - ⁇ d satisfies the set up time of a latching flip-flop and

- the fall timing of the extracted operating clock (g) synchronizes with the fall timing of the wave form (a) of the first transmit signal.

- the fall timing of the wave form (e) of the signal also synchronizes with the rise timing of the first transmit signal (a).

- the operating clock may be formed from the wave form (e) of the signal.

- a signal obtainedby delaying the wave form (d) of the signal by ⁇ d is latched as data so that the demodulated data can be obtained at the rise timing of the first transmit signal (a).

- the circuit structure of the data storage device in this embodiment may be basically the same as the data storage device of the first embodiment shown as a circuit image in Fig. 2, the detailed description thereof is omitted.

- the second transmit signal- is latched to a D flip flop by the trailing edge of the clock pulse as the first transmit signal so that data can be demodulated.

- a circuit for delaying an input signal to the D flip flop by ⁇ d is required.

- a three-stage inverter circuit is connected in series to a reference clock to form the first transmit signal (Fig. 3(a)).

- a two-stage inverter circuit is connected in series to the reference clock to form the second transmit signal (Fig. 3 (b)).

- a transistor switch 401 and a delaying capacitor 402 for switching the wiring load of the inverter circuit are provided.

- a clock pulse passing the three stages of the inverter circuit from the reference clock is outputted to a first transmit signal line.

- "L" voltage is applied to the gate of the transistor switch 401 to turn off the transistor switch 401 and a clock pulse passing the two stages of the inverter circuit is outputted to a second transmit signal line from the reference clock.

- the second transmit signal is outputted more rapidly by one stage of the inverter circuit (td1 of -Fig. 3) more rapidly than the first signal.

- the wiring load is changed by the transistor switch and the delaying capacitor.

- a load of a wiring resistance or a load having the combination of the wiring resistance and the delaying capacitor may be switched by the transistor switch.

- Time td1- ⁇ d in Fig. 3 may be determined so as to satisfy the regulation of the set up time of the D flip flop of the data demodulating circuit 211 in Fig. 2 and

- may be likewise determined so as to satisfy the hold time of the D flip flop.

- the method according to this embodiment in which the transmit signals are formed by changing a signal delay time due to the change of the wiring load in the intermediate node of the signal has advantages as described below.

- the first and second transmit signals are full-wave rectified to form an internal operating power source. Accordingly, when the first and second transmit signals have the same polarity and are temporarily stopped, that is, when the signals are stopped within the time of skew of td1 or td2 shown in Fig. 3, the source voltage of an internal circuit falls. After that, even when the transmission of the signals are resumed, a process cannot be continuously carried out and the process needs to be recommenced from the beginning.

- the first and second transmit signals are formed by an output port of a microcomputer and directly outputted, a situation may often arise that an interrupt process of the microcomputer is generated halfway and the transmit signals to the data storage device are stopped for a prescribed time, and then, a process is resumed.

- the transmit signals are temporarily stopped, the first and second transmit signals always need to be stopped with opposite polarities. Thus, the burden of the microcomputer is increased.

- the first and second transmit signals are stopped with the opposite polarities under a steady state after the delay time of the signal.

- a process can be continuously carried out after the reference clock is resumed without fall of the internal source voltage of the data storage device. Accordingly, an excess burden is not advantageously necessary in the processing of the microcomputer.

- a method for determining the capacity value of the smoothing capacity is the same as that described in the first embodiment. In this embodiment, owing to the skew between the signals (either larger one of td1 or td2), a shorter time than the time t0 in the case of the first embodiment can be realized. Thus, a smaller capacity value may be realized.

- the related art employs an method for detecting the edge of the change point of the signal because of the data of a small amplitude signal, an erroneous demodulation may be possibly simply generated due to the variation of the internal source voltage due to the skew between the signals.

- the data signal is a total amplitude signal represented by the change of the delay time of the clock pulse, a demodulation process can be performed by a logic circuit without requiring the edge detecting type demodulation method.

- data can be extracted without receiving the influence of internal power source noise due to a timing skew between two-wire transmit signals.

- the demodulating circuit of the data storage device can be more simply formed than the related art, merit is high in view of cost. Further, since the structure of the controller does not need ternary voltage values like the related art, an adjustment that takes unevenness in an equivalent resistance of the data storage device into consideration is not necessary. Thus, a burden in design can be reduced.

- Fig. 7 is a voltage wave form diagram showing a two-wire type data communication method according to a third embodiment of the present invention.

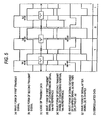

- Fig. 8 is a block diagram showing a structural example of a data storage device in a contact type data storage system using the two-wire type data communication method according to the third embodiment of the present invention.

- the two-wire type data communication method of this embodiment includes a first transmit signal as a stable clock pulse shown in Fig. 7(a) and a second transmit signal as a clock pulse with an opposite phase to that of the first transmit signal as shown in Fig. 7(b) in which the duty ratio of the clock pulse is changed in accordance with the logic of transit data.

- the data storage device receiving the above-described transmit signals firstly forms internal operating voltage by a full-wave rectification of the first and second transmit signals and extracts a stable internal operating clock on the basis of the first transmit signal. Then, the data storage device extracts the change of the duty ratio of the clock pulse of the second transmit signal by using the internal operating clock to simply demodulate the data as shown in Fig. 7(e).

- the data storage device shown in Fig. 8 includes a rectifying circuit 608 for forming internal source voltage from the first and second transmit signals, a . data demodulating circuit 611 for extracting receive data from a controller, a smoothing capacity 612 for an internal power source and a second transmitting circuit 610 used when the data is transmitted from the data storage device to the controller.

- the stable clock pulse (Fig. 7(a)) is extracted on the basis of the first transmit signal and the second transmit signal (Fig. 7(b)) is directly latched to a D flip flop by using the trailing edge of the clock pulse as the operating clock to extract demodulated data (Fig. 7(e)).

- the duty ratio of the clock pulse of the second transmit signal is set to 3:7 when the logic of the transmit data is "1", and the duty ratio is set to 5:5 when the logic of the transmit data is "0".

- a signal obtained by delaying the second transmit signal by ⁇ t is latched by the trailing edge of the first transmit signal.

- the ratio of the duty ratio maybe set so as to adequately satisfy the regulations of the set up time and the hold time of the D flip flop when the second transmit signal is latched by the first transmit signal as the clock.

- the first and second transmit signals are directly inputted to the D flip flop of the data demodulating circuit 611.

- an adjusting circuit is actually required for adjusting a voltage level and a polarity from the first and second transmit signals to reproduce a signal.

- a circuit for delaying an input signal to the D flip flop by ⁇ d is necessary.

- the data demodulating circuit detects the change of the duty ratio of the clock pulse of the second transmit signal as data by using the first transmit signal as the internal operating clock.

- a circuit structure may be formed that combined logical data such as an exclusive OR of the first and second transmit signals is used as the input signal to the D flip flop of the data demodulating circuit 611.

- the smoothing capacity 612 needs to be inserted into the internal power source to maintain the electric power of the block.

- a method for determining the capacity value of the smoothing capacity is basically the same as that described in the first embodiment. Thus, the explanation thereof is omitted.

- the related art employs a method for detecting the edge of the change point of the signal because of the data of a small amplitude signal, an erroneous demodulation may be possibly simply generated due to the variation of the internal source voltage due to the skew between the signals.

- the data signal is a total amplitude signal represented by the change of the duty ratio of the clock pulse, a demodulation process can be performed by a logic circuit without requiring the edge detecting type demodulation method.

- data can be extracted without receiving the influence of internal power source noise due to a timing skew between two-wire transmit signals.

- the demodulating circuit of the data storage device can be more simply formed than the related art, merit is high in view of cost. Further, since the structure of a controller does not need ternary voltage values like the related art and uses the total amplitude signal, the controller can be simply formed by the logic circuit. Thus, a burden in design is reduced.

- Fig. 9 is a voltage wave form diagram showing a two-wire type data communication method according to a fourth embodiment of the present invention.

- Fig. 10 is a block diagram showing a structural example of a data storage device in a contact type data storage system using the two-wire type data communication method according to the fourth embodiment of the present invention.

- the two-wire type data communication method of this embodiment includes a first transmit signal as a stable clock pulse shown in Fig. 9(a) and a second transmit signal as a clock pulse with an opposite phase to that of the first transmit signal as shown in Fig. 9(b) and showing the logical data of "H” or "L” corresponding to the superimposition of a pulse signal with a small time width t0 on the polarity "H" or "L” of the signal.

- the data storage device receiving the above-described transmit signals firstly forms internal operating voltage by a full-wave rectification of the first and second transmit signals and extracts a stable internal operating clock on the basis of the first transmit signal. Then, the data storage device extracts the pulse signal with the small time width t0 superimposed on the second transmit signal in accordance with an exclusive OR of the fist and second transmit signals to detect on which polarity of the clock pulse of the first transmit signal the pulse signal is superimposed and process the pulse signal by the internal operating clock extracted on the basis of the first transmit signal.

- data can be simply demodulated.

- the data storage device shown in Fig. 10 includes a rectifying circuit 808 for forming internal source voltage from the first and second transmit signals, a data demodulating circuit 811 for extracting receive data from a controller, a smoothing capacity 812 for an internal power source and a second transmitting circuit 810 used when the data is transmitted from the data storage device to the controller.

- an exclusive OR signal of the first and second transmit signals is extracted (Fig. 9(d)) and the first transmit signal is latched to a first stage D flip flop using the signal as a clock (Fig. 9(e)). Further, an output of the first stage D flip flop is latched to a next stage D flip flop by the clock pulse extracted on the basis of the first transmit signal to obtain a demodulated data signal (Fig. 9(f)).

- the first and second transmit signals are directly inputted to the D flip flops and a logical gate of the data demodulating circuit 811.

- an adjusting circuit is actually required for adjusting a voltage level and a polarity from the first and second transmit signals to reproduce a signal.

- micro pulses are generated in the exclusive OR of the first and second transmit signals due to a skew between the signals, a filter circuit is actually required.

- an explanation thereof is omitted.

- the smoothing capacity 812 needs to be inserted into the internal power source to maintain the electric power of this block.

- a method for determining the capacity value of the smoothing capacity is basically the same as that described in the first embodiment. Thus, the explanation thereof is omitted.

- the related art employs a method for detecting the edge of the change point of the signal because of the data of a small amplitude signal, an erroneous demodulation may be possibly simply generated due to the variation of the internal source voltage due to the skew between the signals.

- the data signal is a total amplitude signal represented by the time position of the pulse signal on which the data signal is superimposed, a demodulation process can be performed by a logic circuit without requiring the edge detecting type demodulation method.

- data can be extracted without receiving the influence of internal power source noise due to a timing skew between two-wire transmit signals.

- the demodulating circuit of the data storage device can be more simply formed than the related art, merit is high in view of cost. Further, since the structure of the controller does not need ternary voltage values like the related art, an adjustment that takes unevenness in equivalent resistance of the data storage device into consideration is not necessary. Thus, a burden in design can be reduced.

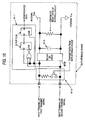

- Fig. 11 is a voltage wave form diagram showing a two-wire type data communication method according to a fifth embodiment of the present invention.

- Fig. 12 is a circuit diagram showing a structural example of a data demodulating circuit of a data storage device in a contact type data storage system using the two-wire type data communication method according to the fifth embodiment of the present invention.

- the two-wire type data communication method of this embodiment includes a first transmit signal (Fig. 11(a)) as a clock pulse in which a duty ratio is changed in accordance with the logic (Fig. 11(c)) of transmit data and a second transmit signal (Fig. 11(b)) as a clock pulse constantly having an opposite phase to that of the first transmit signal.

- the data storage device receiving the above-described transmit signals firstly forms internal operating voltage by a full-wave rectification of the first and second transmit signals and extracts an internal operating clock on the basis of the first transmit signal or the second transmit signal.

- a clock period t is maintained to a constant value. Accordingly, as long as the duty ratio is not set to an extreme value, the internal operating clock can be used.

- data is extracted by the data demodulating circuit having a time deciding function for extracting the change of the duty ratio.

- the rate of change of the duty ratio is set by taking a range of unevenness in time deciding function into consideration.

- the data storage device of this embodiment has the same structure, except the data demodulating circuit, as that of the data storage device shown in Fig. 2 that is described in the first embodiment. Thus, an explanation thereof is omitted.

- the data demodulating circuit in the data storage device of the embodiment shown in Fig. 12 includes a charging and discharging circuit 1001 for deciding time composed of a transistor switch turned on and off in accordance with the signal polarity of the second transmit signal, a resistance element and a capacity element, a comparator 1002 for comparing the output of the charging and discharging circuit with internal reference voltage and a second-stage D flip flop for latching the output by a clock pulse extracted on the basis of the first transmit signal.

- the transistor switch is turned on to charge the capacity element of the charging and discharging circuit 1001 from an internal VDD. At this time, the capacity element is charged to voltage near the internal VDD, so that the capacity element has the voltage higher than the internal reference voltage and the output of the comparator 1002 becomes "H".

- the time of change of the duty ratio of the clock pulse can be decided.

- the electric charge with which the capacity element is charged is discharged through the resistance element.

- the electric charge may be discharged by a transistor circuit in place of the resistance element.

- the output of the comparator 1002 is latched to the trailing edge of the first transmit signal by the D flip flop (Fig. 11(f)), and then, the output is latched by the leading edge of the first transmit signal to extract demodulated data shaped by time (Fig. 11(g)).

- the smoothing capacity of the internal power source of the data storage device may have a small capacity value.

- the related art employs a method for detecting the edge of the change point of the signal because of the data of a small amplitude signal, an erroneous demodulation may be possibly simply generated due to the variation of the internal source voltage due to the skew between the signals.

- the data signal is a total amplitude signal represented by the duty ratio of the clock pulse, a demodulation process can be performed by a logic circuit without requiring the edge detecting type demodulation method.

- data can be extracted without receiving the influence of internal power source noise due to a timing skew between two-wire transmit signals.

- the structure of the controller does not need ternary voltage values like the related art, an adjustment that takes unevenness in equivalent resistance of the data storage device into consideration is not necessary. Thus, a burden in design can be reduced.

- a stable two-wire communication can be realized in which the erroneous data demodulation is not generated due to the noise of the internal source voltage caused by the influence of the increase of a skew between the signals or the operation of the internal circuit of the data storage device.

- the demodulating circuit of the data storage device can be more simply formed than the related art, merit is high in view of cost.

- the structure of the controller does not need ternary voltage values like the related art, an adjustment that takes unevenness in equivalent resistance of the data storage device into consideration is not necessary. Thus, a burden in design can be reduced.

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Power Engineering (AREA)

- Dc Digital Transmission (AREA)

- Cable Transmission Systems, Equalization Of Radio And Reduction Of Echo (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003156584A JP4263023B2 (ja) | 2003-06-02 | 2003-06-02 | 2線式データ通信方法、システム、コントロール装置およびデータ記憶装置 |

| JP2003156584 | 2003-06-02 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| EP1484879A2 true EP1484879A2 (de) | 2004-12-08 |

| EP1484879A3 EP1484879A3 (de) | 2007-06-20 |

| EP1484879B1 EP1484879B1 (de) | 2016-05-11 |

Family

ID=33157134

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| EP04013011.4A Expired - Lifetime EP1484879B1 (de) | 2003-06-02 | 2004-06-02 | Zweidrahtdatenvermittlung |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7583734B2 (de) |

| EP (1) | EP1484879B1 (de) |

| JP (1) | JP4263023B2 (de) |

| KR (1) | KR20040103796A (de) |

| CN (1) | CN100531165C (de) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6159824A (en) * | 1997-05-12 | 2000-12-12 | Silicon Genesis Corporation | Silicon-on-silicon wafer bonding process using a thin film blister-separation method |

| US7363525B2 (en) * | 2004-10-07 | 2008-04-22 | Cisco Technology, Inc. | Bidirectional inline power port |

| US7664168B2 (en) | 2004-11-09 | 2010-02-16 | Canon Kabushiki Kaisha | Data carrier device, data carrier driving device, data communication system using data carrier driving device and data communication method |

| JP4250634B2 (ja) * | 2006-04-18 | 2009-04-08 | キヤノン株式会社 | データ通信装置、データ通信システム及びデータ通信方法 |

| JPWO2010004742A1 (ja) * | 2008-07-11 | 2011-12-22 | セイコーエプソン株式会社 | 液体容器、液体噴射装置、および、液体噴射システム |

| CN102089152A (zh) * | 2008-07-11 | 2011-06-08 | 精工爱普生株式会社 | 液体容器、液体喷射装置以及液体喷射系统 |

| US8427300B2 (en) | 2009-02-20 | 2013-04-23 | Redwood Systems, Inc. | Transmission of power and data with frequency modulation |

| US8207635B2 (en) * | 2009-02-20 | 2012-06-26 | Redwood Systems, Inc. | Digital switch communication |

| US8248230B2 (en) * | 2009-02-20 | 2012-08-21 | Redwood Systems, Inc. | Smart power device |

| RU2012132492A (ru) * | 2009-12-28 | 2014-02-10 | Золиекс Аб | Система для распределения электроэнергии и передачи данных |

| US20120198018A1 (en) * | 2011-01-27 | 2012-08-02 | Microsoft Corporation | Securely publishing data to network service |

| CN102387001A (zh) * | 2011-10-21 | 2012-03-21 | 中兴通讯股份有限公司 | 背板帧头传输方法及系统 |

| CN105471569B (zh) * | 2014-09-12 | 2018-10-26 | 株洲南车时代电气股份有限公司 | 多节点电流环全双工通信电路 |

| CN108370260B (zh) * | 2016-01-04 | 2021-04-30 | 日立汽车系统株式会社 | 电力线通信装置以及具备电力线通信装置的电子控制装置 |

| JP6939085B2 (ja) * | 2017-05-23 | 2021-09-22 | オムロン株式会社 | 通信装置、および通信システム |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5934031B2 (ja) | 1980-01-25 | 1984-08-20 | 誠一 宮崎 | デ−タ伝送方式 |

| JPS595763A (ja) | 1982-07-01 | 1984-01-12 | Hino Denshi Kk | 電力・信号伝送方式 |

| DE3751608T2 (de) * | 1986-09-01 | 1996-06-27 | Nippon Electric Co | Serielles Busschnittstellensystem zur Datenübertragung mit einer Zweidrahtleitung als Taktbus und Datenbus. |

| JPH01143435A (ja) | 1987-11-30 | 1989-06-06 | Nec Corp | データ伝送装置 |

| FR2707024B1 (de) * | 1993-06-22 | 1995-09-01 | Suisse Electronique Microtech | |

| NO951291L (no) * | 1995-04-04 | 1996-10-07 | Einar Gotaas | Fremgangsmåte og system for toveis datakommunikasjon mellom en sentralenhet og et antall stasjoner |

| US5898735A (en) * | 1995-10-06 | 1999-04-27 | Matsushita Electric Industrial Co., Ltd. | Circuit and method for signal transmission |

| US6351489B1 (en) * | 1996-09-30 | 2002-02-26 | Rosemount Inc. | Data bus communication technique for field instrument |

| DE19750317B4 (de) * | 1997-11-13 | 2006-06-14 | Sgs-Thomson Microelectronics Gmbh | Empfangsschaltung für ein CAN-System |

| EP0953936B1 (de) * | 1998-02-17 | 2001-05-09 | Infineon Technologies AG | Datenträger sowohl für den kontaktlosen als auch den kontaktbehafteten Betrieb |

| EP0993652B1 (de) * | 1998-05-05 | 2006-10-11 | Koninklijke Philips Electronics N.V. | Datenträger mit korrekturmöglichkeiten und verbesserter spannungsbegrenzungsmöglichkeit |

| US6384723B1 (en) * | 1998-11-02 | 2002-05-07 | Pittway Corporation | Digital communication system and method |

| CA2376971A1 (en) * | 2001-03-16 | 2002-09-16 | Silicon Image, Inc. | Combining a clock signal and a data signal |

| JPWO2002100058A1 (ja) | 2001-05-30 | 2004-09-24 | ザインエレクトロニクス株式会社 | 半導体集積回路及びデータ伝送システム |

| JP3519708B2 (ja) | 2001-08-24 | 2004-04-19 | 松下電器産業株式会社 | データ通信システム |

| US7113547B2 (en) | 2001-08-24 | 2006-09-26 | Matsushita Electric Industrial Co., Ltd. | Data communication system, controller device and data communication method |

-

2003

- 2003-06-02 JP JP2003156584A patent/JP4263023B2/ja not_active Expired - Fee Related

-

2004

- 2004-06-02 CN CNB2004100631560A patent/CN100531165C/zh not_active Expired - Fee Related

- 2004-06-02 KR KR1020040040088A patent/KR20040103796A/ko not_active Withdrawn

- 2004-06-02 US US10/858,388 patent/US7583734B2/en not_active Expired - Fee Related

- 2004-06-02 EP EP04013011.4A patent/EP1484879B1/de not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| EP1484879A3 (de) | 2007-06-20 |

| US7583734B2 (en) | 2009-09-01 |

| JP4263023B2 (ja) | 2009-05-13 |

| JP2004363684A (ja) | 2004-12-24 |

| EP1484879B1 (de) | 2016-05-11 |

| CN1574801A (zh) | 2005-02-02 |

| CN100531165C (zh) | 2009-08-19 |

| US20050008080A1 (en) | 2005-01-13 |

| KR20040103796A (ko) | 2004-12-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7583734B2 (en) | Two-wire type data communication method and system, controller and data recording apparatus | |

| US11509513B2 (en) | Amplitude-shift keying demodulation for wireless chargers | |

| US10714976B2 (en) | Wireless power receiver | |

| US7876150B2 (en) | ASK demodulator, communication module, communication device, and ASK demodulation method | |

| US10505396B2 (en) | Wireless power receiving apparatus | |

| CN101605114B (zh) | 解调器 | |

| US7734940B2 (en) | Data communication device has data signal generation circuit and transmission circuit on basis of reference voltage and received signal | |

| JP2011019373A (ja) | 復調回路、送電制御装置、送電装置、電子機器およびデータ復調方法 | |

| US9812894B2 (en) | Power switching circuit, semiconductor integrated circuit, radio apparatus, radio system, and power switching method | |

| US10944330B1 (en) | Self-biased gate driver architecture | |

| US7113547B2 (en) | Data communication system, controller device and data communication method | |

| JP6902846B2 (ja) | ワイヤレス受電装置、電子機器、fskが施された電力信号の復調方法 | |

| CN101019308A (zh) | 用于调幅信号的解调器 | |

| JP4692577B2 (ja) | 受信機 | |

| JP3519708B2 (ja) | データ通信システム | |

| US7664168B2 (en) | Data carrier device, data carrier driving device, data communication system using data carrier driving device and data communication method | |

| JP4430117B2 (ja) | データ記憶装置 | |

| JP2006135888A (ja) | データ通信装置、データ通信システム及びデータ通信方法 | |

| US8638894B2 (en) | Data communication apparatus, data communication system, and data communication method | |

| JP3523636B2 (ja) | データ通信システムおよびコントロール装置 | |

| JP3660914B2 (ja) | 信号検知回路 | |

| JP4533113B2 (ja) | データ通信装置及びデータ通信方法 | |

| US20050133603A1 (en) | Integrated circuit comprising a clock generator, a chip card comprising one such integrated circuit and the associated clock generation method | |

| JP2006173707A (ja) | データ通信回路 | |

| JP3899388B2 (ja) | 半導体集積回路装置及びicカード |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PUAI | Public reference made under article 153(3) epc to a published international application that has entered the european phase |

Free format text: ORIGINAL CODE: 0009012 |

|

| AK | Designated contracting states |

Kind code of ref document: A2 Designated state(s): AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HU IE IT LI LU MC NL PL PT RO SE SI SK TR |

|

| AX | Request for extension of the european patent |

Extension state: AL HR LT LV MK |

|

| PUAL | Search report despatched |

Free format text: ORIGINAL CODE: 0009013 |

|

| AK | Designated contracting states |

Kind code of ref document: A3 Designated state(s): AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HU IE IT LI LU MC NL PL PT RO SE SI SK TR |

|

| AX | Request for extension of the european patent |

Extension state: AL HR LT LV MK |

|

| RIC1 | Information provided on ipc code assigned before grant |

Ipc: H04L 25/02 20060101ALI20070515BHEP Ipc: H04L 25/08 20060101AFI20040930BHEP |

|

| 17P | Request for examination filed |

Effective date: 20071112 |

|

| AKX | Designation fees paid |

Designated state(s): DE FR GB IT NL |

|

| RAP1 | Party data changed (applicant data changed or rights of an application transferred) |

Owner name: PANASONIC CORPORATION |

|

| 17Q | First examination report despatched |

Effective date: 20100830 |

|

| RAP1 | Party data changed (applicant data changed or rights of an application transferred) |

Owner name: COLLABO INNOVATIONS, INC. |

|

| GRAP | Despatch of communication of intention to grant a patent |

Free format text: ORIGINAL CODE: EPIDOSNIGR1 |

|

| INTG | Intention to grant announced |

Effective date: 20151124 |

|

| GRAS | Grant fee paid |

Free format text: ORIGINAL CODE: EPIDOSNIGR3 |

|

| GRAA | (expected) grant |

Free format text: ORIGINAL CODE: 0009210 |

|

| AK | Designated contracting states |

Kind code of ref document: B1 Designated state(s): DE FR GB IT NL |

|

| REG | Reference to a national code |

Ref country code: GB Ref legal event code: FG4D |

|

| REG | Reference to a national code |

Ref country code: DE Ref legal event code: R096 Ref document number: 602004049267 Country of ref document: DE |

|

| REG | Reference to a national code |

Ref country code: NL Ref legal event code: MP Effective date: 20160511 |

|

| PG25 | Lapsed in a contracting state [announced via postgrant information from national office to epo] |

Ref country code: NL Free format text: LAPSE BECAUSE OF FAILURE TO SUBMIT A TRANSLATION OF THE DESCRIPTION OR TO PAY THE FEE WITHIN THE PRESCRIBED TIME-LIMIT Effective date: 20160511 |

|

| PG25 | Lapsed in a contracting state [announced via postgrant information from national office to epo] |

Ref country code: IT Free format text: LAPSE BECAUSE OF FAILURE TO SUBMIT A TRANSLATION OF THE DESCRIPTION OR TO PAY THE FEE WITHIN THE PRESCRIBED TIME-LIMIT Effective date: 20160511 |

|

| REG | Reference to a national code |

Ref country code: DE Ref legal event code: R119 Ref document number: 602004049267 Country of ref document: DE |

|

| PLBE | No opposition filed within time limit |

Free format text: ORIGINAL CODE: 0009261 |

|

| STAA | Information on the status of an ep patent application or granted ep patent |

Free format text: STATUS: NO OPPOSITION FILED WITHIN TIME LIMIT |

|

| REG | Reference to a national code |

Ref country code: FR Ref legal event code: ST Effective date: 20170228 |

|

| 26N | No opposition filed |

Effective date: 20170214 |

|

| GBPC | Gb: european patent ceased through non-payment of renewal fee |

Effective date: 20160811 |

|

| PG25 | Lapsed in a contracting state [announced via postgrant information from national office to epo] |

Ref country code: DE Free format text: LAPSE BECAUSE OF NON-PAYMENT OF DUE FEES Effective date: 20170103 Ref country code: FR Free format text: LAPSE BECAUSE OF NON-PAYMENT OF DUE FEES Effective date: 20160711 |

|

| PG25 | Lapsed in a contracting state [announced via postgrant information from national office to epo] |

Ref country code: GB Free format text: LAPSE BECAUSE OF NON-PAYMENT OF DUE FEES Effective date: 20160811 |