-

Technisches Gebiet

-

Verschiedene Ausführungsformen betreffen ein elektronisches Modul, das einen Fluid-Kühlkanal umfasst, und ein Verfahren zum Herstellen desselben.

-

Allgemeiner Stand der Technik

-

Auf dem Gebiet elektronischer Module finden eingebaute elektronische Chips breite Anwendung. Auf Grund des Gehäuses ist die von dem eingebauten elektronischen Chip erzeugte Abwärme oft ein begrenzender Faktor, sodass eine Kühlung vorgesehen werden muss. Oftmals werden so genannte Wärmesenken zum Abführen der Abwärme verwendet.

-

Aus der

WO 2012/ 076 552 A1 ist eine flüssigkeitsgekühlte Wärmesenke bekannt, die eine obere Platte mit einer Anordnung von gewundenen Flüssigkeitskanälen aufweist, wobei jeder Kanal einen separaten Kanaleinlass und einen gemeinsamen zentralen Auslasskanal hat. Die Wärmesenke weist weiterhin eine Bodenplatte mit einer Einlassöffnung und einer Auslassöffnung auf. Die Wärmesenke weist weiterhin eine Zwischenplatte mit Einlassführungskanälen auf, die Flüssigkeitsverbindung zwischen der Einlassöffnung der Bodenplatte und den Kanaleinlässen der oberen Platte bereitstellen, wobei die Zwischenplatte weiterhin einen Auslassführungskanal aufweist, der Flüssigkeitsverbindung zwischen dem gemeinsamen zentralen Auslasskanal der oberen Platte und der Auslassöffnung der Bodenplatte bereitstellt.

-

US 2014/0332950 A1 offenbart eine Halbleitervorrichtung mit einem Kühlteil, welches aus Keramik oder Harz gefertigt ist und eine Montageoberfläche aufweist, eine metallische Leiterplatte, welche auf der Montageoberfläche des Kühlteils montiert ist und eine Element-Montageoberfläche aufweist, und ein Halbleiterelement, welches auf der Element-Montageoberfläche der Leiterplatte montiert ist. Mindestens ein Teil der Leiterplatte, welcher der Element-Montageoberfläche entspricht, ist bezüglich des Kühlteils mit Harz bedeckt.

-

-

WINTRICH, A. [et al.]: Applikationshandbuch Leistungshalbleiter. Ilmenau : Verlag ISLE, 2010. S.73-74. - ISBN 978-3-938843-56-7 beschreiben die Vorteile von Sinterverbindungen.

-

DE 10 2009 002 519 A1 offenbart eine gekapselte Schaltungsvorrichtung für Substrate mit Absorptionsschicht zu wie Verfahren zur Herstellung derselben.

-

-

DE 31 28 457 A1 offenbart ein Kunststoffgekapseltes Halbleiterbauelement und Verfahren zum Herstellen eines Halbleiterbauelements mit Kunststoffgehäuse.

-

Zusammenfassung

-

Die beanspruchte Erfindung betrifft ein elektronisches Modul nach Anspruch 1 sowie ein Verfahren nach Anspruch 11.

-

Verschiedene Ausführungsformen sehen ein elektronisches Modul vor, umfassend einen Interposer, umfassend ein keramisches Material und einen Fluidkanal, der in dem keramischen Material ausgebildet ist, und eine metallische, strukturierte Schicht die zusammen mit dem keramischen Material gesintert ist; mindestens einen elektronischen Chip, der an der metallischen Schicht befestigt ist und in thermischem Kontakt mit dem Fluidkanal steht; eine Umverdrahtungsschicht zur Umverteilung elektrischer Kontakte in dem elektronischen Modul, wobei die Umverdrahtungsschicht auf dem mindestens einen elektronischen Chip angeordnet ist; eine gemoldete Kapselung, die mindestens teilweise um den mindestens einen elektronischen Chip herum ausgebildet ist, wobei die metallische, strukturierte Schicht direkt auf dem keramischen Material gebildet ist; wobei (i) die gemoldete Kapselung eine Oberflächenstruktur umfasst, die ausgeführt ist zum Befestigen des elektronischen Moduls an einer externen Struktur, oder (ii) das elektronische Modul ein Befestigungselement umfasst, eingebettet in die gemoldete Kapselung.

-

Des Weiteren, stellen verschiedene Ausführungsformen ein Verfahren zum Herstellen eines elektronischen Moduls bereit, wobei das Verfahren umfasst: Bereitstellen eines Interposers, umfassend ein keramisches Material und einen Fluidkanal, der in dem keramischen Material ausgebildet ist, und eine metallische, strukturierte Schicht, wobei die metallische, strukturierte Schicht direkt auf dem keramischen Material gebildet ist, und wobei metallische, strukturierte Schicht zusammen mit dem keramischen Material gesintert ist; Befestigen mindestens eines elektronischen Chips an der metallischen, strukturierten Schicht und in thermischem Kontakt mit dem Fluidkanal; Anordnen einer Umverdrahtungsschicht auf dem mindestens einen elektronischen Chip zur Umverteilung elektrischer Kontakte in dem elektronischen Modul; und Molden einer Kapselung mindestens teilweise um den mindestens einen elektronischen Chip herum; wobei (i) die gemoldete Kapselung eine Oberflächenstruktur umfasst, die ausgeführt ist zum Befestigen des elektronischen Moduls an einer externen Struktur, oder (ii) das elektronische Modul ein Befestigungselement umfasst, eingebettet in die gemoldete Kapselung.

-

Figurenliste

-

In den Zeichnungen beziehen sich gleiche Bezugszeichen im Allgemeinen über die verschiedenen Ansichten hinweg auf die gleichen Teile. Die Zeichnungen sind nicht notwendigerweise maßstabsgerecht. Stattdessen liegt der Schwerpunkt allgemein darauf, die Grundgedanken der Erfindung zu veranschaulichen. In der folgenden Beschreibung werden verschiedene Ausführungsformen unter Bezugnahme auf die folgenden Zeichnungen beschrieben, in welchen:

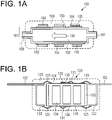

- 1A zeigt schematisch eine Querschnittsansicht eines elektronischen Moduls gemäß einer beispielhaften Ausführungsform;

- 1B zeigt schematisch eine Querschnittsansicht eines elektronischen Moduls gemäß einer beispielhaften Ausführungsform;

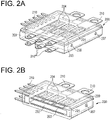

- 2A und 2B zeigen schematisch eine perspektivische Ansicht eines elektronischen Moduls gemäß einer beispielhaften Ausführungsform;

- 3 zeigt einen Ablaufplan eines Verfahrens zum Herstellen eines elektronischen Moduls gemäß einer beispielhaften Ausführungsform;

- 4A bis 4F zeigen schematische perspektivische Ansichten, die verschiedene Schritte eines Herstellungsverfahrens gemäß einer beispielhaften Ausführungsform darstellen; und

- 5A bis 5F zeigen schematische perspektivische Ansichten, die verschiedene Schritte eines Herstellungsverfahrens gemäß einer weiteren beispielhaften Ausführungsform darstellen.

-

Detaillierte Beschreibung

-

Im Folgenden werden weitere Ausführungsbeispiele eines elektronischen Moduls und eines Verfahrens zum Herstellen eines elektronischen Moduls beschrieben. Es sollte beachtet werden, dass die Beschreibung bestimmter Merkmale, die im Kontext eines bestimmten Ausführungsbeispiels beschrieben werden, auch mit anderen Ausführungsbeispielen kombiniert werden kann.

-

Das Wort „beispielhaft“ wird hierin im Sinne von „als ein Beispiel, Fallbeispiel, oder der Veranschaulichung dienend“ verwendet. Jede hierin als „beispielhaft“ beschriebene Ausführungsform oder Gestaltungsform ist nicht notwendigerweise als bevorzugt oder vorteilhaft gegenüber anderen Ausführungsformen oder Gestaltungsformen zu verstehen.

-

Verschiedene Ausführungsformen stellen ein elektronisches Modul bereit, insbesondere ein elektronisches Leistungsmodul, umfassend einen Interposer, umfassend einen Körper gebildet aus einem elektrisch isolierenden Material und mit mindestens einem Fluidkanal darin eingebettet und eine elektrisch leitfähige strukturierte Schicht direkt darauf gebildet. An der elektrisch leitfähigen strukturierten Schicht des Interposers sind mindestens ein oder eine Mehrzahl von elektronischen Chips oder Halbleiterchips befestigt, beispielsweise mittels Bonden(Kupfer oder Aluminium zum Beispiel), Löten, entweder direkt oder indirekt. Der mindestens eine elektronische Chip ist in thermischen Kontakt mit dem Fluidkanal, sodass von dem mindestens einen elektronischen Chip erzeugte Wärme abgeführt oder abgeleitet werden kann. Des Weiteren ist der mindestens eine elektronische Chip mindestens teilweise von einer gemoldeten Kapselung umhüllt.

-

Insbesondere, nur ein Fluidkanal kann in dem Interposer bereitgestellt werden und kann eine gewundene Form oder Gestalt haben oder kann eine einzelne Vertiefung oder ein einzelner Hohlraum sein. Insbesondere, der Fluidkanal kann direkt in einem Körper des Interposers ausgebildet sein und kein anderes Element oder Einheit bilden, die an dem Interposer befestigt ist. Das heißt, Wände (Seitenwände und/oder untere und/oder obere Wände die den Fluidkanal definieren, können ein Teil des Interposers sein, insbesondere des Körpers des Interposers, der aus einen elektrisch isolierenden Material gebildet ist. Des Weiteren sollte erwähnt werden, dass eine Mehrzahl von Interposern übereinander gestapelt werden kann. Insbesondere, das elektronische Modul kann einen Stapel von mehreren Interposern umfassen oder selbst eine Mehrzahl von elektronischen Modulen kann übereinander gestapelt werden.

-

Es ist anzumerken, dass im Prinzip keine Begrenzungen bezüglich der verwendeten elektronischen Chips oder Halbleiterchips gegeben ist, z.B. bezüglich der verwendeten Halbleitermaterialien (wie beispielsweise Galliumnitrid (GaN) oder Siliziumcarbid (SiC)). Dies kann so sein, da die elektronischen Chips in die gemoldete Kapselung eingebettet sein können und weiterhin der Fluidkanal in einem elektrisch isolierenden Basismaterial gebildet sein kann, welches den elektronischen Chip vor einem direkten Kontakt mit dem Kühlfluid schützt. Des Weiteren kann das elektronische Modul eine Mehrzahl von elektronischen Chips oder Mikroplättchen umfassen.

-

Aufgrund der hohen Wärmekapazität oder Wärmeleitfähigkeit des (Kühl-)Fluids kann es selbst möglich sein, Hochleistungselektronikchips in kleinen gekapselten elektronischen Modulen oder Paketen anzuwenden, sodass eine hohe Leistungsdichte erreicht werden kann. Alternativ kann die Effizienz des gesamten elektronischen Moduls erhöht werden aufgrund der Möglichkeit, zu höherer Leistung umzuschalten. Die gemoldete Kapselung kann auch einen verbesserten Schutz gegen mechanische Belastung oder Bruch im Vergleich zu keramischen und/oder Metallgehäusen bieten.

-

Insbesondere, ist anzumerken, dass die gemoldete Kapselung direkt auf dem Interposer gebildet wird und von einem vorgefertigten Gehäuse, das anschließend um einen elektronischen Chip herum angeordnet wird, unterschieden werden muss. Zum Beispiel kann die gemoldete Kapselung den äußeren Umfang oder Silhouette des elektronischen Moduls definieren. Insbesondere, können Formmaterialien, die hohen Temperaturen widerstehen, verwendet werden. Zum Beispiel können typische Formmassen wie Epoxidharz, Bismaleimid, Polyimid, Cyanester oder dergleichen verwendet werden. Des Weiteren können Füllmaterialien in der Einkapselung oder dem Kapselungsmaterial, z. B. Epoxid und/oder Silikon enthalten sein.

-

Insbesondere kann das elektronische Modul ein elektronisches Leistungsmodul sein. Zum Beispiel kann der mindestens eine elektronische Chip ein (Leistungs-)Transistor, eine (Leistungs-) Diode oder jegliche andere Art von elektronischem Chip oder Mikroplättchen sein.

-

Es ist anzumerken, dass keine zusätzlichen, z.B. organische, Zwischenschichten notwendig sein können, um den mindestens einen elektronischen Chip an dem Interposer zu befestigen, oder um den oder die elektronischen Chips thermisch mit dem Kühlelement des Fluidkanals und insbesondere mit einer elektrisch leitfähigen strukturierten Schicht zu verbinden. Solche organischen Schichten werden oft in üblichen (verpackten) elektronischen Modulen verwendet. Die Möglichkeit, eine solche organische Schicht wegzulassen, ist jedoch hilfreich, um die Leistung zu erhöhen, da solche organischen Schichten oftmals große Variationen bezüglich thermischer Leitfähigkeit bewirken können, hohen thermischen Widerstand, der die Lebensdauer des elektronischen Moduls limitieren kann, bewirken können, und/oder das für das elektronische Modul notwendige Volumen vergrößern können. Während solche organischen Schichten anfangs gute Leistungen zeigen können, altern diese oftmals recht schnell, was zu einer erhöhten Geschwindigkeit der Zersetzung über die Zeit (zunehmender Widerstand führt zu einer zunehmenden Wärmeentwicklung, die wiederum führt zu einem zunehmenden Widerstand usw.) führt. Dieser Alterungsprozess kann in den Fällen, in denen „Hochtemperatur“ Halbleiter (wie beispielsweise Galiumnitrid (GaN) oder Siliziumcarbid (SiC) verwendet werden können, selbst noch bedeutender sein. Insbesondere, nur eine zusätzliche Verbindungsschicht kann zwischen den Interposer und den elektronischen Chip angeordnet werden.

-

Die metallische strukturierte Schicht ist eine elektrisch leitfähige Schicht, die durch einen subtraktiven Prozess, wie Ätzen, strukturiert worden sein kann. Des Weiteren kann die elektrisch leitfähige strukturierte Schicht direkt auf das isolierende Material gedruckt werden, z.B. mittels Drucken einer Kupferschicht auf das isolierende Material. In dem Fall eines keramischen Materials als ein Basismaterial des Interposers, kann das keramische Material den Fluidkanal bilden oder definieren. Demzufolge kann das elektrisch leitende Material, das die strukturierte Schicht bildet, mittels des keramischen Materials von dem Fluidkanal elektrisch isoliert sein.

-

Aufgrund der guten wärmeabführenden Fähigkeiten des Fluids, beispielsweise Wasser, Öl, isolierende Flüssigkeiten, Gase oder Luft, kann es möglich sein, sehr kompakte elektronische Module für eine bestimmte Leistung, z.B. Leistungskapazität, bereitgestellt werden. Das heißt, die Leistungskapazität pro Volumen (welche beispielsweise ein begrenzender Faktor in dem Automobilsektor ist) kann erhöht werden. Insbesondere kann die Temperatur des elektronischen Moduls auf einem niedrigeren Niveau gehalten werden, was die Effizienz des elektronischen Moduls erhöhen kann. Das Erhöhen der Effizienz wiederum kann ermöglichen, dass die Anzahl der notwendigen elektronischen Module für eine bestimmte Anwendung verringert werden kann. Zusätzlich kann es möglich sein, die von dem Kühlfluid abgeführte Wärmeenergie für andere Zwecke zu verwenden. Zum Beispiel, in dem Fall eines elektrischen Autos, wo so ein Modul verwendet wird, könnte die Abwärme zum Heizen des Autos oder der Batterie im Winter oder zu ähnlichem verwendet werden.

-

Des Weiteren können Begrenzungen des Materials, das für die Kapselung verwendet wird, gelockert werden, aufgrund der Tatsache, dass die Wärme über das Fluid abgeführt wird. Demzufolge mögen keine wärmeleitenden Bereiche zum Erhöhen der Wärmekapazität und/oder Wärmeleitfähigkeit, wie beispielsweise eine Metallplatte oder ähnliches, zum thermischen Kontakt zwischen dem elektronischen Modul und einer umgebenden Umgebung, in der das elektronische Modul verwendet wird oder in der es befestigt ist, notwendig sein. Es sollte jedoch erwähnt werden, dass ein zusätzlicher wärmeleitender oder wärmeabführender Weg vorgesehen sein kann, z. B. über einen Leadframe oder wärmeleitende Abstandshalter, die auf oder in thermischem Kontakt mit der Vorderseite und/oder Rückseite des elektronischen Chips angeordnet sind. Solch eine umgebende Umgebung kann ein Automobil oder ähnliches sein, wo (leistungs-)elektronische Module verwendet werden können.

-

Des Weiteren kann das den (Kühl-)Fluidkanal aufweisende elektronische Modul möglicher Weise vorteilhaft in Umgebungen oder Anwendungen verwendet werden, wo bereits ein Fluidkühlsystem verwendet wird, an das der Fluidkanal eventuell einfach angeschlossen werden kann. Daher kann es sein, dass keine extra Pumpe zum Pumpen des Fluids durch den Fluidkanal notwendig ist. Alternativ oder zusätzlich kann jedoch eine Pumpe, die spezifisch für das Fluid des Fluidkanals in dem Interposer bestimmt ist, vorgesehen sein.

-

Durch Bereitstellen eines elektronischen Moduls, der eine Fluidkühlung aufweist und von einer Gussform umhüllt wird, kann ein kompaktes Modul mit einer geringen Komplexität bereitgestellt werden. Insbesondere werden, wenn solch ein Modul verwendet wird, einige der Funktionen (z.B. Kühlfunktion), die typischer Weise von der Anwendung, in der das Modul verwendet wird, ausgeführt oder erledigt werden, von dem Modul übernommen. Zum Beispiel, in dem Fall, dass solch ein Modul in dem Automobilbereich verwendet wird, muss der Hersteller des Autos sich nicht um die wärmeableitenden Elemente und/oder isolierende Elemente kümmern (abgesehen von dem Bereitstellen und Abführen des Kühlfluids. Zu einem gewissen Grad ist der elektronische Modul einem „Plug und Play“-Modul ähnlich.

-

Im Folgenden sind beispielhafte Ausführungsformen des elektronischen Moduls beschrieben. Die Merkmale und Elemente, welche in Hinblick auf diese Ausführungsformen beschrieben werden, können jedoch mit Ausführungsbeispielen der Verfahren zum Herstellen eines elektronischen Moduls kombiniert werden.

-

Der Interposer umfasst ein keramisches Material.

-

Insbesondere kann das keramische Material (wie Aluminiumoxid, Aluminiumnitrid, Siliziumnitrid, Aluminiumtitanat, Zirkoniumoxid oder Silikat) ein Basismaterial des Interposers sein. Zum Beispiel kann der Fluidkanal von dem keramischen Material gebildet oder definiert werden. Das heißt, die Wände des Fluidkanals können von dem keramischen Material gebildet werden. Vorzugsweise ist das keramische Material ein elektrisch isolierendes Material. Insbesondere kann das keramische Material ein sinterbares Material sein.

-

Gemäß einer beispielhaften Ausführungsform des elektronischen Moduls ist das keramische Material gesintert.

-

Gemäß einer beispielhaften Ausführungsform des elektronischen Moduls ist die elektrisch leitfähige, metallische strukturierte Schicht zusammen mit dem keramischen Material gesintert.

-

Insbesondere kann das Metall Kupfer sein. Zum Beispiel kann eine Kupferfolie befestigt werden, die dann mittels Ätzen strukturiert wird und dann anschließend verbunden wird. Alternativ kann die metallische strukturierte Schicht gedruckt werden (unter Verwendung einer metallischen Paste) und anschließend gesintert werden. Ein weiterer alternativer Prozess kann das Verwenden von 3D „Drucken“ oder Erzeugungstechnik sein, z.B. Verwenden eines Lasers, um leitende Strukturen (die ebenso bereits von dem Laser gesintert sein können) direkt von einem metallischen Pulver zu bilden. Durch das Sintern des metallischen Materials zusammen mit dem keramischen Material, zeigt eine Verbindung oder Fuge zwischen den beiden Materialien eine große Stärke, d.h. beide Materialien können mit einer großen Adhäsionskraft zusammenhalten. Im Prinzip können beide Komponenten hinterher ein einzelnes Gemisch oder einen einzelnen Verbund bilden.

-

Es ist anzumerken, dass natürlich zusätzliche Schichten oder Verfeinerungsschichten auf der metallischen strukturierten Schicht abgelagert oder angeordnet werden können. Zum Beispiel können eine Nickelschicht, eine Palladiumschicht, eine Silberschicht, Goldschicht und/oder Wolframschicht beispielsweise unter Verwendung eines stromlosen Abscheidungsprozesses abgelagert werden.

-

Des Weiteren kann es möglich sein, eine strukturierte Schicht mit einer Porengröße von etwa 5 Mikrometer bis 30 Mikrometer bereitzustellen. Solch eine Porengröße kann geeignet sein zum Minimieren mechanischer Spannungen, z.B. zwischen dem aktiven elektronischen Gerät oder Chip und der Kupferschicht des Interposers aufgrund von Temperaturveränderungen (z.B. während eines Leistungszyklus). Daher kann das elektronische Modul eine erhöhte Zuverlässigkeit und/oder eine erhöhte Lebensdauer aufweisen.

-

Gemäß einer beispielhaften Ausführungsform umfasst das elektronische Modul weiterhin einen weiteren elektronischen Chip, wobei der mindestens eine elektronische Chip auf einer ersten Hauptfläche des Interposers angeordnet ist und der weitere elektronische Chip auf einer zweiten Hauptfläche des Interposers angeordnet ist.

-

Insbesondere können die erste Hauptfläche und die zweite Hauptfläche sich auf gegenüberliegenden Seiten des Interposers befinden. Es ist anzumerken, dass für jede Hauptfläche eine separate elektrisch leitfähige strukturierte Schicht und/oder Leadframe bereitgestellt werden kann. Das heißt, dass der Interposer eine weitere elektrisch leitfähige strukturierte Schicht umfassen kann (eine für jede Hauptfläche). Des Weiteren können auch auf anderen Seiten oder Oberflächen zusätzliche elektrisch leitfähige strukturierte Schichten vorgesehen sein.

-

Es ist anzumerken, dass natürlich eine Mehrzahl von elektronischen Chips auf einer oder jeder der Hauptflächen oder strukturierten Schichten angeordnet sein kann. Es ist anzumerken, dass die elektronischen Chips von verschiedenen Typen oder vom gleichen Typ sein können. Zum Beispiel können einige Chips Leistungstransistoren oder Leistungsdioden sein, während andere elektronische Chips logische Komponenten umfassen, wie Treiber (z.B. Gate-Treiber), beispielsweise ausgeführt zum Steuern des elektronischen Moduls oder Teilen dessen.

-

Gemäß einer beispielhaften Ausführungsform des elektronischen Moduls wird der mindestens eine elektronische Chip mittels eines Sinterprozesses an der elektrisch leitfähigen strukturierten Schicht befestigt ist.

-

Zum Beispiel kann das Befestigen mittels eines drucklosen Sinterprozesses basierend auf einer spezifischen Paste für einen solchen drucklosen Sinterprozess ausgeführt werden. Der elektronische Chip kann direkt mit dem Interposer oder Chipträger verbunden werden. Zum Beispiel kann die elektrisch leitfähige strukturierte Schicht eine Kupfer- oder Silberschicht sein. Alternativ oder zusätzlich kann das Befestigen unter Verwendung eine (jeden geeigneten) Haftmaterials oder -schicht und/oder Lötprozess, z.B. Diffusionslöten ausgeführt werden.

-

Gemäß einer beispielhaften Ausführungsform umfasst das elektronische Modul weiterhin einen externen elektrischen Kontakt, der mit der elektrisch leitfähigen strukturierten Schicht verbunden ist und teilweise in die gemoldete Kapselung eingebettet ist.

-

Solch ein externer elektrischer Kontakt kann ein Leadframe oder Leiterstift oder ähnliches sein. Ein Leadframe kann außerdem (abgesehen vom Bereitstellen elektrischer Verbindung für das elektronische Modul)zum Handhaben und Umhüllen des elektronischen Moduls verwendet werden. Es ist jedoch anzumerken, dass der externe elektrische Kontakt an die elektrisch leitfähige strukturierte Schicht gelötet werden kann und möglicher Weise (teilweise) frei von Material der gemoldeten Kapselung gehalten werden kann.

-

Gemäß einer beispielhaften Ausführungsform des elektronischen Moduls ist die elektrisch leitfähige strukturierte Schicht mit dem externen elektrischen Kontakt durch einen Verbindungsprozess verbunden, der ausgewählt ist aus der Gruppe bestehend aus: Drahtbonden; Clipbonden; Laserschweißen; Löten; Widerstandsschweißen; und Ultraschallschweißen.

-

Insbesondere, können Kupferdrähte und/oder Aluminiumdrähte und/oder Golddrähte und/oder Silberdrähte für das Drahtbonden verwendet werden. Eine so verbundene Verbindung kann auch für eine (kleine) weitere Thermische Verbindung mit externen Strukturen oder der Umgebung über den Leadframe vorgesehen werden. Die Menge an (Abwärme) Wärmeenergie, die über diesen weiteren thermischen Weg abgeführt wird, kann von den Abmessungen (oder Größe) des Leadframes und der Verbindung abhängen. Zum Beispiel, die Verbindungsstrukturen, der Leadframe und/oder die strukturierte Schicht können jeweils Abschnitte unterschiedlicher Abmessungen oder Dimensionierung umfassen. Zum Beispiel, einige Abschnitte oder Bereiche können von relativ dicken und/oder breiten Strukturen gebildet werden, sodass eher hohe elektrische Ströme übertragbar sind. Zusätzlich können andere Abschnitte von relativ dünnen und/oder schmalen Strukturen gebildet werden und überwiegend für geringe Ströme, z.B. logische Signale, verwendet werden.

-

Gemäß einer beispielhaften Ausführungsform des elektronischen Moduls umfasst die gemoldete Kapselung Oberflächenstrukturen, die ausgeführt sind zum Anbringen oder Befestigen des elektronischen Moduls an einer externen Struktur.

-

Insbesondere können ein oder mehrere Oberflächenstrukturen an einem äußeren Umfang der gemoldeten Kapselung gebildet oder vorgesehen sein. Solch eine Oberflächenstruktur kann insbesondere eine einfache Befestigung oder Anbringung der gemoldeten Kapselung an externen Strukturen ermöglichen. In diesem Zusammenhang kann das Verwenden einer gemoldeten Kapselung (die den äußeren Umfang des elektronischen Moduls bildet) besonders hilfreich sein, um eine große Vielfalt von Gestalten oder Formen ausgebildet für sehr verschiedene externe Strukturen bereitzustellen. Insbesondere kann das Verwenden solcher Oberflächen- oder Befestigungsstrukturen den Vorteil haben, dass kein außergewöhnlicher Druck angewandt werden muss, wenn das elektronische Modul an den externen Strukturen befestigt wird.

-

Insbesondere kann das Verwenden eines Fluid-Kühlkanals oder - röhre ermöglichen, das elektronische Modul an jedem gewünschten Punkt der externen Strukturen anzubringen, insbesondere, da es nicht notwendig sein mag, guten thermischen Kontakt zu der externen Struktur an dem Punkt des Anbringens oder Befestigens vorzusehen (z.B. durch Verwenden einer großen Kontaktfläche zwischen dem elektronischen Modul und der externen Struktur und/oder durch bereitstellen eines Materials mit einer hohen thermischen Leitfähigkeit).

-

Gemäß einer beispielhaften Ausführungsform des elektronischen Moduls hat die Oberflächenstruktur eine Form hat, ausgewählt aus der Gruppe bestehend aus: Rille; Zunge; Schraubenloch; Niet; Schraube; und Aussparung.

-

Im Allgemeinen kann die Oberflächenstruktur jede Form haben, die geeignet ist zum Bereitstellen einer Form oder einer positiven Passung mit einer passenden oder ergänzenden Oberflächenstruktur, ausgebildet in oder an einer externen Struktur oder Element, an dem das elektronische Modul befestigt werden soll. Solche Oberflächenstrukturen können relativ einfach gebildet werden, wenn eine Formmasse für die Kapselung verwendet wird, da typische Formmassen oder Materialien bruchfester als keramische Verbindungen sein können, die manchmal als Materialien zum Herstellen von Gehäusen für allgemein bekannte elektronische Module verwendet werden. Selbst in dem Fall, das der Interposer keramisches Material umfasst oder im Wesentlichen aus keramischen Material besteht, kann dieses keramische Material von der Kapselung, die von einer Formmasse gebildet wird geschützt werden, anstelle eines keramischen Gehäuses.

-

Gemäß einer beispielhaften Ausführungsform umfasst das Modul weiterhin ein in die gemoldete Kapselung eingebettetes Befestigungselement.

-

Insbesondere kann das Befestigungselement eine Mutter Schraube oder dergleichen sein, die in die gemoldete Kapselung eingebettet ist und die ausgeführt sein kann, um an einem komplementären Befestigungselement außerhalb des elektronischen Moduls befestigt oder angebracht werden zu können.

-

Gemäß einer beispielhaften Ausführungsform des elektronischen Moduls umfasst der Fluidkanal ein Eingangsterminal und ein Ausgangsterminal.

-

Insbesondere können das Eingangsterminal und das Ausgangsterminal mit einem Fluidkanal, der sich außerhalb des elektronischen Moduls befindet, verbindbar sein. Das Eingangsterminal und/oder Ausgangsterminal kann aus einem anderen Material bestehen als ein Basismaterial des Interposers. Somit kann der Fluidkanal mit einer externen Wärmesenke oder Wärmeabführelement verbindbar sein.

-

Insbesondere kann der Fluidkanal möglicher Weise über das Eingangsterminal und Ausgangsterminal im Wesentlichen der einzige Wärmeabführkanal oder -weg für (Abwärme) in dem elektronischen Modul, z.B. in dem elektronischen (Leistungs-) Chip, erzeugten Wärme sein. Demzufolge kann es möglich sein, dass ein äußerer Umfang der gemoldeten Kapselung frei von jeglichen Gebieten oder Strukturen (außer den Eingangs- und Ausgangsterminals) sein, die dazu dienen, Wärme zu einer externen Struktur zu leiten.

-

Zum Beispiel, mag keine metallische (z.B. Kupfer) Kontaktfläche außerhalb der gemoldeten Kapselung gebildet werden. Insbesondere kann die gemoldete Kapselung eine eher geringe thermische Leitfähigkeit aufweisen oder es ist mindestens keine Begrenzung bezüglich der Wärmeleitfähigkeit des Formmaterials vorgegeben. Insbesondere sind für den gesamten Interposer nur in Eingangsterminal und ein Ausgangsterminal vorgesehen. Daher kann eine Verbindung mit einer externen Struktur vereinfacht werden.

-

Gemäß einer beispielhaften Ausführungsform des elektronischen Moduls ist der mindestens eine elektronische Chip einer aus der Gruppe bestehend aus: Leistungstransistor; Leistungsdiode; und Logikkomponenten. Insbesondere kann die Logikkomponente einen Logik-Chip, beispielsweise einen (Gate-) Treiber, umfassen oder von diesem gebildet werden.

-

Gemäß einer beispielhaften Ausführungsform umfasst das elektronische Modul weiterhin eine passive elektrische Komponente, die mindestens teilweise in die gemoldete Kapselung eingebettet ist.

-

Insbesondere kann die passive elektrische Komponente eine Spule, ein Widerstand oder eine Kapazität sein. Die passive elektrische Komponente kann auch an der elektrisch leitfähigen strukturierten Schicht befestigt sein oder mit dieser verbunden sein.

-

Gemäß einer beispielhaften Ausführungsform des elektronischen Moduls kann die elektrisch leitfähige strukturierte Schicht Abschnitte verschiedener Abmessungen umfassen.

-

Insbesondere kann die elektrisch leitfähige strukturierte Schicht Abschnitte relativ dünner und/oder schmaler Strukturen aufweisen. Diese Abschnitte können geeignet sein zum Leiten relativ geringer Ströme, wie sie für Logiksignale verwendet werden. Andere Abschnitte können eine relativ große Dicke und/oder breite Strukturen aufweisen. Diese Abschnitte können geeignet sein zum Leiten höherer Ströme.

-

Gemäß einer beispielhaften Ausführungsform des elektronischen Moduls umfasst die Kapselung eine Einkapselung und ein Füllmaterial.

-

Insbesondere kann das Füllmaterial aus Oxiden, wie beispielsweise Siliziumoxid oder Aluminiumoxid, oder aus Nitriden, wie beispielsweise Aluminiumnitrid oder Bornitrid, bestehen. Durch Einbeziehen solcher Füller in das (Basis-)Kapselungsmaterial oder die Einkapselung kann es möglich sein, eine Kapselung bereitzustellen, die auch als ein weiterer wärmeleitender Weg für die Ableitung von (Abwärme) Wärmeenergie fungiert. Zum Beispiel kann eine solche Kapselung wirksam sein beim Reduzieren von Wärmespitzen, die während des Betriebs des mindestens einen elektronischen Chips auftreten.

-

Gemäß einer beispielhaften Ausführungsform umfasst das elektronische Modul weiterhin eine Umverdrahtungsschicht.

-

Insbesondere kann die (galvanische) Umverdrahtungsschicht auf dem mindestens einen elektronischen Chip oder vorzugsweise auf einer Mehrzahl von elektronischen Chips angeordnet sein und kann zur Umverteilung elektrischer Kontakte oder Terminals in dem elektronischen Modul, z.B. von elektrischen Terminals des elektronischen Chips, verwendet werden. Insbesondere kann eine solche Umverdrahtungsschicht hilfreich sein im Fall, dass eine Mehrzahl von elektronischen Chips parallel verarbeitet wird, z.B. in einem so genannten Paneel oder Mehrfachblock, was die Produktionskosten verringern kann. In dem Paneel oder Mehrfachblock können die elektronischen Chips in einer Anordnung angeordnet sein, die von einer ersten oder inneren Kapselung umhüllt sein können, z.B. gebildet von einer Gussform, Laminaten, Glas, Kunststoff oder Keramikverbund.

-

Insbesondere kann das elektronische Modul zwei Schichten Kapselungsmaterial aufweisen, d.h. eine innere und eine äußere Kapselung, wobei das äußere Kapselungsmaterial das sein kann, das von einer Formmasse (z.B. Silizium oder Epoxid) gebildet wird, während das Innere von einem Gussformverbund, z.B. Keramik, Glas, Kunststoffmaterial, Laminaten oder Ähnlichem, gebildet sein kann. Auf oder in der inneren Kapselungsschicht können eine Metallisierungsschicht und/oder Durchkontaktierungen ausgebildet sein, auf denen zusätzlich eine Lötresistschicht ausgebildet sein.

-

Im Folgenden werden beispielhafte Ausführungsformen des Verfahrens zum Herstellen eines elektronischen Moduls beschrieben. Die Merkmale und Elemente, welche in Hinblick auf diese Ausführungsformen beschrieben werden, können jedoch auch mit beispielhaften Ausführungsformen des elektronischen Moduls kombiniert werden.

-

Gemäß einer beispielhaften Ausführungsform des Verfahrens des Moldens der Kapselung umfasst das Bilden von Oberflächenstrukturen ausgeführt, um an externen Strukturen befestigt zu werden.

-

Gemäß einer beispielhaften Ausführungsform des Verfahrens wird eine Mehrzahl von elektronischen Chips an der elektrisch leitfähigen strukturierten Schicht befestigt und das Verfahren umfasst weiterhin Bilden einer inneren Kapselung um die Mehrzahl der elektronischen Chips herum.

-

Insbesondere kann die Mehrzahl von elektronischen Chips eine Anordnung bilden und die innere Kapselungsschicht kann eine Kapselung der Anordnung bilden. Somit kann eine Art Paneel oder Mehrfachblock gebildet werden, welche nachfolgend chargenweise weiter verarbeitet werden kann, z.B. Mittels Anordnen oder Kontaktieren einer (galvanischen) Umverdrahtungsschicht und/oder einer Lötresistschicht, bevor ein Vereinzelungsschritt ausgeführt werden kann, um das Paneel oder den Mehrfachblock zu teilen oder zu vereinzeln und dabei eine Mehrzahl von rohen elektronischen Modulen zu bilden, die dann weiter verarbeitet werden können (z.B. durch Anbringen eines Leadframes und/oder Bilden einer äußeren Kapselung darauf), um so das elektronische Modul herzustellen. Es ist anzumerken, dass einige oder alle der (rohen) elektronischen Module eine Mehrzahl von elektronischen Chips oder Dies aufweisen können.

-

Es ist anzumerken, dass die innere Kapselung nicht nur um die Mehrzahl von elektronischen Chips herum gebildet werden kann (z.B. zum Bilden eines Paneels oder Mehrfachblockes), die nachfolgend vereinzelt werden, um eine Mehrzahl von elektronischen Modulen zu bilden, sondern diese kann auch um ein einzelnes elektronisches Modul oder einen einzelnen Interposer, der anschließend ein einzelnes elektronische Modul bilden soll, herum gebildet werden.

-

Gemäß einer beispielhaften Ausführungsform des Verfahrens ist eine Mehrzahl von elektronischen Chips auf der elektrisch leitfähigen strukturierten Schicht befestigt und das Verfahren umfasst weiterhin Anordnen einer Umverdrahtungsschicht in elektrischem Kontakt mit der Mehrzahl von elektronischen Chips.

-

Insbesondere kann die (galvanische) Umverdrahtungsschicht auf einer inneren oder Paneelkapselung, die die Mehrzahl der elektronischen Chips umhüllt, angeordnet sein. Zusätzliche weitere Schritte, wie beispielsweise Formen einer Lötresistschicht auf der Umverdrahtungsschicht und/oder ein Vereinzelungsschritt des Paneels oder einer Mehrzahl von rohen elektronischen Modulen, können ausgeführt werden. Nach dem Vereinzelungsschritt kann ein Leadframe oder eine andere (Träger-) Struktur auf dem vereinzelten elektronischen Modul befestigt werden. Nach dem Formungsprozess kann das Bilden der gemoldeten oder äußeren Kapselung ausgeführt werden.

-

Im Folgenden werden bestimmte Ausführungsformen des elektronischen Moduls und des Verfahrens zum Herstellen eines elektronischen Moduls in Hinblick auf die Figuren ausführlicher beschrieben. Einige der beschriebenen Ausführungsformen können eine der folgenden Wirkungen oder Vorteile aufweisen. Insbesondere können sie eine hocheffiziente und/oder robuste Kühlung elektronischer Leistungsmodule bereitstellen. Die elektronischen Module oder Pakete können einfach an externen Strukturen befestigt werden und/oder können platzsparende Lösungen bieten. Im Prinzip mögen keine begrenzenden organischen Materialien oder Schichten notwendig sein, um eine gute Wärmeableitung oder -abfuhr zu ermöglichen. Die elektronischen Module können eine einfache und gut definierte Schnittstelle für Anwendungen, in denen diese verwendet werden, und/oder gut definierte Betriebs- und Leistungsparameter bereitstellen.

-

1A zeigt schematisch eine Querschnittsansicht eines elektronischen Moduls 100 gemäß einer beispielhaften Ausführungsform. Insbesondere umfasst das elektronische Modul 100 einen aus einem keramischen Material ausgebildeten Interposer 101 und einschließend einen darin ausgebildeten Fluidkanal 102. Des Weiteren ist eine elektrisch leitfähige strukturierte Schicht 103, z.B. aus Kupfer, direkt auf dem Körper des Interposers 101 ausgebildet (z.B. gedruckt oder gesintert). Zum Beispiel kann eine Kupferschicht oder Folie auf das keramische Material gedruckt sein und kann dann nachfolgend mittels eines Ätzprozesses strukturiert werden.

-

Alternativ kann der Form „erzeugende“ Prozess (z.B. 3D Drucken), wie Laserdrucken, ausgeführt werden, um die strukturierte Schicht zu bilden. Darüber hinaus umfasst das elektronische Modul 100 eine Mehrzahl von elektronischen Chips oder Dies 104 befestigt an der elektrisch leitfähigen Schicht 103 mittels Bonden, Löten, Haftschicht oder ähnlichem, schematisch angezeigt durch eine Schicht 105 in 1A. Somit sind die elektronischen Chips auch an dem Interposer befestigt.

-

Wie ersichtlich kann der Interposer 101 zwei Hauptflächen, eine obere Hauptfläche und eine untere Hauptfläche, aufweisen, auf der eine entsprechende strukturierte Schicht ausgebildet (gesintert) ist und wobei an jeder eine Mehrzahl von elektronischen Chips befestigt ist.

-

Wie oben beschrieben, der (keramische) Interposer umfasst oder bildet Seitenwände des Fluidkanals 102 oder einen Hohlraum, durch den ein flüssiges Kühlmittel, wie Wasser oder Öl, geführt werden kann, wie es in 1A durch Pfeil 106 schematisch gezeigt ist. Im Fall eines einfachen Hohlraums können einige Strukturen, wie Kühlrippen, in den Hohlraum hineinragen. Der Fluidkanal umfasst ein Eingangsterminal 107 und ein Ausgangsterminal 108, welche von dem gleichen (keramischen) Material des Interposers oder einem anderen Material gebildet werden können. Das Eingangsterminal und das Ausgangsterminal können auf gegenüberliegenden Seiten (wie in 1A gezeigt) oder auf benachbarten Seiten gebildet sein.

-

Des Weiteren ist eine gemoldete Kapselung 109 um die Mehrzahl von elektronischen Chips und den Fluidkanal 102 herum ausgebildet. Nur externe elektrische Verbindungen (Abschnitte eines Leadframes, zum Beispiel; nicht gezeigt in dem Querschnitt) und Abschnitte des Eingangsterminals 107 und des Ausgangsterminals 108 werden frei von Kapselungsmaterial, das die Kapselung bildet, gehalten. Der Leadframe kann mit der elektrisch leitfähigen strukturierten Schicht über Draht- und/oder Clipbonden verbunden werden.

-

1B zeigt schematisch eine Querschnittsansicht eines ähnlichen elektronischen Moduls 120, wobei der Querschnitt in einer Richtung senkrecht zu der in 1A vorgenommen ist, d.h. senkrecht zu dem Eingangs- und Ausgangsterminal und Fluidkanäle 134 schneidend. Des Weiteren können Leadframeabschnitte 122 an der linken Seite und an der rechten Seite gesehen werden. Diese Leadframeabschnitte können unterschiedliche Abmessungen aufweisen und können als logische Signalwege bzw. Leistungspfade verwendet werden. Zusätzlich sind Kontaktdrähte 123 gezeigt, die die Leadframeabschnitte mit metallischen strukturierten Schichten 124, die direkt auf einem keramischen Körper 125 gebildet sind, verbinden.

-

Des Weiteren, elektronischen Chips 130 sind an beiden Hauptflächen des Interposers von 1B befestigt, insbesondere mit entsprechenden metallischen strukturierten Schichten 124. Die elektronischen Chips können beispielsweise mit der metallischen strukturierten Schicht 124 clipverbunden 132 oder drahtverbunden 131 sein. Es ist anzumerken, dass vorzugsweise die elektronischen Chips an die Leadframeabschnitte angeglichen sein können, wie in 1B gezeigt. Zum Erreichen des Angleichens können die Leadframeabschnitte gebogen sein, wie in 1B gezeigt. Dieses Angleichen kann dazu führen, dass die Kontaktdrähte 123 eher kurz sein können, was die Leistung des elektronischen Moduls verbessern kann. Des Weiteren ist eine Kapselung 133 gezeigt, die den Interposer und die daran befestigten oder verbundenen elektronischen Chips umhüllt. Es ist anzumerken, dass, während mehrere separate Fluidkanäle 134 in 1B gezeigt sind, auch nur ein Fluidkanal in dem Interposer gebildet werden kann, wobei die Fluidkanäle im Wesentlichen das gesamte Innere des Interposers ausfüllen.

-

2A und 2B zeigen schematisch eine perspektivische Ansicht eines elektronischen Moduls 200 gemäß einer beispielhaften Ausführungsform, wobei 2B eine Querschnittsansicht des elektronischen Moduls von 2A darstellt. Insbesondere, das elektronische Modul 200 umfasst (einen Körper eines)einen Interposer 201 ausgebildet in einem keramischen Material und einen Hohlraum oder einen Fluidkanal 202 darin bildend (vgl. 2B). Des Weiteren ist eine elektrisch leitfähige strukturierte Schicht 203 direkt auf einem Körper des Interposers 201 ausgebildet oder gesintert.

-

Außerdem umfasst das elektronische Modul 200 eine Mehrzahl von elektronischen Chips oder Dies 204, die an der strukturierten Schicht 203 mittels Bonden, z.B. Löten, befestigt sind. Somit sind die elektronischen Chips auch an dem Interposer befestigt.

-

Wie ersichtlich bildet der Interposer 201 einen Hohlraum darin und hat eine obere und eine untere Hauptfläche und jede hat eine Mehrzahl von elektronischen Chips daran befestigt.

-

Durch den Hohlraum kann ein flüssiges Kühlmittel, wie beispielsweise Wasser, geleitet werden. Der Fluidkanal umfasst ein Eingangsterminal 207 und ein Ausgangsterminal 208, welche von entsprechenden Vertiefungen in dem Interposer, die mit dem Hohlraum in dem Interposer 201 in Fluidverbindung stehen, ausgebildet sein können.

-

Des Weiteren ist eine gemoldete Kapselung 209 um die Mehrzahl von elektronischen Chips und den Fluidkanal 202 herum ausgebildet. Nur externe elektrische Verbindungen 210 (Abschnitte eines Leadframes, zum Beispiel) werden frei von Kapselungsmaterial, das die Kapselung bildet, gehalten.

-

3 zeigt einen Ablaufplan eines Verfahrens zum Herstellen eines elektronischen Moduls 300 gemäß einer beispielhaften Ausführungsform. Insbesondere umfasst das Verfahren Bereitstellen eines Interposers umfassend einen Fluidkanal, ausgebildet in einem elektrisch isolierenden Material, und eine elektrisch leitfähige strukturierte Schicht, wobei die elektrisch leitfähige strukturierte Schicht direkt auf dem elektrisch isolierenden Material gebildet wird (Schritt 301). Des Weiteren wird mindestens ein elektronischer Chip an der elektrisch leitfähigen strukturierten Schicht und in thermischem Kontakt mit dem Fluidkanal befestigt (Schritt 302). Zusätzlich wird eine Kapselung mindestens teilweise um den mindestens einen elektronischen Chip herum gemoldet.

-

Im Allgemeinen kann das Herstellungsverfahren auf Leadframebefestigungskonzepten basiert werden und kann das Bilden (zur Wärmeableitung) eines Stapels von Schichten, einschließlich einer leitenden Schicht (beispielsweise Kupfer), die zum Verteilen von Wärme verwendet wird, einer isolierenden Schicht (z.B. Keramik), die einen Kühlkanal oder Kühlkörper bildet (z.B. einen Hohlraum einschließlich Kühlrippen), umfassen und von einem Kapselungsmaterial, das ein Gehäuse des elektronischen Moduls bildet, umhüllt sein. Insbesondere kann das keramische Material, das den Hohlraum definiert, auch einen Interposer bilden. Somit kann ein Wärmeableitungsstapel mit nur einer sehr geringen Anzahl von Schichten, z.B. leitende Schicht (Cu), isolierende Schicht (Keramik) und Hohlraum (oder Kühlfluid, das durch den Hohlraum fließt) bereitgestellt werden.

-

4A bis 4F zeigen schematische perspektivische Ansichten, die ein Herstellungsverfahren eines elektronischen Moduls 400 nach verschiedenen Schritten gemäß einer beispielhaften Ausführungsform darstellen.

-

Insbesondere zeigt 4A das Herstellungsverfahren eines elektronischen Moduls 400 nachdem ein oder mehrere elektronische Chips oder Dies 401 an einer elektrisch leitfähigen strukturierten Schicht 402 befestigt wurden, die direkt auf einem elektrisch isolierenden Material 404 eines Interposers ausgebildet ist. In dem Körper des Interposers ist ein Fluidkanal ausgebildet, der von dem Eingangsterminal 403 angezeigt wird. 4B zeigt schematisch das Verfahren nachdem eine (innere) Kapselung 410 auf dem Die bzw. auf den Dies gebildet wurde, die von eine Kapselungsmaterial oder Verbund, Harz, Glas, Laminat, Kunststoff oder einem anderen geeigneten Material gebildet werden kann.

-

4C zeigt schematisch das Verfahren nachdem eine Metallisierung 411 und/oder Kontaktlöcher auf oder in der (inneren) Kapselung 410 gebildet wurden, auf welcher eine Lötresistschicht 412 gebildet wird, die in 4D gezeigt ist. Vor dem Bilden der Metallisierung kann eine Keimschicht gebildet werden und/der ein thermischer Aktivierungsschritt kann ausgeführt werden. In einem folgenden Schritt kann ein Leadframe 413 an der Lötresistschicht befestigt werden, was in 4E schematisch gezeigt ist. Wie in 4E ersichtlich ist, können die Abmessungen der Leiter des Leadframes verschieden sein, z.B. können breitere Leiter 416 zum Leiten von Strom verwendet werden, während schmalere und/oder dünnere Leiter zum Leiten von Steuer- oder Logiksignalen verwendet werden können. 4F zeigt schematisch das hergestellte elektronische Modul nachdem eine (äußeren) Kapselung 414 gebildet wurde und Fluidterminals 415 an oder in der (äußeren) Kapselung 414 und in Fluidverbindung mit dem Fluidkanal (nicht gezeigt) befestigt oder angeordnet wurden. Während die Fluidterminals als befestigt zu oder gebildet an gegenüberliegenden Seiten der Kapselung oder des Interposers gezeigt sind, versteht es sich von selbst, dass diese auf derselben Seite oder benachbarten Seiten angeordnet sein können.

-

5A bis 5F zeigen schematische perspektivische Ansichten, die ein Herstellungsverfahren eines elektronischen Moduls 500 nach verschiedenen Schritten gemäß einer weiteren beispielhaften Ausführungsform darstellen. Im Gegensatz zu 4, zeigt 5 ein Herstellungsverfahren, in dem ein Paneel oder Mehrfachblock einschließlich einer Anordnung von elektronischen Chips 510 verwendet wird. Insbesondere zeigt 5A eine Anordnung von elektronischen Chips oder Dies umhüllt von einer (inneren) Kapselung 501 und ein Paneel bildend. 5B zeigt das Verfahren von 5 nachdem eine (galvanische) Umverdrahtungsschicht 502 auf der Kapselung der Anordnung gebildet wurde, aus der eine Lötresistschicht 503 gebildet oder angeordnet wird, wie in 5C gezeigt. Zum Beispiel kann die Umverdrahtungsschicht mit einem so genannten Musterabscheidungsvorgang gebildet werden.

-

5D zeigt das Verfahren von 5 nach einem Vereinzelungsschritt, d.h. nachdem das Paneel gewürfelt wurde, sodass ein Körper eines einzelnen elektronischen Moduls 500 gebildet wurde. In einem folgenden Schritt kann ein Leadframe 504 an der Lötresistschicht 503 befestigt werden, was in 5E schematisch gezeigt ist. Wie in 4 können die Abmessungen der Leiter des Leadframes verschieden sein, z.B. können breitere Leiter 511 für Stromsignale geeignet sein, während schmalere Leiter 512 für Logiksignale geeignet sein können. 5F zeigt schematisch das hergestellte elektronische Modul 500 nachdem eine (äußeren) Kapselung 505 gebildet wurde und Fluidterminals 506 an oder in der (äußeren) Kapselung 505 und in Fluidverbindung mit dem Fluidkanal (nicht gezeigt) befestigt oder angeordnet wurden. Während die Fluidterminals als befestigt zu oder gebildet an einer gemeinsamen Seite der Kapselung oder des Interposers gezeigt sind, versteht es sich von selbst, dass diese auf gegenüberliegenden Seiten oder an benachbarten Seiten angeordnet sein können.

-

Gemäß spezifischer Ausführungsformen wird ein elektronisches Modul mit einer verbesserten Zuverlässigkeit aufgrund verringerter mechanischer oder thermischer Beanspruchungen während Leistungszyklen des elektronischen Moduls bereitgestellt. Diese Verringerung der Beanspruchungen kann aufgrund der Tatsache erfolgen, dass die (metallische) strukturierte Schicht, an der der elektronische Chip befestigt ist, teilweise in oder mindestens zusammen mit einem keramischen Körper des Interposers gesintert ist. Somit kann es möglich sein einerseits eine zuverlässige Verbindung zwischen dem keramischen Körper des Interposers und der strukturierten Schicht zu erzielen und andererseits kann eine Porengröße des Materials der strukturierten Schicht in einem geeigneten Bereich zum Sicherstellen geringer Spannungen zwischen der strukturierten Schicht und dem keramischen Material des Körpers des Interposers liegen.

-

Es sollte auch beachtet werden, dass der Begriff „umfassend“ andere Elemente oder Merkmale nicht ausschließt und dass „ein“ oder „eine“ eine Mehrzahl nicht ausschließen. Außerdem können Elemente kombiniert werden, die im Zusammenhang mit unterschiedlichen Ausführungsformen beschrieben sind. Es sollte ebenfalls beachtet werden, dass Bezugszeichen nicht als den Umfang der Ansprüche einschränkend anzusehen sind. Der Umfang der Erfindung ist durch die beigefügten Ansprüche angegeben.