CN1574411A - 在衬底上沉积厚膜电介质的方法 - Google Patents

在衬底上沉积厚膜电介质的方法 Download PDFInfo

- Publication number

- CN1574411A CN1574411A CNA2004100338090A CN200410033809A CN1574411A CN 1574411 A CN1574411 A CN 1574411A CN A2004100338090 A CNA2004100338090 A CN A2004100338090A CN 200410033809 A CN200410033809 A CN 200410033809A CN 1574411 A CN1574411 A CN 1574411A

- Authority

- CN

- China

- Prior art keywords

- layer

- dielectric

- deposited

- thick film

- dry

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02296—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer

- H01L21/02318—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer post-treatment

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01C—RESISTORS

- H01C17/00—Apparatus or processes specially adapted for manufacturing resistors

- H01C17/06—Apparatus or processes specially adapted for manufacturing resistors adapted for coating resistive material on a base

- H01C17/065—Apparatus or processes specially adapted for manufacturing resistors adapted for coating resistive material on a base by thick film techniques, e.g. serigraphy

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G13/00—Apparatus specially adapted for manufacturing capacitors; Processes specially adapted for manufacturing capacitors not provided for in groups H01G4/00 - H01G11/00

- H01G13/04—Drying; Impregnating

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/33—Thin- or thick-film capacitors (thin- or thick-film circuits; capacitors without a potential-jump or surface barrier specially adapted for integrated circuits, details thereof, multistep manufacturing processes therefor)

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/022—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being a laminate, i.e. composed of sublayers, e.g. stacks of alternating high-k metal oxides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02203—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being porous

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/03—Use of materials for the substrate

- H05K1/0306—Inorganic insulating substrates, e.g. ceramic, glass

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4644—Manufacturing multilayer circuits by building the multilayer layer by layer, i.e. build-up multilayer circuits

- H05K3/4664—Adding a circuit layer by thick film methods, e.g. printing techniques or by other techniques for making conductive patterns by using pastes, inks or powders

- H05K3/4667—Adding a circuit layer by thick film methods, e.g. printing techniques or by other techniques for making conductive patterns by using pastes, inks or powders characterized by using an inorganic intermediate insulating layer

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

- Laminated Bodies (AREA)

- Waveguides (AREA)

Abstract

本发明公开了一种在衬底上沉积厚膜电介质的方法。该方法首先在衬底上沉积第一层厚膜电介质,接着将所述第一层风干,让溶剂逸出,从而增加第一层的孔隙度。然后将所述第一层烘干。接着,在第一层之上沉积另外的厚膜电介质层,并在每层被沉积之后将其烘干。最后烧制所沉积的层。

Description

技术领域

本发明涉及在衬底上沉积厚膜电介质的方法,尤其是在微波电路制造中在衬底上沉积厚膜电介质的方法。

背景技术

微波电路通常由独立的薄膜元件(如微波传送带或弯曲微波传送带)构成,这些薄膜元件然后和一个或多个有源电路管芯一起装配到通常称为“金砖(gold brick)”的机制金属封装体中。这些机制封装体经常构成了最终完成的电路的成本中的相当大的部分。为了简化金砖的加工并且改进阻抗匹配,理想情况下薄膜元件与管芯自身的厚度相同。然而,高频率的微波电路将会导致高功率,而高功率又会导致高热耗散,高热耗散将会减小有源电路片的厚度,而有源电路片厚度的减小又导致薄膜元件厚度的减小,薄膜元件厚度的减小会使衬底易碎,易碎的衬底导致工艺产量低、成本高。

发明内容

本发明的一个方面提供了在衬底上沉积厚膜电介质的方法。该方法包括在衬底上沉积第一层厚膜电介质,接着将第一层厚膜电介质风干,让溶剂逸出,从而增加第一层的孔隙度。然后将第一层厚膜电介质烘干。接着,在第一层厚膜电介质之上沉积另外的厚膜电介质层,并在每层厚膜电介质被沉积之后将其烘干。最后烧制所沉积的层。

这里也公开了其他的实施方式。

附图说明

本发明的示例性实施例在附图中被图示,其中:

图1示出了衬底上沉积厚膜电介质的方法;

图2示出了被沉积在接地面上的第一层厚膜电介质;

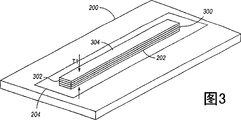

图3示出了在图2中所示的厚膜电介质层上所沉积的另外的厚膜电介质层;

图4示出了烧制之后的图3中所示的厚膜电介质层;

图5示出了被沉积在图4中所示的厚膜电介质上的导体。

具体实施方式

图1示出了一种在衬底上沉积厚膜电介质的方法100。该方法首先在衬底上沉积第一层厚膜电介质102。第一层厚膜电介质沉积之后,让该层持续风干一段时间104,以使溶剂逸出,从而增加第一层厚膜电介质的孔隙度。然后,将该层烘干106。当沉积并干燥所述第一层之后,在所述第一层之上沉积另外的厚膜电介质层108。当每个另外的厚膜电介质层,包括最后一层,被沉积之后,将该层烘干。当所有的层已经被沉积并烘干后,烧制所沉积的这些层110。

图2~图4示出了上述方法的示例应用。图2以示例的方式示出了衬底200,该衬底200可以是40密耳(mil)的研磨过的氧化铝陶瓷衬底。衬底200上表面设有接地面204,但这不是必需的。若设置了接地面,则该接地面可以替代地位于衬底的下表面,甚至可以位于衬底的内部。为了说明的目的,“接地面”一词应当认为包括基本或完全覆盖一个表面的接地面,以及接地迹线,这些接地迹线起到对于一个或多个具体导体的接地面的作用。

按照图1所示的方法,第一层厚膜电介质202被沉积在衬底200上,在一个实施例中,电介质202是KQ CL-90-7858型电介质(一种玻璃电介质),这种电介质可以从Heraeus Cermalloy公司(24 Union Hill Road,West Conshohocken,Pennsylvania,USA)获得。然而,电介质202也可以是其他的电介质,尤其是其他KQ电介质、玻璃电介质或其他具有合适电气性能的电介质。

KQ CL-90-7858型电介质印刷时像标准的厚膜胶;其介电常数为3.95(与氧化铝陶瓷的9.6相比);损耗角正切为2E-4;可以在传统的带式炉中以850℃在空气中进行烧制;烧制后,其在光学上是透明的;该电介质与杜邦QG150型金相容(可从杜邦公司(1007 Market Street,Wilmington,Delaware,USA)获得)。损耗低和介电常数小的特性使KQ CL-90-7858型电介质尤其适合用来制造微波电路(例如微波传输线)。

KQ CL-90-7858型电介质可采用丝网印刷(screen printing)沉积在衬底200/204上。在实际应用中,在沉积前,将KQ CL-90-7858型电介质稀释到粘度为18.0±2.0时的效果较好,然后通过不锈钢屏(200目(mesh)、1.6密耳的金属丝、0.8毫升的乳胶)对其进行印刷来沉积被稀释的电介质。

如果所沉积的电介质层202立即被烘干,那么当其变干时容易破裂。这被认为是被截留的气体(trapped gasses)在电介质层内部产生异常压力的结果。然而已经发现,电介质层的持续风干可以让溶剂从该层中逸出,从而增加该层的孔隙度。对于沉积在镀金氧化铝陶瓷衬底上并且具有约1.5密耳的干印刷厚度的第一层KQ CL-90-7858型电介质,风干至少45分钟,可减轻电介质层在被烘干时的破裂。在风干后,该层202可以采用标准的烘干(例如,在峰值温度150℃左右烘干约15分钟)。

当第一层厚膜电介质202经过风干和烘干后,另外的厚膜电介质层300、302、304就可以被沉积在第一层之上(例如,采用与被用于将第一层厚膜电介质沉积在衬底上相同的工序;见图3)。随后的每一层可以在沉积下一层之前采用约五分钟的快速烘干。假如被干燥但没有被烧制的第一层电介质可能比衬底200/204更加多孔,并且另外的电介质层300-304像合成物那样趋向于互相之间产生比第一层202和衬底200/204之间更牢固的结合,那么对另外的厚膜电介质层的持续风干通常是不必要的,可以被省略来缩短制造工序。

当全部的厚膜电介质层202、300~304已经被沉积和干燥之后,这些层被烧制(见图4的经烧制的电介质400)。如果这些层包含KQ CL-90-7858型电介质,那么可以采取常用的厚膜烧制工艺(例如,厚膜电介质可以用传统的带式炉,在峰值温度大约为850℃的情况下,于峰值处通风烧制10分钟左右。可以采用缓慢地控制温度倾斜上升,以充分散发气体并燃烧所有的有机材料。同样,可以使用缓慢地控制温度倾斜下降来防止衬底的破裂)。

在烧制过程中,所沉积的电介质层202、300~304将会收缩(即,由于溶剂和有机粘合剂被烧去)。因此,只能通过沉积足够达到比预期的最终电介质厚度更大的干印刷厚度(T1,见图3)的电介质层202、300~304,以获得预期的最终电介质厚度(或“烧制后印刷厚度”;T2,见图4)。举例来说,前面所提到的KQ CL-90-7858型电介质在烧制后会收缩到原来的烧制前厚度的60%左右,与此相比,其他电介质材料可能具有更大或更小的收缩系数,不过,对于给定生产商的特定产品类型,其收缩系数通常是固定的。所沉积的层的干印刷厚度和烧制后印刷厚度都可以用垂式厚度测微器(drop-gauge micrometer)或针式轮廓仪来测量。

因为厚膜层的沉积过程中,在可以多么精确地控制厚膜层的高度方面存在一些限制,并且,因为后续的厚膜层的沉积仅是叠加了所有厚膜高度变化的效果,所以,在一些情况下,沉积厚膜电介质层,直到达到超过了预期干印刷厚度的干印刷厚度(T1)。然后,精确的最终电介质厚度(T2)可以通过多种方法获得。其中一种方法就是在所沉积的层202、300~304被烧制之前,将它们平坦化到预期干印刷厚度,并使用已知的收缩系数获得预期的最终结果。在此情况下,“干印刷厚度=烧制后印刷厚度/收缩系数”是一个有用的公式。注意的是,对于10密耳厚的电介质来说,简单剪切金属垫片方式(simple cutout metal shim pattern)可以被用来获得误差小于±0.4密耳的最终厚度。一种更精确但费用也更高的方法是将烧制后的电介质研磨到预期的最终电介质厚度。采用这种方法,10密耳厚的电介质层面可以被控制在误差小于±0.1密耳的变化范围内。接地表面然后可以被抛光以去除刮痕,或者如果电介质采用KQ CL-90-7858型,那么接地电介质400可以被再烧制,以使接地表面以及各边光滑(即,因为KQ CL-90-7858型电介质在再烧制时会回流到小角度)。

应当注意,对于KQ CL-90-7858型电介质而言,当采用研磨方法时,需11密耳左右的干燥印刷厚度来获得约5密耳的最终(烧制后)的电介质厚度。

在接地面204上沉积了厚膜电介质400之后,可以在厚膜电介质上形成导体500(见图5)。举例来说,可以通过在电介质400上沉积导电厚膜(例如,采用丝网印刷、模板印刷(stencil printing)或者刮刀式印刷(doctor blading)),然后在导电厚膜中图案化并蚀刻导体500,来形成这样的导体。另外,导体500也可以采用发明人约翰·F·凯西(John F.Casey)等的题为“在电介质上形成导体的方法(Methods for Forming aConductor on a Dielectric)”的专利申请中所公开的方法来形成。

上述技术还可以被用在本发明的至少一些实施例中,以形成比常规厚膜工艺所生产的电介质层厚许多的高质量电介质层。对于给定的预期的微波阻抗值来说,电介质层越厚,则允许导体带越宽,而导体带越宽,则可以生成更精确的线路,并且可减少因导体损耗而产生的信号衰减。

本申请涉及John F.Casey等人在与本申请相同日期递交的题为“制作微波电路的方法(Methods for Making Microwave Circuits)”的申请(卷号No.10020707-1),以及John F.Casey等人在与本申请相同日期递交的题为“在电介质上形成导体的方法(Methods for Forming a Conductor on aDielectric)”的申请(卷号No.10030748-1)。这些申请所公开的所有内容在这里作为参考而被引用。

尽管这里已经详细描述了本发明的示例性且目前是优选的实施例,但应该理解,本发明的概念可以以别的多种方式来实现和利用,并且所附权利要求应当被解释为包括除了由现有技术所限定的之外的这些变化。

Claims (20)

1.一种在衬底上沉积厚膜电介质的方法,包括:

a)在衬底上沉积第一层厚膜电介质;

b)风干所述第一层,以使溶剂逸出,从而增加所述第一层的孔隙度;

c)烘干所述第一层;

d)在所述第一层之上沉积另外的厚膜电介质层,每个另外的层被沉积之后进行烘干;以及

e)烧制所述沉积的层。

2.如权利要求1所述的方法,其中,所述第一层被风干至少45分钟。

3.如权利要求1所述的方法,其中,所述烘干第一层包括以峰值温度约150℃烘干约15分钟。

4.如权利要求3所述的方法,其中,所述烘干另外的层包括以峰值温度约150℃烘干约15分钟。

5.如权利要求1所述的方法,其中,所述烧制包括以峰值温度约850℃的烧制。

6.如权利要求1所述的方法,还包括测量所沉积的层的干印刷厚度,以确定在所沉积的层被烧制之后是否将达到预期的最终电介质厚度。

7.如权利要求6所述的方法,其中,所沉积的层的所述干印刷厚度通过垂式厚度测微器或针式轮廓仪中的一个来测量。

8.如权利要求6所述的方法,其中,所沉积的层的所述干印刷厚度用垂式厚度测微器来测量。

9.如权利要求1所述的方法,其中,所述厚膜电介质层包括KQ电介质。

10.如权利要求9所述的方法,其中,所述KQ电介质是KQ CL-90-7858型电介质。

11.如权利要求10所述的方法,还包括在烧制之后,将所沉积的层研磨至预期的最终电介质厚度,然后再烧制所沉积的层,以使接地表面以及各边光滑。

12.如权利要求1所述的方法,其中,所述厚膜电介质层包括玻璃电介质。

13.如权利要求1所述的方法,还包括在沉积前将所述厚膜电介质稀释到粘度为18.0±2.0。

14.如权利要求1所述的方法,其中,所述厚膜电介质层是通过具有200目、1.6密耳的金属丝、0.8毫升乳胶的不锈钢屏印刷所述层而被沉积的。

15.如权利要求1所述的方法,还包括沉积另外的厚膜电介质层,直到达到了超过预期干印刷厚度的干印刷厚度,然后在烧制所沉积的层之前,将所沉积的层平坦化至预期干印刷厚度。

16.如权利要求1所述的方法,还包括在烧制之后,将所沉积的层研磨至预期的最终电介质厚度,然后抛光接地表面。

17.如权利要求1所述的方法,其中所述第一层被风干至少45分钟,其中所述烘干第一层包括以峰值温度约150℃烘干约15分钟,其中所述烘干每个另外的层包括以峰值温度约150℃烘干约5分钟,并且其中,所述烧制包括以峰值温度约850℃的烧制。

18.如权利要求17所述的方法,其中,所述厚膜电介质包括KQ CL-90-7858型电介质。

19.如权利要求18所述的方法,其中,所述KQ CL-90-7858型电介质在沉积之前被稀释至粘度为18.0±2.0。

20.如权利要求18所述的方法,还包括在烧制之后,将所沉积的层研磨至预期的最终电介质厚度,然后再烧制所沉积的层,以使接地表面以及各边光滑。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/600,600 | 2003-06-19 | ||

| US10/600,600 US20040258841A1 (en) | 2003-06-19 | 2003-06-19 | Methods for depositing a thickfilm dielectric on a substrate |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN1574411A true CN1574411A (zh) | 2005-02-02 |

Family

ID=33517793

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNA2004100338090A Pending CN1574411A (zh) | 2003-06-19 | 2004-04-14 | 在衬底上沉积厚膜电介质的方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US20040258841A1 (zh) |

| JP (1) | JP2005012229A (zh) |

| CN (1) | CN1574411A (zh) |

| TW (1) | TWI229901B (zh) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7022251B2 (en) * | 2003-06-19 | 2006-04-04 | Agilent Technologies, Inc. | Methods for forming a conductor on a dielectric |

| US6953698B2 (en) * | 2003-06-19 | 2005-10-11 | Agilent Technologies, Inc. | Methods for making microwave circuits |

| US8635767B2 (en) * | 2011-01-05 | 2014-01-28 | Thoe Boeing Company | System for depositing microwire |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3808042A (en) * | 1970-06-05 | 1974-04-30 | Owens Illinois Inc | Multilayer dielectric |

| US4303480A (en) * | 1977-08-01 | 1981-12-01 | General Dynamics, Pomona Division | Electroplating of thick film circuitry |

| DE3616723A1 (de) * | 1986-05-17 | 1987-11-19 | Philips Patentverwaltung | Mikrowellenbaustein |

| US4808274A (en) * | 1986-09-10 | 1989-02-28 | Engelhard Corporation | Metallized substrates and process for producing |

| JPH04267586A (ja) * | 1991-02-22 | 1992-09-24 | Nec Corp | 同軸配線パターンおよびその形成方法 |

| SE468573B (sv) * | 1991-06-14 | 1993-02-08 | Ericsson Telefon Ab L M | Anordningar med boejliga, ytorienterade striplineledningar samt foerfarande foer framstaellning av en saadan anordning |

| JP3241139B2 (ja) * | 1993-02-04 | 2001-12-25 | 三菱電機株式会社 | フィルムキャリア信号伝送線路 |

| US6353189B1 (en) * | 1997-04-16 | 2002-03-05 | Kabushiki Kaisha Toshiba | Wiring board, wiring board fabrication method, and semiconductor package |

| US5910334A (en) * | 1997-12-16 | 1999-06-08 | Delco Electronics Corporation | Method of manufacture for a thick film multi-layer circuit |

| US6000120A (en) * | 1998-04-16 | 1999-12-14 | Motorola, Inc. | Method of making coaxial transmission lines on a printed circuit board |

| US20010012692A1 (en) * | 1998-10-30 | 2001-08-09 | Robin L. Miller | Thick-film etch-back process for use in manufacturing fine-line hybrid circuits |

| US6255730B1 (en) * | 1999-04-30 | 2001-07-03 | Agilent Technologies, Inc. | Integrated low cost thick film RF module |

| FR2806529B1 (fr) * | 2000-03-14 | 2005-03-04 | St Microelectronics Sa | Procede d'ajustage d'un parametre electrique sur un composant electronique integre |

| US6420778B1 (en) * | 2001-06-01 | 2002-07-16 | Aralight, Inc. | Differential electrical transmission line structures employing crosstalk compensation and related methods |

| US6457979B1 (en) * | 2001-10-29 | 2002-10-01 | Agilent Technologies, Inc. | Shielded attachment of coaxial RF connector to thick film integrally shielded transmission line on a substrate |

-

2003

- 2003-06-19 US US10/600,600 patent/US20040258841A1/en not_active Abandoned

-

2004

- 2004-03-17 TW TW093107131A patent/TWI229901B/zh not_active IP Right Cessation

- 2004-04-14 CN CNA2004100338090A patent/CN1574411A/zh active Pending

- 2004-06-21 JP JP2004182359A patent/JP2005012229A/ja active Pending

Also Published As

| Publication number | Publication date |

|---|---|

| US20040258841A1 (en) | 2004-12-23 |

| TW200501249A (en) | 2005-01-01 |

| JP2005012229A (ja) | 2005-01-13 |

| TWI229901B (en) | 2005-03-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7265043B2 (en) | Methods for making microwave circuits | |

| CN1212655C (zh) | 一种制备零收缩率低温共烧陶瓷多层基板的工艺 | |

| JP2002015939A (ja) | 積層型電子部品およびその製法 | |

| CN1574411A (zh) | 在衬底上沉积厚膜电介质的方法 | |

| JP4606115B2 (ja) | 多層基板及びその製造方法 | |

| US7180155B2 (en) | Method for manufacturing thin-film multilayer electronic component and thin-film multilayer electronic component | |

| JP4423025B2 (ja) | 多層基板及びその製造方法 | |

| JP2629543B2 (ja) | 厚膜プリント板のビア形成方法 | |

| JP3162539B2 (ja) | 導体ペーストによって導体を形成したセラミック配線基板の製造方法 | |

| US7022251B2 (en) | Methods for forming a conductor on a dielectric | |

| JP4334659B2 (ja) | セラミック配線基板とその製造方法 | |

| JPH09186044A (ja) | 積層電子部品用内部電極材料ペースト、積層電子部品及びその製造方法 | |

| JP4416346B2 (ja) | 回路基板の製造方法 | |

| JP2676221B2 (ja) | グレーズ処理セラミック基板およびその製造方法 | |

| US8754742B2 (en) | Multilayer ceramic substrate and method for producing the same | |

| JP3559310B2 (ja) | 積層セラミック回路基板の製造方法 | |

| JP2001057471A (ja) | 薄膜配線基板の製造方法 | |

| JPH087646A (ja) | 銅ペースト | |

| JP4610185B2 (ja) | 配線基板並びにその製造方法 | |

| CN1144289C (zh) | 一种晶片排阻端面电极的制作方法 | |

| JP2565351B2 (ja) | 電子回路部品 | |

| WO2022163574A1 (ja) | 配線基板 | |

| JPH0199207A (ja) | コンデンサ構造 | |

| JP2006005379A (ja) | コンデンサ内蔵型積層セラミック回路基板 | |

| JPH04238858A (ja) | 低温焼成ガラスセラミック体 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C02 | Deemed withdrawal of patent application after publication (patent law 2001) | ||

| WD01 | Invention patent application deemed withdrawn after publication |