CN1245759C - 多频带功率放大器 - Google Patents

多频带功率放大器 Download PDFInfo

- Publication number

- CN1245759C CN1245759C CNB02155787XA CN02155787A CN1245759C CN 1245759 C CN1245759 C CN 1245759C CN B02155787X A CNB02155787X A CN B02155787XA CN 02155787 A CN02155787 A CN 02155787A CN 1245759 C CN1245759 C CN 1245759C

- Authority

- CN

- China

- Prior art keywords

- transistor

- wiring

- unit transistor

- unit

- output

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/20—Power amplifiers, e.g. Class B amplifiers, Class C amplifiers

- H03F3/21—Power amplifiers, e.g. Class B amplifiers, Class C amplifiers with semiconductor devices only

- H03F3/211—Power amplifiers, e.g. Class B amplifiers, Class C amplifiers with semiconductor devices only using a combination of several amplifiers

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F1/00—Details of amplifiers with only discharge tubes, only semiconductor devices or only unspecified devices as amplifying elements

- H03F1/30—Modifications of amplifiers to reduce influence of variations of temperature or supply voltage or other physical parameters

- H03F1/302—Modifications of amplifiers to reduce influence of variations of temperature or supply voltage or other physical parameters in bipolar transistor amplifiers

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/60—Amplifiers in which coupling networks have distributed constants, e.g. with waveguide resonators

- H03F3/602—Combinations of several amplifiers

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/72—Gated amplifiers, i.e. amplifiers which are rendered operative or inoperative by means of a control signal

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2200/00—Indexing scheme relating to amplifiers

- H03F2200/111—Indexing scheme relating to amplifiers the amplifier being a dual or triple band amplifier, e.g. 900 and 1800 MHz, e.g. switched or not switched, simultaneously or not

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2200/00—Indexing scheme relating to amplifiers

- H03F2200/429—Two or more amplifiers or one amplifier with filters for different frequency bands are coupled in parallel at the input or output

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2203/00—Indexing scheme relating to amplifiers with only discharge tubes or only semiconductor devices as amplifying elements covered by H03F3/00

- H03F2203/72—Indexing scheme relating to gated amplifiers, i.e. amplifiers which are rendered operative or inoperative by means of a control signal

- H03F2203/7209—Indexing scheme relating to gated amplifiers, i.e. amplifiers which are rendered operative or inoperative by means of a control signal the gated amplifier being switched from a first band to a second band

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Amplifiers (AREA)

- Bipolar Transistors (AREA)

- Bipolar Integrated Circuits (AREA)

Abstract

最终级功率放大晶体管(Trg3,Trd3)的单位晶体管混合配置在最终输出放大晶体管形成区域PW3内。另外,用以连接这些最终输出级晶体管的输出信号线之间连接有电感元件(Lcc)。可以在不使频带间隔离劣化的情况下,避免双频带功率放大器的最终级晶体管中发生电流集中。

Description

技术领域

本发明涉及放大器,具体地说,涉及双频带或三频带等多频带功率放大器的结构。更具体地说,本发明涉及不使通信品质劣化以及芯片尺寸增大的情况下可以防止多频带功率放大器的晶体管特性劣化的结构。

背景技术

现在,作为移动装置通信用的功率放大器,广泛应用采用GaAsMESFET(金属-半导体场效应晶体管)、GaAsHEMT(高电子迁移率晶体管)以及GaAsHBT(异质结双极晶体管)的MMIC(单片微波IC)或组件(混合IC或多片组件)。这些晶体管中,由于利用砷化镓(GaAs)或硅化锗(SiGe)的异质结的GaAs-HBT和SiGe-HBT与传统的FET(场效应晶体管)相比具有以下的优点,因而成为现在最受期待的移动装置通信用的功率元件:

(1)不需要负的栅极偏置电压,可以实现单一电源动作;

(2)与Si-MOSFET(绝缘栅型场效应晶体管)同样,即使在漏极(集电极)侧不设置模拟开关,也可以执行输出的开/关动作;以及

(3)输出功率密度高,可以用比FET功率放大器小型的功率放大器获得规定的输出。

作为移动装置通信的典型的应用有便携电话系统。作为这样的便携电话系统,有现在最广泛采用的900MHz频带便携电话系统即欧州GSM(全球移动通信系统(GLOBAL SYSTEM FOR MOBILECOMMUNICATION)),以及欧州广泛采用的1800MHz频带便携电话系统即DCS(数字无绳系统(DIGITAL CORDLESS SYSTEMS))。这些GSM以及DCS等的通信方式中,采用1W到4W的高输出的便携电话,作为其功率放大器,开始采用可发挥HBT的特征的功率放大器(HBT功率放大器)取代迄今成为主流的Si-MOSFET功率放大器。

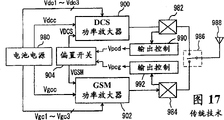

图14是传统的GSM-DCS双频带功率放大电路的结构的概略示意图。图14中,双频带功率放大电路包括:激活时接收DCS信号IN_DCS和偏置电压Vdcc并生成输出信号OUT_DCS的DCS功率放大器900;激活时接收输入信号IN_GSM和偏置电压Vgcc,放大输入信号IN_GSM并生成输出信号OUT_GSM的GSM功率放大器902;根据输出控制电压Vpc和模式选择信号Vmod激活DCS功率放大器900以及GSM功率放大器902的其中一个,且控制激活的功率放大器的偏置电压的偏置开关904。

对DCS功率放大器900以及GSM功率放大器902分别生成偏置控制电压Vpc。

该双频带功率放大电路中,在偏置开关904的控制下,根据模式选择信号Vmod激活DCS功率放大器900以及GSM功率放大器902的其中一个。DCS功率放大器900的输出信号OUT_DCS或GSM功率放大器902的输出信号OUT_GSM通过共用的天线发送。

图15是图14所示的DCS功率放大器900的结构的一例的示意图。图15中,DCS功率放大器900包括:输入匹配电路911,接收输入信号IN_DCS;第1放大级912,放大经由输入匹配电路911提供的信号;第2放大级914,经由级间连接电路913接收第1放大级912的输出信号并放大;第3放大级916,经由级间匹配电路915接收第2放大级914的输出信号并放大;输出匹配电路917,接收第3放大级916的输出信号并生成输出信号OUT_DCS。

输入匹配电路911由短截线、电阻、电容元件构成,令输入信号和该功率放大器900的输入阻抗匹配。向放大级912、914以及916提供集电极偏置电压Vdc1、Vdc2以及Vdc3。这些放大级912、914以及916分别包含异质结双极晶体管(HBT)Trd1、Trd2,以及Trd3作为各自的功率放大元件。通过稳定用的短截线以及电容元件形成的稳定电路向这些晶体管Trd1-Trd3的各个集电极结点提供集电极偏置电压Vdc1、Vdc2以及Vdc3。

各个放大级912、914以及916中,通过经由短截线以及电容元件构成的稳定电路向功率放大晶体管Trd1、Trd2以及Trd3的集电极提供集电极偏置电压Vdc1、Vdc2以及Vdc3,可以根据这些功率放大晶体管Trd1-Trd3的基极电位,稳定且高速地变化该集电极电位。

DCS功率放大器900还包括:低通滤波器920,接收DCS用偏置电压Vdcc;偏置电压控制电路921以及924以及926,根据来自该低通滤波器920的偏置电压Vdcc和图14所示偏置开关904的基极偏置控制电压VDCS,调节功率放大晶体管Trd1、Trd2以及Trd3的基极电压;模式切换电路922,根据来自图17所示偏置开关904的模式选择信号Vmodd,有选择地将这些偏置电压控制电路921、924以及926的输出偏置电压固定为接地电压电平。偏置电压控制电路921由电阻元件构成。

模式切换电路922包括开关晶体管,后者响应模式选择信号Vmodd有选择地导通,通过该开关晶体管的开/截止状态,设定功率放大器900的非激活/激活状态。

根据图14所示模式选择信号Vmod,由偏置开关904生成模式选择信号Vmodd。模式选择信号Vmodd为H电平时,模式切换电路922的开关晶体管变成导通状态,这些功率放大晶体管Trd1、Trd2以及Trd3的基极电压固定为接地电压或基极发射极间电压电平,这些功率放大晶体管Trd1-Trd3全部设定成截止状态。

另一方面,模式选择信号Vmodd为L电平时,该模式切换电路922中的开关晶体管变成非导通状态,来自偏置开关904的偏置控制电压VDCS经由偏置电压控制电路(电阻元件)921提供给初级的功率放大晶体管Trd1的基极,另外,由偏置电压控制电路924以及926向功率放大晶体管Trd2以及Trd3的基极提供根据偏置电压Vdcc和偏置控制电压VDCS的电压电平的偏置电压。功率放大晶体管Trd1、Trd2以及Trd3根据这些基极偏置电压,放大由前级的匹配电路向基极提供的信号。根据偏置控制电压VDCS对放大级914以及916的放大率进行调节。

该图15中,虚线框930表示的部分通常由一个半导体芯片构成,该外部配置有短截线以及电容。

最终级的功率放大晶体管Trd3经由输出匹配电路917生成输出信号OUT_DCS,经由次级的耦合器向天线送出信号。从而,该最终级的功率放大晶体管Trd3的驱动能力与前级的功率放大晶体管Trd1及Trd2相比大很多。该最终级的功率放大晶体管Trd3的集电极结点通常经由焊盘与外部配置的短截线连接。输出结点中配置开环短截线,调节输出电容负载,稳定该最终级的放大级916的输出信号。

图16是图14所示GSM功率放大器904的结构的一例的示意图。图16中,GSM功率放大器904包括:输入匹配电路951,接收GSM输入信号IN_GSM;第1放大级952,放大经由输入匹配电路951提供的信号;第2放大级954,经由级间匹配电路953接收该第1放大级952的输出信号并放大;第3放大级956,经由级间匹配电路955接收该第2放大级954的输出信号并放大;输出匹配电路957,将第3放大级956的输出信号向输出结点传送。

第1放大级952包含功率放大晶体管Trg1,第2放大级954包含功率放大晶体管Trg2,第3放大级956包含功率放大晶体管Trg3。功率放大晶体管Trg1的集电极经由短截线和电容元件形成的稳定电路接收集电极控制电压Vgc1。功率放大晶体管Trg2的集电极经由短截线以及电容元件构成的稳定电路接收集电极控制电压Vgc2。功率放大晶体管Trg3的集电极经由电容元件以及短截线构成的稳定电路接收集电极控制电压Vgc3。

GSM功率放大器904还包括:低通滤波器960,接收偏置电压Vgcc;偏置电压控制电路(电阻元件)961,用以将来自图14所示偏置开关904的偏置控制电压VGSM向功率放大晶体管Trg1的基极提供;偏置电压控制电路964,根据偏置电压Vgcc和偏置控制电压VGSM,调节功率放大晶体管Trg2的基极偏置电压;偏置控制电路966,根据偏置电压Vgcc和偏置控制电压VGSM,调节功率放大晶体管Trg3的基极偏置电压;模式切换电路962,根据来自图14所示偏置开关904的模式选择信号Vmodg,将偏置控制电压VGSM驱动到接地电压电平,将这些功率放大晶体管Trg1、Trg2以及Trg3设定为非导通状态。

模式切换电路962包含开关晶体管,后者响应模式选择信号Vmodg有选择地导通。通过该开关晶体管的导通/截止状态,可将GSM功率放大器有选择地设定为非激活/激活状态。

图14所示偏置开关904根据模式选择信号Vmod生成模式选择信号Vmodg。该模式选择信号Vmodg为H电平时,模式切换电路962中,开关晶体管变成导通状态,偏置控制电压VGSM变成接地电压电平的L电平,功率放大晶体管Trg1变成非导通状态。另外,偏置控制电路964及966中,各个输出电压变成功率放大晶体管Trg2及Trg3的基极·发射极间电压,这些功率放大晶体管Trg2及Trg3也变成非导通状态。从而该状态中,GSM功率放大器904的功率放大动作被停止。

另一方面,模式选择信号Vmodg若变成L电平,则模式切换电路962中的开关晶体管变成截止状态,由偏置电压控制电路961、964以及966根据偏置电压VGSM及偏置控制电压Vgcc对功率放大晶体管Trg1、Trg2、Trg3的基极电压进行偏置,在基极接收来自各个前级的匹配电路的信号并进行放大动作。

图15及图16所示功率放大器900及904具有仅仅其处理频率不同的3级的放大级。由于最终级的功率放大晶体管Trd3及Trg3的集电极与输出焊盘连接,经由输出匹配电路957以大驱动力驱动输出负载,因而其电流驱动能力变得很大。

偏置开关902接收分别与DCS模式及GSM模式对应的偏置控制电压Vpcd及Vpcg,且接收模式选择信号Vmodd及Vmodg,根据模式选择信号激活DCS功率放大器900及GSM功率放大器904的其中一个。

通过由该偏置开关902有选择地激活功率放大器900及904的其中一个,可以用1800MHz频带的DCS及900MHz频带的GSM进行通信。

图17是包含双频带功率放大电路的便携电话机的重要部分结构的概略示意图。图17中,便携电话机包括:电池电源980,向DCS功率放大器900供给集电极偏置电压Vdc1-Vdc3和偏置电压Vdcc,向GSM功率放大电路902供给集电极偏置电压Vgc1-Vgc3和偏置电压Vgcc;高频耦合器982,作为传送DCS功率放大器900的输出信号的频带隔离器;高频耦合器984,作为传送GSM功率放大电路902的输出信号的频带隔离器;选择电路986,根据未图示的模式选择信号选择该高频耦合器982及984的输出信号的其中一个并传送到天线988;输出控制电路990,监视高频耦合器982的输出信号,根据该监视结果生成偏置控制电压Vpcd;输出控制电路992,监视高频耦合器984的输出信号,根据该监视结果生成偏置控制电压Vpcg。

这些输出控制电路990及992的偏置控制电压Vpcd及Vpcg向偏置开关904提供,该偏置开关904根据这些偏置控制电压Vpcd及Vpcg,调节功率放大电路900及902的基极偏置电压VDCS及VGSM的电压电平。

GSM及DCS的用途中,要求功率放大器处理1W以上的大输出功率。从而,为了降低电压调节器中的功率损失,由电池电源980直接向该功率放大电路900及902提供偏置电压Vdc1-Vdc3、Vdcc、Vgc1-Vgc3及Vgcc。

另外,DCS功率放大电路900的输出信号经由高频耦合器982及选择电路985向天线988传送,另外,GSM功率放大电路902的输出信号经由高频耦合器984及选择电路986向天线988传送。这些功率放大电路900及902的输出端子和天线端之间,通常不采用国内的便携电话(例如PDC(个人数字蜂窝))等中一般采用的隔离器。该隔离器配置成在天线端子988的输出阻抗变动时,用以抑制这些功率放大电路900及902的输出负载阻抗的变动。GSM以及DCS的用途中,为了小型化及降低输出损失,不采用这样的隔离器,仅仅采用高频耦合器982及984。

从而,对于功率放大器900及902,存在有当该电池电源980充电时,高电源电压状态及天线端子988的负载变动的影响直接施加到功率放大器900及902的过于苛刻的使用状态。在这样的高电源电压时,在接收大输出负载变动的场合,集电极损失增大,该电流损失引起发热,导致构成功率放大晶体管的晶体管元件的不均一动作。这是因为,功率放大晶体管由多个单位晶体管元件构成,该单位晶体管元件的集电极电流的分布引起动作温度条件的差异,由该温度条件的差异导致该功率放大晶体管的不均一动作。

特别是,最终级的功率放大晶体管Trg3或Trd3内部的单一晶体管元件内的不均一动作引起所谓电流集中,即一部分的单位晶体管元件的动作电流占该最终级晶体管全体的动作电流的大部分。结果,导致突发动作时的脉冲内输出功率的变动,最坏情况下会导致最终级功率放大晶体管的破坏。

这样的发热引起的电流集中的问题是靠近芯片配置多个单位晶体管元件以获得大输出功率的功率放大器特有的问题。

图18是图15及图16所示功率放大器的芯片布局的概略示意图。图18中,DCS功率放大器900及GSM功率放大器902分别在半导体芯片999的2个分割区域形成。该半导体芯片上配置图15及图16中虚线框所示的电路。

DCS功率放大器900的初级功率的功率放大晶体管Trd1配置于晶体管形成区域PWD1,2级功率放大晶体管Trd2配置于晶体管形成区域PWD2。这些晶体管形成区域PWD2及PWD1之间配置了匹配电路配置区域IMD12,用以形成获得功率放大器Trd1及Trd2的级间匹配的级间匹配电路912。

该DCS功率放大器900中,还将用以获得2级功率放大晶体管Trd2和3级(最终)功率放大晶体管Trd3的级间匹配的级间匹配电路915配置于匹配电路配置区域IMD23。通过该匹配电路配置区域IMN23,与晶体管形成区域PWD1、PWD2以及匹配电路配置区域IMD12相对,配置了配置有最终级的功率放大晶体管Trd3的晶体管形成区域PWD3。晶体管形成区域PWD1、匹配电路形成区域IMN12以及晶体管形成区域PWD2配置成一列,匹配电路配置区域IMN23配置成与这些区域PWD1、IMN12以及PWD2邻接。

初级功率放大晶体管Trd1由例如2个单位晶体管元件构成,2级功率放大晶体管Trd2由例如10个单位晶体管元件构成。最终级的功率放大晶体管Trd3由例如6×10个单位晶体管元件构成。

空区域EPY配置成与配置有最终级的功率放大晶体管Trd3的晶体管形成区域PWD3邻接。与这些空区域EPY和晶体管形成区域PWD3相对,配置了配置有DCS用输出焊盘的焊盘区域OBD。由于该最终级的功率放大晶体管Trd3的驱动电流大,该输出信号线的布线宽度也大,因而该焊盘区域OBD中配置多个焊盘,以取得足够大的输出布线宽度。

GSM功率放大器902的初级功率的功率放大晶体管Trg1配置于晶体管形成区域PWG1,2级功率放大晶体管Trg2配置于晶体管形成区域PWG2。这些晶体管形成区域PWG1及PWG2之间,配置了配置有级间匹配电路953的匹配电路配置区域IMG12。这些区域PWG1、IMG12及PWG2配置成一列。

配置有级间匹配电路955的匹配电路配置区域IMG23配置成与这些区域PWG1、PWG2及IMG12邻接。

最终级的功率放大晶体管Trg3形成于晶体管形成区域PWG3,后者与匹配电路配置区域IMG23邻接且与晶体管形成区域PWD3及空区域EPY配置成一列。

功率放大晶体管Trg1由例如4个单位晶体管元件构成,2级功率放大晶体管Trg2由例如16个单位晶体管元件构成。最终级的功率放大晶体管Trg3由例如10×10个单位晶体管元件构成。

与晶体管形成区域PWG3邻接,设置了配置有GSM用输出焊盘的输出焊盘区域OBG。

功率放大器900及902集成在半导体芯片999上。如图18所示,这些DCS功率放大器900及902中,通过使形成对应的构成要素的区域进行并列配置,可有效地配置实质上电路结构相同的功率放大器900及902,并简化该布局。

如该图18所示,功率放大器900及902中的最终级的功率放大晶体管与初级及2级的功率放大晶体管相比,其电流驱动力大,占有较大的芯片面积。

图19是这些功率放大器900及902的最终级的功率放大晶体管Trd3及Trg3的结构的概略示意图。这些最终级输出放大晶体管Trd3及Trg3只是其中包含的晶体管元件数不同,图19中表示一个功率放大晶体管的结构。

图19中,最终级输出放大晶体管包含排列成m行n列的单位晶体管Trl1-Trln至Trm1-Trmn。这些单位晶体管Trl1-Trln至Trm1-Trmn分别由异质结双极晶体管(HBT)构成。

分别与单位晶体管行对应配置副集电极线SCL1-SCLm,另外,分别与单位晶体管元件行对应配置副基极线SBL1-SBLm。副基极线SBL1-SBLm分别连接到主基极线MBL,后者分别通过结点A及B接收来自基极偏置电压控制电路的基极偏置电压和来自前级的级间匹配电路的高频输入(RF输入)。副集电极线SCL1-SCLm共同连接到与输出结点C连接的主集电极线MCL。

单位晶体管Trl1-Trln-Trm1-Trmn的各个基极分别通过基极镇流电阻Rbl1-Rbln至Rbm1-Rbmn与对应的副基极线SBL1-SBLm连接。另外,单位晶体管Trl1-Trln至Trm1-Trmn的各个发射极分别通过发射极镇流电阻Rel1-Reln至Rem1-Remn与接地结点连接。

这些镇流电阻Rbl1-Rbln至Rbm1-Rbmn以及Rel1-Reln至RRem1-Remn在温度上升时,集电极电流增大的场合,进行负反馈,降低对应的单位晶体管的基极·发射极间电压,抑制该集电极电流的增大。这些多个单位晶体管构成的双极晶体管称为多触点双极晶体管。

图20是图19所示最终级的功率放大晶体管的布局的概略示意图。图20中,形成单位晶体管Tr的单位元件区域11-17、21-27、31-37、41-47、51-57以及61-67配置成6行。这些单位元件区域分割成3个框BA、BB及BC。框BA、BB及BC分别包括排列成2行配置的单位元件区域。

单位元件mm11-17、21-27、31-37、41-47、51-57以及61-67中分别形成HBT,包括发射极区域、集电极区域以及基极区域。

对排列成1行而配置的单位元件区域(单位晶体管Tr)共同配置各个副发射极布线5c1-5c6,连接到对应行中配置的单位元件区域的发射极区域。这些副发射极布线5c1-5c6与单位晶体管形成区域的两侧沿列方向延伸配置的发射极布线5a及5b连接。这些发射极布线5a及5b与供给接地电压的接地结点连接。副发射极布线5c1-5c6和形成单位晶体管Tr的区域重叠的区域中,由例如外延层形成发射极镇流电阻。

在各个框BA-BC中,在对应框的单位元件区域共同配置基极布线2b1-2b3。这些副基极布线2b1-2b3延伸到对应框中配置成2行的单位元件区域间的区域,通过基极镇流电阻7与对应框的单位元件区域的基极区域连接。

这些副基极布线2b1-2b3分别与基极布线2a连接。该基极布线2a还与高频信号输入部分1连接。该高频信号输入部分1通过级间匹配电路从前级的放大级接收高频输入(RF输入)。另外,来自对应的偏置电压控制电路的基极偏置控制电压传送到该基极布线2a。单位元件区域11-17~61-67中形成的单位晶体管Tr是异质结双极晶体管HBT,基极电流Ib1、Ib2以及Ib3传送到这些副基极布线2b1、2b2以及2b3。

而且,与单位元件区域的各行对应,副集电极布线4b1、4b6共同配置于对应行的单位元件区域。这些各个副集电极布线4b1-4b6共同连接到对应行的单位元件区域的集电极区域。这些副集电极布线4b1-4b6共同与集电极布线4a连接。集电极布线4a与输出高频信号的输出部分3连接,从该输出部分3输出高频信号(RF输出)。

副集电极布线4b1-4b6中将向集电极布线4a提供的集电极电流分流,分别传送集电极电流Ic1-Ic6。

HBT中,集电极电流随着温度的上升而上升。从而,在该温度上升无法停止的场合,集电极电流进一步上升,该增加电流又引起温度上升,发生电流无限制增加的所谓热散逸。为了防止该热散逸,配置基极镇流电阻7以及未图示的发射极镇流电阻以抑制集电极电流的增大。特别是,通过将发射极镇流电阻以及基极镇流电阻7连接到各单位晶体管Tr,可抑制由单位晶体管Tr形成的多触点双极晶体管的热分布等的不均一性引起的集电极电流Ic的不均一分布。

配置这样的晶体管元件的场合,在副集电极布线4b1-4b6中设定相等的布线阻抗,使流经其中的集电极电流Ic1-Ic6大致变得均一。该场合,如图20中圆形区域8中所示,在动作时,驱动电流引起温度的分布,即晶体管阵列的中央部分温度高、外围部分中温度低。

发生这样的温度分布时,在晶体管阵列的中央部分的单位元件区域34及44的区域中发生集电极电流集中的可能性高。发生这样的集电极电流的集中时,集电极电流Ic1-Ic6的合计的集电极电流的大部分流过单位元件区域34及44中形成的单位晶体管,该单位元件区域34及44的单位晶体管的动作电流占该最终级功率放大晶体管的动作电流的大部分。

从而,单位元件区域34及44中流过大的集电极电流时,该圆形区域8中发生热散逸,单位元件区域34及44的晶体管被破坏,从集电极布线4a向发射极布线5a及5b流过大电流,导致发生整个功率放大晶体管被破坏的问题。

为了避免这样的多触点双极晶体管中的电流集中,扩大单位晶体管的间隔,抑制单位晶体管间的热干涉,以相互热绝缘的状态配置单位晶体管,可有效降低全体的热电阻。但是,该场合中,最终级功率放大晶体管的布局面积增大,占芯片的大部分面积的最终级功率放大晶体管的面积增大,从而导致芯片尺寸增大的问题。

特别是,GaAs等的化合物半导体形成的HBT放大器的场合的成本比Si-MOSFET高,减小芯片面积从价格来说是很重要的。

另外,双频带功率放大电路中,由于GSM功率放大器及DCS功率放大器不同时动作,因而GSM功率放大器及DCS功率放大器的最终级功率放大晶体管的单位晶体管可交互配置,如特开2001-102460号公报所公开的。在该结构的场合,由于单位晶体管的邻接晶体管不动作,等价于放宽了单位晶体管的间距条件,相应地减小了热电阻,可抑制发热。

但是,GSM利用900MHz的频带,另外,DCS利用1800MHz的频带。从而,在这样交互配置单位晶体管的结构中,利用GSM功率放大器的场合下,其谐波通过最终级的功率放大晶体管的电容耦合传送到DCS功率放大器的输出结点,如图17所示,经由耦合器982及选择电路986,来自DCS功率放大器的谐波噪声分量叠加到该GSM发送信号,导致发送品质劣化的问题。

另外,只是为了减小芯片面积,而在各个区域以足够的间距条件形成DCS用及GSM用的输出晶体管的单位晶体管,且这些DCS用输出晶体管形成区域和GSM用输出晶体管形成区域相互靠近配置的场合,同样会因布线间的耦合电容引起噪声叠加,导致发送品质劣化的问题。另外,该场合中,从减小芯片面积的观点看,由于单位晶体管的间距无法取足够大,因而仍然无法充分解决电流集中的问题。

发明内容

本发明的目的在于提供不降低发送品质且可减小芯片尺寸的多频带功率放大电路。

本发明的其他目的在于提供可避免电流集中并减小芯片尺寸的多频带功率放大电路。

本发明的第1观点的放大器包括:第1输出晶体管,具有多个第1单位晶体管元件,用以输出第1频带的信号;第2输出晶体管,具有多个第2单位晶体管元件,用以输出与第1频带不同的第2频带的信号;第1输出晶体管的输出结点和第2输出晶体管的输出结点之间配置的电感元件。

本发明的第2观点的放大器包括:第1输出晶体管,具有多个第1单位晶体管元件,用以输出第1频带的信号;第2输出晶体管,具有配置成与多个第1单位晶体管元件相互包围的多个第2单位晶体管元件,输出第2频带的信号。

第1输出晶体管和第2输出晶体管的输出结点之间配置有电感元件。即使在分别构成第1及第2输出晶体管的单位晶体管元件靠近配置的场合中,对于谐波分量,通过该电感元件和寄生电容形成共振电路,输出结点间用高阻抗连接,可防止第2输出晶体管的谐波分量通过电容耦合经由第1输出晶体管传送。从而,不会降低发送品质。第1单位晶体管元件和第2单位晶体管元件靠近配置,可减小第1及第2输出晶体管的占有面积,降低芯片占有面积。

特别是,晶体管元件形成区域内中第1及第2单位晶体管元件混合配置,即使令这些单位晶体管元件的实际间距长、热电阻小,也可以防止因谐波分量的电容耦合引起噪声分量的发生。从而,不降低发送品质,可更有效地减小芯片尺寸,另外也可防止电流集中引起元件破坏的发生。

另外,通过将单位晶体管元件配置成相互包围,由于动作中的单位晶体管元件中不存在热边界,因而该动作中的晶体管区域中发生热扩散,可抑制热集中的发生,从而防止电流集中的发生。

另外,在第1及第2输出晶体管的单位晶体管元件交互配置的场合,同时动作的单位晶体管元件可以在该晶体管形成区域内分散配置,可相应减小热电阻,抑制发热,另外,可缩短单位晶体管元件的间距,从而减小芯片尺寸。

附图说明

图1是本发明的实施例1的双频带功率放大电路的芯片布局的概略示意图。

图2是说明图1所示电感元件的功能的图。

图3是本发明的实施例2的最终级功率放大晶体管的单位晶体管的配置的概略示意图。

图4是本发明的实施例2的最终级功率放大晶体管的单位晶体管的布局的更具体的示意图。

图5是本发明的实施例3的最终级功率放大晶体管的单位晶体管的布局的概略示意图。

图6是图5所示布线布局中寄生电容的概略示意图。

图7是本发明的实施例3的单位晶体管的布局的更具体的示意图。

图8是本发明的实施例4的最终级功率放大晶体管的单位晶体管的布局的概略示意图。

图9是本发明的实施例4的最终级功率放大晶体管的单位晶体管的布局的更具体的示意图。

图10是本发明的实施例5的最终级功率放大晶体管的单位晶体管的布局的概略示意图。

图11的11A及11B是单位晶体管列的热分布的概略示意图。

图12是图10所示单位晶体管配置中热分布的概略示意图。

图13是本发明的实施例5的单位晶体管的布局的更详细示意图。

图14是传统的双频带功率放大电路的构成的概略示意图。

图15是图14所示DCS功率放大器的电路结构的一例的示意图。

图16是图14所示GSM功率放大器的电路结构的一例的示意图。

图17是采用传统的双频带功率放大电路的便携装置的重要部分结构的概略示意图。

图18是传统的双频带功率放大器中最终级功率放大晶体管的芯片布局的概略示意图。

图19是传统的功率放大器的最终级功率放大晶体管的构成的概略示意图。

图20是图19所示单位晶体管的布局的示意图。

具体实施方式

[实施例1]

图1是本发明的实施例1的DCS/GSM用双频带功率放大电路的芯片布局的概略示意图。图1所示双频带功率放大电路与图18所示双频带功率放大电路在以下点中其布局不同。即,分别构成DCS用功率放大器的最终级的输出放大晶体管Trd3和GSM用功率放大器的最终级的功率放大晶体管Trg3的单位晶体管(Tr)混合配置在最终输出放大晶体管形成区域PW3内。

通过该最终输出放大晶体管形成区域PW3,DCS用焊盘区域PBD和GSM用焊盘区域PBG相对进行配置。DCS用焊盘区域PBD的焊盘与DCS最终级功率放大晶体管的集电极连接的输出布线连接,输出输出信号OUT_DCS。

DSM用焊盘区域PBG包含的焊盘与GSM用最终级功率放大晶体管的集电极连接的输出布线连接,输出输出信号OUT_GSM。

通过相对地配置DCS焊盘区域PBD和GSM焊盘区域PBG,DCM信号输出结点和GSM信号输出结点可尽可能地分离,防止它们的电容耦合,确立频带间的隔离。

而且,该GSM用焊盘区域PBG及DCS用焊盘区域PBD的焊盘(输出布线)通过电感元件Lcc及电容元件Ccc的串联体相互连接。该图1所示双频带功率放大电路的芯片布局中,其他布局与图18所示双频带功率放大电路的芯片布局相同,对应部分附上同一参照编号,省略其详细说明。

最终输出放大晶体管形成区域PW3中,通过混合配置构成DCS功率放大晶体管和GSM功率放大晶体管的单位晶体管,可以使同时动作的单位晶体管间的距离变长,降低热电阻,防止由热集中引起电流集中。另外,混合配置单位晶体管,不必加长邻接单位晶体管间的距离以降低热电阻,因而与传统相比可以较短,且与传统相比可以减小最终级功率放大晶体管的合计的面积。

DCS用焊盘区域PBD的焊盘与用该最终输出放大晶体管形成区域PW3中配置的单位晶体管构成的功率放大晶体管Trd3的集电极连接。另一方面,GSM用焊盘区域PBG的焊盘与最终输出放大晶体管形成区域PW3中配置的功率放大晶体管Trg3的集电极连接。

如上述,最终输出放大晶体管形成区域PW3中,混合配置有构成功率放大晶体管Trd3及Trg3的单位晶体管。后面将详细说明具体的布局,由于相互连接这些单位晶体管的DCS用副集电极线及DSM用副集电极线靠近配置,因此这些布线间存在耦合电容。

图2是最终级的功率放大晶体管Trd3及Trg3的输出部分结构的电气的等价电路图。图2中,功率放大晶体管Trd3及Trg3的集电极结点CND及CNG之间连接有寄生电容Cpr。另一方面,这些集电极结点CND及CNG之间串联连接有电容元件Ccc及电感元件Lcc。电容元件Ccc是用以防止功率放大晶体管Trd3及功率放大晶体管Trg3的直流集电极偏置电压经由电感元件传送的直流切断用(交流短路)电容元件。从而,该电容元件Ccc的高频区域中的阻抗分量与这些寄生电容Cpr及电感元件Lcc的阻抗分量相比可以忽略。该场合,集电极结点CNG及CND间的阻抗Z用下式表示。

Z=1/(j·ω·Cpr+1/j·ω·Lcc)

当共振条件成立时,阻抗Z的绝对值达到最大。该共振条件由下式表示。

从而,若选择1800MHz作为该共振频率ω,则GSM的功率放大器动作,即使存在该输出频带的900MHz的2次谐波分量即1800MHz的分量,也可通过该并联共振电路电气分离集电极结点CND及CNG。从而,可防止2次谐波分量从功率放大晶体管Trg3的集电极结点CNG传送到功率放大晶体管Trd3的集电极结点CND。

从而,通过将该共振频率ω设定成DCS的频带的频率分量,GSM动作时,可通过并联共振电路使得集电极结点CND及CNG之间的阻抗无限大,防止2次谐波分量传送到谐波分量的DCS功率放大器的输出结点。从而,通常的双频带放大电路中,如图17所示,在次级设置高频耦合器以及选择电路,即使是该GSM功率放大器的输出信号从高频耦合器经由选择电路传送到天线端子的场合,也能够可靠地防止谐波噪声分量从该DCS功率放大器的输出结点经由高频耦合器982以及选择电路986传送到天线。

最终输出放大晶体管形成区域PW3中,混合配置最终级功率放大晶体管Trd3及Trg3的单位晶体管,这些单位元件区域的实际的间距条件变小,与各自配置DCS用最终级功率放大晶体管及GSM用最终级功率放大晶体管的结构相比,减小了最终输出放大晶体管形成区域PW3的占有面积。另外,由于同时动作的单位晶体管间的距离变长,等价于减小了热电阻,抑制了发热,防止由发热引起电流集中。通过单位晶体管的混合配置,即使存在寄生电容Cpr,通过在输出结点间配置电感元件Lcc、用该电感元件Lcc和寄生电容对GSM的2次谐波分量形成无限大的阻抗,也能够可靠地防止噪声分量叠加到GSM发送信号,改善发送品质。

另外,该电感元件Lcc的电感值可以适当设定成与实际的寄生电容Cpr的电容值对应。另外,电容元件Ccc可用于实现切断集电极结点CND的偏置电压的直流分量的机能,其电容值可设定成在1800NHz的频带中,令阻抗分量的绝对值1/ω·Ccc与电感元件Lcc的阻抗分量的绝对值ω·Lcc相比可忽略不计的足够小的值。

如上所述,根据本发明的实施例1,双频带方式功率放大电路中,最终级的功率放大晶体管的单位晶体管混合配置在同一晶体管形成区域内,且它们的输出级的功率放大晶体管的输出结点之间配置电感元件,使得其与寄生电容形成并联共振电路,可以减小芯片尺寸且防止2次谐波分量引起的噪声叠加到发送信号,并在不降低发送品质及不导致电流集中的情况下减小芯片尺寸。

[实施例2]

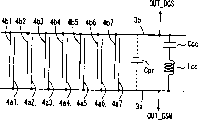

图3是本发明的实施例2的最终级的功率放大晶体管的单位晶体管Tr的配置的概略示意图。图3中,单位晶体管Tr配置成多个行和列。图3中,作为一例,表示了单位晶体管Tr配置成6行7列的布局。

该晶体管阵列中,排列成奇数行R#1、R#3以及R#5的单位晶体管Tr用作DCS功率放大器的最终级功率放大晶体管。另一方面,排列成偶数行R井2、R#4以及R#6的单位晶体管Tr用作GSM功率放大器的最终级功率放大晶体管的构成要素。图3中,用作DCS功率放大晶体管的构成要素的单位晶体管Tr用符号“D”表示,用作GSM功率放大器的最终级功率放大晶体管的构成要素的单位晶体管Tr用符号“G”表示。

单位晶体管D的集电极共同连接到DCS输出信号线3b,单位晶体管G的集电极共同连接到GSM输出信号线3a。这些输出信号线3a以及3b之间,串联连接有切断直流用的电容元件Ccc和与晶体管阵列的寄生电容共同构成并联共振电路的电感元件Lcc。

图3所示单位晶体管阵列中,沿列方向交互配置DCS用的单位晶体管D和GSM用的单位晶体管G。DCS功率放大器和GSM功率放大器选择其一进行动作。例如,DCS用单位晶体管D动作时,GSM用单位晶体管G为非动作状态,不进行电流驱动。从而,等价于DCS单位晶体管D的列方向的间距变长,可以减小该列方向的热电阻,防止热集中,相应地减少电流集中。

即使单位晶体管Tr以最小间距Pmin排列,DCS用单位晶体管D以及GSM用单位晶体管G的列方向的间距为2Pmin,与各个DCS用单位晶体管D及GSM用单位晶体管G分别配置在不同区域的场合相比,可以以最小间距配置单位晶体管,减小占功率放大器大面积的最终级晶体管的配置区域的面积,并减小芯片尺寸。

另外,通过利用电感元件Lcc,相互连接DCS用单位晶体管D及GSM用单位晶体管G各自的集电极区域的布线即使靠近配置,也可以通过集电极布线间寄生电容和电感元件Lcc形成对GSM的2次谐波的并联共振电路。从而,即使发送900MHz的GSM频带的发送信号,对于该2次谐波分量,并联共振电路的阻抗为无限大,防止来自GSM输出信号线3a的GSM2次谐波分量漏泄到DCS输出信号线3b上(并联共振电路的共振频率设定成DCS频带)。

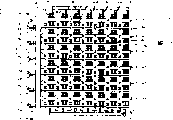

图4是本发明实施例2的最终级功率放大晶体管的布局更具体的示意图。图4中,单位晶体管Tr排列配置成6行7列。第1行R#1中,分别配置形成单位晶体管Tr的单位元件区域11-17,第2行R#2中,配置单位元件区域21-27。第3行R#3中,配置单位元件区域31-37,第4行R#4中,在行方向上排列配置单位元件区域41-47。第5行R#5中,在行方向上排列配置单位元件区域51-57,第6行R#6中,在行方向上排列配置单位元件区域61-67。

这些各个单位元件区域11-17至61-67中,形成用异质结双极晶体管HBT构成的单位晶体管Tr,并分别形成基极区域、集电极区域以及发射极区域。

各个行R#1-R#6中,沿行方向配置副发射极布线5c1-5c6。这些副发射极布线5c1-5c6分别通过发射极镇流电阻电气连接到对应行的单位晶体管元件区域的发射极区域。图4中,这些发射极镇流电阻由外延层构成,在2维布局中配置成与各副发射极布线5c1-5c6重合。这些发射极镇流电阻也可以用扩散电阻构成。

副发射极布线5c1-5c6与在该晶体管元件阵列外部沿列方向上延伸配置的发射极布线5a及5b连接。这些发射极布线5a及5b与供给接地电压的接地结点连接。DCS用功率放大晶体管及GSM用功率放大晶体管的发射极通过未图示的发射极镇流电阻共同连接到接地结点。

晶体管元件区域11-17至61-67的各个基极区域与基极镇流电阻7电气连接。单位晶体管行R#1、R#3以及R#5中,在行方向上延伸,分别配置了副基极布线2b1、2b2以及2b3,它们通过各个对应行中的基极镇流电阻与对应行的单位元件区域的基极区域电气连接。单位元件行R#2、R#4以及R#6中,在行方向上延伸,配置GSM用的副基极布线2a1、2a2以及2a3,它们通过各个对应行中的基极镇流电阻7与对应行的单位元件区域的基极区域电气连接。

GSM用副基极布线2a1-2a3共同经由通孔8a与在列方向上延伸配置的GSM用基极布线1a连接。另外,DCS用副基极布线2b1~2b3经由通孔8b与在列方向上延伸配置的DCS用基极布线1b电气连接。在DCS基极布线1b中传送DCS用输入信号以及DCS用基极偏置电压。在GSM用基极布线1a中传送来自前级的级间匹配电路的GSM信号和来自基极偏置电压控制电路的基极偏置电压。这些基极布线1a及1b互相邻接,在列方向上延伸配置。

对应单位元件区域的各个列,DCS用副集电极布线4b1-4b7在列方向上延伸配置,另外,与副集电极布线4b1-4b7相互邻接,且在列方向上延伸配置有GSM用副集电极布线4a1-4a7。这些副集电极布线4b1-4b7分别经由通孔8b与对应列中的DCS用单位元件区域的集电极区域电气连接。另外,副集电极布线4a1-4a7分别经由通孔8a与对应列中的GSM用单位元件区域的集电极区域电气连接。

从而,该配置中,DCS用的通孔8b在列方向中隔行配置,另外,GSM用的通孔8a在列方向中隔行配置。

副集电极布线4b1-4b7连接到在晶体管元件阵列的一侧沿列方向上延伸配置的DCS用集电极布线3b,另外,副集电极布线4a1-4a7连接到该晶体管元件阵列上与DCS用集电极布线3b相对地在列方向上延伸配置的集电极布线3a。集电极布线3a及3b之间串联连接有直流切断用(交流短路用)的电容元件Ccc和电感元件Lcc。

图4中,副集电极布线4a1-4a7和副集电极布线4b1-4b7相互邻接并在列方向上延伸,且在行方向上交互配置。

如该图4所示,单位晶体管的元件区域的布局中,由于副集电极布线4b1-4b7及4a1-4a7分别配置于各列,虽然副集电极布线引起面积增大,但是通过在列方向中交互配置GSM用单位晶体管和DCS用单位晶体管,可以使GSM用单位晶体管的列方向的距离以及DCS用单位晶体管的列方向的距离变大,即使令单位晶体管元件的列方向的间距变得很小,由于热电阻变得很小,因而可以防止热集中。因而,与DCS用晶体管及GSM用晶体管分别配置在不同区域的场合相比,最终级的功率放大晶体管的合计尺寸可以显著降低,减小芯片尺寸。

另外,DCS用副集电极布线4b1-4b7和GSM用副集电极布线4a1-4a7相互邻接地进行配置,即以所谓“叉指型”的形状配置副集电极布线,集电极间的寄生电容变得比较大。该场合,通常产生称为频带间隔离的问题。即,GSM动作时产生的900MHz的2倍的谐波分量1800MHz通过DCS的输出级匹配电路,其一部分可能从天线辐射。这是因为,由于DCS/GSM用功率放大电路中只配置了耦合器而没有配置类似PDC的频带间隔离器,通过混合配置的叉指型电容的形成,有可能容易地产生该频带间隔离的问题。

DCS用副集电极布线4b1-4b7及GSM用集电极布线4a1-4a7的寄生电容产生的集电极布线3a及3b间的布线间电容和电感元件Lcc形成并联共振电路,在DCS频带中进行共振动作。从而,对于GSM动作时发生的GSM2次谐波分量,该并联共振电路的阻抗变成无限大,可以防止GSM的2次谐波从DCS集电极布线3b经由输出级匹配电路漏泄。

如上所述,根据本发明的实施例2,GSM用单位晶体管及DCS用单位晶体管在列方向中交互配置,最终级功率放大晶体管的合计尺寸几乎不增加,可以有效地防止热集中引起的电流集中,避免单位晶体管的烧毁等的问题。

另外,外部配置有用以构成DCS频带中的并联共振电路的电感元件Lcc,即使DCS用副集电极布线和GSM用副集电极布线邻接地进行配置的场合,通过该并联共振电路也可以可靠地防止GSM谐波漏泄到DCS输出部分,确实防止频带间隔离的劣化,抑制发送品质的劣化。

另外,对于DCS单位晶体管和GSM单位晶体管的配置顺序,只要是沿列方向交互排列这些单位晶体管,则其配置顺序可以是任意的。

另外,分别构成DCS最终级功率放大晶体管和GSM最终级功率放大晶体管的单位晶体管的数目可以分别根据DCS功率放大器以及GSM功率放大器所要求的功率条件适当设定,这些最终级功率放大晶体管的单位晶体管的数目可以相同也可以不同(参照图18)。

[实施例3]

图5是根据本发明的实施例3的单位晶体管的配置的概略示意图。图5中,单位晶体管排列成矩阵状。在各个单位晶体管行R#1-R#6中,构成DCS用功率放大晶体管的单位晶体管D和构成GSM用功率放大晶体管的单位晶体管G交互配置。另外,各个单位晶体管列C#1-C#7中,DCS单位晶体管D和GSM单位晶体管G也交互配置。即,该图5所示单位晶体管元件的配置中,各个行方向以及列方向中,DCS单位晶体管D和GSM单位晶体管G交互进行配置。

为了相互连接该GSM单位晶体管G的集电极,各个单位晶体管列C#1-C#7中,副集电极布线4a1-4a7在列方向上延伸配置,另外,为了连接DCS用单位晶体管D的集电极,副集电极布线4b1-4b7在列方向上延伸配置。这些副集电极布线4a1-4a7共同与GSM输出线3a连接,副集电极布线4b1-4b共同连接到DCS输出线3b。这些输出线3a以及3b之间,串联连接有直流切断用、即交流短路用的电容元件Ccc和电感元件Lcc。

该图5所示布局中,各个单位晶体管列C#1-C#中,副集电极布线4ai以及4bi(i=1-7)邻接地进行配置。从而,如图6所示,与实施例2的布局同样,形成GSM用副集电极布线4a1-4a7与DCS用副集电极布线4b1-4b7分别交互配置的布局,即由输出信号线3a以及3b形成所谓叉指型电容。

若令该叉指型电容的电容值为电容Cpr,则电容Cpr和电感元件Lcc构成DCS频带的并联共振电路。从而,GSM动作时,通过寄生电容Cpr和电感元件Lcc形成的并联共振电路,由于GSM频带的2次谐波分量通过该并联共振电路、经由实质上无限大的阻抗与DCS输出信号线3b连接,可以防止GSM频带的2次谐波分量漏泄到该DCS输出信号线3b上。

图7是本发明实施例3的单位晶体管的布局的概略示意图。图7中也与图4所示实施例2的单位元件的布局同样,形成单位晶体管Tr的单位元件区域11-17至61-67配置成6行7列。

与各个单位元件行R#1-R#6对应,配置副发射极布线5c1-5c6。这些副发射极布线5c1-5c6分别与在单位元件区域外部沿列方向延伸配置的发射极布线5a及5c连接。这些发射极布线5a以及5b与供给接地电压的接地结点连接。

各个单位元件行R#1-R#6中,由于DCS单位晶体管D和GSM单位晶体管G交互配置,各个单位元件行R#1-R#6中,副基极布线2b1-2b6及2a1-2a6在行方向上延伸配置。副基极布线2a1-2a6经由通孔8a分别连接到与对应的单位元件行中每隔一个的单位元件区域的基极区域连接的基极镇流电阻7。另外,副基极布线2b1-2b6经由通孔8b分别连接到与对应的单位元件行的单位元件的基极区域连接的基极镇流电阻7。

副基极布线2a1-2a6经由通孔8a与元件阵列区域外部沿列方向延伸配置的基极布线1a连接。副基极布线2b1-2b6经由通孔8b连接到与基极布线1a邻接并在列方向上延伸配置的基极布线1b。GSM输入信号(前级的匹配电路输出信号和基极偏置控制电压)传送到基极布线1a,DCS输入信号(前级的匹配电路输出信号和基极偏置控制电压)传送到基极布线1b。

该单位元件阵列区域中,由于DCS单位晶体管D和GSM单位晶体管G分别在行方向及列方向中交互配置,对于通孔8a及8b,也在元件阵列区域内中的行方向及列方向中交互配置DCS用通孔8b和GSM用通孔8a,各个单位元件列C#1-C#7中,在列方向上延伸配置副集电极布线4a1-4a7及4b1-4b7。该副集电极布线4a1-4a7经由通孔8a电气连接到对应列中每隔一个的单位元件区域的集电极区域。副集电极布线4b1-4b7分别经由通孔8b电气连接到对应列中每隔一个的单位元件区域的集电极区域。对于该副集电极布线4a1-4a7及4b1-4b7,也在行方向及列方向中交互配置通孔8a及8b。

副集电极布线4a1-4a7共同连接到构成GSM用输出信号线的集电极布线3a,副集电极布线4b1-4b7共同连接到构成DCS用输出信号线的集电极布线3b。

集电极布线3a以及3b之间,串联连接有交流短路用(直流切断用)的电容元件Ccc和用以构成共振电路的电感元件Lcc。

该图7所示布线布局中,除列方向以外,还在行方向中交互配置DCS用单位晶体管D和GSM用单位晶体管G。从而,各个单位元件行R#1-R#6中,由于副基极布线2a(2a1-2a6)以及2b(2b1-2b6)邻接地进行配置,单位元件阵列区域的面积增大了该副基极布线的占有面积部分。但是,由于行方向中交互配置了DCS用单位晶体管以及GSM用单位晶体管,即使以最小的间距配置单位晶体管元件区域,动作时行方向及列方向中邻接的单位晶体管为非作动状态。从而,等价于使单位元件问的间距变长,可充分减小热电阻,在行方向以及列方向上分散热量,避免发热引起电流集中。因而,晶体管元件阵列的占有面积与传统相比可显著降低(由于行方向上单位元件间距也减小)。

另外,与实施例2和同样,由于输出信号线间生成的叉指型电容的寄生电容和电感元件Lcc在DCS频带中形成并联共振电路,因此GSM动作时,可防止2次谐波分量漏泄到DCS用输出信号线3b。

如上所述,根据本发明的实施例3,在行方向及列方向交互配置DCS用单位晶体管以及GSM用单位晶体管,可以在不增大单位元件区域的间距情况下降低行方向及列方向的GSM用单位晶体管及DCS用单位晶体管的热电阻,最终级电流放大晶体管的合计尺寸几乎不增加,可有效地避免电流集中。

另外,在集电极布线3a及3b间配置电感元件Lcc,在GSM动作时的DCS频带中,由输出信号线3a以及3b间的寄生电容和电感元件形成并联共振电路,可以防止GSM频带的2次谐波分量漏泄到DCS信号输出电路,确实抑制频带间隔离的劣化。

另外,DCS最终级功率放大晶体管的单位晶体管的数目以及GSM最终级功率放大晶体管的单位晶体管的数目可以根据所要求的功率条件分别适当设定。

[实施例4]

图8是本发明的实施例4的单位晶体管的配置的概略示意图。图8中,单位晶体管配置成6行7列。行方向中,GCS用的单位晶体管G和DCS用的单位晶体管D交互配置。列方向中,排列配置一种单位晶体管。图8中,在单位元件列C#1、C#3、C#5以及C#7中的列方向上排列配置GCS单位晶体管G,在单位元件列C#2、C#4以及C#6中,排列配置DCS单位晶体管D。

GSM单位晶体管G的集电极区域经由副集电极布线4a1-4a4与构成GSM用输出信号线的集电极布线3a连接。相互连接DCS单位晶体管D的集电极区域的副集电极布线4b1、4b2以及4b3分别与单位元件列C#2、C#4以及C#6对应配置,且与构成DCS用输出信号线的集电极布线3b连接。

这些DCS用输出信号线(DCS集电极布线)3b和GSM输出信号线(GSM集电极布线)3a之间,串联连接有直流切断用的电容元件Ccc和并联共振电路构成用的电感元件Lcc。

该图8所示单位晶体管的配置中,沿行方向交互配置GSM用单位晶体管G和DCS用单位晶体管D。动作时,由于只有GSM单位晶体管G或DCS单位晶体管D的一方动作,因而可以充分确保这些GSM单位晶体管G和DCS单位晶体管D的列方向的间距,降低这些晶体管的行方向上的热电阻,防止由热引起电流集中。

另外,单位元件列C#1至C#7中,交互配置GSM用副集电极布线4a1至4a4和DCS用副集电极布线4b1至4b3。该场合中也在输出信号线3a以及3b之间构成叉指型电容。通过该叉指型电容和电感元件Lcc构成DCS频带中的并联共振电路。从而,GSM动作时,可防止该2次谐波(1800MHz)分量经由DCS输出信号线3b漏泄到DCS输出电路,经由该DCS输出电路漏泄到天线端子,抑制频带间隔离的劣化。

图9是本发明实施例4的单位晶体管的布局的更具体的配置的示意图。图9中,单位晶体管Tr在排列配置成6行7列的单位元件区域11-17至61-67中形成。

与各个单位元件行R#1-R#6对应,配置副发射极布线5c1-5c6。这些副发射极布线5c1-5c6经由未图示的发射极镇流电阻电气连接到各个对应行的单位元件的发射极区域,且连接到该元件阵列区域外部在列方向上延伸配置的发射极布线5a以及5b。

另外,与各个单位元件行R#1-R#6对应,在行方向上延伸配置副基极布线2a1、2b1至2a6、2b6。行方向中,由于交互配置了DCS单位晶体管和GSM单位晶体管,因而各个单位元件行R#1-R#6分别配置2根副基极布线。

各个单位元件行R#1-R#6中,副基极布线2a1、2b1至2a6、2b6的成对副基极布线交互经由通孔8a及8b电气连接到基极镇流电阻7。从而,各个单位元件行R#1-R#6中,对副基极布线2a(2a1-2a6)以及2b(2b1-2b6)交互配置通孔8a及8b。列方向中,通孔8a及8b排列成列,在各行中形成。

副基极布线2a1-2a6经由通孔8a共同连接到元件阵列区域外部在列方向上延伸配置的基极布线1a,另外副基极布线2b1-2b6经由通孔8b共同连接到与基极布线1a邻接且在列方向上延伸配置的基极布线1b。

分别向基极布线1a以及1b提供GSM输入信号及DCS输入信号。

与单位元件列C#1、C#3、C#5以及C#7对应,在列方向上延伸配置副集电极布线4a1-4a4。在各个对应的单位元件列中,副集电极布线4a1-4a4经由通孔8a电气连接到单位元件区域的集电极区域。副集电极布线4a1-4a4共同连接到构成GSM输出信号线的集电极布线3a。

在各个单位元件列C#2、C#4以及C#6中,在列方向上延伸配置副集电极布线4b1、4b2以及4b3。这些各个副集电极布线4b1-4b3经由通孔8b电气连接到对应的单位元件列中的单位元件区域的集电极区域。副集电极布线4b1-4b3共同连接到构成DCS输出信号线的集电极布线3b。

集电极布线(输出信号线)3a以及3b之间,串联连接有电容元件Ccc以及电感元件Lcc。

该图9所示布线布局中,在各个单位元件列C#1-C#7中仅仅配置一根副集电极布线。但是,这些副集电极布线4a1-4a4及4b1-4b3在行方向中交互配置,仅仅间隔了单位元件区域的行方向的间距,用同一布线层的布线构成。从而,构成输出信号线的集电极布线3a及3b即使是通过单位元件阵列区域而相对配置的场合中,也会形成“叉指型电容”,与前面的实施例2及3同样,存在寄生电容。

GSM动作时由电容耦合导致谐波分量发生的场合,由该寄生电容和电感元件Lcc构成并联共振电路,令集电极布线3a及3b间的阻抗为最大,可防止电容耦合引起信号的传播,并防止GSM动作时的2次谐波分量经由集电极布线3b漏泄到DCS输出电路。

另外,该实施例4中,构成最终级的DCS功率放大晶体管的单位晶体管G的数目和构成最终级的功率放大晶体管的单位晶体管D的数目不同。这些单位晶体管的数目根据DCS功率放大器以及GSM功率放大器中分别要求的驱动功率适当设定。从而,这些最终级的GSM功率放大晶体管及DCS功率放大晶体管的单位晶体管的数目也可以相等。而且,该场合中,仅仅通过在图9的行方向的外侧区域的列方向上排列配置构成单位晶体管D(其构成DCS功率放大晶体管)的单位元件区域,可以使分别构成这些DCS功率放大晶体管以及GSM功率放大晶体管的单位晶体管D及G的数目相等。

如上所述,根据本发明的实施例4,在排列成矩阵状的单位晶体管元件中,由于行方向中交互配置了DCS单位晶体管以及GSM单位晶体管,因而可以使行方向中的DCS单位晶体管D以及GSM单位晶体管G的间距变长,可降低这些最终级输出晶体管的热电阻,避免由热集中引起电流集中的发生。

另外,为了分别取出GSM输出信号以及DCS输出信号,由于相互连接单位晶体管的集电极布线进行平行布线,因而即使在寄生电容存在的场合,通过将与寄生电容在DCS频带中构成并联共振电路的电感元件Lcc连接到集电极布线(输出信号线)间,也可以防止GSM动作时的2次谐波分量经由DCS输出电路传送到天线端子,防止频带间隔离的劣化。

[实施例5]

图10是本发明的实施例5的单位晶体管的配置的概略示意图。图10中,单位晶体管与前面的实施例2到4同样,配置成6行7列。单位晶体管阵列中,GSM单位晶体管G以及DCS单位晶体管D交互排列成相互包围的环状。

即,图10所示配置中,单位晶体管元件阵列的中心部分中,6个GSM用单位晶体管G相互邻接配置成矩阵状。环状配置DCS用单位晶体管D,以包围这些GSM单位晶体管G。而且,再环状配置GSM用单位晶体管G,以包围这些DCS单位晶体管D。

与各个单位晶体管列对应,配置副集电极布线4b1-4b6以及副集电极布线4a1-4a7。副集电极布线4a1-4a7以及4b1-4b6分别连接到对应的单位晶体管列中对应的单位晶体管的集电极区域。副集电极布线4a1-4a7共同连接到GSM输出信号线(集电极布线)3a,另外副集电极布线4b1-4b6共同连接到DCS输出信号线(集电极布线)3b。GSM输出信号线(集电极布线)3a和DCS输出信号线(集电极布线)3b之间,串联连接电容元件Ccc和电感元件Lcc。

如图11A、11B所示,在环状配置同一种类的单位晶体管的场合,与通常的配置相比,可以抑制热边界(热分布的边界)的存在。

即,如图11A所示,单位晶体管Tr连续配置、同时动作的场合,由于两端的单位晶体管Tr外部不存在动作元件,变成低温区域。另一方面,由于这些同时动作的单位晶体管Tr由发热产生热的传播,如图11B所示,发生中央部分的单位晶体管Tr温度最高、晶体管列的端部(热边界)温度低的热分布。在产生这样的热分布的场合,中央的单位晶体管因热集中引起电流集中的可能性很高。

但是,如图12所示,在同时动作的单位晶体管环状配置的场合,这些同时动作单位晶体管的区域中,热边界不存在,可抑制热分布的存在,使这些单位晶体管在均一的温度下同时动作,抑制因热集中引起的电流集中。

从而,该单位元件阵列内中配置同一种类的单位晶体管的场合,该四方的晶体管阵列端部区域形成热边界,晶体管阵列发生热分布,中央部分的单位晶体管产生热集中的可能性变高。但是,如图10所示,通过环状配置同时动作的单位晶体管,热边界变得不存在,同时动作的单位晶体管的动作温度变得均一,抑制了热集中。

另外,由于同时动作的单位晶体管的区域被非动作状态的单位晶体管包围,所有各单位晶体管至少与2方向上的非动作状态的单位晶体管邻接,从而可以降低热电阻,等价于使各单位晶体管的间距变长,防止热集中的发生。

由于该图10所示配置中也在列方向上延伸配置副集电极布线4b1-4b6以及4a1-4a7,为了防止该布线电容引起电容耦合,配置用以构成DCS频带中的并联共振电路的电感元件Lcc。可以抑制电流集中、改善频带间隔离的特性的劣化,另外,由于不同种类的单位晶体管混合配置,可以减小芯片的尺寸。

图13是本发明实施例5的最终级输出放大晶体管的单位晶体管布局的更具体的示意图。图13中,单位元件区域11-17至61-67配置成6行7列。与单位元件行对应,分别配置副基极布线2a1-2a6,且与这些副基极布线2a1-2a6分别邻接、在列方向上延伸配置副基极布线2b1-2b6。

副基极布线2a1经由通孔8a共同连接到列方向上延伸的基极布线1a。另外,副基极布线2b1-2b6经由通孔8b共同连接到列方向上延伸的基极布线1b。

与单位元件列对应,GSM用副集电极布线4a1-4a7分别在列方向上延伸配置,另外,与这些副集电极布线4a1-4a7分别邻接、配置在列方向上延伸的DCS用副集电极布线4b1-4b7。

与存储元件行对应,配置副发射极布线5c1-5c6。这些副发射极布线5c1-5c6共同连接到列方向上延伸的发射极布线5a及5b。副发射极布线5c1-5c6经由未图示的发射极镇流电阻电气连接到各个对应的单位元件列的单位元件区域中形成的发射极区域。

副基极布线2a1-2a6、2b1-2b6和副集电极布线4a1-4a6、4b1-4b6分别经由通孔8a及8b电气连接到对应的单位元件区域的基极区域及集电极区域,使得GSM用单位晶体管及DCS单位晶体管配置成相互包围的环状。即,单位元件区域11-17中,基极镇流电阻7经由通孔8a与副基极布线2a1连接,另外,各个集电极区域经由通孔8a与副集电极布线4a1-4a7连接。

第2行中,单位元件区域21及27的各个基极区域经由基极镇流电阻及通孔8a与副基极布线2a2电气连接,各个集电极区域经由通孔8a与副集电极布线4a1及4a7电气连接。单位元件区域22-26的各个基极区域经由基极镇流电阻及通孔8b与副基极布线2b2电气连接,另外,各个集电极区域经由通孔8b与副集电极布线4b2-4b6电气连接。

第3行中,单位元件区域31、33-35及37的各个基极区域经由基极镇流电阻及通孔8a与副基极布线2a3电气连接,各个集电极区域经由通孔8a与副集电极布线4a1、4a3-4a5及4a7电气连接。单位元件区域32及36的各个基极区域经由基极镇流电阻及通孔8b与副基极布线2b3电气连接,各个集电极区域经由通孔8b与副集电极布线4b2及4b6电气连接。

第4行中,与第3行同样,单位元件区域41、43-45及47的各个基极区域经由基极镇流电阻以及通孔8a与副基极布线2a4电气连接,各个集电极区域经由通孔8a与副集电极布线4a1、4a3-4a5及4a7电气连接。单位元件区域42及46的各个基极区域经由基极镇流电阻及通孔8b与副基极布线2b4电气连接,各个集电极区域经由通孔8b分别与副集电极布线4b2及4b6电气连接。

第5行中,单位元件区域51及57的各个基极区域经由基极镇流电阻以及通孔8a与副基极布线2a5电气连接,且各个集电极区域经由通孔8a与副集电极布线4a1以及4a7电气连接。单位元件区域52-56的各个基极区域经由基极镇流电阻7及通孔8b与副基极布线2b5电气连接,各个集电极区域经由通孔8b与副集电极布线4b2-4b6电气连接。

第6行中,元件区域61-67的各个基极区域经由基极镇流电阻以及通孔8a与副基极布线2a6电气连接,且各个集电极区域经由通孔8a与副集电极布线4a1-4a7连接。

从而,如图13所示,通过将单位元件区域排列成矩阵状、且在各行中配置副发射极布线及副基极布线、在各列中配置副集电极布线,可将DCS单位晶体管及GSM单位晶体管配置成环状,只是它们的接触位置发生了变更。

另外,在该图10及图13所示单位晶体管元件的配置中,为了进行频带间隔离而配置类似PDC的隔离器的场合,没有必要特别设置用以形成并联共振电路的电感元件Lcc。

另外,在图11以及图13所示单位晶体管元件的配置中,可根据GSM用功率放大晶体管及DCS用功率放大晶体管所要求的输出功率适当设定单位晶体管的数目。

如上所述,根据本发明的实施例5,通过在单位元件阵列内将GSM单位晶体管及DCS单位晶体管配置成相互包围的环状,不会增大形成单位晶体管的单位元件区域的间距,可以避免电流集中,减小芯片的尺寸。

另外,在DCS用及GSM用的副集电极布线邻接地进行配置的场合,由电感元件构成DCS频带中的并联共振电路,GSM动作时,可防止该2次谐波漏泄到DCS功率放大器的输出结点、经由DCS输出电路传送到天线,充分抑制频带间隔离的劣化。

[其他适用例]

上述的说明中,对作为功率放大器的构成要素的HBT进行了说明。但是,对于包含有以MOSFET及MESFET等的绝缘栅型场效应晶体管代替该HBT作为构成要素的功率放大器,通过应用本发明,也可获得同样的效果。

另外,上述的说明中,作为双频带功率放大器,说明了GSM/DCS功率放大器。但是,不限于通信方式,只要是放大频带互不相同的多个频带的信号的多频带功率放大电路,都可以应用本发明。

另外,在配置并联共振电路的场合,在双频带的频带中,只要是一方的频带的谐波分量包含于另一方的频带的分量中的结构,都可以应用本发明。

另外,本发明一般适用于进行多个频带的信号的功率放大的多频带功率放大器。

[发明的效果]

如上所述,根据本发明,通过在单位元件阵列区域内分散配置多频带功率放大器的最终级的功率放大晶体管的各单位晶体管元件,不会增加最终级的功率放大晶体管的合计尺寸,可以使其热电阻变小,防止发热引起的电流集中,并防止单位晶体管的烧毁。

另外,即使是为了分别取出多频带的各信号而使输出信号布线靠近配置的场合,也可通过在该输出信号线间配置电感元件,在一方的频带的信号输出动作时,可以防止其谐波分量通过电容耦合漏泄到另一方的输出信号线上,能够可靠地抑制频带间隔离的劣化。

Claims (12)

1.一种放大器,包括:

第1输出晶体管,具有多个第1单位晶体管元件,用以输出第1频带的信号;

第2输出晶体管,具有多个第2单位晶体管元件,用以输出与所述第1频带不同的第2频带的信号;

所述第1输出晶体管的输出结点和所述第2输出晶体管的输出结点之间耦合的电感元件。

2.如权利要求1所述的放大器,其特征在于,所述第1及第2输出晶体管至少包含一处用以在沿某一方向排列的2个第1单位晶体管元件之间形成一个第2单位晶体管元件的部分。

3.如权利要求1或2所述的放大器,其特征在于,所述第1输出晶体管的输出结点和所述第2输出晶体管的输出结点之间还配置有与所述电感元件串联的电容元件。

4.如权利要求2所述的放大器,其特征在于,所述第1单位晶体管元件和所述第2单位晶体管元件沿着第1方向和与所述第1方向正交的第2方向中至少一个方向交互配置。

5.如权利要求2所述的放大器,其特征在于,所述第1单位晶体管元件和所述第2单位晶体管元件沿着第1方向和与所述第1方向正交的第2方向交互配置。

6.如权利要求2所述的放大器,其特征在于,所述第1单位晶体管元件和所述第2单位晶体管元件交互配置成相互包围。

7.如权利要求1所述的放大器,其特征在于,所述多个第1单位晶体管元件和所述多个第2单位晶体管元件沿着第1方向和与所述第1方向正交的第2方向排列配置,分别包含有第1导通结点、第2导通结点以及控制结点,

所述第1输出晶体管还包括:

多根第1布线,在所述第1方向上延伸配置,用以相互电气连接所述多个第1单位晶体管元件的第1导通结点;

多根第2布线,在所述第2方向上延伸配置,用以相互电气连接所述多个第1单位晶体管元件的第2导通结点;

多根第3布线,在所述第2方向上延伸,用以相互电气连接所述第1单位晶体管元件的控制结点;

多根第4布线,在所述第2方向上延伸,与所述第1布线电气连接并形成所述第1输出晶体管的输出结点;

所述第2输出晶体管还包括:

第5布线,在所述第1方向上延伸配置且在所述第2方向上与所述第1布线交互配置,用以相互电气连接所述第2单位晶体管元件的第1导通结点;

多根第6布线,在所述第2方向上延伸且与所述第2布线共同配置,用以相互电气连接所述多个第2单位晶体管元件的第2导通结点;

多根第7布线,在所述第2方向上延伸且在所述第1方向上与所述第3布线交互配置,用以相互电气连接所述第2单位晶体管元件的控制结点;

第8布线,与所述第4布线相对地在所述第2方向上延伸配置,与所述第5布线电气连接并形成所述第2输出晶体管的输出结点;

所述第2布线和所述第6布线与用以传送规定电压的基准电压线相互连接,而且,

所述第1布线和第5布线在第1方向和第2方向中至少一个方向交互连接到对应的单位晶体管元件。

8.如权利要求7所述的放大器,其特征在于,所述第1及第5布线分别配置成对应于所述第1方向中排列配置的单位元件列。

9.如权利要求1所述的放大器,其特征在于,所述第1频带包含有所述第2频带的频率分量的整数倍的频率分量。

10.一种放大器,它包括:

第1输出晶体管,具有多个第1单位晶体管元件,用以输出第1频带的信号;

第2输出晶体管,具有配置成与多个第1单位晶体管元件相互包围的多个第2单位晶体管元件,用以输出第2频带的信号。

11.如权利要求10所述的放大器,其特征在于,所述多个第1单位晶体管元件和所述多个第2单位晶体管元件沿着第1方向和与所述第1方向正交的第2方向排列配置,分别包含有第1导通结点、第2导通结点以及控制结点,

第1输出晶体管还包括:

多根第1布线,在所述第1方向上延伸配置,用以相互电气连接所述多个第1单位晶体管元件的第1导通结点;

多根第2布线,在所述第2方向上延伸配置,用以相互电气连接所述多个第1单位晶体管元件的第2导通结点;

多根第3布线,在所述第2方向上延伸,用以相互电气连接所述第1单位晶体管元件的控制结点;

多根第4布线,在所述第2方向上延伸,与所述第1布线电气连接并形成所述第1输出晶体管的输出结点;

所述第2输出晶体管还包括:

第5布线,在所述第1方向上延伸配置且在所述第2方向上与所述第1布线交互配置,用以相互电气连接所述第2单位晶体管元件的第1导通结点;

多根第6布线,在所述第2方向上延伸且与所述第2布线共同配置,用以相互电气连接所述多个第2单位晶体管元件的第2导通结点;

多根第7布线,在所述第2方向上延伸且在所述第1方向上与所述第3布线交互配置,用以相互电气连接所述第2单位晶体管元件的控制结点;

第8布线,通过所述第1及第2单位晶体管元件的形成区域与所述第4布线相对地在所述第2方向上延伸配置,与所述第5布线电气连接并形成所述第2输出晶体管的输出结点;

所述第2布线和所述第6布线与用以传送规定电压的基准电压线相互连接,而且,

所述第1布线和第5布线连接到对应的单位晶体管,使得所述第1单位晶体管元件及所述第2单位晶体管元件交互配置成相互包围。

12.如权利要求10所述的放大器,其特征在于,所述第1频带包含有所述第2频带的频率分量的整数倍的频率分量。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP371206/01 | 2001-12-05 | ||

| JP371206/2001 | 2001-12-05 | ||

| JP2001371206A JP2003174335A (ja) | 2001-12-05 | 2001-12-05 | 増幅器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1424762A CN1424762A (zh) | 2003-06-18 |

| CN1245759C true CN1245759C (zh) | 2006-03-15 |

Family

ID=19180284

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB02155787XA Expired - Fee Related CN1245759C (zh) | 2001-12-05 | 2002-12-05 | 多频带功率放大器 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US6838941B2 (zh) |

| JP (1) | JP2003174335A (zh) |

| CN (1) | CN1245759C (zh) |

| DE (1) | DE10255941A1 (zh) |

| FR (1) | FR2833114A1 (zh) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10651804B2 (en) | 2017-06-08 | 2020-05-12 | Murata Manufacturing Co., Ltd. | Power amplifier circuit |

Families Citing this family (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7026876B1 (en) * | 2003-02-21 | 2006-04-11 | Dynalinear Technologies, Inc. | High linearity smart HBT power amplifiers for CDMA/WCDMA application |

| US7135919B2 (en) * | 2004-08-06 | 2006-11-14 | Avago Technologies Wireless Ip (Singapore) Pte. Ltd. | Power amplifier with switchable load |

| KR101034621B1 (ko) * | 2004-08-10 | 2011-05-12 | 엘지전자 주식회사 | 다중밴드 이동통신 단말기 |

| WO2007003224A1 (en) * | 2005-07-05 | 2007-01-11 | Freescale Semiconductor, Inc. | Compensation for parasitic coupling between rf or microwave transistors in the same package |

| JP2007060616A (ja) * | 2005-07-29 | 2007-03-08 | Mitsubishi Electric Corp | 高周波電力増幅器 |

| US20070252651A1 (en) * | 2006-04-28 | 2007-11-01 | Huai Gao | Power Amplifier With A Output Matching Network |

| US7683483B2 (en) * | 2007-02-05 | 2010-03-23 | Freescale Semiconductor, Inc. | Electronic device with connection bumps |

| JP4849029B2 (ja) * | 2007-07-23 | 2011-12-28 | 三菱電機株式会社 | 電力増幅器 |

| CN101588195B (zh) * | 2008-05-21 | 2012-10-17 | 华为技术有限公司 | 功放装置及信号收发系统 |

| JP5282954B2 (ja) * | 2008-12-03 | 2013-09-04 | 株式会社村田製作所 | Rf電力増幅装置 |

| JP5453120B2 (ja) * | 2009-01-30 | 2014-03-26 | 株式会社Nttドコモ | マルチバンド整合回路、およびマルチバンド電力増幅器 |

| CN101667810B (zh) * | 2009-09-29 | 2011-11-16 | 锐迪科科技有限公司 | 双频射频功率放大器电路芯片 |

| JPWO2011039792A1 (ja) * | 2009-09-29 | 2013-02-21 | 株式会社東芝 | 半導体装置 |

| DE102010009984A1 (de) | 2009-12-28 | 2011-06-30 | Rohde & Schwarz GmbH & Co. KG, 81671 | Verstärkerbaustein mit einem Kompensationselement |

| CN102281220B (zh) | 2010-06-12 | 2015-04-29 | 华为技术有限公司 | 数据流处理方法、设备及系统 |

| CN102130657A (zh) * | 2010-09-14 | 2011-07-20 | 华为技术有限公司 | 一种功率放大器、不对称达赫笛功率放大设备和基站 |

| JP5527313B2 (ja) * | 2011-12-08 | 2014-06-18 | 株式会社村田製作所 | 半導体装置およびそれを用いた無線通信機器 |

| JP6208413B2 (ja) * | 2012-07-06 | 2017-10-04 | 日本無線株式会社 | 増幅器制御装置 |

| JP5821876B2 (ja) * | 2013-03-05 | 2015-11-24 | 株式会社村田製作所 | 電力増幅モジュール |

| JP5719467B1 (ja) * | 2014-05-30 | 2015-05-20 | 日本電信電話株式会社 | 低雑音増幅器 |

| US9231550B2 (en) | 2014-06-09 | 2016-01-05 | Mitsubishi Electric Research Laboratories, Inc. | Output matching network for wideband power amplifier with harmonic suppression |

| US9647703B2 (en) * | 2014-09-16 | 2017-05-09 | Skyworks Solutions, Inc. | Multi-band device with reduced band loading |

| KR20210057875A (ko) * | 2019-11-12 | 2021-05-24 | 삼성전자주식회사 | 집적 클럭 게이팅 회로 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6151754A (ja) | 1984-08-20 | 1986-03-14 | Matsushita Electric Ind Co Ltd | 密閉型鉛蓄電池 |

| JPH11251849A (ja) * | 1998-03-04 | 1999-09-17 | Matsushita Electric Ind Co Ltd | 高周波電力増幅器 |

| US6151509A (en) * | 1998-06-24 | 2000-11-21 | Conexant Systems, Inc. | Dual band cellular phone with two power amplifiers and a current detector for monitoring the consumed power |

| DE69904560T2 (de) | 1999-03-08 | 2003-06-26 | Motorola, Inc. | Sender |

| US6232840B1 (en) * | 1999-06-10 | 2001-05-15 | Raytheon Company | Transistor amplifier having reduced parasitic oscillations |

| JP2001068556A (ja) | 1999-08-30 | 2001-03-16 | Mobile Communications Tokyo Inc | 高周波電力増幅用半導体装置 |

| JP3892630B2 (ja) | 1999-09-30 | 2007-03-14 | 株式会社東芝 | 半導体装置 |

| EP1202446B1 (en) * | 2000-10-23 | 2009-10-14 | Panasonic Corporation | Power amplifier |

-

2001

- 2001-12-05 JP JP2001371206A patent/JP2003174335A/ja active Pending

-

2002

- 2002-11-29 DE DE10255941A patent/DE10255941A1/de not_active Ceased

- 2002-12-04 FR FR0215274A patent/FR2833114A1/fr active Pending

- 2002-12-04 US US10/309,239 patent/US6838941B2/en not_active Expired - Fee Related

- 2002-12-05 CN CNB02155787XA patent/CN1245759C/zh not_active Expired - Fee Related

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10651804B2 (en) | 2017-06-08 | 2020-05-12 | Murata Manufacturing Co., Ltd. | Power amplifier circuit |

| TWI695579B (zh) * | 2017-06-08 | 2020-06-01 | 日商村田製作所股份有限公司 | 功率放大電路 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2003174335A (ja) | 2003-06-20 |

| US6838941B2 (en) | 2005-01-04 |

| FR2833114A1 (fr) | 2003-06-06 |

| CN1424762A (zh) | 2003-06-18 |

| DE10255941A1 (de) | 2003-07-03 |

| US20030117219A1 (en) | 2003-06-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1245759C (zh) | 多频带功率放大器 | |

| CN1134901C (zh) | 高频放大器、发射装置、接收装置及控制放大器状态的方法 | |

| CN1178390C (zh) | 可变衰减器 | |

| CN1249918C (zh) | 射频可变增益放大器件 | |

| CN1167171C (zh) | 天线装置 | |

| CN1309166C (zh) | 高频开关装置和半导体装置 | |

| CN1262019C (zh) | 半导体器件 | |

| CN1278446C (zh) | 双模谐振腔 | |

| CN1263228C (zh) | 高频开关、高频开关·放大电路及移动体通信终端 | |

| CN1941639A (zh) | 发射装置和用于阻抗匹配的方法 | |

| CN1445926A (zh) | 平衡高频器件,平衡特性的改进方法和采用此类器件的平衡高频电路 | |

| CN1574612A (zh) | 差分电路、差分放大器、混频器、振荡器和无线电电路 | |

| CN1314122C (zh) | 非易失性半导体存储器件 | |

| CN1472843A (zh) | 单极天线装置、通信系统和移动通信系统 | |

| CN1623232A (zh) | 带有补偿的射频放大器装置 | |

| CN1268055C (zh) | 能抑制接收频带的噪声功率且进行增益切换的功率放大器 | |

| CN101079598A (zh) | 高频功率放大器和通信设备 | |

| CN1874155A (zh) | 化合物半导体装置 | |

| CN1255936C (zh) | 功率放大器 | |

| CN1256738C (zh) | 高频功率放大装置 | |

| CN1977446A (zh) | 双向频率变换器以及使用它的无线器 | |

| CN1224166C (zh) | 功率放大器和通信装置 | |

| CN1169287C (zh) | 具有放大元件的高效放大器及无线发信装置 | |

| CN1279692C (zh) | 高频放大器和放大元件 | |

| CN1048596C (zh) | 整流传送门电路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C17 | Cessation of patent right | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20060315 Termination date: 20121205 |