CN110047747B - 蚀刻方法和蚀刻装置 - Google Patents

蚀刻方法和蚀刻装置 Download PDFInfo

- Publication number

- CN110047747B CN110047747B CN201910043237.0A CN201910043237A CN110047747B CN 110047747 B CN110047747 B CN 110047747B CN 201910043237 A CN201910043237 A CN 201910043237A CN 110047747 B CN110047747 B CN 110047747B

- Authority

- CN

- China

- Prior art keywords

- gas

- etching

- wafer

- substrate

- silicon

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000005530 etching Methods 0.000 title claims abstract description 175

- 238000000034 method Methods 0.000 title claims abstract description 53

- 239000000758 substrate Substances 0.000 claims abstract description 54

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims abstract description 39

- 229910052710 silicon Inorganic materials 0.000 claims abstract description 39

- 239000010703 silicon Substances 0.000 claims abstract description 39

- XRURPHMPXJDCOO-UHFFFAOYSA-N iodine heptafluoride Chemical compound FI(F)(F)(F)(F)(F)F XRURPHMPXJDCOO-UHFFFAOYSA-N 0.000 claims abstract description 20

- 238000012545 processing Methods 0.000 claims description 59

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 claims description 6

- 229910021529 ammonia Inorganic materials 0.000 claims description 3

- VJUJMLSNVYZCDT-UHFFFAOYSA-N iodine trifluoride Chemical compound FI(F)F VJUJMLSNVYZCDT-UHFFFAOYSA-N 0.000 claims 8

- 239000007789 gas Substances 0.000 description 232

- 238000012360 testing method Methods 0.000 description 57

- 238000011156 evaluation Methods 0.000 description 46

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 45

- 229920005591 polysilicon Polymers 0.000 description 45

- 230000008569 process Effects 0.000 description 34

- 239000012535 impurity Substances 0.000 description 15

- 230000000052 comparative effect Effects 0.000 description 14

- 238000010438 heat treatment Methods 0.000 description 13

- 229910017855 NH 4 F Inorganic materials 0.000 description 12

- 229910021417 amorphous silicon Inorganic materials 0.000 description 12

- 238000012546 transfer Methods 0.000 description 11

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 8

- 229910052814 silicon oxide Inorganic materials 0.000 description 8

- 238000009792 diffusion process Methods 0.000 description 7

- 230000000694 effects Effects 0.000 description 6

- 230000007723 transport mechanism Effects 0.000 description 6

- 230000009471 action Effects 0.000 description 4

- 238000010586 diagram Methods 0.000 description 4

- 238000000859 sublimation Methods 0.000 description 4

- 230000008022 sublimation Effects 0.000 description 4

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 3

- 238000003917 TEM image Methods 0.000 description 3

- 238000002474 experimental method Methods 0.000 description 3

- 229910052731 fluorine Inorganic materials 0.000 description 3

- 239000011737 fluorine Substances 0.000 description 3

- 239000004065 semiconductor Substances 0.000 description 3

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 2

- ROSDSFDQCJNGOL-UHFFFAOYSA-N Dimethylamine Chemical compound CNC ROSDSFDQCJNGOL-UHFFFAOYSA-N 0.000 description 2

- OAKJQQAXSVQMHS-UHFFFAOYSA-N Hydrazine Chemical compound NN OAKJQQAXSVQMHS-UHFFFAOYSA-N 0.000 description 2

- BAVYZALUXZFZLV-UHFFFAOYSA-N Methylamine Chemical compound NC BAVYZALUXZFZLV-UHFFFAOYSA-N 0.000 description 2

- 150000001412 amines Chemical class 0.000 description 2

- 238000001312 dry etching Methods 0.000 description 2

- 230000007246 mechanism Effects 0.000 description 2

- 238000001020 plasma etching Methods 0.000 description 2

- 230000032258 transport Effects 0.000 description 2

- 238000001039 wet etching Methods 0.000 description 2

- DDFHBQSCUXNBSA-UHFFFAOYSA-N 5-(5-carboxythiophen-2-yl)thiophene-2-carboxylic acid Chemical compound S1C(C(=O)O)=CC=C1C1=CC=C(C(O)=O)S1 DDFHBQSCUXNBSA-UHFFFAOYSA-N 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- 239000000654 additive Substances 0.000 description 1

- 230000000996 additive effect Effects 0.000 description 1

- 230000001464 adherent effect Effects 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- HQABUPZFAYXKJW-UHFFFAOYSA-N butan-1-amine Chemical compound CCCCN HQABUPZFAYXKJW-UHFFFAOYSA-N 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 238000007865 diluting Methods 0.000 description 1

- 239000012895 dilution Substances 0.000 description 1

- 238000010790 dilution Methods 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 230000005764 inhibitory process Effects 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 238000010926 purge Methods 0.000 description 1

- 239000000243 solution Substances 0.000 description 1

- 239000007921 spray Substances 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 238000011144 upstream manufacturing Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3205—Deposition of non-insulating-, e.g. conductive- or resistive-, layers on insulating layers; After-treatment of these layers

- H01L21/321—After treatment

- H01L21/3213—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer

- H01L21/32133—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer by chemical means only

- H01L21/32135—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer by chemical means only by vapour etching only

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/30604—Chemical etching

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B08—CLEANING

- B08B—CLEANING IN GENERAL; PREVENTION OF FOULING IN GENERAL

- B08B7/00—Cleaning by methods not provided for in a single other subclass or a single group in this subclass

- B08B7/0064—Cleaning by methods not provided for in a single other subclass or a single group in this subclass by temperature changes

- B08B7/0071—Cleaning by methods not provided for in a single other subclass or a single group in this subclass by temperature changes by heating

-

- C—CHEMISTRY; METALLURGY

- C09—DYES; PAINTS; POLISHES; NATURAL RESINS; ADHESIVES; COMPOSITIONS NOT OTHERWISE PROVIDED FOR; APPLICATIONS OF MATERIALS NOT OTHERWISE PROVIDED FOR

- C09K—MATERIALS FOR MISCELLANEOUS APPLICATIONS, NOT PROVIDED FOR ELSEWHERE

- C09K13/00—Etching, surface-brightening or pickling compositions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02041—Cleaning

- H01L21/02057—Cleaning during device manufacture

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/3065—Plasma etching; Reactive-ion etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31105—Etching inorganic layers

- H01L21/31111—Etching inorganic layers by chemical means

- H01L21/31116—Etching inorganic layers by chemical means by dry-etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/67005—Apparatus not specifically provided for elsewhere

- H01L21/67011—Apparatus for manufacture or treatment

- H01L21/67098—Apparatus for thermal treatment

- H01L21/67103—Apparatus for thermal treatment mainly by conduction

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/67005—Apparatus not specifically provided for elsewhere

- H01L21/67011—Apparatus for manufacture or treatment

- H01L21/67017—Apparatus for fluid treatment

- H01L21/67063—Apparatus for fluid treatment for etching

- H01L21/67069—Apparatus for fluid treatment for etching for drying etching

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Chemical & Material Sciences (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- Plasma & Fusion (AREA)

- Inorganic Chemistry (AREA)

- Materials Engineering (AREA)

- Organic Chemistry (AREA)

- Drying Of Semiconductors (AREA)

- ing And Chemical Polishing (AREA)

- Manufacturing Of Printed Circuit Boards (AREA)

Abstract

本发明提供一种蚀刻方法和蚀刻装置。在基板的面内均匀性较高地对含硅膜进行蚀刻。向在表面形成有含硅膜(13)的基板(W)供给七氟化碘气体和碱性气体,来对该含硅膜(13)进行蚀刻。通过这样的处理,能够在基板的面内均匀性较高地蚀刻。并且,在对基板(W)以残留含硅膜(13)的方式进行蚀刻的情况下,能提高所残留的含硅膜的表面的平坦性。

Description

技术领域

本发明涉及使用七氟化碘气体来对含硅膜进行蚀刻的蚀刻方法和蚀刻装置。

背景技术

在半导体装置的制造工序中,具有进行去除在半导体晶圆(以下,记载为晶圆)的表面形成的多晶硅膜等含硅膜的处理的情况。在专利文献1、2中,示出有如下内容:在对多晶硅膜进行蚀刻时,使用IF7(七氟化碘)气体作为蚀刻选择性相对于该多晶硅膜较高的气体。另外,在专利文献3中记载有如下内容:为了对蚀刻性能进行调整,将向IF7气体添加氧化性气体或者非活性气体而成的气体用作蚀刻气体,来对硅层进行蚀刻。

现有技术文献

专利文献

专利文献1:日本特再公表2015-115002号公报

专利文献2:日本特再公表2015-60069号公报

专利文献3:日本特许第6032033号公报

发明内容

发明要解决的问题

在使用上述的IF7气体等蚀刻气体来进行含硅膜的干蚀刻的情况下,难以在晶圆的面内均匀性较高地进行蚀刻。另外,例如具有如下情况:对埋入到晶圆表面的含硅膜进行蚀刻,以形成作为图案的凹部的方式进行处理,但具有如下情况:由于如此蚀刻的均匀性较低,产生上述的凹部的侧壁附近的底部的含硅膜比较多地残留的、被称为Footing的现象。也就是说,在纵截侧面中看来凹部的侧面与底面之间的正交性较低,难以形成该正交性较高的良好的形状的凹部。

因此,具有如下情况:在例如通过使用了等离子体的各向异性蚀刻将含硅膜的上部侧去除了后,进行利用湿蚀刻去除含硅膜的下部侧的处理。不过,上述的等离子体蚀刻有可能对晶圆表面造成损伤,且由于进行等离子体蚀刻和湿蚀刻这样的多个处理,因此,花费劳力和时间。为此,具有要以不使用等离子体的上述的干蚀刻进行含硅膜的去除这样的要求。上述的专利文献1~3所记载的技术并不是能够解决这样的问题的技术。

本发明是基于这样的状况作成的,其目的在于提供一种能够在基板的面内均匀性较高地对含硅膜进行蚀刻的技术。

用于解决问题的方案

本发明的蚀刻方法的特征在于,该蚀刻方法包括如下工序:向在表面形成有含硅膜的基板供给七氟化碘素气体和碱性气体,而对该含硅膜进行蚀刻。

本发明的蚀刻装置的特征在于,该蚀刻装置具备:

处理容器;

载置部,其设置于所述处理容器内,用于载置在表面形成有含硅膜的基板;以及

气体供给部,其向所述处理容器内供给七氟化碘气体和碱性气体,而对所述含硅膜进行蚀刻。

发明的效果

根据本发明,通过向在表面形成有含硅膜的基板供给七氟化碘气体和碱性气体,能够在基板的面内均匀性较高地对含硅膜进行蚀刻。

附图说明

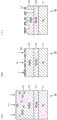

图1是说明比较例中的蚀刻工序的工序图。

图2是说明本发明的蚀刻工序的工序图。

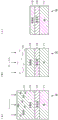

图3是用于进行蚀刻的基板处理装置的俯视图。

图4是设置于所述基板处理装置的蚀刻模块的纵剖侧视图。

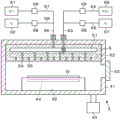

图5是利用所述基板处理装置处理的晶圆的纵剖侧视图。

图6是由所述基板处理装置处理后的晶圆的纵剖侧视图。

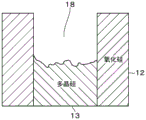

图7是表示比较试验中的晶圆的纵截侧面的示意图。

图8是表示比较试验中的晶圆的纵截侧面的示意图。

图9是表示针对评价试验中的蚀刻量的结果的图表。

图10是表示针对评价试验中的粗糙度的结果的图表。

图11是表示针对评价试验中的蚀刻量的结果的图表。

图12是表示针对评价试验中的粗糙度的结果的图表。

附图标记说明

W、晶圆;14、多晶硅膜;2、基板处理装置;20、控制部;4、蚀刻模块;42、载置台;5、喷头。

具体实施方式

在对本发明的处理进行说明之前,一边参照作为晶圆W的表面部的纵截侧面图的图1一边对比较例的处理进行说明。如图1的(a)所示,晶圆W的表面部是以从下方朝向上方按照Si(硅)层11、氧化硅膜12、多晶硅膜13的顺序层叠Si(硅)层11、氧化硅膜12、多晶硅膜13而构成的。在该处理例中,向晶圆W供给IF7气体,以氧化硅膜12不暴露的方式对作为含硅膜的多晶硅膜13的上部侧进行蚀刻。在多晶硅膜13混入有由例如氧化硅构成的杂质14。

IF7气体相对于含硅膜的蚀刻选择性比较高,因此,蚀刻速度变得比较高。因而,多晶硅膜13被朝向下方急剧地蚀刻(图1的(b))。在其蚀刻的进行中,上述的杂质14暴露,但IF7气体相对于杂质14的蚀刻选择性比较低,因此,该杂质14作为掩模发挥作用。因此,在晶圆W的面内难以在杂质14的下方进行蚀刻,在杂质14不存在的部位接着进行急剧的蚀刻。图1的(c)表示蚀刻结束后的晶圆W。如上述那样,由于杂质14存在,晶圆W的面内各部的蚀刻量产生比较大的偏差。另外,若进行基于该IF7气体的蚀刻,则确认到残留的多晶硅膜13的表面的粗糙变得比较大(图1的(c))。

接下来,参照图2来对本发明的处理的概要和推定为在该处理中产生的的反应进行说明。在该处理中,将添加有作为碱性气体的NH3(氨)气体的IF7气体作为蚀刻气体向例如具备已述的表面部的晶圆W供给(图2的(a))。IF7气体和NH3气体如下述的式1所示那样相互反应,生成NH4F(氟化铵),认为该NH4F成为附着于晶圆W的表面的附着物。

3IF7+aNH3=3IF5+bHF+cNH4F+N2...式1

(其中,a=2~5、b=8-a(=0~6)、c=a-2(=0~3))

并且,附着到晶圆W的表面的NH4F与杂质14反应,该杂质14被蚀刻。另外,在该NH4F附着到晶圆W的状态下IF7气体被供给,因此,多晶硅膜13的蚀刻速度变得过大的情况被抑制。因而,对于暴露到晶圆W的表面的杂质14,被蚀刻去除,而在杂质14不存在的区域中以急剧的多晶硅膜13的蚀刻被防止的方式进行蚀刻(图2的(b))。此外,对于附着到晶圆W的NH4F,如随后详细地说明那样由于该蚀刻中的晶圆W的加热温度升华而被去除。图2的(c)表示蚀刻结束后的晶圆W。作为如已述那样进行蚀刻的结果,如该图2的(c)所示,多晶硅膜13在晶圆W的面内均匀性较高地被蚀刻。另外,通过如此进行蚀刻,确认到多晶硅膜13的表面的粗糙被抑制。

接下来,参照图3的俯视图说明包括使用上述的IF7气体和作为添加气体的NH3气体来进行蚀刻的蚀刻模块4的基板处理装置2。基板处理装置2具备:输入输出部21,其用于输入输出晶圆W;两个加载互锁室31,其与输入输出部21相邻地设置;两个热处理模块30,其与两个加载互锁室31分别相邻地设置;以及两个蚀刻模块4,其与两个热处理模块30分别相邻地设置。

输入输出部21具备:常压输送室23,其设置有第1基板输送机构22,并且设为常压气氛;以及承载件用载置台25,其设置到该常压输送室23的侧部,用于载置收纳晶圆W的承载件24。图中附图标记26是与常压输送室23相邻的定方位器室,其是为了使晶圆W旋转而以光学方式求出偏心量、进行晶圆W相对于第1基板搬送机构22的对位而设置的。第1基板输送机构22在承载件用载置台25上的承载件24与定方位器室26和加载互锁室31之间输送晶圆W。

在各加载互锁室31内设置有例如具有多关节臂构造的第2基板输送机构32,该第2基板输送机构32将晶圆W在加载互锁室31与热处理模块30和蚀刻模块4之间输送。构成热处理模块30的处理容器内和构成蚀刻模块4的处理容器内构成为真空气氛,加载互锁室31内的常压气氛和真空气氛被切换,以使能够在这些真空气氛的处理容器内与常压输送室23之间进行晶圆W的交接。

图中附图标记23是开闭自由的闸阀,分别设置于常压输送室23与加载互锁室31之间、加载互锁室31与热处理模块30之间、热处理模块30与蚀刻模块4之间。对于热处理模块30,包括以下构件等:处理容器,其收纳晶圆W,并且,内部被排气而设为真空气氛;以及载置台,其设置于处理容器内,并且,能够对所载置的晶圆W进行加热。构成为,通过具备这样的结构,对进行了使用了上述的IF7气体和NH3气体的蚀刻之后的晶圆W进行加热处理,能够将由于蚀刻而附着到晶圆W的残渣去除。

接下来,参照作为纵剖侧视图的图4来对蚀刻模块4进行说明。蚀刻模块4具备:处理容器41;载置台42,其配置到处理容器41的内部;气体喷头5,其以与载置台42相对的方式配置到处理容器41的上部;以及排气单元43,其对处理容器41的内部进行排气而对该处理容器41内的压力进行调整。图中附图标记40是在处理容器41形成的晶圆W的输送口,由上述的闸阀33进行开闭。晶圆W可水平地载置于已述的载置台42的上表面。图中附图标记44是埋设到载置台42的加热器,以载置到该载置台42的晶圆W成为所设定的温度的方式进行加热。在载置台42设置有相对于其上表面突出没入自由的3个升降销,以便与已述的第2基板输送机构32之间进行晶圆W的交接,但省略图示。

作为气体供给部的气体喷头5构成为水平的板状体。在气体喷头5的上侧、下侧分别设置有扁平的扩散空间51、52,这些扩散空间51、52被相互划分开。在气体喷头5的下表面分别开口有许多相互划分开的气体喷出口54、55,气体喷出口54与扩散空间51连接,气体喷出口55与扩散空间52连接。

在扩散空间51的上部侧连接有气体流路56的下游端。气体流路56的上游侧分支而形成气体流路57、58,气体流路57、58的上游侧与IF7气体的供给源61、Ar(氩)气体供给源62分别连接。在扩散空间52的上部侧连接有被相对于气体流路56划分开的气体流路63的下游端。气体流路63的上游侧分支而形成气体流路64、65,气体流路64、65的上游侧与NH3气体的供给源66、Ar气体供给源67分别连接。在气体流路57、58、64、65上分别夹设有由阀、质量流量控制器构成的流量调整部68,进行向各流路的下游侧的气体的供给断开以及向各流路的下游侧的气体的流量的调整。上述的Ar气体是用于稀释处理容器41内的IF7气体和NH3气体的稀释气体。如上述那样,通过构成蚀刻模块4,从气体供给源61、66供给来的IF7气体和NH3气体直到从气体喷头5喷出为止未相互混合,在从气体喷头5喷出后在处理容器41内相互混合。

如图3所示,基板处理装置2具备作为计算机的控制部20,该控制部20具备程序、存储器以及CPU。在程序中编入有命令(各步骤),以便进行已述的晶圆W的处理和晶圆W的输送,该程序被储存于计算机存储介质、例如光盘、硬盘、光磁盘、DVD等,被安装于控制部20。控制部20利用该程序向基板处理装置2的各部输出控制信号,并控制各部的动作。具体而言,蚀刻模块4的动作、热处理模块30的动作、第1的基板输送机构22、第2基板输送机构32的动作、定方位器室26的动作被控制信号控制。作为上述的蚀刻模块4的动作,包括加热器44的输出的调整、由各流量调整部68进行的各气体的流量调整以及各气体的供给断开、由排气单元43进行的排气流量的调整等各动作。本发明的蚀刻装置由该控制部20和蚀刻模块4构成。

对基板处理装置2中的晶圆W的处理进行说明。在此,作为对图5所示的晶圆W进行处理的情况来进行说明。在该晶圆W的表面设置有氧化硅膜12。在该氧化硅膜12形成有贯通孔16,以埋入该贯通孔16内的方式形成有多晶硅膜13。在该处理例中,对该多硅膜13的上部侧进行蚀刻。

收纳有以图5进行了说明的晶圆W的承载件24被载置于承载件用载置台25。然后,该晶圆W按照常压输送室23→定方位器室26→常压输送室23→加载互锁室31的顺序被输送,被经由热处理模块30向蚀刻模块4的处理容器41内输送。然后,该晶圆W被载置于载置台42而被加热成例如80℃。另一方面,处理容器41内的压力、也就是说、晶圆W的周围的压力设为例如13.3Pa(100mTorr)~66.6Pa(500mTorr)。设为这样的比较小的压力的目的在于,如已述那样抑制IF7气体对作为含硅膜的多晶硅膜13的蚀刻速度过快。

接下来,IF7气体、NH3气体、Ar气体被从气体喷头5向处理容器41内供给。如以图2进行了说明那样IF7气体与NH3气体相互反应而产生NH4F,该NH4F附着于晶圆W。晶圆W被加热成80℃,在该温度下,附着到晶圆W的NH4F气体升华。如此在晶圆W的表面进行了NH4F的附着和升华的状态下,进行基于IF7气体的多晶硅膜13的蚀刻,由于该蚀刻,在晶圆W的表面形成凹部18,该凹部18深度逐渐变大。

即使以图2进行了叙述的由氧化硅物构成的杂质14包含于多晶硅膜13,该多晶硅膜13也被附着于晶圆W的NH4F去除,另外,多晶硅膜13的蚀刻速度过量地变大的情况被该NH4F抑制。作为结果,与对以图2所叙述的多晶硅膜13进行蚀刻的情况同样地,在晶圆W的面内均匀性较高地对多晶硅膜13进行蚀刻。此外,对于NH4F,认为除了对杂质14起作用之外,也对氧化硅膜12起作用,但根据所进行的实验,确认到氧化硅膜12的外形几乎没有变化(没有膜损失)。关于杂质14,在膜中所含有的量是微量,因此,认为其被该NH4F充分地去除。

然后,在从IF7气体、NH3气体和Ar气体的供给开始经过了预定的时间之后,使所述各气体的从气体喷头5的供给停止,蚀刻结束。图6表示蚀刻结束了的状态的晶圆W。如上述那样,通过进行了蚀刻,凹部18的深度在晶圆W的面内一致。另外,构成凹部的底面的多硅膜13的粗糙被抑制。因而,作为该凹部,在发明要解决的问题的项目中所叙述的Footing的产生被抑制。蚀刻结束了的晶圆W被向热处理模块30输送而以成为预定的温度的方式受到加热处理,在蚀刻残渣被去除了之后,晶圆W按照加载互锁室31→常压输送室23的顺序被输送而被返回承载件24。

根据包括该蚀刻模块4的基板处理装置2,在晶圆W的面内均匀性较高地对多晶硅膜13进行蚀刻,能够抑制蚀刻后残留的多晶硅膜13的表面的粗糙。而且,根据上述的处理,无需使用等离子体,因此,晶圆W的表面的各膜不会受到来自该等离子体的损伤,因此,也具有能够提高由晶圆W形成的半导体装置的可靠性这样的优点。不过,使用等离子体来进行蚀刻的情况也包含于本发明的保护范围。此外,说明了作为在基板处理装置2中对图5所示的晶圆W进行处理的情况,但也可以对图2的(a)所示的晶圆W进行处理。因而,基板处理装置2并不限于对埋入到孔、凹部内的含硅膜进行蚀刻。

另外,对于上述的各处理例,示出了仅对多晶硅膜13的上侧进行蚀刻的例子,但也可以以对在晶圆W表面形成的多晶硅膜13整体进行蚀刻的方式进行处理。在该情况下,晶圆W的面内各部中的多晶硅膜13的蚀刻速度的均匀性较高,因此,获得能够抑制蚀刻所需的时间这样的效果。更具体地说明,在晶圆W的面内的蚀刻速度的偏差较大的情况下,即使蚀刻在晶圆W的面内的一个区域已经结束,由于蚀刻速度在其他区域较低,成为蚀刻未结束的状态,因此,将蚀刻时间设定成,在一个区域被蚀刻了之后也进行蚀刻,以使多晶硅膜13在面内的全部的区域中被蚀刻。也就是说,针对一个区域设定进行过度蚀刻的时间。不过,由于蚀刻速度的均匀性较高,能够使这样的过度蚀刻的时间缩短化或消除,因此,如上述那样,能够抑制蚀刻所需的时间。

不过,在对上述的多晶硅膜13进行蚀刻的处理例中,将IF7气体和NH3气体同时向处理容器41内供给。即、供给IF7气体的期间和供给NH3气体的期间以相互一致的方式重叠。

也可以不如此供给IF7气体和NH3气体。也可以是,首先,仅将IF7气体和NH3气体中的、NH3气体向处理容器41内供给而使NH3气体吸附于晶圆W。之后,使NH3气体的供给停止,仅将IF7气体和NH3气体中的IF7气体向晶圆W供给,使IF7气体与吸附到晶圆W的NH3气体反应来使NH4F产生,而将杂质14去除,并且,进行基于IF7气体的多晶硅膜13的蚀刻。也就是说,也可以将NH3气体和IF7气体以NH3气体和IF7气体的顺序向晶圆W供给而进行处理。也可以反复进行该顺序的气体供给。即、也可以是,在将NH3气体、IF7气体按照NH3气体、IF7气体的顺序供给了之后,再次将NH3气体、IF7气体按照NH3气体、IF7气体的顺序供给。并不限于如此NH3气体以向IF7气体添加的方式向晶圆W供给。此外,也可以是,例如,在将IF7气体和NH3气体同时向晶圆W供给开始了之后,在使IF7气体的供给停止之前先进行NH3气体的供给的停止。也就是说,供给IF7气体的期间与供给NH3气体的期间重叠并不限于这些期间相互一致。

不过,含硅膜是含有硅作为主成分的膜,并不限于多晶硅膜。具体而言,例如非晶硅膜、单晶硅膜、SiGe膜、SiC膜等也包含于含硅膜。另外,作为除了IF7气体之外向晶圆W供给的碱性气体,认为能够与IF7气体反应而与NH4F同样地含有氮和氟、生成对氧化物具有蚀刻作用的化合物即可,因此,也可以使用除了NH3气体以外的碱性气体。具体而言,碱性气体包含有N2H4(肼)、作为胺的(CH3)NH2(甲胺)、正丁胺、二甲胺等。

在上述的蚀刻模块4中,也可以构成为IF7气体、NH3气体被向例如气体喷头5内的通用的扩散空间供给。详细地说明,气体喷头5构成为,在气体喷头5内进行这些IF7气体和NH3气体的混合,其混合气体向晶圆W喷出。另外,在上述的蚀刻模块4中,也可以设为如下结构来替代气体喷头5:以沿着例如俯视晶圆W的周边的方式设置具备呈同心圆状开口的气体的喷出口的气体供给部,气体被向晶圆W供给。也就是说,作为气体供给部,并不限于构成为气体喷头。此外,作为本发明,并不限于在已述的实施例、随后论述的评价试验中说明的例子,各例能够适当变更、或相互组合。

(评价试验)

说明与本发明相关联而进行了的评价试验。

评价试验1

作为评价试验1,使用与以图4进行了说明的蚀刻模块4大致相同地构成的蚀刻装置来向具有以图5进行了说明的构造的晶圆W同时供给IF7气体、NH3气体和Ar气体,来对多晶硅膜13进行了蚀刻。并且,在蚀刻后使用TEM(透过型电子显微镜)来取得了晶圆W的纵截侧面的图像。IF7气体的流量设定成20sccm~500sccm,NH3气体的流量设定成10sccm~500sccm、Ar气体的流量设定成100sccm~1000sccm。这些气体的供给时间、即蚀刻时间设定成3秒,处理容器41内的压力设定成6.66Pa~199.9Pa(50mTorr~1500mTorr),晶圆W的温度设定成20℃~100℃。

另外,以与评价试验1不同的处理条件进行了比较试验1-1、1-2,在该比较试验1-1、1-2中,进行具有以图5说明了的构造的晶圆W中的多硅膜13的蚀刻,与评价试验1同样地取得蚀刻后的晶圆W的纵截侧面的图像。在比较试验1-1中,将F2(氟)气体以200sccm~1000sccm、将NH3气体以5sccm~100sccm、将N2气体以50sccm~1000sccm分别同时向处理容器41内供给而进行了蚀刻。所述各气体向处理容器41断续地供给7次,在进行了第N次(N是整数)的供给之后,且在进行第N+1次的供给之前,进行了基于吹扫气体的处理容器41内的吹扫。另外,1次F2气体、NH3气体和N2气体的供给时间设定成30秒。另外,处理容器41内的压力设定成13.33Pa~333.3Pa(100mTorr~2500mTorr),晶圆W的温度设定成30℃~120℃。作为比较试验1-2,将ClF3(三氯化氟)气体以50sccm~500sccm、将N2气体以100sccm~1500sccm向处理容器41内分别同时供给而进行了蚀刻。这些气体向处理容器41的供给次数与评价试验1同样地是1次,气体的供给时间设为36.3秒。另外,处理容器41内的压力上设定成13.33Pa~333.3Pa(100mTorr~2500mTorr),晶圆W的温度设定成30℃~120℃。

对于评价试验1,构成凹部18的底部的蚀刻后的多晶硅膜13的表面的平坦性较高,没有发现Footing。因而,确认到在晶圆W的面内各部均匀性较高地进行了蚀刻。并且,凹部18的深度=蚀刻量是50nm。此外,已述的图6是将在该评价试验1中所取得的TEM图像表示为概略图的图。另外,图7是将从比较试验1-1获得的TEM图像表示为概略图的图,图8是将从比较试验1-2获得的TEM图像表示为概略图的图。如这些图7、8所示,在比较试验1-1、1-2中,与评价试验1相比,多晶硅膜13的表面的平坦性较低,发现了Footing。另外,在比较试验1-1中,蚀刻量是30nm,在比较试验1-2中,蚀刻量是36.3nm。因而,对于蚀刻速度,与比较试验1-1、1-2相比,评价试验1的该蚀刻速度较快。如此,根据评价试验1的结果示出了如下内容:通过使用IF7气体和NH3气体,能够以在晶圆W的面内均匀性较高、蚀刻后的多晶硅膜13的粗糙被抑制的方式进行该多晶硅膜13的蚀刻,且获得较高的蚀刻速度。

另外,在评价试验1中,NH3气体相对于IF7气体的流量比(=NH3气体的流量/IF7气体的流量)是0.6。晶圆W的温度被设定成20℃~100℃,处理容器41内的压力被设定成6.66Pa~199.9Pa(50mTorr~1500mTorr)。因而,确认到如下内容:通过设定成这样的流量比、晶圆W的温度以及处理容器41内的压力来进行处理,能够如已述那样在晶圆W的面内均匀性较高地进行蚀刻,且获得较高的蚀刻速度。此外,本发明人针对处理容器41内的压力设定成除了26.6Pa以外的值而进行与评价试验1同样的试验,在将处理容器41内的压力设定成13.3Pa(100mTorr)~133.3Pa(1000mTorr)的范围内的情况下,确认与评价试验1的结果同样地获得良好的凹部18的形状。因而,优选处理容器41内的压力设定成该13.3Pa~133.3Pa。

评价试验2

作为评价试验2-1,在晶圆W的表面以膜厚成为200nm的方式对非晶硅膜进行成膜,使用与以图4进行了说明的蚀刻模块4大致相同地构成的蚀刻装置,来将IF7气体和NH3气体同时供给8秒而进行了该非晶硅膜的蚀刻。与评价试验1同样地处理容器41内的压力设为50mTorr~1500mTorr。在蚀刻后,取得残留于晶圆W的非晶硅膜的表面的图像,对该非晶硅膜的蚀刻量(200nm-残留的非晶硅膜的膜厚)和残留于晶圆W的非晶硅膜的表面的粗糙度进行了测定。对于处理条件中的、NH3气体的流量和载置台42表面的温度(=晶圆W的温度)的组合,按照处理进行了变更。作为NH3气体/IF7气体的流量比(=NH3气体的流量/IF7气体的流量),设定成0.2、0.4、0.6、1.2或1.8,对于晶圆W的温度,设定成35℃、60℃、80℃、100℃或120℃。IF7气体的流量设定成20sccm~500sccm。另外,进行蚀刻前的非晶硅膜的表面的粗糙度是2.53nm,对于该粗糙度的值,越小,表示平坦性越高。

另外,作为评价试验2-2,在晶圆W的表面对多硅膜进行成膜,来替代非晶硅膜,除了对该多晶硅膜进行了蚀刻之外,进行了与评价试验2-1同样的试验。并且,对多晶硅膜的蚀刻量(200nm-残留的多晶硅膜的膜厚)和该多晶硅膜的表面的粗糙度进行了测定。进行蚀刻之前的非晶硅膜的粗糙度是7.46nm。

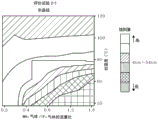

图9、图10的各图表表示评价试验2-1的结果,图11、图12的各图表表示评价试验2-2的结果。图9~图12的各图表的纵轴是表示供晶圆W载置的载物台的温度=晶圆W的温度。另外,图9~图12的各图表的横轴是NH3气体/IF7气体的流量比。图9、图11的图表表示针对蚀刻量的结果。详细地说明,通过在图表内标注等高线,包围蚀刻量近似的区域,并且,相互区分开来表示蚀刻量离得比较远的区域。并且,为了使由等高线围成的各区域相互区别,对该各区域标注互不相同的纹路来表示。

图10、图12的图表表示针对粗糙度的结果。详细地说明,通过在图表内标注等高线,包围粗糙度的值近似的区域,并且,相互区分开来表示粗糙度的值离得比较远的区域。并且,与图9、图11的图表同样,为了使由等高线围成的各区域相互区别,对该各区域标注互不相同的纹路来表示。此外,实际上,图9~图12的图表是根据计算机图形学用彩色的渐变来表示针对蚀刻量或者粗糙度的分布的图,但出于图示的方便如已述那样表示。

对于蚀刻量,在评价试验2-1中,是大致4nm~54nm的范围内的值,在评价试验2-2中,是大致4nm~44nm的范围内的值。对于粗糙度,在评价试验2-1中,是大致2.5nm~5.5nm的范围内的值,在评价试验2-2中,是大致4.0nm~8.0nm的范围内的值。因而,在评价试验2-1、2-2中,在蚀刻后所残留的非晶硅膜、多晶硅膜的表面的粗糙度的值与蚀刻前的粗糙度的值相比,并未大幅度上升。因而,根据该评价试验2的结果确认到获得这样的本发明的效果:在将晶圆W的温度设为35℃~120℃而供给IF7气体和NH3气体时,能够在晶圆W的面内均匀性较高地进行蚀刻。另外,在晶圆W的温度是35℃的情况下,对于粗糙度的值,在评价试验2-1中,是4.2以下,在评价试验2-2中,是7.2以下,相对于蚀刻前的粗糙度的值的上升被相对抑制。即使晶圆W的温度是比该35℃稍低的值,也认为粗糙度的值没有大幅度变动,因此,推定为在晶圆W的温度是例如30℃~120℃时,获得能够提高上述的蚀刻的均匀性的效果。

而且,如图9所示,对于评价试验2-1,在晶圆W的温度是35℃、60℃的情况下,若NH3气体/IF7气体的流量比比较大,则蚀刻量比较小。不过,在晶圆W的温度是80℃以上的情况下,不管NH3气体/IF7气体的流量比如何,蚀刻量均成为比较高的值,具体而言是30nm以上。并且,如图10所示那样,对于粗糙度,不管晶圆W的温度和NH3气体/IF7气体的流量比如何,均比较低,具体而言是5.6nm以下。

另外,如图11所示,对于评价试验2-2,在晶圆W的温度是35℃、60℃的情况下,若NH3气体/IF7气体的流量比比较大,则蚀刻量比较小。不过,在晶圆W的温度是80℃以上的情况下,不管NH3气体/IF7气体的流量比如何,蚀刻量均成为比较高的值,具体而言是29nm以上。并且,在NH3气体/IF7气体的流量比是0.2、0.6、1.2、1.8的情况下,与将晶圆W的温度设为120℃相比,将晶圆W的温度设为100℃的情况下的蚀刻量较大。因而,对于晶圆W的温度,与设为120℃相比,设为100℃的话,对于蚀刻量而言,可知具有变大的倾向。并且,如从图12清楚那样,对于粗糙度,不管晶圆W的温度和NH3气体/IF7气体的流量比如何,均比较低,具体而言是9nm以下。根据这样的评价试验2-1、2-2的结果可知:对于非晶硅膜和多晶硅膜,为了获得较高的蚀刻速度,并且抑制蚀刻后的粗糙度,更优选将蚀刻时的晶圆W的温度设为80℃~100℃。

而且,在评价试验2-1、2-2中,若对晶圆W的温度是80℃的情况和100℃的情况进行比较,则在NH3气体/IF7气体的流量比相同时,晶圆W的温度是80℃的情况的蚀刻量较大。另外,在NH3气体/IF7气体的流量比是0.2、0.4时,晶圆W的温度是80℃的情况的粗糙度的值较小。另外,在评价试验2-2中,若对晶圆W的温度是80℃的情况和100℃的情况进行比较,则在NH3气体/IF7气体的流量比相同时,晶圆W的温度是80℃的情况的蚀刻量较大且粗糙度的较小。如此在评价试验2中所设定的晶圆W的温度中,出于使蚀刻速度提高、且抑制蚀刻后的粗糙度的观点的观点考虑,80℃成为最优选的值。

不过,如上述那样设定蚀刻时的处理容器41内的压力,因此,在晶圆W的温度是80℃以上时,NH4F从晶圆W升华。在评价试验2-1、2-2中,在晶圆W的温度是80℃以上的情况下,认为蚀刻量比较大的原因在于,即使NH4F附着,也如此引起升华,因此,IF7气体的蚀刻作用未受到该NH4F大幅度妨碍。不过,晶圆W的温度越低,NH3气体和NH4F吸附于晶圆W的概率越高。因而,若在蚀刻时晶圆W的温度过高,则该NH4F的作用变弱。出于这样的理由,推定为成为如下结果:与晶圆W的温度是120℃的情况相比,优选晶圆W的温度是100℃的情况,更优选晶圆W的温度是80℃的情况。并且,即使是相对于该80℃稍微变动的温度,也认为蚀刻速度较高且粗糙度变低。如上述那样,若想到能够在晶圆W的温度是80℃以上时使NH4F升华,则认为特别优选的晶圆W的温度范围是该80℃以上的温度、且比100℃低的温度、具体而言是80℃~90℃。

不过,在评价试验2-1中,若观察晶圆W的温度是35℃或60℃的情况的结果,则在NH3气体的流量比IF7气体的流量大时,也就是说,在NH3气体/IF7气体的流量比是1.2、1.8时,蚀刻量比较小。不过,在NH3气体的流量比IF7气体的流量小时,也就是说,在NH3气体/IF7气体的流量比是0.2~0.6时,除了晶圆W的温度是35℃且NH3气体/IF7气体的流量比是0.6的情况的结果之外,成为蚀刻量比较大的结果。

另外,若观察评价试验2-2中晶圆W的温度是35℃或60℃的情况的结果,则在NH3气体/IF7气体的流量比是1.2、1.8时,蚀刻量比较小。并且,在NH3气体/IF7气体的流量比是0.2~0.6时,除了晶圆W的温度是35℃且NH3气体/IF7气体的流量比是0.6的情况之外,成为蚀刻量比较大的结果。

认为成为这样的结果的原因在于,如上述那样,NH4F从晶圆W升华的温度是80℃以上,在不引起该升华的35℃、60℃的情况下,若NH3气体的流量比较大,则NH4F向晶圆W的附着量变得过剩,从而由IF7气体进行蚀刻的蚀刻量降低。因而,根据该评价试验2的结果确认到如下内容:在晶圆W的温度比80℃低的情况下,优选将NH3气体/IF7气体的流量比设为0.6以下。

另外,在评价试验2-1、2-2中,在将晶圆W的温度设定成80℃以上的情况下,不会因NH3气体/IF7气体的流量比而粗糙度的值大幅度变化,但对于蚀刻量,与将NH3气体/IF7气体的流量比设定成0.6相比,将NH3气体/IF7气体的流量比设定成1.2或1.8的蚀刻量较大。因而,在晶圆W的温度是80℃以上的情况下,确认到如下内容:对于NH3气体/IF7气体的流量比,若是1.2~1.8,则获得较高的蚀刻速度,并且,能够大幅度抑制蚀刻后的粗糙度。也就是说,确认到如下内容:对于NH3气体的流量/IF7气体的流量,优选设为1.2~1.8的范围内。

不过,在晶圆W的温度是80℃以上的情况下,即使NH3气体/IF7气体的流量比是比1.2稍微小的值,也认为蚀刻作用没有大幅度变动,在晶圆W的温度比80℃低的情况下,即使NH3气体/IF7气体的流量比是比0.6稍微大的值,也认为蚀刻作用没有大幅度变动。具体而言,在晶圆W的温度是80℃以上的情况下,对于NH3气体/IF7气体的流量比,只要是例如1以上,在晶圆W的温度比80℃低的情况下,对于NH3气体/IF7气体的流量比,只要是例如1以下,就认为蚀刻作用的变动较少。因而,推定为:在晶圆W的温度是80℃以上的情况下,对于NH3气体/IF7气体的流量比,优选设为1~1.8,在比80℃低的情况下,对于NH3气体的流量/IF7气体的流量,优选设为1以下。

Claims (12)

1.一种蚀刻方法,其特征在于,

该蚀刻方法包括如下工序:向在表面形成有含硅膜的基板供给七氟化碘气体和碱性气体,来对该含硅膜进行蚀刻,

其中,向所述基板供给七氟化碘气体的期间与向所述基板供给所述碱性气体的期间相互重叠,

在将所述基板的温度设成80℃以上的状态下,以使所述碱性气体的流量/所述七氟化碘气体的流量成为1~1.8的方式向收纳该基板的处理容器内供给该碱性气体和七氟化碘气体。

2.根据权利要求1所述的蚀刻方法,其特征在于,

碱性气体、七氟化碘气体向所述基板的供给以该碱性气体、七氟化碘气体的顺序进行。

3.根据权利要求1或2所述的蚀刻方法,其特征在于,

对所述含硅膜进行蚀刻的工序包括如下工序:在将所述基板的温度设为80℃~120℃的状态下,向该基板供给所述七氟化碘气体和所述碱性气体。

4.根据权利要求1或2所述的蚀刻方法,其特征在于,

对所述含硅膜进行蚀刻的工序包括如下工序:将容纳所述基板的处理容器内的压力设为13.3Pa~133.3Pa而供给所述七氟化碘气体和所述碱性气体。

5.根据权利要求1或2所述的蚀刻方法,其特征在于,

所述碱性气体是氨气。

6.一种蚀刻方法,其特征在于,

该蚀刻方法包括如下工序:向在表面形成有含硅膜的基板供给七氟化碘气体和碱性气体,来对该含硅膜进行蚀刻,

其中,向所述基板供给七氟化碘气体的期间与向所述基板供给所述碱性气体的期间相互重叠,以及

在所述基板的温度比80℃低的状态下,以使所述碱性气体的流量/所述七氟化碘气体的流量成为1以下的方式向收纳该基板的处理容器内供给该碱性气体和七氟化碘气体。

7.根据权利要求6所述的蚀刻方法,其特征在于,

碱性气体、七氟化碘气体向所述基板的供给以该碱性气体、七氟化碘气体的顺序进行。

8.根据权利要求6或7所述的蚀刻方法,其特征在于,

对所述含硅膜进行蚀刻的工序包括如下工序:在将所述基板的温度设为30℃以上且低于80℃的状态下,向该基板供给所述七氟化碘气体和所述碱性气体。

9.根据权利要求6或7所述的蚀刻方法,其特征在于,

对所述含硅膜进行蚀刻的工序包括如下工序:将容纳所述基板的处理容器内的压力设为13.3Pa~133.3Pa而供给所述七氟化碘气体和所述碱性气体。

10.根据权利要求6或7所述的蚀刻方法,其特征在于,

所述碱性气体是氨气。

11.一种蚀刻装置,其特征在于,

该蚀刻装置具备:

处理容器;

载置部,其设置于所述处理容器内,用于载置在表面形成有含硅膜的基板;以及

气体供给部,其向所述处理容器内供给七氟化碘气体和碱性气体而对所述含硅膜进行蚀刻,

其中,向所述处理容器内供给七氟化碘气体的期间与向所述处理容器内供给所述碱性气体的期间相互重叠,

在将所述基板的温度设成80℃以上的状态下,所述气体供给部以使所述碱性气体的流量/所述七氟化碘气体的流量成为1~1.8的方式向收纳该基板的所述处理容器内供给该碱性气体和七氟化碘气体。

12.一种蚀刻装置,其特征在于,

该蚀刻装置具备:

处理容器;

载置部,其设置于所述处理容器内,用于载置在表面形成有含硅膜的基板;以及

气体供给部,其向所述处理容器内供给七氟化碘气体和碱性气体而对所述含硅膜进行蚀刻,

其中,向所述处理容器内供给七氟化碘气体的期间与向所述处理容器内供给所述碱性气体的期间相互重叠,

在所述基板的温度比80℃低的状态下,所述气体供给部以使所述碱性气体的流量/所述七氟化碘气体的流量成为1以下的方式向收纳该基板的所述处理容器内供给该碱性气体和七氟化碘气体。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2018-005792 | 2018-01-17 | ||

| JP2018005792A JP6981267B2 (ja) | 2018-01-17 | 2018-01-17 | エッチング方法及びエッチング装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN110047747A CN110047747A (zh) | 2019-07-23 |

| CN110047747B true CN110047747B (zh) | 2023-05-23 |

Family

ID=67214216

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201910043237.0A Active CN110047747B (zh) | 2018-01-17 | 2019-01-17 | 蚀刻方法和蚀刻装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US20190221440A1 (zh) |

| JP (1) | JP6981267B2 (zh) |

| KR (1) | KR102229993B1 (zh) |

| CN (1) | CN110047747B (zh) |

| TW (1) | TWI796416B (zh) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7345334B2 (ja) * | 2019-09-18 | 2023-09-15 | 東京エレクトロン株式会社 | エッチング方法及び基板処理システム |

| JP7550534B2 (ja) | 2020-05-15 | 2024-09-13 | 東京エレクトロン株式会社 | エッチング方法およびエッチング装置 |

| TW202310038A (zh) * | 2021-05-31 | 2023-03-01 | 日商東京威力科創股份有限公司 | 基板處理方法及基板處理裝置 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5698070A (en) * | 1991-12-13 | 1997-12-16 | Tokyo Electron Limited | Method of etching film formed on semiconductor wafer |

| CN101840884A (zh) * | 2009-03-19 | 2010-09-22 | 东京毅力科创株式会社 | 衬底的蚀刻方法以及系统 |

| CN102648171A (zh) * | 2009-12-01 | 2012-08-22 | 中央硝子株式会社 | 蚀刻气体 |

| CN104340960A (zh) * | 2013-08-02 | 2015-02-11 | 中央硝子株式会社 | 由if7生成的氟化碘化合物的回收方法及回收装置 |

| CN104969333A (zh) * | 2013-02-01 | 2015-10-07 | 中央硝子株式会社 | 硅的干蚀刻方法 |

| JP2016139782A (ja) * | 2015-01-23 | 2016-08-04 | セントラル硝子株式会社 | ドライエッチング方法 |

| CN106663626A (zh) * | 2014-09-24 | 2017-05-10 | 中央硝子株式会社 | 附着物的去除方法、干式蚀刻方法以及基板处理装置 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE2548615C2 (de) | 1975-10-30 | 1982-06-03 | M.A.N. Maschinenfabrik Augsburg-Nürnberg AG, 8900 Augsburg | Vorrichtung zur Ansteuerung eines durch Fluiddruck, insbesondere pneumatischen Druck, betätigbaren Anlaß- und Bremsventils an einer umsteuerbaren Brennkraftmaschine |

| US5888906A (en) * | 1996-09-16 | 1999-03-30 | Micron Technology, Inc. | Plasmaless dry contact cleaning method using interhalogen compounds |

| JP2008177209A (ja) * | 2007-01-16 | 2008-07-31 | Taiyo Nippon Sanso Corp | プラズマエッチング方法 |

| DE102008037943B4 (de) * | 2008-08-14 | 2018-04-26 | Nawotec Gmbh | Verfahren und Vorrichtung zum elektronenstrahlinduzierten Ätzen und Halbleiterbauelement mit einer Struktur geätzt mittels eines derartigen Verfahrens |

| CN105051195B (zh) | 2013-02-06 | 2019-09-06 | 埃沃尔瓦公司 | 用于提高莱鲍迪苷d和莱鲍迪苷m之产生的方法 |

| JP6107198B2 (ja) * | 2013-02-14 | 2017-04-05 | セントラル硝子株式会社 | クリーニングガス及びクリーニング方法 |

| WO2015016149A1 (ja) * | 2013-07-29 | 2015-02-05 | 株式会社日立国際電気 | 基板処理装置、半導体装置の製造方法および記録媒体 |

| KR20150060069A (ko) | 2013-11-25 | 2015-06-03 | 에스티엑스조선해양 주식회사 | 조립식 비계장치용 고정부재 |

-

2018

- 2018-01-17 JP JP2018005792A patent/JP6981267B2/ja active Active

-

2019

- 2019-01-09 KR KR1020190002798A patent/KR102229993B1/ko active IP Right Grant

- 2019-01-10 US US16/244,511 patent/US20190221440A1/en not_active Abandoned

- 2019-01-15 TW TW108101455A patent/TWI796416B/zh active

- 2019-01-17 CN CN201910043237.0A patent/CN110047747B/zh active Active

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5698070A (en) * | 1991-12-13 | 1997-12-16 | Tokyo Electron Limited | Method of etching film formed on semiconductor wafer |

| CN101840884A (zh) * | 2009-03-19 | 2010-09-22 | 东京毅力科创株式会社 | 衬底的蚀刻方法以及系统 |

| CN102648171A (zh) * | 2009-12-01 | 2012-08-22 | 中央硝子株式会社 | 蚀刻气体 |

| CN104969333A (zh) * | 2013-02-01 | 2015-10-07 | 中央硝子株式会社 | 硅的干蚀刻方法 |

| CN104340960A (zh) * | 2013-08-02 | 2015-02-11 | 中央硝子株式会社 | 由if7生成的氟化碘化合物的回收方法及回收装置 |

| CN106663626A (zh) * | 2014-09-24 | 2017-05-10 | 中央硝子株式会社 | 附着物的去除方法、干式蚀刻方法以及基板处理装置 |

| JP2016139782A (ja) * | 2015-01-23 | 2016-08-04 | セントラル硝子株式会社 | ドライエッチング方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP6981267B2 (ja) | 2021-12-15 |

| CN110047747A (zh) | 2019-07-23 |

| KR20190088009A (ko) | 2019-07-25 |

| JP2019125715A (ja) | 2019-07-25 |

| TWI796416B (zh) | 2023-03-21 |

| KR102229993B1 (ko) | 2021-03-18 |

| TW201936994A (zh) | 2019-09-16 |

| US20190221440A1 (en) | 2019-07-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN110047747B (zh) | 蚀刻方法和蚀刻装置 | |

| CN109216186B (zh) | 蚀刻方法和残渣去除方法 | |

| CN110476225B (zh) | 基板处理方法和存储介质 | |

| US8232207B2 (en) | Substrate processing method | |

| CN108666213B (zh) | 蚀刻方法以及记录介质 | |

| TW202030794A (zh) | 蝕刻方法、蝕刻裝置以及記憶媒體 | |

| JP5809144B2 (ja) | 基板処理方法および基板処理装置 | |

| KR102272823B1 (ko) | 에칭 방법 및 에칭 장치 | |

| US8828880B2 (en) | Method and apparatus for manufacturing semiconductor device | |

| JP2018207088A (ja) | エッチング方法 | |

| TW201742134A (zh) | 基板處理方法 | |

| JP6161972B2 (ja) | エッチング方法及び記録媒体 | |

| US7993540B2 (en) | Substrate processing method and substrate processing apparatus | |

| JP7413542B2 (ja) | エッチング方法およびエッチング装置 | |

| WO2022102421A1 (ja) | エッチング方法およびエッチング装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PB01 | Publication | ||

| PB01 | Publication | ||

| SE01 | Entry into force of request for substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| GR01 | Patent grant | ||

| GR01 | Patent grant |