CN109427552B - 半导体装置的形成方法 - Google Patents

半导体装置的形成方法 Download PDFInfo

- Publication number

- CN109427552B CN109427552B CN201711131821.9A CN201711131821A CN109427552B CN 109427552 B CN109427552 B CN 109427552B CN 201711131821 A CN201711131821 A CN 201711131821A CN 109427552 B CN109427552 B CN 109427552B

- Authority

- CN

- China

- Prior art keywords

- openings

- enlarged

- structures

- opening

- substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H10P76/204—

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/004—Photosensitive materials

- G03F7/09—Photosensitive materials characterised by structural details, e.g. supports, auxiliary layers

-

- H10P50/28—

-

- H10P76/4085—

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/004—Photosensitive materials

- G03F7/09—Photosensitive materials characterised by structural details, e.g. supports, auxiliary layers

- G03F7/11—Photosensitive materials characterised by structural details, e.g. supports, auxiliary layers having cover layers or intermediate layers, e.g. subbing layers

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/20—Exposure; Apparatus therefor

-

- H10P50/00—

-

- H10P76/2041—

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Structural Engineering (AREA)

- Architecture (AREA)

- Chemical & Material Sciences (AREA)

- Inorganic Chemistry (AREA)

- Drying Of Semiconductors (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Exposure And Positioning Against Photoresist Photosensitive Materials (AREA)

Abstract

本公开一些实施例提供半导体装置的形成方法,包括提供基板以及基板上的图案化层,其中基板包含多个结构以接受处理工艺;形成至少一开口于图案化层中,其中结构部分地露出于至少一开口中;进行方向性蚀刻,使至少一开口于第一方向中的尺寸扩大,以形成至少一扩大的开口;以及经由至少一扩大的开口对结构进行处理工艺。

Description

技术领域

本公开实施例关于以光微影工艺形成图案或装置以用于集成电路,更特别关于在光微影工艺时克服图案角落圆润化的问题并增加图案保真度的方法。

背景技术

半导体集成电路产业已经历指数成长。集成电路材料与设计的技术进展,使每一代的集成电路均比前一代具有更小且更复杂的电路。在集成电路的演进中,功能密度(单位晶片面积所具有的内连线装置数目)通常随着几何尺寸(如最小构件或线路)减少而增加。尺寸缩小的工艺通常有利于增加产能并降低相关成本。上述尺寸缩小亦增加集成电路的工艺复杂度,为实现上述进展,亦需发展集成电路工艺。

举例来说,图案角落圆润化的问题在工艺节点越小时变得越明显。图案角落圆润化指的是设计图案中的直角,在微影工艺(比如光致抗蚀剂图案)与蚀刻工艺(如硬遮罩图案)中变得圆润。此问题在半导体工艺中,会直接影响工艺容忍度与图案保真度,比如关键尺寸变异控制。因此亟需方法降低图案角落圆润化对图案保真度的影响,并改善工艺容忍度。

发明内容

本公开一实施例提供半导体装置的形成方法,包括:提供基板以及基板上的图案化层,其中基板包含多个结构以接受处理工艺;形成至少一开口于图案化层中,其中结构部分地露出于至少一开口中;进行方向性蚀刻,使至少一开口于第一方向中的尺寸扩大,以形成至少一扩大的开口;以及经由至少一扩大的开口对结构进行处理工艺。

附图说明

图1是一些例示性实施例中,集成电路设计的示意图。

图2是本公开一实施例中,克服角落圆润化问题的方法其流程图。

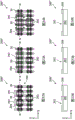

图3A、4A、5A、6A、7A、8A、9A、与10A是一些实施例中,以图2的方法形成的装置于多种工艺阶段的上视图。

图3B、4B、5B、6B、7B、8B、9B、与10B是一些实施例中,以图2的方法形成的装置于多种工艺阶段的剖视图。

图11A与11B是本公开一实施例中,装置于方向性蚀刻工艺中的剖视图。

图12是本公开一实施例中,另一集成电路设计的示意图。

图13A、14A、15A、16A、17A、与18A是一些实施例中,以图2的方法形成的另一装置于多种工艺阶段的上视图。

图13B、14B、15B、16B、17B、与18B是一些实施例中,以图2的方法形成的另一装置于多种工艺阶段的剖视图。

图19A、20A、21A、22A、23A、24A、25A、26A、与27A是一些实施例中,以图2的方法形成的又一装置于多种工艺阶段的上视图。

图19B、20B、21B、22B、23B、24B、25B、26B、与27B是一些实施例中,以图2的方法形成的又一装置于多种工艺阶段的剖视图。

附图标记说明:

c1、c2、c3、c4、c5、c6 行

r1、r2、r3、r4 列

10 集成电路

12 主动区

14 栅极结构

18、276 区块

18'、276' 凸角

18"、276" 凹角

20、282、284 轮廓

26、30 区域

28 距离

100 方法

102、104、106、108、110、112、114 步骤

200、200'、200" 装置

202 基板

204 硬遮罩层

206 光致抗蚀剂层

220 图案

222、288、292 开口

250 等离子体离子束

252 有效水平分量

254 有效垂直分量

260 掺质

272 栅极堆迭

273 栅极片段

274 栅极接点

286、290 孔洞型图案

296 角落

具体实施方式

下述内容提供的不同实施例或实例可实施本公开的不同结构。特定构件与排列的实施例是用以简化本公开而非局限本公开。举例来说,形成第一构件于第二构件上的叙述包含两者直接接触,或两者之间隔有其他额外构件而非直接接触。此外,本公开的多种例子中可重复标号及/或符号,但这些重复仅用以简化与清楚说明,不代表不同实施例及/或设置之间具有相同标号及/或符号的单元之间具有相同的对应关系。

此外,空间性的相对用语如「下方」、「其下」、「较下方」、「上方」、「较上方」、或类似用语可用于简化说明某一元件与另一元件在图示中的相对关系。空间性的相对用语可延伸至以其他方向使用的元件,而非局限于图示方向。元件亦可转动90°或其他角度,因此方向性用语仅用以说明图示中的方向。

图1是本公开一实施例中,集成电路10的布局图。如图1所示,布局10包含多个主动区12,其沿着X方向纵向定向;以及多个栅极结构14,其沿着Y方向纵向定向,且X方向垂直于Y方向。主动区12与栅极结构14的每一交会处形成场效晶体管。在一实施例中,主动区12为鳍状,而形成其上的场效晶体管为鳍状场效晶体管。图1所示的例子具有四列(r1、r2、r3、与r4)的主动区12与六行(c1、c2、c3、c4、c5、与c6)的栅极结构14,两者共同形成24个场效晶体管。在一些设计中,需要一些晶体管的物理特性及/或电性不同于其他晶体管。举例来说,区块18中的晶体管(第一型晶体管)其临界电压不同于区块18外的晶体管(第二型晶体管)。举例来说,第一型晶体管设计为具有高临界电压,而第二型晶体管设计为具有低临界电压。上述设计为静态随机存取记忆单元设计及/或外围电路设计所需。

为实施集成电路10,方法之一为形成遮罩单元覆盖第二型晶体管,并露出第一型晶体管以进行工艺;或者形成遮罩单元覆盖第一型晶体管,并露出第二型晶体管以进行工艺。上述工艺可为离子布植。遮罩单元可包含光致抗蚀剂材料或硬遮罩材料,其可由光微影工艺形成。区块18的边界可位于相邻结构的中间处,比如水平地位于栅极结构14之间,以及垂直地位于主动区12之间。在图1所示的例子中,区块18包含六个直角凸角(外侧角落)18',以及两个直角凹角(内侧角落)18"。凸角指的是区域的角落,其为两线段交会的顶点,且连接两个线段上任一对点的直线是位于区域中。凹角指的是区域的角落,其为两线段交会的顶点,且连接两个线段上任一对点的直线位于区域之外。之后将说明光微影工艺后,凹角或凸角均会圆润化。为简化说明,圆润的凹角与圆润的凸角仍分别称作凹角与凸角。在多种实施例中,区块18的形状可比图1所示的形状简单或复杂。区块18的形状为光微影工艺将形成的例示性目标图案。

理想状态下,实际上的遮罩单元与目标图案(如区块18)的尺寸一致。然而光微影工艺中的光学效应及/或蚀刻偏差,通常会让遮罩单元不符目标图案。相反地,实际的遮罩单元其轮廓20具有圆润的角落,因此遮罩单元的边界靠近一些集成电路结构,特别是在凹角18"。缩小的距离即为失去的设计余裕。图1亦显示围绕晶体管的区域26。区域26指的是遮罩单元的轮廓20不可接触的区域。举例来说,区域26可用于工艺变异如关键尺寸变异与覆盖变异。凹角18"其轮廓20与区域26之间的距离,通常小于凸角18'其轮廓20与区域26之间的距离。轮廓20与区域26之间的最小距离即设计余裕,比如图1的例子所示的距离28。图1亦显示围绕晶体管的区域30。区域30即遮罩单元的轮廓必需围绕的区域。由于集成电路的尺寸持续缩小,越来越需要实际的遮罩单元其轮廓20不具凹角的形成方法,比如在整个微影图案化工艺中,将目标图案(如区块18)转换成一组不具凹角的子图案,以符合特定区域(比如区域26与30)对遮罩与非遮罩的需求。本公开提供一或多个实施例以解决微影图案化工艺中凹角圆润化的问题。这些实施例可用于多种集成电路设计,比如搭配集成电路10或替代集成电路10的设计。

如图2所示,方法100的流程图用于形成孔洞型图案,其通过方向性蚀刻技术具有多个孔洞(或开口)而不具凹角。方法100仅用以举例,而非局限本公开至权利要求未实际限缩的部分。在方法100之前、之中、或之后可进行额外步骤,且方法的其他实施例可置换、省略、或调换一些上述步骤。

在多种实施例中,方法100形成多个开口露出部分的装置结构以进行后续处理(如蚀刻或离子布植),接着施加方向性蚀刻以扩大每一开口,直到完全露出装置结构。在一些实施例中,每一开口的形状可为具有圆润角落的实质上矩形,以避免孔洞型图案中的凹角。此外,方法100可用以形成孔洞型光致抗蚀剂图案或孔洞型硬遮罩图案。图3A至10A及图3B至10B分别为装置200于方法100的第一实施例的多种工艺步骤中的上视图与剖视图,其中具有凹角的目标孔洞型图案调整为不具有凹角的孔洞型图案,且对孔洞型光致抗蚀剂图案进行方向性蚀刻工艺。图11A与11B是例示性的方向性蚀刻工艺。图12、图13A至18A、与图13B至18B分别为装置200'于方法100的第二实施例的多种工艺步骤中的上视图与剖视图,其依据装置结构的几何形状与位置形成孔洞型光致抗蚀剂图案,并省略方法100的步骤106与108。图19A至27A与图19B至27B分别为装置200"于方法100的第三实施例的多种工艺步骤中的上视图与剖视图,其依据装置结构的几何形状与位置形成孔洞型硬遮罩图案,并施加方向性蚀刻工艺至孔洞型硬遮罩图案。在多种实施例中,光微影工艺的方向性蚀刻可分别施加至光致抗蚀剂图案与硬遮罩图案,或者同时施加至光致抗蚀剂图案与硬遮罩图案。举例来说,光微影工艺可依据方法100的实施例,只处理光致抗蚀剂图案、只处理硬遮罩图案、或者处理光致抗蚀剂图案与硬遮罩图案。方法100将搭配图2、图3A至10A、与图3B至10B说明如下。

在步骤102中,方法100(见图2)提供基板202(见图3A与3B)。在多种实施例中,基板202包含一或多个材料层,且可处于装置200的形成工艺的中间步骤。装置200可为集成电路,装置200可为集成电路或其部分,其可包含静态随机存取存储器存储器及/或其他逻辑电路,被动构件如电阻、电容、或电感,或主动构件如p型场效晶体管、n型场效晶体管、金氧半场效晶体管、互补式金氧半晶体管、双极晶体管、高压晶体管、高频晶体管、其他记忆单元、或上述的组合。装置200可包含三维装置与多闸装置,比如双闸场效晶体管、鳍状场效晶体管、三闸场效晶体管、Ω-场效晶体管、栅极全绕装置、或垂直栅极全绕装置。在一实施例中,基板202为半导体基板如晶圆。在一实施例中,基板202包含结晶结构的硅。在其他实施例中,基板202包含其他半导体元素如锗、或半导体化合物如碳化硅、砷化镓、砷化铟、或磷化铟。基板202可包含绝缘层上硅基板、可具有应力以增进效能、可包含磊晶区、可包含隔离区、可包含掺杂区、可包含一或多个半导体装置或其部分、可包含导电及/或非导电层、及/或可包含其他合适的结构与层状物。

装置200在许多方面可与图1的集成电路10实质上类似。装置200具有多个主动区12,其沿着X方向纵向定向;以及多个栅极结构14,其沿着Y方向纵向定向,且X方向垂直于Y方向。场效晶体管(如鳍状场效晶体管)形成于主动区12与栅极结构14的每一交会处。区域30为需要额外处理(如离子布植)的场效晶体管结构,而区域26为不需额外处理(用于区域30)的场效晶体管结构。

在步骤104中,方法100(见图2)形成图案化层于基板202上。图案化层亦可包含多个材料层。在图4A与4B所示的此实施例中,步骤104形成硬遮罩层204于基板202上,并形成光致抗蚀剂层206于硬遮罩层204上。在多种实施例中,可在光致抗蚀剂层206与硬遮罩层204之间新增其他材料层。在一些实施例中,亦可在硬遮罩层204与基板202之间新增其他材料层。

硬遮罩层204可包含非晶硅、氧化硅、氮化硅、氮化钛、氮氧化硅、氮化碳硅、或其他合适材料或组成,且其形成方法可为化学气相沉积、低压化学气相沉积、等离子体增强化学气相沉积、物理气相沉积、原子层沉积、或其他合适的沉积方法。

在一实施例中,光致抗蚀剂层206的形成方法为旋转涂布工艺后进行软烘烤工艺。光致抗蚀剂层可为正光致抗蚀剂或负光致抗蚀剂。正光致抗蚀剂通常不溶于光致抗蚀剂显影剂中,但经射线如深紫外线或极紫外线曝光后转为可溶。例示性的正光致抗蚀剂材料为化学放大光致抗蚀剂。负光致抗蚀剂具有相反特性:通常溶于光致抗蚀剂显影剂中,但经射线如深紫外线或极紫外线曝光后转为不可溶。例示性的负光致抗蚀剂材料为聚合物,其经曝光后可形成分子内交联及/或分子间交联。上述聚合物可由乙基(α-羟基)丙烯酸酯与甲基丙烯酸聚合而成。

在步骤106中,方法100(见图2)提供目标图案如区块18,其形成于图案化层中(见图5A与5B)。区块18对应具有至少一开口的孔洞型图案。在此实施例中,区块18包含一开口。若图案化层依据区块18图案化,则形成的开口将完全露出基板202中需要额外处理的区域(如区域30),而图案化层仍覆盖其下方的其他区域(如区域26)。由于区域26与30的几何尺寸与位置,定义于区块18中的开口将具有多个凸角18'与至少一凹角18"。若将开口转移至图案化层,则光微影工艺中的光学效应及/或蚀刻偏差会使凸角与凹角圆润化。圆润的凹角18"会造成开口轮廓更靠近区域26,即减少设计余裕。

如图5A与5B所示的步骤108中,方法100(见图2)将区块18转为改良图案,比如此实施例中的图案220。定义于区块18中的开口将改为图案220中的多个开口(或孔洞)222。开口222不具有凹角。举例来说,一些实施例中的开口形状为圆形、方形、或矩形。改良的图案220中的开口,可覆盖定义于区块18中的部分开口区域。开口222露出部分的区域30。

在步骤110中,方法100(见图2)形成一或多个孔洞型图案于图案化层中,且一或多个孔洞型图案包含图案220(见图6A与6B)。在此实施例中,图案220中的开口222转移至光致抗蚀剂层206。为了简化附图,形成于光致抗蚀剂层206中的个别开口仍称作开口222。在一实施例中,图案化光致抗蚀剂层206的步骤包括以射线曝光光致抗蚀剂层206、曝光后烘烤、在显影剂中显影光致抗蚀剂层206、以及硬烘烤,以移除光致抗蚀剂层206的曝光部分(或未曝光部分,若采用负光致抗蚀剂)。保留的部分光致抗蚀剂层206成为具有开口222的光致抗蚀剂图案。开口222可具有实质上矩形的上视形状。由于曝光工艺的光学效应等因素,形成于光致抗蚀剂层206中的开口222其上视形状将圆润化。然而开口222只具有凸角,因此圆润化的角落不会劣化开口222与区域26之间的设计余裕。每一开口222可具有实质上相同的尺寸。由于开口222的位置与尺寸,一实施例中的每一开口222完全露出至少一区域30;另一实施例中的每一开口222露出至少一区域且部分地露出至少另一区域30、且又一实施例中的每一开口222只部分地露出一或两个区域30。

在步骤112中,方法100(见图2)沿着一方向对开口222的内侧壁进行方向性蚀刻。如图7A与7B所示的实施例,区域30沿着Y方向纵向延伸,而方向性蚀刻沿着X方向进行,且X方向垂直于Y方向。在一些实施例中,方向性蚀刻对光致抗蚀剂层206具有选择性,且不蚀刻(至少不明显地蚀刻)硬遮罩层204。

开口222的内侧壁可沿着方向性蚀刻的方向扩大,且此蚀刻方向位于与基板202的上表面平行的平面中。在多种实施例中,放向性蚀刻亦具有垂直参数,比如沿着Z方向,且Z方向垂直于基板202的上表面。在一实施例中,步骤112可包含斜向的等离子体蚀刻工艺,其朝着X或Y方向偏向。图11A与11B显示斜向等离子体蚀刻工艺的例子。如图11A所示,等离子体离子束250自Z方向倾斜,因此具有有效水平分量252与有效垂直分量254。在一实施例中,等离子体离子束250可包含氩离子。在其他实施例中,等离子体离子束250可包含氦、硅烷、甲烷、氧、氮、二氧化碳、或上述的组合。装置200可嵌置于晶圆站点上,并沿着X方向、Y方向、或垂直于Z方向的另一方向扫描装置200。当晶圆站点移动时,等离子体离子束250维持相同角度(或角分布)。在图11A所示的例子中,等离子体离子束250具有单峰角分布。在图11B所示的例子中,等离子体离子束250具有双峰角分布,其中等离子体离子束250同时沿着两方向蚀刻光致抗蚀剂层206的图案。通过调整等离子体离子束250的入射角与角分布,可良好地控制水平方向(沿着X及/或Y方向)的蚀刻速率。

如图8A与8B所示,在方向性蚀刻之后,可沿着方向性蚀刻的方向扩大开口222。开口222在扩大后,可称作扩大的开口或延伸的开口。在一些实施例中,扩大的开口222具有实质上相同的尺寸。在一些实施例中,每一扩大的开口222的上视形状为具有圆润角落的实质上矩形。此外,每一扩大的开口222可具有沿着方向性蚀刻的方向纵向延伸的中间线,且至少两个扩大的开口222的中间线未对准(即非共线性),比如图8A所示的两个扩大的开口222。一些扩大的开口222在扩大后可彼此合并。在图8A所示的例子中,两个扩大的开口222仍维持彼此分离。

与定义于目标图案18中的开口相较,扩大的开口222只露出一部分定义于目标图案18中的开口。图案化层仍覆盖扩大的开口222之间的部份基板202。与此同时,一些实施例中扩大的开口222完全露出区域30。每一区域30完全露出于开口222之一中,且在后续步骤中可经由开口222对区域30进行额外处理。由于扩大的开口222中不具有凹角,因此可维持设计余裕并增加图案保真度。

如图9A与9B所示,步骤112可还包含将光致抗蚀剂层206中扩大的开口222转移至硬遮罩层204。采用图案化的光致抗蚀剂层206作为蚀刻遮罩,并蚀刻硬遮罩层204。举例来说,硬遮罩层204的蚀刻方法可为湿蚀刻工艺、干蚀刻工艺、原子层蚀刻工艺、或其他合适的蚀刻工艺。蚀刻工艺可消耗部分的光致抗蚀剂层206。蚀刻后若残留任何的光致抗蚀剂层206,可采用光致抗蚀剂剥除工艺移除。

在步骤114中,方法100(见图2)采用硬遮罩层204中扩大的开口222,对区域30(见图10A与10B)进行进行额外处理。在一些实施例中,方法100采用图案化的硬遮罩层204作为离子布植遮罩,以将掺质260布植至区域30中。硬遮罩层204覆盖的区域26仍实质上不含掺质260。在另一实施例中,方法100(见图2)采用图案化的光致抗蚀剂层206作为离子布植遮罩。举例来说,方法100可形成光致抗蚀剂层206于基板202上,并省略硬遮罩层204。在曝光与显影光致抗蚀剂层206后,可进一步对光致抗蚀剂层206进行前述的方向性蚀刻工艺。之后对基板202进行离子布植工艺时,图案化的光致抗蚀剂层206可作为遮罩单元。

图12、图13A至18A、与图13B至18B分别为装置200'于方法100的第二实施例的多种工艺步骤中的上视图与剖视图,其略过方法100的步骤106与108。此实施例有许多方面与图1、图3A至10A、及图3B至10B所述的内容类似。

如图12所示,装置200'包含多个栅极结构272,其沿着Y方向纵向定向。在一实施例中,每一栅极结构272具有需额外处理的栅极片段273。额外处理可为栅极切割工艺,其自对应的栅极结构272移除栅极片段273,并将栅极结构272分隔成多个不相连的片段。在一些设计中,一或多个栅极结构272可具有额外结构,比如图12的例子所示的栅极接点274。在栅极切割工艺中,栅极接点274可维持不变。为实施装置200',方法之一为形成遮罩单元以覆盖栅极片段273以外的栅极堆迭272与栅极接点274,并经由遮罩单元中的开口露出栅极片段273以进行工艺。举例来说,区块276为遮罩单元中的开口。栅极接点274为区块276未接触的区域。为了适用于相邻结构,区块276可包含多个直角的凸角276'与至少一直角的凹角276"。区块276的形状为光微影工艺形成的目标图案。由于光微影工艺的光学效应及/或蚀刻偏差,遮罩单元通常无法正确地符合目标图案。举例来说,遮罩单元可包含光致抗蚀剂层与硬遮罩层。轮廓282指的是曝光与显影光致抗蚀剂后,形成于光致抗蚀剂层中的开口(比如显影后检查的轮廓)。轮廓284指的是将光致抗蚀剂层中的开口转移至硬遮罩层后的开口(比如蚀刻后检查的轮廓)。形成于遮罩单元中的实际开口的轮廓282与284,其上视图均具有圆润的角落。特别是硬遮罩层中的轮廓284,由于处理栅极片段273的步骤可采用图案化的硬遮罩层作为蚀刻遮罩,栅极接点274需位于轮廓284之外。圆润的凹角会让遮罩单元的边界更靠近需维持覆盖的结构,因此会缩小设计余裕。目前需要新的方法形成开口于遮罩单元中,其不具凹角且在整个光微影工艺中符合特定区域(比如栅极接点274与栅极片段273)的遮罩与未遮罩需求。

如图13A与13B所示,方法100的步骤102提供基板202。在多种实施例中,基板202包含一或多个材料层,且可处于装置200'的形成工艺其中间阶段。装置200'包含多个栅极堆迭272。每一栅极堆迭272具有栅极片段273,且后续的栅极切割工艺将移除栅极片段273。栅极堆迭272的一者还包含栅极接点274形成其上。

如图14A与14B所示,方法100的步骤104形成图案化层于基板202上。图案化层可还包含多个材料层,比如硬遮罩层204,以及硬遮罩层204上的光致抗蚀剂层206。

如图15A与15B所示,方法100的步骤110形成孔洞型图案286,其包含多个开口288。在一些实施例中,可视情况进行或省略方法100中的步骤106与108。孔洞型图案286可取决于需露出的结构(如栅极片段273)的几何形状与位置,而不需由初始的目标图案开始。在图15A与15B中的实施例,先将孔洞型图案286转移至光致抗蚀剂层206。开口288形成于每一栅极片段273上。开口288露出部分的栅极片段273。在一例中,在Y方向上的开口288其尺寸大于栅极片段273,但在X方向上的开口288其尺寸小于栅极片段273。开口288不具有凹角。举例来说,开口288的上视形状可为圆形、方形、矩形。在一例中,每一开口288具有实质上相同的形状与尺寸,比如具有圆润角落的矩形。

如图16A与16B所示,方法100的步骤112沿着一方向对开口288的内侧壁进行方向性蚀刻。在此实施例中,栅极堆迭272沿着Y方向纵向延伸,而方向性蚀刻沿着X方向进行,且X方向垂直于Y方向。在方向性蚀刻后,可在X方向上扩大开口288。在一例中,每一扩大的开口288为具有圆润角落的实质上矩形。此外,每一扩大的开口288可具有实质上类似的尺寸,以及沿着X方向纵向延伸的中间线。由于栅极接点274导致一些开口288偏移,因此至少两个扩大的开口288的中间线未对准。每一扩大的开口288完全露出下方的个别的栅极片段273。一些扩大的开口288在扩大后可彼此合并,或者维持分离。在图16A与16B所示的实施例中,扩大的开口288维持分离。

如图17A与17B所示,方法100将光致抗蚀剂层206中扩大的开口288转移至硬遮罩层204。以图案化的光致抗蚀剂层206作为蚀刻遮罩,并蚀刻硬遮罩层204。此蚀刻工艺会消耗部分的光致抗蚀剂层206。蚀刻后若残留任何的光致抗蚀剂层206,可采用光致抗蚀剂剥除工艺移除。

如图18A与18B所示,方法100的步骤114采用硬遮罩层204中扩大的开口288,在栅极片段273上进行额外处理如栅极切割工艺。在栅极切割工艺中可经由扩大的开口288,施加合适的蚀刻剂至栅极堆迭272以蚀刻栅极片段273。由于扩大的开口288中不存在圆润的凹角,因此开口288与栅极接点274之间可维持合适距离,并增加图案保真度。

图19A至27A与图19B至27B分别为装置200"于方法100的第三实施例的多种工艺步骤中的上视图与剖视图,其略过方法100的步骤106与108,且对孔洞型硬遮罩层而非光致抗蚀剂层进行方向性蚀刻工艺。此实施例有许多方面与图1、图3A至10A、及图3B至10B所述的内容类似。

如图19A与19B所示,方法100的步骤102提供基板202。在多种实施例中,基板202包含一或多个材料层,且可处于装置200"的形成工艺其中间阶段。装置200"包含区域30以进行后续处理如离子布植,以及区域26以避免后续处理。如图20A与20B所示,方法100的步骤104形成图案化层于基板202上。图案化层可包含硬遮罩层204,与硬遮罩层204上的光致抗蚀剂层206。

如图21A与21B所示,方法100的步骤110形成孔洞型图案290于硬遮罩层204中。孔洞型图案290包含多个开口290,且开口290各自不含凹角。在一实施例中,先采用光微影工艺形成孔洞型图案290于光致抗蚀剂层206中,接着以蚀刻工艺将孔洞型图案290转移至硬遮罩层204。蚀刻工艺会消耗部分的光致抗蚀剂层206。开口292的角落因光微影工艺中的光学效应及/或蚀刻偏差而产生不想要的圆润化,但全部均为圆润凸角可避免图案保真度更差的圆润凹角。开口292可露出部分的区域30。在此实施例中,每一区域30只部分的露出于个别的开口292中。在一例中,开口292部分地露出侧壁边缘上的一区域30,并部分地露出相反侧壁边缘上的另一区域30。

如图22A与22B所示,方法100的步骤112对形成于硬遮罩层204中的开口292其内侧壁进行第一方向性蚀刻。在此实施例中,区域30沿着Y方向纵向延伸,方向性蚀刻沿着X方向,且X方向垂直于Y方向。在方向性蚀刻之后,可在X方向扩大开口292。如图23A与23B所示,一些扩大的开口292可合并,而一些扩大的开口292仍维持分离。扩大的开口292完全露出区域30,而每一开口292完全露出至少一区域30。在一例中,上视图中的开口292为具有圆润角落的实质上矩形。在方向性蚀刻之后,图案化层仍覆盖区域26。

如图24A与24B所示的一些实施例,方法100可视情况对开口292的内侧壁进行第二方向性蚀刻。在图24A中的例示性实施例,第二方向性蚀刻沿着Y方向进行,且Y方向垂直于X方向。第二方向性蚀刻可在Y方向扩大开口292,让区域30与开口292的轮廓在Y方向之间的距离增加,使对区域30进行的后续处理具有较大的工艺容忍度。在一实施例中,对开口292进行的第一与第二方向性蚀刻可同时进行。此外,对开口292进行的第一与第二方向性蚀刻可各自包含垂直参数(如沿着Z方向)。对开口292进行的蚀刻可对硬遮罩层204具有选择性,且不蚀刻基板202。在一实施例中,对开口292进行的蚀刻可采用斜向等离子体蚀刻工艺如前述。对开口292进行双重方向性蚀刻的结果,如图25A与25B所示。开口292在Y方向可更靠近彼此。在一些实施例中,开口292可合并成一个较大开口,如图26A与26B所示。此外,开口292的角落296可变得更锐利,其各自具有实质上90°的角度(见图25A)。在第一与第二方向蚀刻中,靠近角落296的开口292的部分内侧壁的蚀刻量会大于其他部分的内侧壁的蚀刻量,因为这些内侧壁比其他部分接收更多蚀刻剂或离子轰击。举例来说,这些内侧壁接收第一与第二方向性蚀刻步骤的蚀刻剂与离子轰击两者,而其他部分只接收第一与第二方向性蚀刻步骤的蚀刻剂或离子轰击(而非接收两者)。如此一来,角落296变得较尖锐且各自具有实质上90°的角度。

如图27A与27B所示,方法的步骤114采用硬遮罩层204中扩大的开口292对区域30进行后续处理。在一些实施例中,后续处理包含离子布植。区域30经由开口292接收掺质260。被硬遮罩层26覆盖的区域26,维持实质上不含掺质260。

值得注意的是,本公开讨论发明概念的多种实施例。这些实施例并未彼此相斥。本公开可提供许多优点,但这些优点并非用以局限本公开。举例来说,本公开多种实施例可应用于光微影工艺中,以克服图案中的凹角圆润化问题。本公开实施例形成的遮罩单元(如蚀刻遮罩或离子布植遮罩)不具有凹角,其可改善工艺容忍度并增加图案保真度。

在本公开一例示性的实施例中,半导体装置的形成方法包括:提供基板以及基板上的图案化层,其中基板包含多个结构以接受处理工艺;形成至少一开口于图案化层中,其中结构部分地露出于至少一开口中;进行方向性蚀刻,使至少一开口于第一方向中的尺寸扩大,以形成至少一扩大的开口;以及经由至少一扩大的开口对结构进行处理工艺。在一实施例中,进行方向型蚀刻以形成至少一扩大的开口的步骤中,至少一扩大的开口完全露出结构。在一实施例中,至少一开口不具有凹角。在一实施例中,每一扩大的开口为具有圆润角落的实质上矩形图案。在一实施例中,至少一扩大的开口包含两个或更多扩大的开口,且扩大的开口沿着第一方向纵向延伸的中心线未对准。在一实施例中,至少一扩大的开口包含两个或更多扩大的开口合并。在一实施例中,至少一扩大的开口包含两个或更多扩大的开口彼此分离。在一实施例中,进行方向性蚀刻的步骤包括进行斜向等离子体蚀刻工艺。在一实施例中,每一结构沿着第二方向纵向延伸,且第一方向垂直于第二方向。在一实施例中,结构为主动区,且处理工艺包含离子布植。在一实施例中,结构为栅极结构,且处理工艺包括栅极切割工艺。

在本公开另一例示性的实施例中,半导体装置的形成方法包括:提供基板,且基板具有多个结构以进行工艺;形成图案化层于基板上;形成多个孔洞于图案化层中,而孔洞不具有凹角且部分地露出结构;对每一孔洞的内侧壁进行方向性蚀刻工艺,以形成多个延伸的孔洞,且延伸的孔洞完全露出结构;以及经由延伸的孔洞对结构进行处理工艺。在一实施例中,每一延伸的孔洞尺寸与其他延伸的孔洞尺寸实质上相同。在一实施例中,每一延伸的孔洞彼此分离。在一实施例中,每一孔洞完全露出至少一结构。在一实施例中,至少一孔洞完全露出结构的一者,且部分地露出结构的另一者。

在本公开另一例示性的实施例中,半导体装置的形成方法包括:提供基板与基板上的图案化层,其中基板具有区域以进行工艺;提供目标图案以对应开口,且开口具有至少一凹角且应形成于图案化层中以完全露出区域;将目标图案转为调整图案,其中开口分成多个孔洞,且每一孔洞不具有凹角;依据调整图案形成孔洞于图案化层中;以及进行方向性蚀刻扩大每一孔洞于方向的尺寸,以形成多个扩大的孔洞,其中扩大的孔洞完全露出区域。在一实施例中,扩大的孔洞覆盖的区域小于开口。在一实施例中,孔洞部分地露出区域。在一实施例中,扩大的孔洞包括第一扩大的孔洞,其第一中心线沿着方向纵向延伸;以及第二扩大的孔洞,其第二中心线沿着方向纵向延伸,且其中第一中心线与第二中心线不具共线性。

上述实施例的特征有利于本技术领域技术人员理解本公开。本技术领域技术人员应理解可采用本公开作基础,设计并变化其他工艺与结构以完成上述实施例的相同目的及/或相同优点。本技术领域技术人员亦应理解,这些等效置换并未脱离本公开精神与范畴,并可在未脱离本公开的精神与范畴的前提下进行改变、替换、或变动。

Claims (27)

1.一种半导体装置的形成方法,包括:

提供一基板以及该基板上的一图案化层,其中该基板包含多个结构以接受一处理工艺;

形成至少一开口于该图案化层中,其中在一上视图中的该些结构部分地露出于至少一该开口下;

进行一方向性蚀刻,使该图案化层中的至少一该开口于第一方向中的尺寸扩大,以形成至少一扩大的开口于该图案化层中;以及

经由至少一该扩大的开口对该些结构进行该处理工艺,其中每一该些结构沿着第二方向纵向延伸,且第一方向垂直于第二方向。

2.如权利要求1所述的半导体装置的形成方法,其中进行该方向性蚀刻以形成至少一该扩大的开口的步骤中,在该上视图中至少一该扩大的开口完全露出该些结构。

3.如权利要求1所述的半导体装置的形成方法,其中在该上视图中至少一该开口不具有一凹角。

4.如权利要求3所述的半导体装置的形成方法,其中在该上视图中每一该扩大的开口为具有圆润角落的矩形图案。

5.如权利要求1所述的半导体装置的形成方法,其中在该上视图中至少一该扩大的开口包含两个或更多扩大的开口,且该些扩大的开口沿着第一方向纵向延伸的中心线未对准。

6.如权利要求1所述的半导体装置的形成方法,其中至少一该扩大的开口包含两个或更多扩大的开口合并。

7.如权利要求1所述的半导体装置的形成方法,其中至少一该扩大的开口包含两个或更多扩大的开口彼此分离。

8.如权利要求1所述的半导体装置的形成方法,其中进行该方向性蚀刻的步骤包括对该图案化层进行斜向等离子体蚀刻工艺。

9.如权利要求1所述的半导体装置的形成方法,其中该些结构为多个主动区,且该处理工艺包含离子布植。

10.如权利要求1所述的半导体装置的形成方法,其中该些结构为多个栅极结构,且该处理工艺包括栅极切割工艺。

11.一种半导体装置的形成方法,包括:

提供一基板,且该基板具有多个结构以进行工艺;

形成一图案化层于该基板上;

形成多个孔洞于该图案化层中,而该些孔洞不具有凹角且部分地露出该些结构;

对每一该些孔洞的内侧壁进行一方向性蚀刻工艺,以形成多个延伸的孔洞,且该些延伸的孔洞完全露出该些结构;以及

经由该些延伸的孔洞对结构进行一处理工艺。

12.如权利要求11所述的半导体装置的形成方法,其中每一该些延伸的孔洞尺寸与其他该些延伸的孔洞尺寸相同。

13.如权利要求11所述的半导体装置的形成方法,其中每一该些延伸的孔洞彼此分离。

14.如权利要求11所述的半导体装置的形成方法,其中每一该些孔洞完全露出至少一该些结构。

15.如权利要求11所述的半导体装置的形成方法,其中至少一该些孔洞完全露出该些结构的一者,且部分地露出该些结构的另一者。

16.一种半导体装置的形成方法,包括:

提供一基板与该基板上的一图案化层,其中该基板具有一区域以进行工艺;

提供一目标图案以对应一开口,且该开口具有至少一凹角且形成于该图案化层中以完全露出该区域;

将该目标图案转为一调整图案,其中该开口分成多个孔洞,且每一该些孔洞不具有凹角;

依据该调整图案形成多个孔洞于该图案化层中;以及

进行一方向性蚀刻扩大每一该些孔洞于一方向的尺寸,以形成多个扩大的孔洞,其中该些扩大的孔洞完全露出该区域。

17.如权利要求16所述的半导体装置的形成方法,其中该些扩大的孔洞覆盖的该区域小于该开口。

18.如权利要求16所述的半导体装置的形成方法,其中该些孔洞部分地露出该区域。

19.如权利要求16所述的半导体装置的形成方法,其中该些扩大的孔洞包括一第一扩大的孔洞,其第一中心线沿着该方向纵向延伸;以及一第二扩大的孔洞,其第二中心线沿着该方向纵向延伸,且其中该第一中心线与该第二中心线不具共线性。

20.一种半导体装置的形成方法,包括:

提供一基板,且该基板具有多个结构以进行工艺;

形成一图案化层于该基板上;

形成多个开口于该图案化层中,而在一上视图中该些开口不具有凹角且部分地露出该些结构;

对该图案化层中的每一该些开口的内侧壁进行一方向性蚀刻工艺,以形成多个延伸的开口于该图案化层中,且在该上视图中该些延伸的开口完全露出该些结构;以及

经由该些延伸的开口对该些结构进行离子布植工艺。

21.如权利要求20所述的半导体装置的形成方法,其中每一该些延伸的开口尺寸与其他该些延伸的开口尺寸实质上相同。

22.如权利要求20所述的半导体装置的形成方法,其中每一该些延伸的开口与其他该些延伸的开口彼此分离。

23.如权利要求20所述的半导体装置的形成方法,其中在该上视图中每一该些开口完全露出至少一该些结构。

24.如权利要求20所述的半导体装置的形成方法,其中在该上视图中至少一该些开口完全露出该些结构的一者,且部分地露出该些结构的另一者。

25.一种半导体装置的形成方法,包括:

提供一基板与该基板上的一图案化层,其中该基板具有一区域以进行工艺;

形成多个开口于该图案化层中,且在一上视图中该些开口部分地露出该区域;

进行一方向性蚀刻以扩大该图案化层中的每一该些开口于第一方向的尺寸,以形成多个扩大的开口于该图案化层中,其中在该上视图中该些扩大的开口完全露出该区域;以及

经由该些扩大的开口对该区域进行离子布植。

26.如权利要求25所述的半导体装置的形成方法,其中在上视图中该些开口的每一者不具有凹角。

27.如权利要求25所述的半导体装置的形成方法,其中在该上视图中该些扩大的开口具有一第一扩大的开口,其第一中心线沿着一方向纵向延伸;以及一第二扩大的开口,其第二中心线沿着该方向纵向延伸,且其中第一中心线与第二中心线不具共线性。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US15/689,172 US10861698B2 (en) | 2017-08-29 | 2017-08-29 | Pattern fidelity enhancement |

| US15/689,172 | 2017-08-29 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN109427552A CN109427552A (zh) | 2019-03-05 |

| CN109427552B true CN109427552B (zh) | 2023-05-23 |

Family

ID=65435429

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201711131821.9A Active CN109427552B (zh) | 2017-08-29 | 2017-11-15 | 半导体装置的形成方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (4) | US10861698B2 (zh) |

| CN (1) | CN109427552B (zh) |

| TW (1) | TWI742191B (zh) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10861698B2 (en) * | 2017-08-29 | 2020-12-08 | Taiwan Semiconductor Manufacturing Co., Ltd. | Pattern fidelity enhancement |

| CN109411415B (zh) * | 2018-09-07 | 2021-04-30 | 上海集成电路研发中心有限公司 | 一种半导体结构的形成方法 |

| US11043632B2 (en) * | 2019-09-17 | 2021-06-22 | Headway Technologies, Inc. | Ion beam etching process design to minimize sidewall re-deposition |

| US11796922B2 (en) | 2019-09-30 | 2023-10-24 | Taiwan Semiconductor Manufacturing Co., Ltd. | Method of manufacturing semiconductor devices |

| US20220102200A1 (en) * | 2020-09-30 | 2022-03-31 | Taiwan Semiconductor Manufacturing Company, Ltd. | Patterning material including carbon-containing layer and method for semiconductor device fabrication |

| CN114496737B (zh) * | 2020-11-12 | 2024-09-13 | 长鑫存储技术有限公司 | 半导体器件及其制造方法 |

| US12362177B2 (en) | 2022-05-31 | 2025-07-15 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method of manufacturing semiconductor devices |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0882915A (ja) * | 1994-09-14 | 1996-03-26 | Hitachi Ltd | フォトマスクパターン設計方法および設計システム |

| CN109791874A (zh) * | 2016-09-22 | 2019-05-21 | 瓦里安半导体设备公司 | 使用方向性离子形成图案化特征的技术 |

Family Cites Families (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2000067302A1 (en) | 1999-04-28 | 2000-11-09 | Nikon Corporation | Exposure method, exposure device, exposure system, mask and device manufacturing method |

| JP2002141421A (ja) * | 2000-10-31 | 2002-05-17 | Toshiba Corp | 半導体集積回路装置 |

| KR100408405B1 (ko) * | 2001-05-03 | 2003-12-06 | 삼성전자주식회사 | 반도체 소자의 제조 장치 |

| JP4817746B2 (ja) * | 2005-07-27 | 2011-11-16 | 株式会社東芝 | 半導体装置の設計データ処理方法、そのプログラム、及び半導体装置の製造方法 |

| DE112007002810T5 (de) * | 2007-01-05 | 2009-11-12 | Nxp B.V. | Ätzverfahren mit verbesserter Kontrolle der kritischen Ausdehnung eines Strukturelements an der Unterseite dicker Schichten |

| KR100950472B1 (ko) * | 2007-12-28 | 2010-03-31 | 주식회사 하이닉스반도체 | 4f2 트랜지스터를 갖는 반도체 소자의 제조방법 |

| US9213234B2 (en) | 2012-06-01 | 2015-12-15 | Taiwan Semiconductor Manufacturing Company, Ltd. | Photosensitive material and method of lithography |

| US9256133B2 (en) | 2012-07-13 | 2016-02-09 | Taiwan Semiconductor Manufacturing Company, Ltd. | Apparatus and method for developing process |

| US9028915B2 (en) | 2012-09-04 | 2015-05-12 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method of forming a photoresist layer |

| US9093530B2 (en) | 2012-12-28 | 2015-07-28 | Taiwan Semiconductor Manufacturing Company, Ltd. | Fin structure of FinFET |

| US9012132B2 (en) | 2013-01-02 | 2015-04-21 | Taiwan Semiconductor Manufacturing Company, Ltd. | Coating material and method for photolithography |

| US9223220B2 (en) | 2013-03-12 | 2015-12-29 | Taiwan Semiconductor Manufacturing Company, Ltd. | Photo resist baking in lithography process |

| US9146469B2 (en) | 2013-03-14 | 2015-09-29 | Taiwan Semiconductor Manufacturing Company, Ltd. | Middle layer composition for trilayer patterning stack |

| US8796666B1 (en) | 2013-04-26 | 2014-08-05 | Taiwan Semiconductor Manufacturing Company, Ltd. | MOS devices with strain buffer layer and methods of forming the same |

| TWI667708B (zh) * | 2013-11-11 | 2019-08-01 | Tokyo Electron Limited | 蝕刻後聚合物及硬遮罩移除之加強型移除用方法及硬體 |

| US9548303B2 (en) | 2014-03-13 | 2017-01-17 | Taiwan Semiconductor Manufacturing Company, Ltd. | FinFET devices with unique fin shape and the fabrication thereof |

| US20160064239A1 (en) * | 2014-08-28 | 2016-03-03 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method for Integrated Circuit Patterning |

| US9536759B2 (en) | 2015-05-29 | 2017-01-03 | Taiwan Semiconductor Manufacturing Co., Ltd | Baking apparatus and method |

| US10049918B2 (en) * | 2016-09-29 | 2018-08-14 | Taiwan Semiconductor Manufacturing Co., Ltd. | Directional patterning methods |

| US10658184B2 (en) * | 2016-12-15 | 2020-05-19 | Taiwan Semiconductor Manufacturing Co., Ltd. | Pattern fidelity enhancement with directional patterning technology |

| US10861698B2 (en) * | 2017-08-29 | 2020-12-08 | Taiwan Semiconductor Manufacturing Co., Ltd. | Pattern fidelity enhancement |

-

2017

- 2017-08-29 US US15/689,172 patent/US10861698B2/en active Active

- 2017-11-08 TW TW106138604A patent/TWI742191B/zh active

- 2017-11-15 CN CN201711131821.9A patent/CN109427552B/zh active Active

-

2020

- 2020-12-07 US US17/114,070 patent/US11791161B2/en active Active

-

2023

- 2023-07-30 US US18/361,878 patent/US12334342B2/en active Active

-

2025

- 2025-06-12 US US19/236,606 patent/US20250308892A1/en active Pending

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0882915A (ja) * | 1994-09-14 | 1996-03-26 | Hitachi Ltd | フォトマスクパターン設計方法および設計システム |

| CN109791874A (zh) * | 2016-09-22 | 2019-05-21 | 瓦里安半导体设备公司 | 使用方向性离子形成图案化特征的技术 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20250308892A1 (en) | 2025-10-02 |

| TW201913226A (zh) | 2019-04-01 |

| CN109427552A (zh) | 2019-03-05 |

| TWI742191B (zh) | 2021-10-11 |

| US20190067000A1 (en) | 2019-02-28 |

| US11791161B2 (en) | 2023-10-17 |

| US20210118674A1 (en) | 2021-04-22 |

| US12334342B2 (en) | 2025-06-17 |

| US10861698B2 (en) | 2020-12-08 |

| US20230369047A1 (en) | 2023-11-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN109427552B (zh) | 半导体装置的形成方法 | |

| US11126774B2 (en) | Layout optimization of a main pattern and a cut pattern | |

| US11158509B2 (en) | Pattern fidelity enhancement with directional patterning technology | |

| US20240379358A1 (en) | Methods for integrated circuit design and fabrication | |

| US10763113B2 (en) | Lithographic technique for feature cut by line-end shrink | |

| US9274413B2 (en) | Method for forming layout pattern | |

| CN109935515B (zh) | 形成图形的方法 | |

| US10593551B2 (en) | Method to increase the process window in double patterning process | |

| US12315737B2 (en) | Feature patterning using pitch relaxation and directional end-pushing with ion bombardment | |

| US20070105053A1 (en) | Method of manufacturing semiconductor device | |

| US9274416B2 (en) | Method for forming photo-mask and OPC method | |

| US8765329B2 (en) | Sub-resolution rod in the transition region | |

| US20140120729A1 (en) | Method for removing a patterned hard mask layer | |

| CN107479338B (zh) | 结构上的光致抗蚀剂图案制作工艺 | |

| TW201419493A (zh) | 半導體佈局圖案之製作方法、半導體元件之製作方法以及半導體元件 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PB01 | Publication | ||

| PB01 | Publication | ||

| SE01 | Entry into force of request for substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| GR01 | Patent grant | ||

| GR01 | Patent grant |