CN103813640A - 一种全印制电路板及其制造方法 - Google Patents

一种全印制电路板及其制造方法 Download PDFInfo

- Publication number

- CN103813640A CN103813640A CN201210450725.1A CN201210450725A CN103813640A CN 103813640 A CN103813640 A CN 103813640A CN 201210450725 A CN201210450725 A CN 201210450725A CN 103813640 A CN103813640 A CN 103813640A

- Authority

- CN

- China

- Prior art keywords

- groove

- substrate

- insulating properties

- allprint

- base material

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Abstract

本发明涉及印制电路板技术领域,尤其涉及一种全印制电路板及其制造方法,以解决全印制电子技术印制电路板存在形成导电线路和图形精度不高,且对导电油墨要求较高的问题。本发明实施例的方法包括将至少两个含有导体图形的基片进行叠板和压合处理,形成多层全印制电路板的方法;或将含有导体图形的基片、绝缘性基材和保护膜进行叠板和压合处理,在绝缘性基材的表面制作至少一个凹槽,并在部分或全部凹槽处制作盲孔,在凹槽和盲孔处填充导电油墨,形成多层全印制电路板的方法;避免了全印制电子技术印制电路板形成导电线路和图形精度不高,且对导电油墨要求较高的问题,提高了多层全印制电路板的导电线路和图形精度,降低了对导电油墨的要求。

Description

技术领域

本发明涉及印制电路板技术领域,尤其涉及一种全印制电路板及其制造方法。

背景技术

在电子产品趋于多功能复杂化的前提下,集成电路元件的接点距离随之缩小,信号传送的速度则相对提高,随之而来的是接线数量的提高、点间配线的长度局部性缩短,这些就需要应用高密度线路配置及微孔技术实现,因此全印制电子技术应运而生。全印制电子技术(Print Full Electronic Technology)是指采用快速、高效和灵活的数字喷墨打印技术在基板(无导体)上面形成导电线路和图形,或形成整个印制电路板的过程。

全印制电子技术印制电路板的过程是利用超级喷墨打印机把金属纳米油墨喷印到基板上形成平面的线路层,然后在这个层平面上喷印连接凸块,用于层间连接,再形成层间的绝缘层,然后再在绝缘层上形成第二层的线路,依此类推,便可形成所需层数的多层线路板,即全印制电子的PCB。

但全印制电子技术印制电路板存在一些缺陷,由于电路板上接线数量较多,线与线之间间隔较小,全印制电子技术印制电路板采用喷墨打印的方法形成导电线路和图形,图形精度不高,易出现短路等现象;另外,印制电路板需使用金属纳米级油墨,要求油墨要与基板表面保持一定的接触角,即油墨本身要有一定大小的表面张力,因此,对导电油墨要求较高。

因此,全印制电子技术印制电路板存在形成导电线路和图形精度不高,且对导电油墨要求较高的问题。

发明内容

本发明实施例提供一种全印制电路板及其制造方法,以解决全印制电子技术印制电路板存在形成导电线路和图形精度不高,且对导电油墨要求较高的问题。

本发明实施例提供了一种全印制电路板的基片的制造方法,包括:

在绝缘性基材的上表面和下表面预贴合保护膜;

在绝缘性基材的上表面和/或下表面制作至少一个凹槽,并在部分或全部凹槽处制作通孔;在凹槽和通孔处填充导电油墨;去除绝缘性基材表面预贴合保护膜,形成含有导体图形的基片。

本发明实施例提供了一种利用全印制电路板的基片制造全印制电路板的方法,包括:

将至少两个含有导体图形的基片进行叠板和压合处理,形成多层全印制电路板;

其中,多层全印制电路板的上表面和下表面都含有凹槽,且任意相邻两个含有导体图形的基片相接处的表面含有凹槽,且每个含有导体图形的基片通孔进行叠板和压合处理后形成多层全印制电路板的叠合导通孔。

本发明实施例提供了一种利用全印制电路板的基片制造全印制电路板的方法,包括:

按照含有导体图形的基片、绝缘性基材和保护膜的顺序进行叠板和压合处理,其中含有导体图形的基片是上、下表面都含有凹槽的导体图形的基片,且含有导体图形的基片中与绝缘性基材接触的表面是上表面和/或下表面;在绝缘性基材的表面制作至少一个凹槽,并在部分或全部凹槽处制作盲孔;在凹槽和所述盲孔处填充导电油墨,去除绝缘性基材表面预贴合的保护膜,形成多层全印制电路板。

本发明实施例提供了一种单层全印制电路板的制作方法,包括:

在绝缘性基材的需要制作凹槽的表面预贴合保护膜,并在预贴合保护膜的表面制作至少一个凹槽;在凹槽处填充导电油墨;去除绝缘性基材表面预贴合保护膜,形成单层全印制电路板。

本发明实施例提供了一种多层全印制电路板,包括:

至少一个含有导体图形的基片;其中,该多层全印制电路板的上表面和下表面都含有凹槽,在部分或全部的凹槽处含有通孔,任意两个相邻的含有导体图形的基片相接处的表面含有凹槽;凹槽和所述通孔中填充有导电油墨。

本发明实施例提供了一种全印制电路板的基片,包括:

在绝缘性基材的上表面和/或下表面至少含有一个凹槽,并在部分或全部凹槽处含有通孔;在凹槽和通孔处填充有导电油墨。

本发明实施例提供了一种单层全印制电路板,包括:

一个绝缘性基材,在该绝缘性基材上含有至少一个凹槽,在凹槽内填充有导电油墨。

本发明实施例通过采用将所需数量的含有导体图形的基片进行叠板和压合处理,形成多层全印制电路板的方案,避免了全印制电子技术印制电路板形成导电线路和图形精度不高,且全印制电子技术印制电路板对导电油墨要求较高的问题,提高了多层全印制电路板的导电线路和图形精度,降低了对导电油墨的要求。

附图说明

图1为本发明实施例中一种全印制电路板的基片的制造方法的流程示意图;

图2A为本发明实施例中单面含有导体图形的基片的制造方法的流程示意图;

图2B为本发明实施例中单面含有导体图形的基片的制造方法的过程示意图

图3A为本发明实施例中双面含有导体图形的基片的制造方法的流程示意图;

图3B为本发明实施例中双面含有导体图形的基片的制造方法的过程示意图

图4为本发明实施例中印刷导电油墨的具体过程示意图;

图5为本发明实施例中采用层压法制造多层全印制电路板方法的流程示意图;

图6A为本发明实施例中第一种层压法制造4层全印制电路板的过程示意图;

图6B为本发明实施例中第二种层压法制造4层全印制电路板的过程示意图;

图6C为本发明实施例中第三种层压法制造4层全印制电路板的过程示意图;

图6D为本发明实施例中第四种层压法制造4层全印制电路板的过程示意图;

图7为本发明实施例中采用积层法制造多层全印制电路板方法的流程示意图;

图8A为本发明实施例中采用积层法制造4层全印制电路板方法的流程示意图;

图8B为本发明实施例中采用积层法制造4层全印制电路板方法的过程示意图;

图9A为本发明实施例中一种单层全印制电路板的制作方法的流程示意图;

图9B为本发明实施例中一种单层全印制电路板的制作方法的过程示意图;

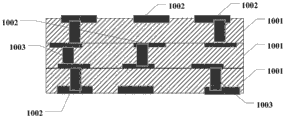

图10为本发明实施例中4层全印制电路板的结构示意图;

图11为本发明实施例中一种全印制电路板的基片的结构示意图;

图12为本发明实施例中一种全印制电路板的结构示意图;

图13为本发明实施例中单层全印制电路板的结构示意图。

具体实施方式

本发明实施例采用将至少两个含有导体图形的基片进行叠板和压合处理,形成多层全印制电路板的方法;或按照含有导体图形的基片、绝缘性基材和保护膜的顺序进行叠板和压合处理,在绝缘性基材的表面制作至少一个凹槽,并在部分或全部凹槽处制作盲孔,在凹槽和所述盲孔处填充导电油墨,去除绝缘性基材表面预贴合的保护膜,形成多层全印制电路板的方法制作多层全印制电路板;避免了全印制电子技术印制电路板形成导电线路和图形精度不高,且全印制电子技术印制电路板对导电油墨要求较高的问题,提高了多层全印制电路板的导电线路和图形精度,降低了对导电油墨的要求。

下面结合说明书附图对本发明实施例作进一步详细描述。

如图1所示,为本发明实施例一种全印制电路板的基片的制造方法,包括下列步骤:

步骤101:在绝缘性基材的上表面和下表面预贴合保护膜;

步骤102:在绝缘性基材的上表面和/或下表面制作至少一个凹槽,并在部分或全部凹槽处制作通孔;

步骤103:在凹槽和通孔处填充导电油墨;

步骤104:去除绝缘性基材表面预贴合保护膜,形成含有导体图形的基片。

其中,步骤101中绝缘性基材与保护膜的预贴合温度要低于绝缘性基材中树脂的玻璃化转化温度,进而避免在预贴合过程中绝缘性基材的树脂发生固化,失去粘结性,影响预贴合效果。

保护膜包括但不限于聚酯膜或者聚酰亚胺膜;且由于导电油墨具有一定的流动性,若保护膜的厚度过厚,在去除保护膜后,保护膜处形成凹槽的导电油墨可能会发生流动,造成形成的导体图形不精确的问题,因此,较佳地保护膜的厚度要小于25μm。

步骤102中,如图2B中223所示,根据需要可以在绝缘性基材的上表面或下表面制作至少一个凹槽,并在部分或全部凹槽处制作通孔;如图3B中323所示,也可以在绝缘性基材的上表面制作至少一个凹槽,在绝缘性基材的上表面部分或全部凹槽对应的下表面的相应位置制作凹槽。

步骤103中,在凹槽和通孔处填充导电油墨的方式可以采用印刷的方式,其中,印刷导电油墨的方式根据需要,可选择手动印刷,半自动印刷,全自动印刷或真空印刷的方式,也可以根据需要,将几种印刷方式搭配使用。

其中,导电油墨的种类包括但不限于下列种类:

导电铜油墨,导电银油墨,导电碳油墨。

采用图1所述方法制造形成的含有导体图形的基片共有两种,下面分别进行介绍。

第一种含有导体图形的基片

第一种含有导体图形的基片是在绝缘性基材的上表面或下表面制作至少一个凹槽,并在部分或全部凹槽处制作通孔,形成单面含有导体图形的基片。

如图2A所示,为单面含有导体图形的基片的制作方法,包括:

步骤201:在绝缘性基材21的上表面和下表面预贴合保护膜22,步骤201的过程图具体可以参见图2B的221;

步骤202:在预贴合保护膜22的绝缘性基材21表面进行加工,制作凹槽23,步骤202的过程图具体可以参见图2B的222;

步骤203:在制作出的凹槽23的位置,进行钻孔处理,制作出通孔24,步骤203的过程图具体可以参见图2B的223;

步骤204:对制作出的凹槽23和通孔24填充导电油墨,步骤204的过程图具体可以参见图2B的224;

步骤205:去除绝缘性基材表面预贴合的保护膜,步骤205的过程图具体可以参见图2B的225。

其中,绝缘性基材21可以是半固化片;其中,半固化片包括但不限于下列高分子聚合物:

环氧树脂玻纤布基板,芳香族聚酰胺树脂纤维的织布,环氧树脂无纺布基板,聚酰亚胺树脂基板,聚四氟乙烯树脂基板,聚苯醚树脂基板,聚苯醚树脂基板,氰酸酯树脂基板,双马来酰亚胺改性三嗪树脂基板。

较佳地,步骤201中,绝缘性基材21与保护膜22的预贴合温度要低于绝缘性基材中树脂的玻璃化转化温度,进而避免在预贴合过程中绝缘性基材的树脂发生固化,失去粘结性,影响预贴合效果。

对绝缘性基材21进行预贴合保护膜22的处理,是为了避免印刷导电油墨时,油墨对绝缘性基材21表面造成污染,导致形成的导体图形不精确,或造成短路等问题。

其中,保护膜包括但不限于聚酯膜或者聚酰亚胺膜;且由于导电油墨具有一定的流动性,若保护膜的厚度过厚,在去除保护膜后,保护膜处形成凹槽的导电油墨可能会发生流动,造成形成的导体图形不精确的问题,因此保护膜的厚度要小于25μm。

步骤202中,可以采用机械加工或激光加工的方法,在绝缘性基材表面进行加工制作凹槽23,为避免形成的电路板上的导线脱落的问题,增加导体图形对导线的固定能力,在绝缘性基材上加工的凹槽的深度应不小于5μm;较佳地,为了使凹槽的加工深度较为精确,可选择激光加工凹槽的方法。

其中,激光加工凹槽的方法包括但不限于:红外激光控深切割的方法和紫外激光控深切割的方法。

步骤203中,制作通孔24可以采用激光钻孔的方法或采用机械钻孔的方法,当所钻通孔的直径不小于0.1mm时,采用机械钻孔或激光钻孔的方法均可,当所钻通孔的直径小于0.1mm时,为了保证所钻通孔的尺寸精度,优选的采用激光钻孔的方法钻取所需通孔。

步骤204中,对制作出的凹槽23和通孔24填充导电油墨的方式可采用印刷的方式,其中印刷方式包括但不限于下列印刷方式:手动印刷,半自动印刷,全自动印刷或真空印刷的方式。根据印刷电路板的需要,可以选择其中一种印刷方式,也可此选择几种印刷方式混合使用。

其中,导电油墨的种类包括但不限于下列种类:

导电铜油墨,导电银油墨,导电碳油墨。

第二种含有导体图形的基片

第二种含有导体图形的基片是在绝缘性基材的上表面制作至少一个凹槽,并在部分或全部上表面凹槽对应的下表面的相应位置制作凹槽,在部分或全部凹槽处制作通孔,形成双面含有导体图形的基片。

如图3B的325所示,双面含有导体图形的基片上可以含有下列部分或全部种类的导通孔:第一种,在绝缘性基材的上表面制作凹槽,并在下表面相同位置制作凹槽,在上表面凹槽和下表面凹槽之间制作通孔;第二种,在绝缘性基材的上表面凹槽,在绝缘性基材的下表面的相应位置制作凹槽,在上表面凹槽和下表面凹槽之间制作通孔,使上表面的凹槽,上表面凹槽对应的下表面凹槽,以及对应的通孔形成通路。

双面含有导体图形的基片上也可以含有单面导通孔,即在绝缘性基材的上表面或下表面制作一个凹槽,在凹槽处制作通孔,形成单面导通孔。

如图3A所示,为双面含有导体图形的基片的制作方法,包括:

步骤301:在绝缘性基材31的上表面和下表面预贴合保护膜32,步骤301的过程图具体可以参见图3B的321;

步骤302:在预贴合保护膜32的绝缘性基材上表面和下表面的相应位置制作凹槽33,步骤302的过程图具体可以参见图3B的322;

步骤303:在部分制作出的凹槽33的位置,进行钻孔处理,制作出通孔34,步骤303的过程图具体可以参见图3B的323;

步骤304:对制作出的凹槽33和通孔34填充导电油墨,步骤304的过程图具体可以参见图3B的324;

步骤305:去除绝缘性基材表面预贴合的保护膜,步骤305的过程图具体可以参见图3B的325。

其中,绝缘性基材31与方式一中的绝缘性基材21可以使同一种绝缘性基材,也可以是不同种的绝缘性基材;绝缘性基材31可以是半固化片;其中,半固化片包括但不限于下列高分子聚合物:

环氧树脂玻纤布基板,芳香族聚酰胺树脂纤维的织布,环氧树脂无纺布基板,聚酰亚胺树脂基板,聚四氟乙烯树脂基板,聚苯醚树脂基板,聚苯醚树脂基板,氰酸酯树脂基板,双马来酰亚胺改性三嗪树脂基板。

较佳地,步骤301中,保护膜32与方式一中的保护膜22可以为同种保护膜,也可以为不同种的保护膜;且绝缘性基材31与保护膜32的预贴合温度要低于绝缘性基材中树脂的玻璃化转化温度,进而避免在预贴合过程中绝缘性基材的树脂发生固化,失去粘结性,影响预贴合效果。

对绝缘性基材31进行预贴合保护膜32的处理,是为了避免印刷导电油墨时,油墨对绝缘性基材31表面造成污染,导致形成的导体图形不精确,或造成短路等问题。

其中,保护膜包括但不限于聚酯膜或者聚酰亚胺膜;且由于导电油墨具有一定的流动性,若保护膜的厚度过厚,在去除保护膜后,保护膜处形成凹槽的导电油墨可能会发生流动,造成形成的导体图形不精确的问题,因此保护膜的厚度要小于25μm。

步骤302中,如图3B中323所示,在预贴合保护膜32的绝缘性基材上表面和下表面分别制作所需数量的凹槽33,其中,凹槽33可以采用机械加工或激光加工的方法,在绝缘性基材表面进行加工制作凹槽33,为避免形成的电路板上的导线脱落的问题,增加导体图形对导线的固定能力,在绝缘性基材上加工的凹槽的深度应不小于5μm;较佳地,为了使凹槽的加工深度较为精确,可选择激光加工凹槽的方法。

其中,激光加工凹槽的方法包括但不限于:红外激光控深切割的方法和紫外激光控深切割的方法。

步骤303中,制作通孔34可以采用激光钻孔的方法或采用机械钻孔的方法,当所钻通孔的直径不小于0.1mm时,采用机械钻孔或激光钻孔的方法均可,当所钻通孔的直径小于0.1mm时,为了保证所钻通孔的尺寸精度,优选的采用激光钻孔的方法钻取所需通孔。

步骤304中,对制作出的凹槽33和通孔34填充导电油墨的方式可采用印刷的方式,其中印刷方式包括但不限于下列印刷方式:手动印刷,半自动印刷,全自动印刷或真空印刷的方式。根据印刷电路板的需要,可以选择其中一种印刷方式,也可此选择几种印刷方式混合使用。

其中,导电油墨的种类包括但不限于下列种类:

导电铜油墨,导电银油墨,导电碳油墨。

如图4所示,为以单面含有导电图形的基片为例,印刷导电油墨的具体过程。

在制作完成的凹槽和通孔旁的基材表面堆积一定体积的导电油墨,通过刮刀将导电油墨刮到凹槽和通孔中,则完成一个凹槽和通孔的导电油墨的填充,刮刀移动至下一凹槽旁。

其中,导电油墨堆积的基材表面预贴合了保护膜,避免了导电油墨会对绝缘性基材表面造成污染,或导致导体图形不精确的问题;且导电油墨的体积略大于凹槽和通孔的体积之和,以保证导电油墨能将凹槽和通孔填充满。

其中,刮刀可以使用橡胶刮刀或不锈钢刮刀。

本发明实施例中利用全印制电路板的基片制造多层全印制电路板共有两种方法,一种为层压法制造多层全印制电路板,另一种为积层法制造多层全印制电路板,下面对两种制造多层全印制电路板的方法分别进行介绍。

一、层压法制造多层全印制电路板

如图5所示,为本发明实施例采用层压法制造多层全印制电路板方法,包括下列步骤:

步骤501:将至少两个含有导体图形的基片进行叠板处理;

步骤502:将叠板处理后的含有导体图形的基片进行压合处理,形成多层全印制电路板。

其中,形成的多层全印制电路板的上表面和下表面都含有凹槽,且任意相邻两个含有导体图形的基片相接处的表面含有凹槽,且每个含有导体图形的基片通孔进行叠板和压合处理后形成多层全印制电路板的叠合导通孔,形成的多层全印制电路板的叠合导通孔如图10所示。

步骤501中,进行叠板处理的含有导体图形的基片至少含有一个双面含有导电图形的基片,多层全印制电路板的制造方式可以有多种,下面以4层全印制电路板的制作方式为例,分别对几种层压法制造多层全印制电路板的制造方式进行介绍。

方式一

如图6A所示,为第一种层压法制造4层全印制电路板的制造方式。将两个单面含有导体图形的基片和一个双面含有导体图形的基片进行叠板处理,其叠板顺序为单面含有导体图形的基片、双面含有导体图形的基片和单面含有导体图形的基片;其中两个单面含有导体图形的基片中不含有凹槽的表面与双面含有导体图形的基片的表面接触;将叠板处理后的基片进行压合处理,形成4层全印制电路板。

方式二

如图6B所示,为第二种层压法制造4层全印制电路板的制造方式。将两个单面含有导体图形的基片和一个双面含有导体图形的基片进行叠板处理,其叠板顺序为单面含有导体图形的基片、单面含有导体图形的基片和双面含有导体图形的基片;其中,与双面含有导体图形的基片相邻的单面含有导体图形的基片的不含凹槽的表面与双面含有导体图形的基片的表面接触,另一单面含有导体图形的基片不含凹槽的表面与相邻的单面含有导体图形的基片的含有凹槽的表面接触;将叠板处理后的基片进行压合处理,形成4层全印制电路板。

方式三

如图6C所示,为第三种层压法制造4层全印制电路板的制造方式。将三个双面含有导体图形的基片进行叠板和压合处理,形成4层全印制电路板。

方式四

如图6D所示,为第四种层压法制造4层全印制电路板的制造方式,将只含有凹槽的基片,与两个双面含有导体图形的基片进行叠板和压合处理,其叠板顺序为双面含有导体图形的基片、只含有凹槽的基片、双面含有导体图形的基片,形成4层全印制电路板。

二、积层法制造多层全印制电路板

如图7所示,为本发明实施例采用积层法制造多层全印制电路板方法,包括下列步骤:

步骤701:按照含有导体图形的基片、绝缘性基材和保护膜的顺序进行叠板;

步骤702:将叠板处理后的含有导体图形的基片、绝缘性基材和保护膜进行压合处理;

步骤703:在绝缘性基材的表面制作至少一个凹槽;

步骤704:在部分或全部凹槽处制作盲孔,其中绝缘性基材上的凹槽和盲孔的位置与进行叠板和压合处理的含有导体图形的基片上的凹槽和通孔形成通路;

步骤705:在凹槽和所述盲孔处填充导电油墨;

步骤706:去除绝缘性基材表面预贴合的保护膜,形成多层全印制电路板。

步骤701中的绝缘性基材可以是半固化片;其中,半固化片包括但不限于下列高分子聚合物:

环氧树脂玻纤布基板,芳香族聚酰胺树脂纤维的织布,环氧树脂无纺布基板,聚酰亚胺树脂基板,聚四氟乙烯树脂基板,聚苯醚树脂基板,聚苯醚树脂基板,氰酸酯树脂基板,双马来酰亚胺改性三嗪树脂基板。

较佳地,步骤702中,对,双面含有导体图形的基片,绝缘性基材和保护膜进行压合时,压合温度要低于绝缘性基材中树脂的玻璃化转化温度,进而避免在预贴合过程中绝缘性基材的树脂发生固化,失去粘结性,影响预贴合效果。

在绝缘性基材表面压合保护膜,是为了避免印刷导电油墨时,油墨对绝缘性基材表面造成污染,导致形成的导体图形不精确,或造成短路等问题。

其中,保护膜包括但不限于聚酯膜或者聚酰亚胺膜;且由于导电油墨具有一定的流动性,若保护膜的厚度过厚,在去除保护膜后,保护膜处形成凹槽的导电油墨可能会发生流动,造成形成的导体图形不精确的问题,因此保护膜的厚度要小于25μm

步骤703中,在绝缘性基材表面制作凹槽时,为避免形成的电路板上的导线脱落的问题,增加导体图形对导线的固定能力,凹槽的深度应不小于5μm;其中,凹槽的加工方法可选择机械加工或激光加工的方法,为了使凹槽的加工深度较为精确,优选的选择激光加工凹槽的方法。

其中,激光加工凹槽的方法包括但不限于:红外激光控深切割的方法和紫外激光控深切割的方法。

步骤704中,盲孔的制作可采用激光钻孔的方法或采用机械钻孔的方法,当所钻通孔的直径不小于0.1mm时,采用机械钻孔或激光钻孔的方法均可,当所钻通孔的直径小于0.1mm时,为了保证所钻通孔的尺寸精度,优选的采用激光钻孔的方法钻取所需通孔。

其中,步骤704中盲孔的深度与绝缘性基材去除凹槽后的厚度相同;即使绝缘性基材上制作的凹槽和盲孔与双面含有导体图形的基片的凹槽和通孔形成通路。

步骤705中,对制作出的凹槽和盲孔填充导电油墨的方式可采用印刷的方式,其中印刷方式包括但不限于下列印刷方式:手动印刷,半自动印刷,全自动印刷或真空印刷的方式。根据印刷电路板的需要,可以选择其中一种印刷方式,也可此选择几种印刷方式混合使用。

其中,导电油墨的种类包括但不限于下列种类:

导电铜油墨,导电银油墨,导电碳油墨。

较佳地,步骤701中,含有导体图形的基片是双面含有导体图形的基片,且双面含有导体图形的基片中与绝缘性基材接触的表面是上表面和/或下表面。即双面含有导体图形的基片的上表面和下表面分别与一个绝缘性基材接触,进行叠板处理;或双面含有导体图形的基片的上表面或下表面与一个绝缘性基材接触,进行叠板处理。

如图8A所示,以双面含有导体图形的基片的上表面和下表面分别与一个绝缘性基材接触,进行叠板处理,制作4层全印制电路板为例,对积层法制造多层全印制电路板的方法进行进一步阐述。

步骤801:将一个双面含有导体图形的基片81,两个绝缘性基材82,两个保护膜83,进行叠板处理,叠板的顺序为:保护膜83,绝缘性基材82,双面含有导体图形的基片81,绝缘性基材82和保护膜83;步骤801的过程图具体可以参见图8B的821;

步骤802:将叠板处理后的双面含有导体图形的基片81,绝缘性基材82和保护膜83,进行压合处理,步骤802的过程图具体可以参见图8B的822;

步骤803:在两个压合了保护膜83的绝缘性基材82的表面制作凹槽84,步骤803的过程图具体可以参见图8B的823;

步骤804:在绝缘性基材82的表面的凹槽84的位置制作盲孔85,其中,绝缘性基材82上的盲孔85与双面含有导体图形的基片81的通孔形成通路,步骤804的过程图具体可以参见图8B的824;

步骤805:对制作出的凹槽凹槽84和盲孔85填充导电油墨,步骤805的过程图具体可以参见图8B的825;

步骤806:去除绝缘性基材82表面预贴合的保护膜83,步骤806的过程图具体可以参见图8B的826。

如图9A所示,为本发明实施例提供的一种单层全印制电路板的制作方法,包括下列步骤:

步骤901:在绝缘性基材91的需要制作凹槽的表面预贴合保护膜92,步骤901的过程图具体可以参见图9B的921;

步骤902:在预贴合保护膜92的绝缘性基材91的表面制作至少一个凹槽93,步骤902的过程图具体可以参见图9B的922;

步骤903:在凹槽93处填充导电油墨,步骤903的过程图具体可以参见图9B的923;

步骤904:去除绝缘性基材91表面预贴合保护膜92,形成单层全印制电路板。

其中,绝缘性基材91可以是半固化片;其中,半固化片包括但不限于下列高分子聚合物:

环氧树脂玻纤布基板,芳香族聚酰胺树脂纤维的织布,环氧树脂无纺布基板,聚酰亚胺树脂基板,聚四氟乙烯树脂基板,聚苯醚树脂基板,聚苯醚树脂基板,氰酸酯树脂基板,双马来酰亚胺改性三嗪树脂基板。

较佳地,步骤901中,绝缘性基材91与保护膜92的预贴合温度要低于绝缘性基材中树脂的玻璃化转化温度,进而避免在预贴合过程中绝缘性基材的树脂发生固化,失去粘结性,影响预贴合效果。

对绝缘性基材91进行预贴合保护膜92的处理,是为了避免印刷导电油墨时,油墨对绝缘性基材91表面造成污染,导致形成的导体图形不精确,或造成短路等问题。

其中,保护膜包括但不限于聚酯膜或者聚酰亚胺膜;且由于导电油墨具有一定的流动性,若保护膜的厚度过厚,在去除保护膜后,保护膜处形成凹槽的导电油墨可能会发生流动,造成形成的导体图形不精确的问题,因此保护膜的厚度要小于25μm。

步骤902中,可以采用机械加工或激光加工的方法,在绝缘性基材表面进行加工制作凹槽93,为避免形成的电路板上的导线脱落的问题,增加导体图形对导线的固定能力,在绝缘性基材上加工的凹槽的深度应不小于5μm;较佳地,为了使凹槽的加工深度较为精确,可选择激光加工凹槽的方法。

其中,激光加工凹槽的方法包括但不限于:红外激光控深切割的方法和紫外激光控深切割的方法。

步骤903中,对制作出的凹槽93填充导电油墨的方式可采用印刷的方式,其中印刷方式包括但不限于下列印刷方式:手动印刷,半自动印刷,全自动印刷或真空印刷的方式。根据印刷电路板的需要,可以选择其中一种印刷方式,也可此选择几种印刷方式混合使用。

其中,导电油墨的种类包括但不限于下列种类:

导电铜油墨,导电银油墨,导电碳油墨。

本发明实施例中多层全印制电路板是由若干含有导体图形的基片通过层压法获得,或由含有导体图形的基片与绝缘性基材通过积层法获得,以4层全印制电路板为例,结合图10所示,对4层全印制电路板的结构阐述如下。

该4层全印制电路板由三个绝缘性基材构成,每个绝缘性基材1001的上表面和/或下表面含有若干个凹槽1002,部分凹槽上含有通孔1003,凹槽1002和通孔1003中填充有导电油墨。

如图11所示,为本发明实施例中一种全印制电路板的基片的结构。

该全印制电路板的基片包括一个绝缘性基材1101,在该绝缘性基材1101上的上表面和/或下表面含有至少一个凹槽1102,在部分或全部凹槽1102处含有通孔1103,在凹槽1102和通孔1103内填充有导电油墨。

如图12所示,为本发明实施例中一种多层全印制电路板的结构。

该多层全印制电路板包括若干个全印制电路板的基片1201,在绝缘性基材1201的上表面和/或下表面含有至少一个凹槽1102,在部分或全部凹槽1102处含有通孔1103,在凹槽1102和通孔1103内填充有导电油墨。

如图13所示,为本发明实施例中一种单层全印制电路板的结构。

该单层全印制电路板包括一个绝缘性基材1301,在该绝缘性基材1301上含有至少一个凹槽1302,在凹槽1302内填充有导电油墨。

显然,本领域的技术人员可以对本发明进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包含这些改动和变型在内。

Claims (12)

1.一种全印制电路板的基片的制造方法,其特征在于,该方法包括:

在绝缘性基材的上表面和下表面预贴合保护膜;

在绝缘性基材的上表面和/或下表面制作至少一个凹槽,并在部分或全部凹槽处制作通孔;

在所述凹槽和所述通孔处填充导电油墨;

去除绝缘性基材表面预贴合保护膜,形成含有导体图形的基片。

2.如权利要求1所述的方法,其特征在于,在绝缘性基材的上表面和下表面制作至少一个凹槽,并在部分或全部凹槽处制作通孔,包括:

在绝缘性基材的上表面制作的一个凹槽,和在该凹槽对应的下表面制作的一个凹槽,以及在该上表面凹槽上制作的通孔共同形成该绝缘性基材的一个电连接通路。

3.一种利用权利要求2制作的基片制造全印制电路板的方法,其特征在于,该方法还包括:

将形成的至少两个所述含有导体图形的基片进行叠板和压合处理,形成多层全印制电路板;

其中,所述多层全印制电路板的上表面和下表面都含有凹槽,且任意相邻两个所述含有导体图形的基片相接处的表面含有凹槽,且每个所述含有导体图形的基片通孔进行叠板和压合处理后形成多层全印制电路板的叠合导通孔。

4.一种利用权利要求1或2制作的基片制造全印制电路板的方法,其特征在于,该方法包括:

按照含有导体图形的基片、绝缘性基材和保护膜的顺序进行叠板和压合处理,其中所述含有导体图形的基片是上、下表面都含有凹槽的导体图形的基片,且含有导体图形的基片中与绝缘性基材接触的表面是上表面和/或下表面;

在绝缘性基材的表面制作至少一个凹槽,并在部分或全部凹槽处制作盲孔;

在所述凹槽和所述盲孔处填充导电油墨,去除绝缘性基材表面预贴合的保护膜,形成多层全印制电路板。

5.如权利要求4所述的方法,其特征在于,形成多层全印制电路板之后,还包括:

判断多层全印制电路板的层数是否满足设定层数,若是,则停止操作,否则,按照多层全印制电路板、绝缘性基材和保护膜的顺序进行叠板和压合处理,并返回判断多层全印制电路板的层数是否满足设定层数的步骤。

6.一种全印制电路板的制造方法,其特征在于,该方法包括:

在绝缘性基材上需要制作凹槽的表面预贴合保护膜,并在预贴合保护膜的表面制作至少一个凹槽;

在所述凹槽处填充导电油墨;

去除绝缘性基材表面预贴合保护膜,形成单层全印制电路板。

7.一种多层全印制电路板,其特征在于,该电路板包括:

至少两个含有导体图形的基片;

其中,该多层全印制电路板的上表面和下表面都含有凹槽,在部分或全部的凹槽处含有通孔,任意两个相邻的含有导体图形的基片相接处的表面含有凹槽;所述凹槽和所述通孔中填充有导电油墨。

8.如权利要求7所述的电路板,其特征在于,所述含有导体图形的基片还包括:

在所述含有导体图形的基片的上表面和/或下表面上含有至少一个凹槽,且部分或全部凹槽的位置上含有通孔,凹槽和通孔内填充有导电油墨。

9.如权利要求8所述的电路板,其特征在于,在所述含有导体图形的基片的上表面和/或下表面上含有至少一个凹槽,包括:

绝缘性基材的上表面含有的一个凹槽,和该凹槽对应的下表面的一个凹槽,以及在该上表面凹槽上含有的通孔共同形成该绝缘性基材的一个电连接通路。

10.一种全印制电路板的基片,其特征在于,该基片包括:

在绝缘性基材的上表面和/或下表面至少含有一个凹槽,并在部分或全部凹槽处含有通孔;

在所述凹槽和所述通孔处填充有导电油墨。

11.一种全印制电路板,其特征在于,包含如权利要求10所述的基片。

12.一种单层全印制电路板,其特征在于,该电路板包括:

一个绝缘性基材,在该绝缘性基材上含有至少一个凹槽,在凹槽内填充有导电油墨。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201210450725.1A CN103813640A (zh) | 2012-11-12 | 2012-11-12 | 一种全印制电路板及其制造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201210450725.1A CN103813640A (zh) | 2012-11-12 | 2012-11-12 | 一种全印制电路板及其制造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN103813640A true CN103813640A (zh) | 2014-05-21 |

Family

ID=50709668

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201210450725.1A Pending CN103813640A (zh) | 2012-11-12 | 2012-11-12 | 一种全印制电路板及其制造方法 |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN103813640A (zh) |

Cited By (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104093279A (zh) * | 2014-07-16 | 2014-10-08 | 电子科技大学 | 一种基于激光凹槽加工工艺的印制电路板制作方法 |

| CN107087355A (zh) * | 2017-06-16 | 2017-08-22 | 东莞职业技术学院 | 一种采用丝网印刷技术实现pcb内层互联的方法 |

| CN110324991A (zh) * | 2019-07-10 | 2019-10-11 | 广东工业大学 | 一种复合电路板的制备方法 |

| CN110536551A (zh) * | 2019-07-10 | 2019-12-03 | 广东工业大学 | 一种电路板的制备方法 |

| CN112533386A (zh) * | 2020-12-24 | 2021-03-19 | 深圳市百柔新材料技术有限公司 | 一种导电电路板的制作方法 |

| WO2022006789A1 (zh) * | 2020-07-08 | 2022-01-13 | 广东工业大学 | 一种复合电路板的制备方法 |

| CN114007346A (zh) * | 2021-10-26 | 2022-02-01 | 武汉天喻信息产业股份有限公司 | 一种多层电路板制作方法及多层电路板 |

| CN114126224A (zh) * | 2020-08-28 | 2022-03-01 | 深南电路股份有限公司 | 一种线路板及其线路板的制造方法 |

| US11348831B2 (en) | 2019-07-04 | 2022-05-31 | Universal Global Technology (Shanghai) Co., Ltd | Method of manufacturing a semiconductor unit |

| TWI803185B (zh) * | 2022-02-10 | 2023-05-21 | 福懋科技股份有限公司 | 印刷裝置 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000232267A (ja) * | 1999-02-12 | 2000-08-22 | Matsushita Electric Ind Co Ltd | 多層プリント配線板の製造方法 |

| CN101466205A (zh) * | 2007-12-19 | 2009-06-24 | 富葵精密组件(深圳)有限公司 | 电路板及电路板的制作方法 |

| CN101610635A (zh) * | 2008-06-20 | 2009-12-23 | 欣兴电子股份有限公司 | 线路板结构及其工艺 |

| CN102595809A (zh) * | 2012-03-14 | 2012-07-18 | 柏承科技(昆山)股份有限公司 | 高密度互联印刷电路板的制作方法 |

-

2012

- 2012-11-12 CN CN201210450725.1A patent/CN103813640A/zh active Pending

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000232267A (ja) * | 1999-02-12 | 2000-08-22 | Matsushita Electric Ind Co Ltd | 多層プリント配線板の製造方法 |

| CN101466205A (zh) * | 2007-12-19 | 2009-06-24 | 富葵精密组件(深圳)有限公司 | 电路板及电路板的制作方法 |

| CN101610635A (zh) * | 2008-06-20 | 2009-12-23 | 欣兴电子股份有限公司 | 线路板结构及其工艺 |

| CN102595809A (zh) * | 2012-03-14 | 2012-07-18 | 柏承科技(昆山)股份有限公司 | 高密度互联印刷电路板的制作方法 |

Cited By (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104093279A (zh) * | 2014-07-16 | 2014-10-08 | 电子科技大学 | 一种基于激光凹槽加工工艺的印制电路板制作方法 |

| CN107087355A (zh) * | 2017-06-16 | 2017-08-22 | 东莞职业技术学院 | 一种采用丝网印刷技术实现pcb内层互联的方法 |

| US11348831B2 (en) | 2019-07-04 | 2022-05-31 | Universal Global Technology (Shanghai) Co., Ltd | Method of manufacturing a semiconductor unit |

| CN110324991A (zh) * | 2019-07-10 | 2019-10-11 | 广东工业大学 | 一种复合电路板的制备方法 |

| CN110536551A (zh) * | 2019-07-10 | 2019-12-03 | 广东工业大学 | 一种电路板的制备方法 |

| WO2022006789A1 (zh) * | 2020-07-08 | 2022-01-13 | 广东工业大学 | 一种复合电路板的制备方法 |

| CN114126224A (zh) * | 2020-08-28 | 2022-03-01 | 深南电路股份有限公司 | 一种线路板及其线路板的制造方法 |

| CN112533386A (zh) * | 2020-12-24 | 2021-03-19 | 深圳市百柔新材料技术有限公司 | 一种导电电路板的制作方法 |

| CN114007346A (zh) * | 2021-10-26 | 2022-02-01 | 武汉天喻信息产业股份有限公司 | 一种多层电路板制作方法及多层电路板 |

| TWI803185B (zh) * | 2022-02-10 | 2023-05-21 | 福懋科技股份有限公司 | 印刷裝置 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN103813640A (zh) | 一种全印制电路板及其制造方法 | |

| CN104125724B (zh) | 一种pcb金属半孔产品的生产工艺 | |

| CN102045949A (zh) | 刚挠结合印制电路板的制作方法 | |

| CN102480852B (zh) | 电路板的制作方法 | |

| US20110302775A1 (en) | Method for manufacturing printed circuit board | |

| CN103906364B (zh) | 一种印制电路板中隐埋电阻的加工方法 | |

| CN104125727A (zh) | 一种多层软板的软硬结合印刷线路板的制作方法 | |

| CN101120623A (zh) | 多层电路基板的制造方法和多层电路基板 | |

| CN103108491A (zh) | 电路板及其制作方法 | |

| CN104349574A (zh) | 电路板及其制作方法 | |

| CN105188278A (zh) | 树脂塞孔压合板结构及树脂塞孔工艺 | |

| CN104519680A (zh) | 用于构造电路板的生态学方法 | |

| CN103108485A (zh) | 多层印刷电路板及其制作方法 | |

| CN204046961U (zh) | 一种电路板黄色阻焊油墨塞孔装置 | |

| CN104717840A (zh) | 电路板制作方法和电路板 | |

| CN102227959B (zh) | 配线板及其制造方法 | |

| CN103841771A (zh) | 组合印制电路板和印制电路板的制造方法以及印制电路板 | |

| CN104735899B (zh) | 可挠式电路板及其制作方法 | |

| CN106061140A (zh) | 一种高阶任意层hdi板制作工艺 | |

| CN103857176A (zh) | 电路板及其制作方法 | |

| CN103906376A (zh) | 可挠折的电路板及其制作方法 | |

| CN104159392A (zh) | 一种印制电路板及其制备方法 | |

| CN103144378B (zh) | 一种pn固化体系的覆铜板、pcb板及其制作方法 | |

| CN101951737A (zh) | 多层式电路板的制造方法 | |

| CN103582321A (zh) | 多层线路板及其制作方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| RJ01 | Rejection of invention patent application after publication | ||

| RJ01 | Rejection of invention patent application after publication |

Application publication date: 20140521 |