CN101436606A - 非易失性半导体存储器件 - Google Patents

非易失性半导体存储器件 Download PDFInfo

- Publication number

- CN101436606A CN101436606A CNA2008101740296A CN200810174029A CN101436606A CN 101436606 A CN101436606 A CN 101436606A CN A2008101740296 A CNA2008101740296 A CN A2008101740296A CN 200810174029 A CN200810174029 A CN 200810174029A CN 101436606 A CN101436606 A CN 101436606A

- Authority

- CN

- China

- Prior art keywords

- layer

- recording material

- volatile recording

- metal wiring

- mentioned

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 145

- 239000000463 material Substances 0.000 claims abstract description 155

- 238000003860 storage Methods 0.000 claims abstract description 23

- 230000007704 transition Effects 0.000 claims description 11

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 7

- 229910052710 silicon Inorganic materials 0.000 claims description 7

- 239000010703 silicon Substances 0.000 claims description 6

- 239000002131 composite material Substances 0.000 claims description 4

- 229910005542 GaSb Inorganic materials 0.000 claims description 2

- 229910052798 chalcogen Inorganic materials 0.000 claims description 2

- 150000001787 chalcogens Chemical class 0.000 claims description 2

- WPYVAWXEWQSOGY-UHFFFAOYSA-N indium antimonide Chemical group [Sb]#[In] WPYVAWXEWQSOGY-UHFFFAOYSA-N 0.000 claims description 2

- 230000008859 change Effects 0.000 abstract description 12

- 239000010410 layer Substances 0.000 description 358

- 229910052751 metal Inorganic materials 0.000 description 88

- 239000002184 metal Substances 0.000 description 87

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 70

- 229920005591 polysilicon Polymers 0.000 description 70

- 239000011159 matrix material Substances 0.000 description 48

- 229910021417 amorphous silicon Inorganic materials 0.000 description 24

- 238000004519 manufacturing process Methods 0.000 description 24

- 239000000758 substrate Substances 0.000 description 23

- 230000002093 peripheral effect Effects 0.000 description 18

- 238000000034 method Methods 0.000 description 14

- 238000009792 diffusion process Methods 0.000 description 11

- 230000006866 deterioration Effects 0.000 description 9

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 9

- 229910052721 tungsten Inorganic materials 0.000 description 9

- 239000010937 tungsten Substances 0.000 description 9

- 238000005224 laser annealing Methods 0.000 description 8

- 230000015572 biosynthetic process Effects 0.000 description 7

- 239000010949 copper Substances 0.000 description 7

- 238000002425 crystallisation Methods 0.000 description 7

- 230000008025 crystallization Effects 0.000 description 7

- 239000012535 impurity Substances 0.000 description 6

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 5

- 239000004411 aluminium Substances 0.000 description 5

- 229910052782 aluminium Inorganic materials 0.000 description 5

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 5

- 229910052802 copper Inorganic materials 0.000 description 5

- 238000010586 diagram Methods 0.000 description 5

- 239000007784 solid electrolyte Substances 0.000 description 5

- 229910008310 Si—Ge Inorganic materials 0.000 description 4

- 230000007812 deficiency Effects 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- 230000006870 function Effects 0.000 description 4

- 238000001459 lithography Methods 0.000 description 4

- 238000001259 photo etching Methods 0.000 description 4

- 230000000630 rising effect Effects 0.000 description 4

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 3

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 3

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 3

- 230000005540 biological transmission Effects 0.000 description 3

- 229910052796 boron Inorganic materials 0.000 description 3

- 150000001875 compounds Chemical class 0.000 description 3

- 238000005530 etching Methods 0.000 description 3

- 239000012467 final product Substances 0.000 description 3

- 229910052733 gallium Inorganic materials 0.000 description 3

- 229910052738 indium Inorganic materials 0.000 description 3

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 3

- 230000003287 optical effect Effects 0.000 description 3

- 239000011241 protective layer Substances 0.000 description 3

- 239000000126 substance Substances 0.000 description 3

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 2

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 2

- 238000001816 cooling Methods 0.000 description 2

- 238000005520 cutting process Methods 0.000 description 2

- 230000012447 hatching Effects 0.000 description 2

- 229910000765 intermetallic Inorganic materials 0.000 description 2

- 229910052698 phosphorus Inorganic materials 0.000 description 2

- 239000011574 phosphorus Substances 0.000 description 2

- 230000005855 radiation Effects 0.000 description 2

- 229910021332 silicide Inorganic materials 0.000 description 2

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 2

- 230000009466 transformation Effects 0.000 description 2

- 229910005866 GeSe Inorganic materials 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 230000005611 electricity Effects 0.000 description 1

- 230000003760 hair shine Effects 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 1

- 239000000696 magnetic material Substances 0.000 description 1

- 238000012423 maintenance Methods 0.000 description 1

- 238000003701 mechanical milling Methods 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 238000005457 optimization Methods 0.000 description 1

- 239000012782 phase change material Substances 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 239000000047 product Substances 0.000 description 1

- 238000004151 rapid thermal annealing Methods 0.000 description 1

- 238000002310 reflectometry Methods 0.000 description 1

- 229910052711 selenium Inorganic materials 0.000 description 1

- 229910052717 sulfur Inorganic materials 0.000 description 1

- 229910052714 tellurium Inorganic materials 0.000 description 1

- 150000003498 tellurium compounds Chemical class 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/20—Multistable switching devices, e.g. memristors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/10—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a repetitive configuration

- H01L27/101—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a repetitive configuration including resistors or capacitors only

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/02—Disposition of storage elements, e.g. in the form of a matrix array

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B63/00—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B63/00—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices

- H10B63/20—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices comprising selection components having two electrodes, e.g. diodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B63/00—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices

- H10B63/80—Arrangements comprising multiple bistable or multi-stable switching components of the same type on a plane parallel to the substrate, e.g. cross-point arrays

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/011—Manufacture or treatment of multistable switching devices

- H10N70/061—Shaping switching materials

- H10N70/063—Shaping switching materials by etching of pre-deposited switching material layers, e.g. lithography

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/20—Multistable switching devices, e.g. memristors

- H10N70/231—Multistable switching devices, e.g. memristors based on solid-state phase change, e.g. between amorphous and crystalline phases, Ovshinsky effect

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/20—Multistable switching devices, e.g. memristors

- H10N70/24—Multistable switching devices, e.g. memristors based on migration or redistribution of ionic species, e.g. anions, vacancies

- H10N70/245—Multistable switching devices, e.g. memristors based on migration or redistribution of ionic species, e.g. anions, vacancies the species being metal cations, e.g. programmable metallization cells

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/821—Device geometry

- H10N70/826—Device geometry adapted for essentially vertical current flow, e.g. sandwich or pillar type devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/881—Switching materials

- H10N70/882—Compounds of sulfur, selenium or tellurium, e.g. chalcogenides

- H10N70/8825—Selenides, e.g. GeSe

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/881—Switching materials

- H10N70/882—Compounds of sulfur, selenium or tellurium, e.g. chalcogenides

- H10N70/8828—Tellurides, e.g. GeSbTe

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0004—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements comprising amorphous/crystalline phase transition cells

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/71—Three dimensional array

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/72—Array wherein the access device being a diode

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Semiconductor Memories (AREA)

Abstract

本发明提供一种非易失性半导体存储器件。在相变存储器等中,存在如下问题:用薄膜形成记录材料和选择元件双方时,因重写工作等的热而使与记录材料层相邻的层的原子扩散到记录材料层,重写特性发生变化。为了解决上述问题,本发明在非易失性记录材料层(224)与选择元件(220、221)之间具有膜厚为5nm~200nm的半导体层(222)。由此,可得到大容量且重写条件稳定的非易失性存储器。

Description

技术领域

本发明涉及非易失性地存储由金属化合物的结晶状态和非结晶状态之间的相变来决定的电阻值的、可进行电重写的相变存储器装置。

背景技术

在非易失性存储器件中,有的存储器件将金属化合物的结晶状态和非结晶状态用作存储信息。作为该存储材料,通常使用碲化合物。利用它们反射率的差异来存储信息的原理广泛应用于如DVD(数字视盘)那样的光信息存储介质。

近年来,提出将该原理应用于电信息存储。该方法与光学方法不同,是用电流量或电压变化来检测非晶与结晶的电阻差、即非晶的高电阻状态与结晶的低电阻状态。应用于后者的电信息存储的存储器称为相变存储器,相变存储器的基本存储器单元的构造是将相变电阻元件和选择元件组合在一起的构造。相变存储器利用由对相变电阻元件施加电流而产生的焦耳热来使相变电阻元件的构成要素、即非易失性记录材料层为结晶状态或非结晶状态。相变存储器通过维持非易失性记录材料层的结晶状态或非结晶状态来存储保持信息。对于重写,在为电气的高电阻非结晶状态时,在施加大电流而使作为非易失性存储材料的电阻变化材料的温度为熔点以上之后,进行快速冷却即可,在为电气的低电阻非结晶状态时,限制施加的电流而使电阻变化材料的温度为低于熔点的结晶温度即可。通常非易失性记录材料层的电阻值会因为相变而发生2位数~3位数左右的变化。因此,相变存储器利用结晶或非晶而读出的信号有较大不同,易于进行读出工作。

专利文献1:US 2006/020354/A1

专利文献2:US 6,426,891B1

发明内容

在以往的相变存储器的重写中,从结晶状态相变到非结晶状态或从非结晶状态相变到结晶状态,因此非易失性记录材料层被加热到非常高的温度。因此,随着反复重写,存在构成与非易失性记录材料层接近的膜的原子从与非易失性记录材料层接近的膜扩散,重写条件发生变化的问题。

在现有技术、例如US 2006/020354/A1(专利文献1)所记载的技术中,在非易失性记录材料层与选择元件之间配置有电连接成为电阻的金属膜,但金属元素从金属膜向非易失性记录材料层扩散,重写条件发生变化,这成为一个问题。在US 6,426,891B1(专利文献2)中,在非易失性记录材料层与选择元件之间,为了防止在重写时发生的来自非易失性记录材料层的热扩散而配置导电性隔热膜,但存在难以进行非易失性记录材料层的非晶化所需的快速冷却这样的问题。本发明的目的在于提供一种相变存储器,其防止从与非易失性记录材料层相邻的层扩散原子、或即使发生了扩散也成为不影响重写条件的原子,进而还容易进行用于非晶化的快速冷却,从而保持稳定的重写条件。

例举本申请的代表性技术方案,本发明的非易失性半导体存储器件包括第一电极、第二电极、形成在第一电极和第二电极之间的非易失性记录材料层和选择元件、形成在非易失性记录材料层和选择元件之间的包括非易失性记录材料层所含元素的半导体层。以下,将形成在非易失性记录材料层和选择元件之间的包括非易失性记录材料层所含元素的半导体层简称为半导体层。

根据本发明,可得到重写条件稳定的相变存储器。例如实现可在重写时间为50ns以下进行109次以上重写的非易失性存储器。

附图说明

图1是本发明实施方式1的存储器单元的要部剖视图。

图2是本发明实施方式2的存储器单元的要部剖视图。

图3是本发明实施方式3的存储器单元的要部剖视图。

图4是本发明实施方式4的存储器单元的要部剖视图。

图5表示本发明实施方式1的半导体器件的制造工序中的概观图。

图6是表示硅基板、外围电路部及存储器矩阵部的位置关系的图。

图7是表示硅基板、外围电路部及存储器矩阵部的位置关系的图。

图8是表示硅基板、外围电路部及存储器矩阵部的位置关系的图。

图9是接着图5的半导体器件的制造工序中的概观图。

图10是接着图9的半导体器件的制造工序中的概观图。

图11是接着图10的半导体器件的制造工序中的概观图。

图12是接着图11的半导体器件的制造工序中的概观图。

图13是接着图12的半导体器件的制造工序中的概观图。

图14是接着图13的半导体器件的制造工序中的概观图。

图15是接着图14的半导体器件的制造工序中的概观图。

图16是接着图15的半导体器件的制造工序中的概观图。

图17是接着图16的半导体器件的制造工序中的概观图。

图18是接着图17的半导体器件的制造工序中的概观图。

图19是与图18所记载的构造对应的俯视图。

图20是表示本发明的半导体器件的存储器矩阵的要部电路图。

图21表示本发明实施方式1的半导体器件的制造工序中的概观图。

图22表示本发明实施方式2的半导体器件的制造工序中的概观图。

图23是接着图22的半导体器件的制造工序中的概观图。

图24是接着图23的半导体器件的制造工序中的概观图。

图25是接着图24的半导体器件的制造工序中的概观图。

图26是接着图25的半导体器件的制造工序中的概观图。

图27是接着图26的半导体器件的制造工序中的概观图。

图28是与Si-Ge的光学常数相关的图。

图29是接着图27的半导体器件的制造工序中的概观图。

图30是与图29所记载的构造对应的俯视图。

图31表示本发明实施方式4的半导体器件的制造工序中的概观图。

图32表示本发明实施方式5的半导体器件的制造工序中的概观图。

具体实施方式

使用图1~图4说明本发明的非易失性存储器的存储器单元。关于其构造,与非易失性记录材料层和选择元件位于不同的层、经塞柱(plug)而电连接的构造不同,是不经塞柱而在同一层将非易失性记录材料层和选择元件电连接的所谓柱形构造。另外,在此作为选择元件以pn多晶硅二极管为例加以说明。因此,在图1~图4中,虽然示出了形成pn结的第一多晶硅层和第二多晶硅层,但也可以是如np结、pin结那样的其他结的构造。或者,可以在存储器单元使用采用了金属布线层与多晶硅层的肖特基(Schottky)结的选择元件。在此以Ge2Sb2Te5为例说明非易失性记录材料层,但通过选择用包含硫族元素(S、Se、Te)中至少一种元素的材料的组成,能够得到同等程度的性能。

在以下的各实施例中,对按各不相同的层叠顺序层叠的构造以及适当的膜厚进行总括说明。

图1表示的是将第一多晶硅层107、第二多晶硅层106、半导体层105、非易失性记录材料层104、第二金属布线层103、第三金属布线层101依次层叠在第一金属布线层102上而成的实施例1所述的构造。

将非易失性记录材料层104形成在半导体层105、第一多晶硅层107和第二多晶硅层106上。如此,在由第一多晶硅层107和第二多晶硅层106构成的pn多晶硅二极管与非易失性记录材料层104之间设有半导体层105,因此能够抑制因重写工作时产生的热而在pn多晶硅二极管内作为杂质掺杂的原子扩散到非易失性记录材料层104。半导体层105的膜厚无论过厚还是过薄都不能发挥功能。若过厚,则虽有导电性,但电阻过大,因其温度依赖性而使非易失性记录材料层104的电阻值的温度余量不足。若过薄,则由于非易失性记录材料层104的存储写入时的反复温度上升而不能防止选择元件的特性劣化。

关于膜厚与低电阻状态、高电阻状态的在高温下的电阻比的关系,在半导体层105的膜厚为160nm时,低电阻状态、高电阻状态的电阻比约为1:20,在膜厚为200nm时,电阻比约为1:10,在膜厚为240nm时,电阻比约为1:5。在这样的电阻变化型非易失性存储器中,从防止误读出的观点考虑,需要使低电阻状态和高电阻状态的电阻比为10倍左右,因此,半导体层105的膜厚为200nm以下。

另外,对于膜厚与可重写次数的关系,在半导体层105的膜厚为3nm时,可重写次数约为105次,在半导体层105的膜厚为5nm时,可重写次数约为106次,在半导体层105的膜厚为8nm时,可重写次数约为106次。在电阻变化型非易失性存储器中,需要至少具有约106次的可重写次数,因此半导体层105的膜厚为5nm以上。

图2表示的是将非易失性记录材料层104、半导体层105、第二多晶硅层106、第一多晶硅层107、第二金属布线层103、第三金属布线层101依次层叠在第一金属布线层102上而成的实施例2所述的构造。

将非易失性记录材料层104形成在半导体层105、第二多晶硅层106和第一多晶硅层107上。如此,在由第一多晶硅层107和第二多晶硅层106构成的pn多晶硅二极管与非易失性记录材料层104之间设有半导体层105,因此能够抑制因重写工作时产生的热而在pn多晶硅二极管内作为杂质掺杂的原子扩散到非易失性记录材料层104。半导体层105的膜厚无论过厚还是过薄都不能发挥功能。若过厚,则虽然有导电性,但电阻过大,因其温度依赖性而使非易失性记录材料层104的电阻值的温度余量不足。若过薄,则由于非易失性记录材料层104的存储写入时的反复温度上升而不能防止选择元件的特性劣化。

在图2的情况下,膜厚与电阻比的关系、膜厚与可重写次数的关系也与上述图1的情况相同。

图3表示的是将第一多晶硅层107、第二多晶硅层106、半导体层105、非易失性记录材料层104、半导体层105、第二金属布线层103、第三金属布线层101依次层叠在第一金属布线层102上而成的实施例3所述的构造。即,在实施例1所述构造的半导体层105与第二金属布线层103之间还新增加了半导体层105。由此,除了实施例1所述的效果之外,还能够抑制第二金属布线层103内的金属原子向非易失性记录材料层104的扩散,能够抑制因金属原子引起的重写条件的变化。利用新增加的半导体层105能够抑制第二金属布线层103因热循环而引起的劣化,使可重写次数提高5倍以上。

图4表示的是将半导体层105、非易失性记录材料层104、半导体层105、第二多晶硅层106、第一多晶硅层107、第二金属布线层103、第三金属布线层101依次层叠在第一金属布线层102上而成的实施例4所述的构造。即,在实施例2所述构造的半导体层105与第一金属布线层102之间还新增加了半导体层105。由此,除了实施例2所述的效果之外,还能够抑制第一金属布线层102内的金属原子向非易失性记录材料层104的扩散,能够抑制因金属原子引起的重写条件的变化。利用新增加的半导体层105能够抑制第一金属布线层102因热循环而引起的劣化,使可重写次数提高5倍以上。

在图3~图4的情况下,膜厚和可重写次数的关系与上述图1的情况相同。半导体层105的总膜厚与电阻比的关系与上述图1的情况相同。

实施例1

以下,参照附图详细说明本发明的非易失性存储器的存储器单元的制造方法。在用于说明实施例的所有附图中,对同样的构件标注相同的附图标记,省略其重复说明。在以下的实施方式中,除了特别必要时,原则上不重复相同或大致相同的部分的说明。在实施方式所使用的附图中,虽然是剖视图,有时为了容易观察附图,会省略剖面线。虽然是俯视图,有时为了容易看附图,会标注剖面线。

在本实施方式中,本发明的存储器单元形成在图5所示的半导体基板201上。半导体基板201是用于形成非易失性存储器,以及形成使非易失性存储器的存储器矩阵工作的外围电路的基板。使用现有的CMOS技术制造外围电路。在此,半导体基板、存储器矩阵和外围电路的位置关系如图6~图8所示。图6~图8示意性表示与作为半导体基板的硅基板的元件形成表面相垂直的方向的剖视图。在本实施方式中,如图6所示,以在外围电路部上制造存储器矩阵部的情况为例进行说明。即,为在硅基板上形成作为第一层的外围电路部、在第二层形成存储器矩阵的层叠构造。存储器矩阵和外围电路的位置关系可以是如图7所示那样存储器矩阵部和外围电路部处于同一层,也可以是如图8所示那样存储器矩阵部和外围电路部处于同一层、且存储器矩阵部的下层也有外围电路部的层叠构造。在图6和图8中,存储器矩阵部是第二层,但也可以是第三层、第四层,至少位于外围电路部的上层。

图5表示在半导体基板201上依次堆积第一金属布线层202、第一多晶硅层203、第二非晶硅层204的构造。第一金属布线层202由溅镀形成。第一金属布线层202的材料是钨。更优选是,由于电阻率低的材料的电压降较小,可取得读出电流,因此该第一金属布线层202的材料例如可以是铝或铜。为了提高粘结性,可以在第一金属布线层202与半导体基板201之间堆积TiN等金属化合物。

第一多晶硅层203是如下这样形成:通过LP-CVD(Low PressureChemical Vapor Deposition:低压化学气相蒸镀法)堆积包含硼、镓、铟中任一种元素的非晶硅,其后通过RTA(Rapid Thermal Annealing:急速加热处理)进行结晶和杂质活性化。第一多晶硅层203具有50~250nm的膜厚。在此,在第一金属布线层202为钨的情况下,对于用来形成第一多晶硅层203的材料而言,含有硼的非晶硅与含有镓或铟的非晶硅相比难以形成钨的硅化物,因此是优选的。为了防止钨与非晶硅直接接触而发生反应形成钨的硅化物,可以在第一多晶硅层203与第一金属布线层202之间堆积TiN等金属化合物。接着,第二非晶硅层204可通过利用LP-CVD堆积含有磷或砷的非晶硅而获得。第二非晶硅层204具有50~250nm的膜厚。

图9表示对在图5中堆积的第二非晶硅层204实施激光退火的工序。通过激光退火进行第二非晶硅层204的结晶化和杂质活性化,从而形成第二多晶硅层205。在本实施例中,构成存储器单元的选择元件是pn二极管。因此,以第一多晶硅层203与第二多晶硅层205的结为pn结进行说明,也可以在存储器单元使用如np结、pin结、pi结那样的其他结、或与第一金属布线层203的肖特基结的选择元件。

图10是表示在图9基础上依次堆积了半导体层206、非易失性记录材料层207、第二金属布线层208后的图。半导体层206、非易失性记录材料层207、第二金属布线层208通过溅镀而堆积。

非易失性记录材料层207的材料是Ge2Sb2Te5,膜厚为5~300nm,更优选是纵横比较低的5~50nm,从而容易进行后工序的干蚀刻、绝缘性材料的埋入。

半导体层206是由含有非易失性记录材料层104的构成元素的材料构成的半导体层。通过使用这样的层,即使由于激光退火的高温状态而引起一部分元素从半导体层206向非易失性记录材料层扩散,也能将重写特性、对二极管的影响抑制到实用上不会有问题的程度。例如在Ge-Sb-Te族材料中即使Ge扩散,存储器特性的变化也是没有问题的程度。

半导体层206以难以发生非易失性记录材料层207的重写条件变化的Ge为材料,膜厚为5nm~200nm。该膜厚范围的理由如上所述。并且,优选Ge含量是90原子%以上。即使改变Ge而使用Ge-Si混合材料,也能得到同样的效果。在该情况下,膜厚也优选为5nm~200nm。另外,除此之外,也可以是包含Ge和除Si之外的元素。此时,若Ge含量是40原子%以上,则非易失性存储器的重写特性难以劣化,因此优选。即,作为半导体层206,在使用除Ge-Si混合材料以外的材料时,由至少含有40原子%以上的Ge的材料构成。作为该半导体层206,可以使用除Ge以外的公知的各种半导体材料,可以使用InSb、GaSb。作为半导体层尤其重要之处在于该半导体层由含有构成非易失性记录材料层的材料的半导体材料构成。即使在这些场合下,对于膜厚,优选是5nm~200nm。

在本实施例中,非易失性记录材料层207的构成元素以Ge2Sb2Te5为例,也可以使用Ge3Sb2Te6、Ge5Sb2Te8、Ge-Te等非易失性记录材料层。作为信息重写原理,相变存储器的原理是一例,但除此之外,在采用固体电解质存储器的原理时,例如可以以Cu2Se层、GeSe层作为非易失性记录材料层,使第一金属布线层和第二金属布线层的至少一方为Cu。但是,固体电解质存储器有在写入工作和消去工作中施加相反方向电压的双向工作方式、和在写入工作和消去工作中施加相同方向电压的单向工作方式,在此由于使用二极管作为非易失性记录材料层的选择元件,因此需要以单向电压驱动。

半导体层206的膜厚无论过厚还是过薄都不能发挥功能。若过厚,则虽然有导电性,但电阻过大,因其温度依赖性而使非易失性记录材料层207的电阻值的温度余量不足。若过薄,则由于非易失性记录材料层207的存储写入时的反复温度上升而不能防止选择元件的特性劣化。根据前述的理由,半导体层206的膜厚处于5nm以上200nm以下。

图11表示在图10基础上使用现有的光刻技术对抗蚀剂进行蚀刻的构造。抗蚀剂209的图案是存储器矩阵的字线的图案,是与相邻的字线图案平行延伸、纵纹状的图案。

图12表示使用现有的干刻技术在掩模对图11所示的抗蚀剂209进行蚀刻,对第二金属布线层208、非易失性记录材料层207、半导体层206、第一多晶硅层205、第二多晶硅层203和第一金属布线层202进行蚀刻,并使用现有技术除去了抗蚀剂209之后的构造。由第一金属布线层210、第一多晶硅层211、第二多晶硅层212、半导体层213、非易失性记录材料层214和第二金属布线层215构成的层叠膜的图案反映抗蚀剂209的图案,形成纵纹状图案。第一金属布线层210作为存储器矩阵的字线与半导体基板201电连接,从而可进行非易失性存储器的读出和写入,在此省略了图示。

图13表示将绝缘性材料填充于图12中的图案之间后,使用现有技术的CMP(Chemical Mechanical Polishing:化学机械研磨法)对该绝缘性材料进行切削后的构造。该切削量是与绝缘性材料217和第二金属布线层215的表面高度相同的量。

图14是通过溅镀在图13的绝缘性材料217和第二金属布线层215之上堆积第三金属布线层218的构造。第三金属布线层218的材料是钨,但更优选是电阻率低的铝、铜。

图15表示在图14的第三金属布线层218上使用现有的光刻技术对抗蚀剂进行图案形成后的构造。抗蚀剂219的图案是存储器矩阵的位线图案,是与相邻的位线图案平行延伸、纵纹状图案。抗蚀剂219的图案与第一金属布线层210的图案交叉。

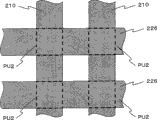

图16表示使用现有的干刻技术在掩模对图15所示的抗蚀剂219进行蚀刻,对第三布线层218、第二金属布线层215、非易失性记录材料层214、半导体层213、第二多晶硅层212、第一多晶硅层211和绝缘性材料217进行加工,使用现有技术除去了抗蚀剂219之后的构造。此时,为了能够选择存储器单元,需要残留相当于存储器矩阵字线的第一金属布线层210。由第一多晶硅层220、第二多晶硅层221、半导体层222、非易失性记录材料层223和第二金属布线层224构成的层叠膜PU1是柱状。相当于存储器矩阵位线的第三金属布线层226是与相邻的第三金属布线层226平行的纵纹形状,与第一金属布线层210交叉配置。第三金属布线层226作为存储器矩阵的位线而与半导体基板201电连接,从而可进行非易失性存储器的读出和写入,在此省略了图示。

图17表示在图16的图案之间堆积了绝缘性材料之后,使用现有技术的CMP对堆积的绝缘性材料进行切削后的构造。切削量是与绝缘性材料228和第三金属布线层226的表面高度相同的量。

图18表示在图17的构造基础上堆积了绝缘性材料229后的构造。

将按以上使用图15~图18说明的制造方法制作出的存储器单元的俯视图示于图19。作为存储器字线的第一金属布线层210与作为位线的第三金属布线层226交叉,层叠膜PU1配置在其交点。

以下,使用附图说明应用了本发明非易失性存储器的存储单元的存储器矩阵的工作方式。

图20是非易失性存储器的存储器单元阵列的结构图。存储器单元MCij(i=1、2、3···,m)(j=1、2、3···,n)的构造是:配置在多条平行配置的第一布线(以下称为字线)WLi(i=1、2、3···,m)、和与字线WLi交叉的多条并行配置的第二布线(以下称为位线)BLj(j=1、2、3···,n)的交点,选择元件SE与相变电阻元件VR串联连接。在该图中,选择元件SE的一端与字线WLi连接,相变电阻元件VR的一端与位线BLj连接,但如后所述,为了向字线WLi和位线BLj施加电压而选择存储器单元,也可以将选择元件SE的一端与位线BLj连接,相变电阻元件VR的一端与字线WLi连接。

非易失性存储器的记录如下这样进行。例如,在重写存储器单元MS11时,对第一个字线WL1施加电压Vh,对其他字线WLi施加电压V1,对第一个位线BL1施加电压V1,对其他位线BLj施加电压V1,在MC11的相变电阻元件流过电流来存储信息。在此,电压Vh是高于电压V1的电压。在重写时,为了使非选择的存储器单元不进行误写入,需要发挥作用的选择元件SE。当然,电压Vh必须是选择元件SE的击穿电压以下。非易失性存储器的读出如下这样进行。例如在读出存储器单元MC11的信息时,对第一个字线WL1施加电压Vm,对另一字线WLi施加电压V1,对第一个位线BL1施加电压V1,根据流到BL1的电流大小读出信息。

上述记述了存储器矩阵仅是在第一层的单层进行的写入、读出,若做成多层,能够进一步大容量化,因此优选。例如,如图21所示,将存储器矩阵层叠两层时,在图18的构造基础上,即在绝缘性材料310上,与实施例1的图5~图8同样,形成存储器矩阵的第二层字线即第一金属布线层402、由第二层的第一多晶硅层403、第二层的第二多晶硅层404、第二层的半导体层405、第二层的非易失性记录材料层406和第二层的第二金属布线层407构成的柱状的第二层的层叠膜PU11、相当于存储器矩阵的第二层位线的第三金属布线层409,并形成绝缘性材料408和绝缘性材料410即可。

此时,对第二层的多晶硅层进行退火时,同时第一层的非易失性记录材料层214被过热,但由布线层和绝缘层覆盖非易失性记录材料层214,因此能够防止变形、剥离。

进而在层叠k层(k=1、2、3···1)存储器矩阵时也用同样的方法制作存储器矩阵。当然,在层叠存储器矩阵的情况下,在进行非易失存储器的记录和读出时需要选择层。关于层的选择,例如在各层的字线共用的情况下,只要用位线选择写入层即可。

如此,通过层叠存储器矩阵,存储器单元的位密度变高,因此能够以低成本制造非易失存储器。

实施例2

在本实施方式中,本发明的存储器单元形成在图22所示的半导体基板201上。半导体基板201是不仅形成非易失性存储器、还形成用于使非易失性存储器的存储器矩阵工作的外围电路的基板。使用现有的CMOS技术制造外围电路。外围电路和存储器矩阵的位置关系与实施例1相同。

图22表示在半导体基板201上依次堆积第一金属布线层202、非易失性记录材料层207、半导体层206、第二非晶硅层204、第一非晶硅层251的构造。第一金属布线层202由溅镀形成。第一金属布线层202的材料是钨。更优选是,由于电阻率较低的材料的电压降较小,可取得读出电流,因此该第一金属布线层202的材料例如可以是铝或铜。为了提高粘结性,可以在第一金属布线层202与半导体基板201之间堆积TiN等金属化合物。非易失性记录材料层207、半导体层206通过溅镀堆积。非易失性记录材料层207的材料例如是适于利用结晶-非晶相变进行记录的Ge2Sb2Te5,膜厚为5~300nm,更优选是纵横比低的5~50nm的膜厚,从而容易进行后工序的干蚀刻、绝缘性材料的埋入。到此进行了层叠的阶段,也可以将半导体层206作为保护层,对非易失性记录材料层进行激光退火。此时,对半导体层206的激光退火优选使用透射多晶硅层的波长为460nm~1μm以下的长波长激光,但也可使用450nm以下的短波长的激光,以便使用多晶硅层吸收光,利用热传递使非易失性记录材料层被加热。激光照射是连续照射或脉冲照射。

第二非晶硅层204通过利用LP-CVD堆积含有磷或砷的非晶硅而获得。第二非晶硅层204具有50~250nm的膜厚。第一非晶硅层251通过利用LP-CVD堆积含有硼、镓或铟的非晶硅而获得。第一非晶硅层251具有50~250nm的膜厚。

半导体层206的膜厚无论过厚还是过薄都不能发挥功能。若过厚,则虽然有导电性,但电阻过大,因其温度依赖性而使非易失性记录材料层207的电阻值的温度余量不足。若过薄,则由于非易失性记录材料层207的存储写入时的反复温度上升而不能防止选择元件的特性劣化。出于上述理由,半导体层206的膜厚是5nm~200nm。

半导体层206的材料是难以发生非易失性记录材料层207的重写条件变化的、Ge含量为90%以上的材料。也可以是实施例1所述的材料。在本实施例中,非易失性记录材料层207的构成元素以Ge2Sb2Te5为例,也可以使用Ge3Sb2Te6、Ge5Sb2Te8、Ge-Te等非易失性记录材料层。还可以使用适用于固体电解质存储器记录的固体电解质材料。

图23表示对在图22中堆积的第二非晶硅层204和第一非晶硅层251实施激光退火的工序。通过激光退火进行第二非晶硅层204和第一非晶硅层251的结晶化和杂质活性化,从而形成第二多晶硅层205和第一多晶硅层203。在本实施例中,构成存储器单元的选择元件是pn二极管。因此,以第一多晶硅层203与第二多晶硅层205的结为pn结进行说明,但也可以在存储器单元使用如np结、pin结、pi结那样的其他结的选择元件。

若将非易失性记录材料层207形成在半导体层206、第二非晶硅层204和第一非晶硅层251的下方,则至少将半导体层206作为保护层而由激光照射对非易失性记录材料层207进行退火,从而大幅度减少as-depo状态的原子排列的紊乱,能够将存储器元件的工作成品率提高10%以上。在对多晶硅层进行退火时,隔着半导体层206位于其下方的非易失性记录材料层207也可能成为大幅度高于熔点的高温,但若用短波长的短脉冲激光进行退火,则能够抑制向下方热扩散,防止变形、剥离。在用波长为450nm以下、脉冲宽度为100μs以下的脉冲激光照射时,未观察到变形、剥离。

图24是通过溅镀在图23的多晶硅层上堆积第二金属布线层208的构造。第二金属布线层208的材料是钨,但更优选是电阻率低的铝、铜。

图25与实施例1的图11和图12所说明的方法相同,表示使用现有的光刻技术、干刻技术在图24所示的第二金属布线层208上对第二金属布线层208、第一多晶硅层203、第二多晶硅层205、半导体层206、非易失性记录材料层207和第一金属布线层202进行加工后的构造。由第一金属布线层210、第一多晶硅层211、第二多晶硅层212、半导体层213、非易失性记录材料层214和第二金属布线层215构成的层叠膜的图案与存储器矩阵的字线图案相同,是与相邻的图案平行延伸的纵纹状图案。第一金属布线层210作为存储器矩阵的字线与半导体基板201电连接,从而可进行非易失性存储器的读出和写入,在此省略了图示。

图26表示在图25的构造形成之后,使用HDP-CVD将绝缘性材料填充于图案之间,并通过CMP进行了平坦化之后,通过现有的溅镀堆积第三金属布线层218的构造。第三金属布线层218的材料是钨,但更优选是电阻率低的铝、铜。

图27表示在图26的基础上使用现有的光刻技术、干刻技术对第三金属布线层218、第二金属布线层215、非易失性记录材料层214、半导体层213、第二多晶硅层212、第一多晶硅层211和绝缘性材料217进行加工后的构造。此时,为了能够选择存储器单元,需要残留相当于存储器矩阵字线的第一金属布线层210。由非易失性记录材料层223、半导体层222、第二多晶硅层221、第一多晶硅层220、和第二金属布线层224构成的层叠膜PU2是柱状。第三金属布线层226的图案是存储器矩阵的位线图案,是与相邻的位线图案平行而延伸的纵纹形状。另外,第三金属布线层226作为存储器矩阵的位线而与半导体基板201电连接,从而可进行非易失性存储器的读出和写入,在此省略了图示。

若将半导体层最优化,则可以在层叠到第一多晶硅层后,用波长为350nm~450nm的连续激光或脉冲激光同时照射第一多晶硅层和非易失性记录材料层。此时,半导体层的材料可以是Si-Ge混合材料。Si-Ge族的折射率和衰减系数的波长依赖性如图28所示那样,因此,可以用透射多晶硅层的波长为460nm~1μm的长波长激光对非易失性记录材料层进行退火,接着用波长为350nm以下的短波长激光对多晶硅层进行退火。更优选是,在用含有Si为77原子%~94原子%的Si-Ge做成膜厚为5nm~200nm的情况下,构成对多晶硅层和非易失性记录材料层都适合的退火。

图29是在图27的构造形成之后,使用HDP-CVD将绝缘性材料228填充于图案之间,并通过CMP进行了平坦化之后,通过现有的溅镀堆积绝缘性材料229的图。

将按以上使用图22~图27和图29说明的制造方法制作出的存储器单元的俯视图示于图30。作为存储器字线的第一金属布线层210与作为位线的第三金属布线层226交叉,层叠膜PU2配置在其交点。各层所使用的材料与实施例1相同。与实施例1相同,也可以层叠多层存储器矩阵。

应用了本发明的非易失性存储器的存储器单元的存储器矩阵的工作方式与实施例1相同。

实施例3

与实施例1的图5~图18相同,图31表示在半导体基板201上形成作为存储器矩阵字线的第一金属布线层210、由第一多晶硅层220、第二多晶硅层221、半导体层222、非易失性记录材料层223、半导体层222、和第二金属布线层224构成的柱状的层叠膜PU5、相当于存储器矩阵位线的第三金属布线层226,并形成绝缘性材料229和绝缘性材料228。

通过设置半导体层,防止在非易失性记录材料层进行反复写入时由热循环引起的劣化,提高可重写次数为5倍以上。对于半导体层的总膜厚,与实施例1相同。各层所使用的材料与实施例1相同。与实施例1相同,也可以层叠多层存储器矩阵。

在本实施例中,与第二金属布线层之下无半导体层的情况相比,形成半导体材料后,将该层作为保护层,能够对非易失性记录材料层进行激光退火。对于半导体层的膜厚,与实施例1相同。各层所使用的材料与实施例1相同。与实施例1相同,也可以层叠多层存储器矩阵。

应用了本发明的非易失性存储器的存储器单元的存储器矩阵的工作方式与实施例1相同。外围电路和存储器矩阵的位置关系与实施例1相同。

实施例4

与实施例1的图5~图18相同,图32表示在半导体基板201上形成作为存储器矩阵字线的第一金属布线层210、由半导体层222、非易失性记录材料层223、半导体层222、第二多晶硅层221、第一多晶硅层220和第二金属布线层224构成的柱状的层叠膜PU6、相当于存储器矩阵位线的第三金属布线层226,并形成绝缘性材料229和绝缘性材料228。

通过设置半导体层,防止在非易失性记录材料层进行反复写入时由热循环引起的劣化,提高可重写次数为5倍以上。对于半导体层的总膜厚,与实施例1相同。各层所使用的材料与实施例1相同。与实施例1相同,也可以层叠多层存储器矩阵。

应用了本发明的非易失性存储器的存储器单元的存储器矩阵的工作方式与实施例1相同。外围电路和存储器矩阵的位置关系与实施例1相同。

以上,对各实施例进行说明。在各实施例中,在多晶硅二极管与非易失性记录材料层之间设置含有非易失性记录材料层所含元素的半导体层,从而能够抑制多晶硅二极管中所含杂质因重写工作时产生的热而扩散到非易失性记录材料层。由于该半导体层含有非易失性记录材料层所含元素,因此即使该半导体内的元素扩散到非易失性记录材料层,对重写条件的影响较小。因此,可得到重写条件稳定的非易失性存储器或可重写次数比现有技术更多的非易失性存储器。

在以上的各实施例中对相变存储器进行了说明,但只要不脱离本发明的思想,对非易失性记录材料层就能使用公知的各种非易失性记录材料。例如是相变材料、固体电解质材料和磁性材料等。此时,作为半导体材料,通过设置包含各种材料所含元素的半导体层,可以得到相同的效果。

Claims (12)

1.一种非易失性半导体存储器件,其特征在于,包括:

第一电极;

第二电极;

形成在上述第一电极和上述第二电极之间的非易失性记录材料层和选择元件;以及

形成在上述非易失性记录材料层和上述选择元件之间的、包含上述非易失性记录材料层所包含的元素的半导体层。

2.根据权利要求1所述的非易失性半导体存储器件,其特征在于,

上述半导体层形成在上述选择元件上,

上述非易失性记录材料层形成在上述半导体层上。

3.根据权利要求1所述的非易失性半导体存储器件,其特征在于:

上述半导体层形成在上述非易失性记录材料层上,

上述选择元件形成在上述半导体层上。

4.根据权利要求1所述的非易失性半导体存储器件,其特征在于:

上述非易失性记录材料层包括含有硫族元素中至少一种元素的材料。

5.根据权利要求1所述的非易失性半导体存储器件,其特征在于:

上述半导体层包含40原子%以上的Ge。

6.根据权利要求5所述的非易失性半导体存储器件,其特征在于:

上述半导体层包含90原子%以上的Ge。

7.根据权利要求1所述的非易失性半导体存储器件,其特征在于:

上述半导体层是Ge和Si的混合材料。

8.根据权利要求1所述的非易失性半导体存储器件,其特征在于:

上述半导体层是InSb或GaSb。

9.根据权利要求1所述的非易失性半导体存储器件,其特征在于:

上述半导体层具有5nm~200nm的膜厚。

10.根据权利要求1所述的非易失性半导体存储器件,其特征在于:

上述选择元件是二极管。

11.根据权利要求10所述的非易失性半导体存储器件,其特征在于:

上述二极管是多晶硅PIN二极管。

12.根据权利要求1所述的非易失性半导体存储器件,其特征在于:

存储器单元包括上述非易失性记录材料层和上述选择元件,

上述存储器单元是相变存储器的存储器单元。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007292723 | 2007-11-12 | ||

| JP2007292723A JP2009123725A (ja) | 2007-11-12 | 2007-11-12 | 不揮発性半導体記憶装置 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN101436606A true CN101436606A (zh) | 2009-05-20 |

Family

ID=40674792

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNA2008101740296A Pending CN101436606A (zh) | 2007-11-12 | 2008-11-12 | 非易失性半导体存储器件 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US20090140233A1 (zh) |

| JP (1) | JP2009123725A (zh) |

| KR (1) | KR20090049028A (zh) |

| CN (1) | CN101436606A (zh) |

| TW (1) | TW200939469A (zh) |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104465694B (zh) * | 2013-09-25 | 2018-10-09 | 爱思开海力士有限公司 | 电子设备 |

| CN108986859A (zh) * | 2017-05-30 | 2018-12-11 | 希捷科技有限公司 | 具有可重写原地存储器的数据存储设备 |

| CN110335942A (zh) * | 2019-07-08 | 2019-10-15 | 中国科学院上海微系统与信息技术研究所 | 一种相变存储器及其制作方法 |

| US20220077261A1 (en) * | 2020-09-08 | 2022-03-10 | Samsung Display Co., Ltd. | Display device and manufacturing method thereof |

| WO2022109973A1 (zh) * | 2020-11-27 | 2022-06-02 | 江苏时代全芯存储科技股份有限公司 | 相变存储器的制备方法和相变存储器 |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009283486A (ja) * | 2008-05-19 | 2009-12-03 | Toshiba Corp | 不揮発性記憶装置及びその製造方法 |

| JP5550239B2 (ja) * | 2009-01-26 | 2014-07-16 | 株式会社東芝 | 不揮発性半導体記憶装置、及びその製造方法 |

| JP5439147B2 (ja) | 2009-12-04 | 2014-03-12 | 株式会社東芝 | 抵抗変化メモリ |

| JP5420436B2 (ja) * | 2010-01-15 | 2014-02-19 | 株式会社日立製作所 | 不揮発性記憶装置およびその製造方法 |

| US8017433B2 (en) * | 2010-02-09 | 2011-09-13 | International Business Machines Corporation | Post deposition method for regrowth of crystalline phase change material |

| JP5161911B2 (ja) | 2010-03-25 | 2013-03-13 | 株式会社東芝 | 抵抗変化メモリ |

| JP5641779B2 (ja) * | 2010-05-18 | 2014-12-17 | 株式会社日立製作所 | 不揮発性記憶装置およびその製造方法 |

| JP5566217B2 (ja) * | 2010-07-30 | 2014-08-06 | 株式会社東芝 | 不揮発性記憶装置 |

| JP5674548B2 (ja) * | 2011-04-28 | 2015-02-25 | 株式会社日立製作所 | 半導体記憶装置 |

| CN103137646A (zh) * | 2013-03-15 | 2013-06-05 | 中国科学院微电子研究所 | 用于双极型阻变存储器交叉阵列集成方式的选通器件单元 |

| US8981334B1 (en) * | 2013-11-01 | 2015-03-17 | Micron Technology, Inc. | Memory cells having regions containing one or both of carbon and boron |

| US9876054B1 (en) | 2016-07-27 | 2018-01-23 | Western Digital Technologies, Inc. | Thermal management of selector |

| US10008665B1 (en) | 2016-12-27 | 2018-06-26 | Intel Corporation | Doping of selector and storage materials of a memory cell |

| KR102638628B1 (ko) | 2017-10-20 | 2024-02-22 | 삼성전자주식회사 | 가변 저항 메모리 소자 및 이의 제조 방법 |

| KR20210011638A (ko) * | 2019-07-23 | 2021-02-02 | 삼성전자주식회사 | 가변 저항 메모리 장치 및 그 제조 방법 |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4491870B2 (ja) * | 1999-10-27 | 2010-06-30 | ソニー株式会社 | 不揮発性メモリの駆動方法 |

| US20060203541A1 (en) * | 2003-03-18 | 2006-09-14 | Haruki Toda | Phase change memory device |

-

2007

- 2007-11-12 JP JP2007292723A patent/JP2009123725A/ja not_active Withdrawn

-

2008

- 2008-10-24 TW TW097140778A patent/TW200939469A/zh unknown

- 2008-11-10 US US12/268,118 patent/US20090140233A1/en not_active Abandoned

- 2008-11-11 KR KR1020080111556A patent/KR20090049028A/ko not_active Application Discontinuation

- 2008-11-12 CN CNA2008101740296A patent/CN101436606A/zh active Pending

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104465694B (zh) * | 2013-09-25 | 2018-10-09 | 爱思开海力士有限公司 | 电子设备 |

| CN108986859A (zh) * | 2017-05-30 | 2018-12-11 | 希捷科技有限公司 | 具有可重写原地存储器的数据存储设备 |

| CN108986859B (zh) * | 2017-05-30 | 2022-04-19 | 希捷科技有限公司 | 具有可重写原地存储器的数据存储设备 |

| CN110335942A (zh) * | 2019-07-08 | 2019-10-15 | 中国科学院上海微系统与信息技术研究所 | 一种相变存储器及其制作方法 |

| US20220077261A1 (en) * | 2020-09-08 | 2022-03-10 | Samsung Display Co., Ltd. | Display device and manufacturing method thereof |

| US11715739B2 (en) * | 2020-09-08 | 2023-08-01 | Samsung Display Co., Ltd. | Display device and manufacturing method thereof |

| WO2022109973A1 (zh) * | 2020-11-27 | 2022-06-02 | 江苏时代全芯存储科技股份有限公司 | 相变存储器的制备方法和相变存储器 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20090049028A (ko) | 2009-05-15 |

| JP2009123725A (ja) | 2009-06-04 |

| US20090140233A1 (en) | 2009-06-04 |

| TW200939469A (en) | 2009-09-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN101436606A (zh) | 非易失性半导体存储器件 | |

| CN101645453B (zh) | 非易失性存储装置及其制造方法 | |

| JP6860325B2 (ja) | メモリ素子及び半導体素子 | |

| US9019777B2 (en) | Nonvolatile semiconductor memory device and operating method of the same | |

| CN101499437B (zh) | 非易失性存储器件及其制造方法 | |

| US7382647B1 (en) | Rectifying element for a crosspoint based memory array architecture | |

| US8288752B2 (en) | Phase change memory device capable of reducing disturbance and method of manufacturing the same | |

| JP5420436B2 (ja) | 不揮発性記憶装置およびその製造方法 | |

| US20110141801A1 (en) | Use of symmetric resistive memory material as a diode to drive symmetric or asymmetric resistive memory | |

| CN1983660B (zh) | 非易失存储元件的制造方法 | |

| KR102507303B1 (ko) | 메모리 소자 | |

| CN110544742B (zh) | 一种铁电相变混合存储单元、存储器及操作方法 | |

| JP6505619B2 (ja) | 超格子メモリ及びクロスポイント型メモリ装置 | |

| KR20190124106A (ko) | 저항 스위칭 소자 및 이를 이용한 상변화 메모리 소자 | |

| KR101177284B1 (ko) | 상변화 물질층과 그 제조방법과 이 방법으로 형성된 상변화물질층을 포함하는 상변화 메모리 소자와 그 제조 및 동작방법 | |

| US8791448B2 (en) | Semiconductor memory devices having strapping contacts | |

| TWI704705B (zh) | 半導體記憶裝置 | |

| JP2022085888A (ja) | 半導体装置 | |

| JP2016119373A (ja) | 半導体記憶装置及びその製造方法 | |

| US20100163836A1 (en) | Low-volume phase-change material memory cell | |

| JP2024031380A (ja) | 磁気デバイス及び磁気記憶デバイス |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C02 | Deemed withdrawal of patent application after publication (patent law 2001) | ||

| WD01 | Invention patent application deemed withdrawn after publication |

Open date: 20090520 |