CN100517497C - 写入或读出信息的存储器件、方法和系统 - Google Patents

写入或读出信息的存储器件、方法和系统 Download PDFInfo

- Publication number

- CN100517497C CN100517497C CNB028279077A CN02827907A CN100517497C CN 100517497 C CN100517497 C CN 100517497C CN B028279077 A CNB028279077 A CN B028279077A CN 02827907 A CN02827907 A CN 02827907A CN 100517497 C CN100517497 C CN 100517497C

- Authority

- CN

- China

- Prior art keywords

- address

- word

- bits

- bit

- memory

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

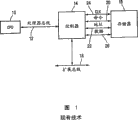

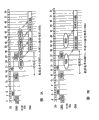

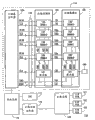

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1015—Read-write modes for single port memories, i.e. having either a random port or a serial port

- G11C7/103—Read-write modes for single port memories, i.e. having either a random port or a serial port using serially addressed read-write data registers

- G11C7/1033—Read-write modes for single port memories, i.e. having either a random port or a serial port using serially addressed read-write data registers using data registers of which only one stage is addressed for sequentially outputting data from a predetermined number of stages, e.g. nibble read-write mode

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Dram (AREA)

- Static Random-Access Memory (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/008,710 US6775759B2 (en) | 2001-12-07 | 2001-12-07 | Sequential nibble burst ordering for data |

| US10/008,710 | 2001-12-07 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1618104A CN1618104A (zh) | 2005-05-18 |

| CN100517497C true CN100517497C (zh) | 2009-07-22 |

Family

ID=21733211

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB028279077A Expired - Fee Related CN100517497C (zh) | 2001-12-07 | 2002-12-05 | 写入或读出信息的存储器件、方法和系统 |

Country Status (8)

| Country | Link |

|---|---|

| US (3) | US6775759B2 (enExample) |

| EP (1) | EP1454322A2 (enExample) |

| JP (1) | JP4238136B2 (enExample) |

| KR (1) | KR100637947B1 (enExample) |

| CN (1) | CN100517497C (enExample) |

| AU (1) | AU2002362048A1 (enExample) |

| TW (1) | TWI226535B (enExample) |

| WO (1) | WO2003050690A2 (enExample) |

Families Citing this family (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7003643B1 (en) | 2001-04-16 | 2006-02-21 | Micron Technology, Inc. | Burst counter controller and method in a memory device operable in a 2-bit prefetch mode |

| US6775759B2 (en) * | 2001-12-07 | 2004-08-10 | Micron Technology, Inc. | Sequential nibble burst ordering for data |

| US7142461B2 (en) * | 2002-11-20 | 2006-11-28 | Micron Technology, Inc. | Active termination control though on module register |

| US6967896B2 (en) * | 2003-01-30 | 2005-11-22 | Saifun Semiconductors Ltd | Address scramble |

| US6982892B2 (en) * | 2003-05-08 | 2006-01-03 | Micron Technology, Inc. | Apparatus and methods for a physical layout of simultaneously sub-accessible memory modules |

| JP4153882B2 (ja) * | 2004-02-17 | 2008-09-24 | 株式会社東芝 | 半導体集積回路装置 |

| US7236385B2 (en) * | 2004-06-30 | 2007-06-26 | Micron Technology, Inc. | Memory architecture |

| US7519877B2 (en) | 2004-08-10 | 2009-04-14 | Micron Technology, Inc. | Memory with test mode output |

| US20060161743A1 (en) * | 2005-01-18 | 2006-07-20 | Khaled Fekih-Romdhane | Intelligent memory array switching logic |

| US20060171234A1 (en) * | 2005-01-18 | 2006-08-03 | Liu Skip S | DDR II DRAM data path |

| US20060171233A1 (en) * | 2005-01-18 | 2006-08-03 | Khaled Fekih-Romdhane | Near pad ordering logic |

| KR100596799B1 (ko) * | 2005-04-27 | 2006-07-04 | 주식회사 하이닉스반도체 | 메모리 장치용 입력 데이타 분배 장치 |

| US7457901B2 (en) * | 2005-07-05 | 2008-11-25 | Via Technologies, Inc. | Microprocessor apparatus and method for enabling variable width data transfers |

| US7441064B2 (en) | 2005-07-11 | 2008-10-21 | Via Technologies, Inc. | Flexible width data protocol |

| US7502880B2 (en) * | 2005-07-11 | 2009-03-10 | Via Technologies, Inc. | Apparatus and method for quad-pumped address bus |

| US7590787B2 (en) * | 2005-07-19 | 2009-09-15 | Via Technologies, Inc. | Apparatus and method for ordering transaction beats in a data transfer |

| US7444472B2 (en) | 2005-07-19 | 2008-10-28 | Via Technologies, Inc. | Apparatus and method for writing a sparsely populated cache line to memory |

| KR100759780B1 (ko) * | 2006-09-05 | 2007-09-20 | 삼성전자주식회사 | 반도체 메모리 장치 및 반도체 메모리 장치의 데이터 입출력 방법 |

| US9009570B2 (en) * | 2012-06-07 | 2015-04-14 | Micron Technology, Inc. | Integrity of an address bus |

| KR102468764B1 (ko) * | 2017-12-19 | 2022-11-18 | 에스케이하이닉스 주식회사 | 반도체 장치 |

| US10747466B2 (en) * | 2018-12-28 | 2020-08-18 | Texas Instruments Incorporated | Save-restore in integrated circuits |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5953278A (en) * | 1996-07-11 | 1999-09-14 | Texas Instruments Incorporated | Data sequencing and registering in a four bit pre-fetch SDRAM |

| US6240047B1 (en) * | 1998-07-06 | 2001-05-29 | Texas Instruments Incorporated | Synchronous dynamic random access memory with four-bit data prefetch |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5659713A (en) | 1992-04-24 | 1997-08-19 | Digital Equipment Corporation | Memory stream buffer with variable-size prefetch depending on memory interleaving configuration |

| JP2982618B2 (ja) | 1994-06-28 | 1999-11-29 | 日本電気株式会社 | メモリ選択回路 |

| JP2817672B2 (ja) | 1995-08-11 | 1998-10-30 | 日本電気株式会社 | 半導体メモリ |

| JPH09223389A (ja) | 1996-02-15 | 1997-08-26 | Mitsubishi Electric Corp | 同期型半導体記憶装置 |

| US5784705A (en) * | 1996-07-15 | 1998-07-21 | Mosys, Incorporated | Method and structure for performing pipeline burst accesses in a semiconductor memory |

| US5802005A (en) * | 1996-09-23 | 1998-09-01 | Texas Instruments Incorporated | Four bit pre-fetch sDRAM column select architecture |

| JPH1139871A (ja) | 1997-01-10 | 1999-02-12 | Mitsubishi Electric Corp | 同期型半導体記憶装置 |

| JPH10334659A (ja) | 1997-05-29 | 1998-12-18 | Mitsubishi Electric Corp | 同期型半導体記憶装置 |

| US5996043A (en) * | 1997-06-13 | 1999-11-30 | Micron Technology, Inc. | Two step memory device command buffer apparatus and method and memory devices and computer systems using same |

| US6115321A (en) * | 1997-06-17 | 2000-09-05 | Texas Instruments Incorporated | Synchronous dynamic random access memory with four-bit data prefetch |

| KR100306966B1 (ko) | 1998-08-04 | 2001-11-30 | 윤종용 | 동기형버스트반도체메모리장치 |

| US6137735A (en) * | 1998-10-30 | 2000-10-24 | Mosaid Technologies Incorporated | Column redundancy circuit with reduced signal path delay |

| US6172893B1 (en) * | 1999-01-05 | 2001-01-09 | Micron Technology, Inc. | DRAM with intermediate storage cache and separate read and write I/O |

| US6081479A (en) * | 1999-06-15 | 2000-06-27 | Infineon Technologies North America Corp. | Hierarchical prefetch for semiconductor memories |

| JP4756724B2 (ja) | 2000-02-24 | 2011-08-24 | エルピーダメモリ株式会社 | 半導体記憶装置 |

| US6658523B2 (en) * | 2001-03-13 | 2003-12-02 | Micron Technology, Inc. | System latency levelization for read data |

| US6779074B2 (en) * | 2001-07-13 | 2004-08-17 | Micron Technology, Inc. | Memory device having different burst order addressing for read and write operations |

| US6775759B2 (en) * | 2001-12-07 | 2004-08-10 | Micron Technology, Inc. | Sequential nibble burst ordering for data |

-

2001

- 2001-12-07 US US10/008,710 patent/US6775759B2/en not_active Expired - Fee Related

-

2002

- 2002-12-03 TW TW091135016A patent/TWI226535B/zh not_active IP Right Cessation

- 2002-12-05 KR KR1020047008745A patent/KR100637947B1/ko not_active Expired - Fee Related

- 2002-12-05 WO PCT/US2002/038572 patent/WO2003050690A2/en not_active Ceased

- 2002-12-05 AU AU2002362048A patent/AU2002362048A1/en not_active Abandoned

- 2002-12-05 JP JP2003551678A patent/JP4238136B2/ja not_active Expired - Fee Related

- 2002-12-05 EP EP02797174A patent/EP1454322A2/en not_active Withdrawn

- 2002-12-05 CN CNB028279077A patent/CN100517497C/zh not_active Expired - Fee Related

-

2004

- 2004-02-13 US US10/778,257 patent/US7085912B2/en not_active Expired - Fee Related

-

2006

- 2006-04-20 US US11/407,780 patent/US7340584B2/en not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5953278A (en) * | 1996-07-11 | 1999-09-14 | Texas Instruments Incorporated | Data sequencing and registering in a four bit pre-fetch SDRAM |

| US6240047B1 (en) * | 1998-07-06 | 2001-05-29 | Texas Instruments Incorporated | Synchronous dynamic random access memory with four-bit data prefetch |

Also Published As

| Publication number | Publication date |

|---|---|

| CN1618104A (zh) | 2005-05-18 |

| TW200300882A (en) | 2003-06-16 |

| EP1454322A2 (en) | 2004-09-08 |

| US6775759B2 (en) | 2004-08-10 |

| US20030110348A1 (en) | 2003-06-12 |

| KR20040063985A (ko) | 2004-07-15 |

| TWI226535B (en) | 2005-01-11 |

| JP2005512262A (ja) | 2005-04-28 |

| AU2002362048A1 (en) | 2003-06-23 |

| US20040162935A1 (en) | 2004-08-19 |

| JP4238136B2 (ja) | 2009-03-11 |

| US20060190677A1 (en) | 2006-08-24 |

| US7340584B2 (en) | 2008-03-04 |

| WO2003050690A2 (en) | 2003-06-19 |

| US7085912B2 (en) | 2006-08-01 |

| AU2002362048A8 (en) | 2003-06-23 |

| WO2003050690A3 (en) | 2004-01-29 |

| KR100637947B1 (ko) | 2006-10-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100517497C (zh) | 写入或读出信息的存储器件、方法和系统 | |

| US5555528A (en) | Dynamic random access memory persistent page implemented as processor register sets | |

| TW384426B (en) | Virtual channel memory system | |

| CN100419901C (zh) | 具有用于读写操作的不同突发顺序寻址的存储器件 | |

| US6128244A (en) | Method and apparatus for accessing one of a plurality of memory units within an electronic memory device | |

| JPH1186532A (ja) | 半導体記憶装置 | |

| CN101568904A (zh) | 非易失性存储器的成扇形展开的高速系统体系结构和输入/输出电路 | |

| CN101401166A (zh) | 具有多个地址、数据及命令总线的存储器装置及方法 | |

| USRE38955E1 (en) | Memory device having a relatively wide data bus | |

| JPH08297966A (ja) | マルチバンク構造のメモリセルアレイ | |

| JP2817685B2 (ja) | 半導体メモリ | |

| JP4828037B2 (ja) | 半導体メモリ装置及びデータ伝送方法 | |

| JPH1166892A (ja) | 半導体装置のデータ入出力回路及びデータ入出力方法 | |

| EP1028427B1 (en) | Hierarchical prefetch for semiconductor memories | |

| JP2002334582A (ja) | メモリ装置及びオーダーリング方法 | |

| KR100571435B1 (ko) | 메모리 디바이스 및 그 어드레스 지정 방법 | |

| JPH10134576A (ja) | 半導体メモリ装置 | |

| JP2000132968A (ja) | 半導体集積回路装置 | |

| JPH01149445A (ja) | 半導体集積回路装置 | |

| HK1018341A (en) | Synchronous dynamic random access memory architecture for sequential burst mode |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C17 | Cessation of patent right | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20090722 Termination date: 20101205 |