CN100451663C - 电源电平检测器 - Google Patents

电源电平检测器 Download PDFInfo

- Publication number

- CN100451663C CN100451663C CNB2007100016616A CN200710001661A CN100451663C CN 100451663 C CN100451663 C CN 100451663C CN B2007100016616 A CNB2007100016616 A CN B2007100016616A CN 200710001661 A CN200710001661 A CN 200710001661A CN 100451663 C CN100451663 C CN 100451663C

- Authority

- CN

- China

- Prior art keywords

- power supply

- circuit

- reference voltage

- comparator circuit

- control circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000003990 capacitor Substances 0.000 claims description 15

- 230000008878 coupling Effects 0.000 claims description 3

- 238000010168 coupling process Methods 0.000 claims description 3

- 238000005859 coupling reaction Methods 0.000 claims description 3

- 239000004065 semiconductor Substances 0.000 claims description 3

- 229910044991 metal oxide Inorganic materials 0.000 claims description 2

- 150000004706 metal oxides Chemical class 0.000 claims description 2

- 238000007689 inspection Methods 0.000 claims 2

- 230000008676 import Effects 0.000 claims 1

- 238000001514 detection method Methods 0.000 abstract description 22

- 230000007423 decrease Effects 0.000 description 4

- 238000000034 method Methods 0.000 description 4

- 238000010586 diagram Methods 0.000 description 3

- 230000009471 action Effects 0.000 description 2

- 230000008569 process Effects 0.000 description 2

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

Images

Landscapes

- Measurement Of Current Or Voltage (AREA)

- Electronic Switches (AREA)

- Dram (AREA)

Abstract

本发明的电源电平检测器包括一电源分压器、一能隙参考电压产生器、一比较电路、一控制电路以及一强制电路。一电源经电源分压器分压后输出一检电压。电源重置后,能隙参考电压产生器会在电源回复至一电平后产生一能隙参考电压。比较电路比较检电压以及能隙参考电压以判断电源的电平。控制电路在能隙参考电压尚未产生时禁止比较电路,并在能隙参考电压产生后切换成使能比较电路。强制电路耦接比较电路的输出端,用于在比较电路为禁止状态时,强制比较电路的输出端电压为一定值,以避免输出错误信息。

Description

技术领域

本发明涉及一种电源电平检测器(power detector)。

背景技术

图1为一种传统电源电平检测器100,用于检一芯片所使用的电源VDD的电平,其中,包括一能隙参考电压产生器(Bandgap Voltage Generator)102、一检电压产生电路104、以及一比较器CMP。该能隙参考电压产生器102常见于一般集成电路芯片中,乃用来产生一能隙参考电压VBG供芯片参考。该能隙参考电压VBG为固定值(通常为1.25伏特)不受温度影响、亦不随电源VDD飘移。该检电压产生电路104包括三个晶体管(M1、M2、与M3)以及两个电阻(R1与R2),乃用来在该能隙参考电压VBG产生后,分压该电源VDD,产生一检电压Vdet。如图1所示,该能隙参考电压VBG产生后,晶体管M1导通、晶体管M2操作在饱和区(saturation region)、并且晶体管M3导通且产生一电流流经上述电阻R1与R2。由于晶体管M3的面积远大于晶体管M2,因此晶体管M3操作在线性区(linear region),以电阻型态操作,其电阻值为Ron。电阻Ron、R1、与R2将该电源VDD分压后输出该检电压Vdet。该比较器CMP比较该检电压Vdet以及该能隙参考电压VBG后,输出一标记Flag标示比较结果,以供判断该电源VDD目前的电平。

然而,该电源VDD遭重置(reset)时,上述传统电源电平检测器100常发生错误。因为该能隙参考电压产生器102在电源VDD被重置后,并不是立即产生该能隙参考电压VBG;必须在该电源VDD回复至一电平以后,才会产生该能隙参考电压VBG举例说明之,假设VDD为5V,该电源VDD被重置后,该能隙参考电压产生器102一开始并不会输出该能隙参考电压VBG,必须等到该电源VDD回升至一电平(例如2.5V)后才会产生该能隙参考电压VBG。如此一来,该电源VDD遭重置后尚未回升至该电平的这一段时间,该比较器CMP的两个输入信号(该能隙参考电压VBG以及该检电压Vdet)都还没有准备好,因此该比较器CMP的运作会发生错误。

发明内容

本发明提供一种新颖的电源电平检测器,可避免上述传统电源电平检测器100在电源重置时所发生的问题。

本发明所提出的电源电平检测器包括一电源分压器、一能隙参考电压产生器、一比较电路、一控制电路、以及一强制电路。该电源分压器乃用来分压一电源,以产生一检电压。在重置(reset)该电源后,该能隙参考电压产生器会在该电源回复至一电平后,产生一能隙参考电压。该比较电路乃用来比较该检电压以及该能隙参考电压,以判断该电源的电平。在该能隙参考电压尚未产生时,该控制电路会禁止(disable)该比较电路。在该能隙参考电压产生后,该控制电路由禁止该比较电路切换成使能(enable)该比较电路。该强制电路耦接于该比较电路的输出端,由该控制电路控制。在该比较电路为禁止状态时,该强制电路会强制该比较电路的输出端电压为一定值,以避免该比较电路输出错误信息。

为让本发明的上述和其它目的、特征、和优点能更明显易懂,下文特举出较佳实施例,并配合附图作详细说明。

附图说明

图1为一种传统电源电平检测器;

图2为本发明的电源电平检测器的示意图;

图3为本发明的电源电平检测器的一实施例;

图4为控制电路304的一实施例;

图5为控制电路304的另一实施例;

图6为该放电电流I与图5的第二晶体管M2的漏源极压差VDS_M2的关系图;

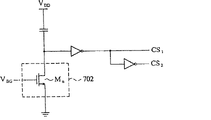

图7为控制电路304的另一实施例;

图8为本发明的电源电平检测器的一实施例;

图9为本发明的电源电平检测器的一实施例;以及

图10为本发明的电源电平检测器的一实施例。

附图符号说明

100-传统电源电平检测器;

102-能隙参考电压产生器;104-检电压产生电路;

200-电源电平检测器; 202-电源分压器;

204-能隙参考电压产生器;206-比较电路;

208-控制电路; 210-强制电路;

300-电源电平检测器; 302-比较电路;

304-控制电路; 402-放电电路;

502-放电电路; 702-放电电路;

802-电源分压器; 902-切换电路;

904-电源分压器; 906-比较电路;

1002、1004-比较电路; 1006-电源分压器;

C-电容; CMP-比较器;

CS1-第一控制信号; CS2-第二控制信号;

Flag、Flag1、Flag2-比较电路的输出标记;

I-放电电流; Inv1-第一反相器;

Inv2-第二反相器;

M1、M2、与M3-晶体管; Mn-N型金属氧化物半导体晶体管;

R1与R2-电阻;

SW1-第一开关; SW2-第二开关;

SW3-第三开关; SW4-第四开关;

VBG-能隙参考电压 VDD-电源;

Vdet、Vdet1、Vdet2-检电压。

具体实施方式

图2为本发明的电源电平检测器的示意图,其中,一电源电平检测器200包括一电源分压器202、一能隙参考电压产生器204、一比较电路206、一控制电路208、以及一强制电路210。该电源分压器202将一电源VDD分压后,输出一检电压Vdet。该检电压Vdet为该电源VDD的分压。该能隙参考电压产生器204乃用来产生具有固定值的一能隙参考电压VBC。当该电源VDD发生重置(reset)时,该能隙参考电压产生器204必须等待该电源VDD回升至一电平后,才会产生该能隙参考电压VBG。该比较电路206乃用来比较该检电压Vdet以及该能隙参考电压VBG,以判断该电源VDD的电平。该比较电路206的使能/禁止(enable/disable)由该控制电路208控制。在该能隙参考电压VBG尚未产生时,该控制电路208的动作为禁止(disable)该比较电路206。在该能隙参考电压VBG产生后,该控制电路208的动作由禁止该比较电路206切换成使能(enable)该比较电路206。该强制电路210耦接于该比较电路206的输出端,亦由该控制电路208控制。该比较电路206为禁止状态时,该强制电路210会强制该比较电路206的输出端电压为一定值,以避免该比较电路206输出错误的比较结果。

图3为本发明的电源电平检测器的一实施例。电源电平检测器300所采用的比较电路302包括一比较器CMP以及一第一开关SW1。该第一开关SW1耦接于该比较器CMP的电源端与该电源VDD之间,由控制电路304所产生的一第一控制信号CS1控制。该第一开关SW1在该控制电路304禁止该比较电路302时为不导通,并且在该控制电路304使能该比较电路302时为导通。

如图3所示,电源电平检测器300以一第二开关SW2实现图2的强制电路210。该第二开关SW2由控制电路304所产生的一第二控制信号CS2控制。由于此实施例将该能隙参考电压VBG输入该比较器CMP的反相输入端,并且将该检电压Vdet输入该比较器CMP的非反相输入端,故该第二开关SW2必须在该比较电路302为禁止状态时将其输出端耦接至一接地端(一定电压端),以确保该比较电路302不会在该比较电路302为禁止状态时误判该检电压Vdet高于该能隙参考电压VBG。

图4为控制电路304的一实施例,其中包括一电容C、一放电电路402、一第一反相器Inv1、以及一第二反相器Inv2。如图所示,该电容C的第一端点以及第二端点分别耦接该电源VDD以及该放电电路402。该放电电路402在该能隙参考电压VBG产生后启动,用于产生一放电电流I放电该电容C。该第一反相器Inv1的输入端耦接该电容C的第二端点,以输出上述第一控制信号CS1控制上述第一开关SW1。该第一控制信号CS1为高电平时,该第一开关SW1导通,该比较电路302被使能;反之,该第一开关SW1不导通,该比较电路302被禁止。该第二反相器Inv2的输入端耦接该第一反相器Inv1的输出端,用于反相该第一控制信号CS1以产生上述第二控制信号CS2控制该第二开关SW2。该第二控制信号CS2为高电平时,该第二开关SW2导通,反之,则不导通。

在本发明中,上述放电电流I可随着该电容C的第二端点的电压电平下降而减少。图5为控制电路304的另一实施例,所采用的放电电路502为一电流镜,其中,包括一第一晶体管M1以及一第二晶体管M2。该第一晶体管M1的栅极与漏极耦接在一起。该第一与第二晶体管(M1以及M2)的栅极电压皆由该能隙参考电压VBG控制,并且具有同样的栅源极压差。该第二晶体管M2的漏极端耦接该电容C的第二端点。

参阅图5,该电源VDD发生重置但尚未回升至一电平时,该能隙参考电压VBG尚未产生,故该放电电路502尚未开启,该放电电流I为零。此时,该电容C的第二端点的电位会随着其第一端点变化,即随着该电源VDD上升。因此,该电容C的第二端点的电位经该第一与第二反相器Inv1与Inv2处理后,会输出低电平的第一控制信号CS1以及高电平的第二控制信号CS2。参阅图3,藉由上述第一与第二控制信号(CS1以及CS2),该控制电路304禁止该比较电路302并且强制该比较电路302所产生的标记Flag为接地,以避免该比较电路302输出错误的判断结果。

参阅图5,该电源VDD回升至该电平后,该能隙参考电压VBG产生,该放电装置502开启并且产生一放电电流I放电该电容C。图6为该放电电流I与该第二晶体管M2的漏源极压差VDS_M2的关系图。如图6所示,该放电电流I刚产生时,该电容C的第二端点的电位(即该第二晶体管M2的漏源极压差VDS_M2)为V0,该放电电流I=I0。该电容C的第二端点的电位(VDS_M2)在放电过程中逐渐下降,如图6所示,该放电电流I亦随之逐渐降低,最后两者皆降至零。上述放电程序会令该电容C的第二端点电位经该第一与第二反相器Inv1与Inv2处理后,输出高电平的第一控制信号CS1、及低电平的第二控制信号CS2。因此,该比较电路302被使能,并且该比较电路302的输出端不再被强制接地。该比较电路302得以开始正常运作。

图7为控制电路304的另一实施例,所采用的放电电路702为一N型金属氧化物半导体晶体管Mn,其栅极耦接该能隙参考电压VBG、其漏极耦接该电容C的第二端点、并且其源极接地。由上述实施例可知,本发明的放电电路在该电容C的第二端点的电位降至零后即停止提供该放电电流I,故本发明不需要耗费大量能量。

图8为本发明的另一实施例,其中,所采用的电源分压器802乃由串联在该电源VDD与一接地端之间的多个电阻(本实施例为R1与R2)所组成。本发明采用单纯电阻分压,使用者可轻易掌握该检电压Vdet与该电源VDD的关系。反观图1的传统电源电平检测器100,该检电压产生电路104的晶体管M3的电阻值Ron会随着工艺过程变化,不易掌握,容易造成使用者困扰。

图9为本发明的另一实施例,其中,还包括一切换装置902,耦接于该电源分压器904与该比较电路906之间,用于在该比较电路906为禁止状态时,将该检电压Vdet切换成一接地端以输入该比较电路906。如图所示,该切换装置902包括一第三开关SW3、以及一第四开关SW4。该第三开关SW3在该比较电路906被使能(该第一控制信号CS1为高电平)时导通,用于耦接该检电压Vdet至该比较电路906。该第四开关SW4在该比较电路906被禁止(该第二控制信号CS2为高电平)时导通,用于耦接该接地端至该比较电路906。

图10为本发明的另一种实施例,其中包括多组比较电路(1002与1004)。本实施例的电源分压器1006会输出两组检电压(Vdet1与Vdet2),分别输入比较电路1002与1004。所述比较电路1002与1004的使能与否、以及其输出端所耦接的强制电路的动作与否皆和本发明其它实施例相同。藉由本实施例,使用者可由标记Flag1与Flag2判断该电源VDD目前位于某一电压范围内。

本发明虽以较佳实施例揭露如上,然其并非用于限定本发明的范围,任何熟习此项技艺者,在不脱离本发明的精神和范围内,当可做些许的更动与润饰,因此本发明的保护范围当视本发明的申请专利范围所界定者为准。

Claims (10)

1.一种电源电平检测器,其中包括:

一电源分压器,分压一电源以产生一检电压;

一能隙参考电压产生器,在该电源被重置并且回复至一电平后产生一能隙参考电压;

一比较电路,比较该检电压以及该能隙参考电压,以判断该电源的电平;

一控制电路,在该能隙参考电压尚未产生时,禁止该比较电路,并且在该能隙参考电压产生后,由禁止该比较电路转变成使能该比较电路;以及

一强制电路,耦接于该比较电路的输出端,由该控制电路控制,用于在该控制电路尚未使能该比较电路时,强制该比较电路的输出端电压为一定值。

2.如权利要求1所述的电源电平检测器,其中,该比较电路包括:

一比较器;以及

一第一开关,耦接于该比较器的电源端与该电源之间,由该控制电路控制,在上述控制电路禁止该比较电路时为不导通,并且在上述控制电路使能该比较电路时为导通。

3.如权利要求2所述的电源电平检测器,其中,该强制电路可为一第二开关,用于在该控制电路尚未使能该比较电路时,耦接该比较电路的输出端至一定电压端以提供该定值。

4.如权利要求3所述的电源电平检测器,其中,该控制电路包括:

一电容,其第一端点耦接该电源;

一放电装置,耦接该电容的第二端点,在该能隙参考电压产生后启动,以产生一放电电流对该电容放电;

一第一反相器,其输入端耦接该电容的第二端点以输出一第一控制信号控制该第一开关,其中,该第一控制信号为高电平时,该第一开关导通,反之则不导通;以及

一第二反相器,用于反相该第一控制信号以产生一第二控制信号控制该第二开关,其中,该第二控制信号为高电平时,该第二开关导通,反之则不导通。

5.如权利要求4所述的电源电平检测器,其中,上述放电电流随着该电容的第二端点的电压电平下降而减少。

6.如权利要求4所述的电源电平检测器,其中,该放电装置可为一电流镜,其中包括:

一第一晶体管,其栅极与漏极耦接在一起;以及

一第二晶体管,与该第一晶体管具有同样的栅源极压差,其中,该第二晶体管的漏极耦接该电容的第二端点,并且该第二晶体管的栅极与该第一晶体管的栅极耦接于该能隙参考电压产生器的输出端。

7.如权利要求4所述的电源电平检测器,其中,该放电装置可为一N型金属氧化物半导体晶体管,其栅极耦接该能隙参考电压产生器的输出端,其漏极耦接该电容的第二端点,并且其源极耦接一接地端。

8.如权利要求1所述的电源电平检测器,其中,该电源分压器由串联在该电源与一接地端之间的多个电阻组成。

9.如权利要求1所述的电源电平检测器,还包括一切换装置,用于在该控制电路尚未使能该比较电路时,将该检电压切换成一接地端以输入该比较电路。

10.如权利要求9所述的电源电平检测器,其中,该切换装置包括:

一第三开关,由该控制电路控制,用于在该控制电路使能该比较电路时,耦接该检电压至该比较电路,并且在该控制电路禁止该比较电路时为不导通;以及

一第四开关,由该控制电路控制,用于在该控制电路禁止该比较电路时,耦接该接地端至该比较电路,并且在该控制电路使能该比较电路时为不导通。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US82429006P | 2006-09-01 | 2006-09-01 | |

| US60/824,290 | 2006-09-01 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1996025A CN1996025A (zh) | 2007-07-11 |

| CN100451663C true CN100451663C (zh) | 2009-01-14 |

Family

ID=38251168

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB2007100016616A Active CN100451663C (zh) | 2006-09-01 | 2007-01-09 | 电源电平检测器 |

Country Status (2)

| Country | Link |

|---|---|

| CN (1) | CN100451663C (zh) |

| TW (1) | TWI312869B (zh) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101923145B (zh) * | 2009-06-15 | 2013-01-23 | 凌通科技股份有限公司 | 电源检测电路、便携式装置以及防止数据遗失的方法 |

| CN101726649B (zh) * | 2009-10-30 | 2013-04-24 | 海洋王照明科技股份有限公司 | 一种信号检测电路、应急电源切换装置及应急灯 |

| CN103516349A (zh) * | 2012-06-26 | 2014-01-15 | 深圳市威尔科思技术有限公司 | 高电压兼容输入系统 |

| US9081396B2 (en) * | 2013-03-14 | 2015-07-14 | Qualcomm Incorporated | Low power and dynamic voltage divider and monitoring circuit |

| CN108349725B (zh) * | 2015-11-12 | 2021-11-19 | 罗切斯特大学 | 用于高性能能量有效低温计算的超导系统架构 |

| CN105403791A (zh) * | 2015-12-09 | 2016-03-16 | 华南理工大学 | 一种设备启动检测电路 |

| TWI629492B (zh) * | 2017-08-03 | 2018-07-11 | 新唐科技股份有限公司 | 參考電壓電路之測試系統及方法 |

| CN111092613B (zh) * | 2018-10-23 | 2023-12-05 | 雅特力科技(重庆)有限公司 | 上电重置电路与相关的重置方法 |

| CN111987754A (zh) * | 2019-05-24 | 2020-11-24 | 凹凸电子(武汉)有限公司 | 可移动设备以及对负载供电的控制方法 |

| CN112787486B (zh) * | 2019-11-08 | 2023-04-28 | 奇景光电股份有限公司 | 电源就绪信号产生装置及其操作方法 |

| CN113760802B (zh) * | 2020-06-03 | 2024-05-14 | 长鑫存储技术有限公司 | 片上终端电路及存储器设备 |

| US11888474B2 (en) | 2020-06-03 | 2024-01-30 | Changxin Memory Technologies, Inc. | On die termination circuit and memory device |

| CN116482564A (zh) * | 2023-04-26 | 2023-07-25 | 星宸科技股份有限公司 | 电源检测装置与电源检测方法 |

| CN118837605B (zh) * | 2024-06-25 | 2025-10-31 | 珠海全志科技股份有限公司 | 供电电压自动检测装置、方法及电子设备 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN2432731Y (zh) * | 2000-05-30 | 2001-05-30 | 麦肯积体电路股份有限公司 | 电源电压检测电路 |

| CN2438273Y (zh) * | 2000-06-12 | 2001-07-04 | 麦肯积体电路股份有限公司 | 检测电源电压切入点电路 |

| CN1381732A (zh) * | 2002-04-15 | 2002-11-27 | 威盛电子股份有限公司 | 电压电位检测器 |

| CN1494759A (zh) * | 2001-11-30 | 2004-05-05 | 索尼公司 | 电源产生电路、显示装置和便携终端器件 |

| US20040113681A1 (en) * | 2002-10-12 | 2004-06-17 | Oki Electric Industry Co., Ltd. | Voltage sensing circuit |

-

2006

- 2006-12-29 TW TW95149874A patent/TWI312869B/zh active

-

2007

- 2007-01-09 CN CNB2007100016616A patent/CN100451663C/zh active Active

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN2432731Y (zh) * | 2000-05-30 | 2001-05-30 | 麦肯积体电路股份有限公司 | 电源电压检测电路 |

| CN2438273Y (zh) * | 2000-06-12 | 2001-07-04 | 麦肯积体电路股份有限公司 | 检测电源电压切入点电路 |

| CN1494759A (zh) * | 2001-11-30 | 2004-05-05 | 索尼公司 | 电源产生电路、显示装置和便携终端器件 |

| CN1381732A (zh) * | 2002-04-15 | 2002-11-27 | 威盛电子股份有限公司 | 电压电位检测器 |

| US20040113681A1 (en) * | 2002-10-12 | 2004-06-17 | Oki Electric Industry Co., Ltd. | Voltage sensing circuit |

Non-Patent Citations (1)

| Title |

|---|

| 高精度宽容限电源电压检测电路的设计. 张颖,潘亮.中国集成电路,第68期. 2005 * |

Also Published As

| Publication number | Publication date |

|---|---|

| CN1996025A (zh) | 2007-07-11 |

| TW200813443A (en) | 2008-03-16 |

| TWI312869B (en) | 2009-08-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100451663C (zh) | 电源电平检测器 | |

| US5440254A (en) | Accurate low voltage detect circuit | |

| CN102025263A (zh) | 电源启动检测电路 | |

| KR101646910B1 (ko) | 파워 온 리셋 회로를 포함하는 반도체 소자 | |

| EP3550723B1 (en) | Pad tracking circuit for high-voltage input-tolerant output buffer | |

| CN111693759B (zh) | 电压检测器 | |

| JP2004163315A (ja) | 電圧検出回路 | |

| CN109964276B (zh) | 用于从处于断电状态的器件中泄放电源电压的电路 | |

| CN109696940B (zh) | 用于识别装置输出处的故障的方法和其系统 | |

| CN106921371B (zh) | 低功耗上电复位电路 | |

| CN115754440B (zh) | 一种低功耗、结构简易的电压检测电路 | |

| US9086434B1 (en) | Methods and systems for voltage reference power detection | |

| US8344779B2 (en) | Comparator circuit with hysteresis, test circuit, and method for testing | |

| CN111007910B (zh) | 开漏输出控制电路 | |

| JP2001339285A (ja) | パワーオフ検出回路 | |

| CN106972852B (zh) | 接口电路和电子设备 | |

| KR20210127207A (ko) | 정전 검출 회로 | |

| CN119543898B (zh) | 一种具有迟滞效应的上电复位电路 | |

| CN115201542B (zh) | 电压检测电路 | |

| US12542541B2 (en) | Control method of power switch module and associated circuit | |

| US7463074B2 (en) | Integrated circuit and method for generating a ready signal | |

| KR200222131Y1 (ko) | 전력 오류 감지 회로 | |

| US8194491B2 (en) | Power-up circuit | |

| KR100223672B1 (ko) | 커플링현상에 의한 액티브 피크 전류를 방지하기위한 반도체 장치 | |

| CN115764797A (zh) | 欠压锁定电路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant |