WO2020179494A1 - 半導体装置および撮像装置 - Google Patents

半導体装置および撮像装置 Download PDFInfo

- Publication number

- WO2020179494A1 WO2020179494A1 PCT/JP2020/007048 JP2020007048W WO2020179494A1 WO 2020179494 A1 WO2020179494 A1 WO 2020179494A1 JP 2020007048 W JP2020007048 W JP 2020007048W WO 2020179494 A1 WO2020179494 A1 WO 2020179494A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- substrate

- wirings

- wiring

- semiconductor substrate

- insulating film

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 193

- 238000003384 imaging method Methods 0.000 title claims description 144

- 239000000463 material Substances 0.000 claims abstract description 52

- 239000000758 substrate Substances 0.000 claims description 324

- 239000010410 layer Substances 0.000 claims description 273

- 238000012546 transfer Methods 0.000 claims description 59

- 238000009792 diffusion process Methods 0.000 claims description 48

- 238000007667 floating Methods 0.000 claims description 42

- 238000012545 processing Methods 0.000 claims description 42

- 230000003321 amplification Effects 0.000 claims description 36

- 238000003199 nucleic acid amplification method Methods 0.000 claims description 36

- 238000000034 method Methods 0.000 claims description 31

- 238000006243 chemical reaction Methods 0.000 claims description 27

- 239000011229 interlayer Substances 0.000 claims description 24

- 230000008569 process Effects 0.000 claims description 14

- 239000011800 void material Substances 0.000 claims description 13

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 8

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 6

- 238000005498 polishing Methods 0.000 claims description 6

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 claims description 5

- 229910020177 SiOF Inorganic materials 0.000 claims description 3

- 238000012986 modification Methods 0.000 description 82

- 230000004048 modification Effects 0.000 description 82

- 238000010586 diagram Methods 0.000 description 30

- 238000004519 manufacturing process Methods 0.000 description 27

- 229910052751 metal Inorganic materials 0.000 description 27

- 239000002184 metal Substances 0.000 description 27

- 238000001514 detection method Methods 0.000 description 23

- 230000000875 corresponding effect Effects 0.000 description 19

- 238000004891 communication Methods 0.000 description 17

- 238000005516 engineering process Methods 0.000 description 16

- 239000010949 copper Substances 0.000 description 13

- 230000003287 optical effect Effects 0.000 description 11

- 229910052782 aluminium Inorganic materials 0.000 description 10

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 10

- 230000004888 barrier function Effects 0.000 description 10

- 230000000694 effects Effects 0.000 description 9

- 238000002955 isolation Methods 0.000 description 9

- 239000004020 conductor Substances 0.000 description 8

- 238000002674 endoscopic surgery Methods 0.000 description 8

- 230000006870 function Effects 0.000 description 8

- 229910021332 silicide Inorganic materials 0.000 description 8

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 8

- 239000010936 titanium Substances 0.000 description 8

- 239000012535 impurity Substances 0.000 description 7

- 239000011159 matrix material Substances 0.000 description 7

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 6

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 6

- 230000005540 biological transmission Effects 0.000 description 6

- 239000000470 constituent Substances 0.000 description 6

- 229910052802 copper Inorganic materials 0.000 description 6

- 238000010030 laminating Methods 0.000 description 6

- 230000002093 peripheral effect Effects 0.000 description 6

- 229910052710 silicon Inorganic materials 0.000 description 6

- 239000010703 silicon Substances 0.000 description 6

- 239000007769 metal material Substances 0.000 description 5

- 230000000149 penetrating effect Effects 0.000 description 5

- 238000003860 storage Methods 0.000 description 5

- 239000000126 substance Substances 0.000 description 5

- 229910019001 CoSi Inorganic materials 0.000 description 4

- 229910005883 NiSi Inorganic materials 0.000 description 4

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 4

- 229910045601 alloy Inorganic materials 0.000 description 4

- 239000000956 alloy Substances 0.000 description 4

- 230000001276 controlling effect Effects 0.000 description 4

- 230000006866 deterioration Effects 0.000 description 4

- 238000005530 etching Methods 0.000 description 4

- 230000005284 excitation Effects 0.000 description 4

- 230000007246 mechanism Effects 0.000 description 4

- 238000000206 photolithography Methods 0.000 description 4

- 229910052715 tantalum Inorganic materials 0.000 description 4

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 4

- 229910052719 titanium Inorganic materials 0.000 description 4

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 4

- 229910052721 tungsten Inorganic materials 0.000 description 4

- 239000010937 tungsten Substances 0.000 description 4

- 208000005646 Pneumoperitoneum Diseases 0.000 description 3

- 230000008859 change Effects 0.000 description 3

- 239000007772 electrode material Substances 0.000 description 3

- 238000010336 energy treatment Methods 0.000 description 3

- 239000000203 mixture Substances 0.000 description 3

- 230000003647 oxidation Effects 0.000 description 3

- 238000007254 oxidation reaction Methods 0.000 description 3

- 230000001681 protective effect Effects 0.000 description 3

- 238000000926 separation method Methods 0.000 description 3

- 238000009825 accumulation Methods 0.000 description 2

- 230000009471 action Effects 0.000 description 2

- 210000004204 blood vessel Anatomy 0.000 description 2

- 239000003153 chemical reaction reagent Substances 0.000 description 2

- 238000005401 electroluminescence Methods 0.000 description 2

- MOFVSTNWEDAEEK-UHFFFAOYSA-M indocyanine green Chemical compound [Na+].[O-]S(=O)(=O)CCCCN1C2=CC=C3C=CC=CC3=C2C(C)(C)C1=CC=CC=CC=CC1=[N+](CCCCS([O-])(=O)=O)C2=CC=C(C=CC=C3)C3=C2C1(C)C MOFVSTNWEDAEEK-UHFFFAOYSA-M 0.000 description 2

- 229960004657 indocyanine green Drugs 0.000 description 2

- 238000009434 installation Methods 0.000 description 2

- 230000001678 irradiating effect Effects 0.000 description 2

- 230000003071 parasitic effect Effects 0.000 description 2

- 238000007747 plating Methods 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 238000004544 sputter deposition Methods 0.000 description 2

- 238000001356 surgical procedure Methods 0.000 description 2

- 230000002194 synthesizing effect Effects 0.000 description 2

- 240000004050 Pentaglottis sempervirens Species 0.000 description 1

- 235000004522 Pentaglottis sempervirens Nutrition 0.000 description 1

- 229910052581 Si3N4 Inorganic materials 0.000 description 1

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 1

- 230000001133 acceleration Effects 0.000 description 1

- 230000000740 bleeding effect Effects 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 238000002485 combustion reaction Methods 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 230000002596 correlated effect Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 239000000284 extract Substances 0.000 description 1

- 238000002073 fluorescence micrograph Methods 0.000 description 1

- 229910000449 hafnium oxide Inorganic materials 0.000 description 1

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 1

- 238000005286 illumination Methods 0.000 description 1

- 238000005304 joining Methods 0.000 description 1

- 230000031700 light absorption Effects 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 238000012423 maintenance Methods 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 239000003595 mist Substances 0.000 description 1

- 230000000116 mitigating effect Effects 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- 239000013307 optical fiber Substances 0.000 description 1

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 1

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 230000000750 progressive effect Effects 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- 238000005070 sampling Methods 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 239000002344 surface layer Substances 0.000 description 1

- 229910001936 tantalum oxide Inorganic materials 0.000 description 1

- 230000002123 temporal effect Effects 0.000 description 1

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 1

- 230000000007 visual effect Effects 0.000 description 1

- 229910052845 zircon Inorganic materials 0.000 description 1

- GFQYVLUOOAAOGM-UHFFFAOYSA-N zirconium(iv) silicate Chemical compound [Zr+4].[O-][Si]([O-])([O-])[O-] GFQYVLUOOAAOGM-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14636—Interconnect structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3205—Deposition of non-insulating-, e.g. conductive- or resistive-, layers on insulating layers; After-treatment of these layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/08—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind

- H01L27/085—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only

- H01L27/088—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14634—Assemblies, i.e. Hybrid structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14683—Processes or apparatus peculiar to the manufacture or treatment of these devices or parts thereof

- H01L27/1469—Assemblies, i.e. hybrid integration

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

Definitions

- the present disclosure relates to, for example, a semiconductor device having a gap between wirings and an imaging device including the semiconductor device.

- Patent Documents 1 and 2 disclose semiconductor devices in which a gap (air gap) is formed between wirings to reduce the capacitance between the wirings.

- the semiconductor device of one embodiment of the present disclosure is provided on a first wiring layer having a plurality of first wirings extending in one direction and a first wiring layer, and a gap is provided in at least a part between the plurality of wirings. Is formed, and a first insulating layer having a laminated region in which a first insulating film and a second insulating film made of different materials are laminated above the voids is laminated.

- the first semiconductor substrate has a first substrate having sensor pixels for photoelectric conversion

- the second semiconductor substrate has a pixel signal based on the charge output from the sensor pixels. It has a readout circuit for outputting the above, has a multilayer wiring layer laminated on the second semiconductor substrate, and has a second substrate laminated on the first substrate. It has the configuration of a semiconductor device of the form.

- the second imaging device includes a first semiconductor substrate having a sensor pixel that performs photoelectric conversion and a readout circuit that outputs a pixel signal based on the charge output from the sensor pixel, and a first semiconductor substrate.

- the first image pickup device of one embodiment, and the second image pickup device of one embodiment of the present disclosure on a first wiring layer having a plurality of first wires extending in one direction. And a first insulating layer forming a space between the plurality of wirings.

- the first insulating layer has a stacked region above the void in which a first insulating film and a second insulating film made of different materials are stacked. This reduces variation in the film thickness of the first insulating layer within the surface.

- FIG. 6 is a diagram illustrating an example of a manufacturing process of the semiconductor device illustrated in FIG. 1. It is a figure which shows an example of the manufacturing process following FIG. 4A. It is a figure which shows an example of the manufacturing process following FIG. 4B. It is a figure showing an example of the manufacturing process following FIG. 4C. It is a figure showing an example of the manufacturing process following FIG. 4D.

- FIG. 4E It is a figure which shows an example of the manufacturing process following FIG. 4E. It is a figure showing an example of the manufacturing process following FIG. 4F. It is a figure following FIG. 4G which shows an example of the manufacturing process of the semiconductor device shown in FIG. It is a figure showing an example of the manufacturing process following FIG. 5A. It is a figure which shows an example of the manufacturing process following FIG. 5B. It is a figure which shows an example of the cross-sectional structure in the vertical direction of the image pickup apparatus which concerns on embodiment of this disclosure. It is a figure which shows an example of the schematic structure of the image pickup apparatus shown in FIG. It is a figure which shows an example of the sensor pixel and the reading circuit shown in FIG.

- FIG. 7 is a diagram illustrating an example of a horizontal cross-sectional configuration of the imaging device illustrated in FIG. 6. It is a figure which shows an example of the cross-sectional structure in the horizontal direction of the image pickup apparatus shown in FIG. It is a figure which shows an example of the wiring layout in the horizontal plane of the image pickup apparatus shown in FIG.

- FIG. 7 is a diagram showing an example of a wiring layout in a horizontal plane of the image pickup apparatus shown in FIG. 6.

- FIG. 7 is a diagram showing an example of a wiring layout in a horizontal plane of the image pickup apparatus shown in FIG. 6.

- 7A and 7B are diagrams illustrating an example of a manufacturing process of the imaging device illustrated in FIG. 6. It is a figure which shows an example of the manufacturing process following FIG. 19A. It is a figure showing an example of the manufacturing process following FIG. 19B. It is a figure showing an example of the manufacturing process following FIG. 19C. It is a figure which shows an example of the manufacturing process following FIG. 19D.

- FIG. 19E It is a figure showing an example of the manufacturing process following FIG. 19E. It is a figure showing an example of the manufacturing process following FIG. 19F. It is a figure which shows an example of the manufacturing process of the semiconductor device which is a reference example. It is a figure showing an example of the manufacturing process following FIG. 20A. It is a figure explaining the main part of the manufacturing process of the semiconductor device of this embodiment. It is a figure which shows an example of the manufacturing revision following FIG. 21A. It is a figure which shows an example of the cross-sectional structure in the vertical direction of the image pickup apparatus which concerns on the modification 1 of this disclosure.

- FIG. 16 is a diagram illustrating an example of a vertical cross-sectional configuration of an imaging device according to a second modification of the present disclosure.

- FIG. 16 is a diagram illustrating an example of a horizontal cross-sectional configuration of an imaging device according to Modification 4 of the present disclosure. It is a figure which shows an example of the cross-sectional structure in the horizontal direction of the image pickup apparatus which concerns on the modification 5 of this disclosure.

- FIG. 16 is a diagram illustrating an example of a horizontal cross-sectional configuration of an imaging device according to Modification 6 of the present disclosure.

- FIG. 16 is a diagram illustrating another example of the horizontal cross-sectional configuration of the imaging device according to the modified example 6 of the present disclosure.

- FIG. 16 is a diagram illustrating another example of the horizontal cross-sectional configuration of the imaging device according to the modified example 6 of the present disclosure.

- FIG. 16 is a diagram illustrating an example of a circuit configuration of an image pickup device in an image pickup device according to a modified example 7 of the present disclosure.

- FIG. 32 is a diagram illustrating an example in which the imaging device of FIG. 31 according to Modification Example 8 of the present disclosure is configured by stacking three substrates. It is a figure which shows the example which formed the logic circuit which concerns on the modification 9 of this disclosure separately into the substrate which provided the sensor pixel, and the substrate which provided the readout circuit.

- FIG. 16 is a diagram illustrating an example in which a logic circuit according to Modification Example 10 of the present disclosure is formed on a third substrate. It is a figure which shows an example of the schematic structure of the image pickup system provided with the image pickup apparatus which concerns on the said Embodiment and the modification. It is a figure which shows an example of the imaging procedure in the imaging system of FIG. 35. It is a figure which shows the outline

- Embodiment an example of a semiconductor device having a stacked region in which insulating films made of different materials are stacked above a void provided between a plurality of wires extending in one direction

- Configuration of semiconductor device 1-2 Manufacturing method of semiconductor device 1-3.

- Configuration of imaging device 1-4 Manufacturing method of imaging device 1-5.

- Modification 1 (Example using flat TG) 2-2.

- Deformation example 2 (Example using Cu-Cu bonding at the outer edge of the panel) 2-3.

- Modification 3 (Example in which an offset is provided between the sensor pixel and the readout circuit) 2-4.

- Modification 4 (Example in which a silicon substrate provided with a readout circuit has an island shape) 2-5.

- Modification 5 (Example in which a silicon substrate provided with a readout circuit has an island shape) 2-6.

- Modification 6 (Example in which FD is shared by four sensor pixels) 2-7.

- Modification 7 (example in which the column signal processing circuit is configured by a general column ADC circuit) 2-8.

- Modification 8 (Example in which the imaging device is configured by laminating three substrates) 2-9.

- Modification 9 (Example in which logic circuits are provided on the first and second boards) 2-10.

- Modification 10 (Example in which a logic circuit is provided on a third substrate) 3.

- Application example 4. Application example

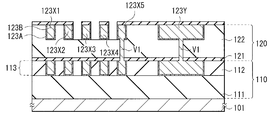

- FIG. 1 illustrates an example of a vertical cross-sectional configuration of a semiconductor device (semiconductor device 100) according to an embodiment of the present disclosure.

- FIG. 2 shows an example of a horizontal sectional configuration of the entire semiconductor device 100 shown in FIG.

- the semiconductor device 100 has, for example, a multilayer wiring structure in which a plurality of wiring layers are stacked, and is applicable to, for example, the imaging device 1 described later.

- the wiring layer 123 having a plurality of wirings (for example, wirings 123X1 to 123X5 and wirings 123Y) extending in one direction (for example, the Z-axis direction), for example, wirings 123X1 to 123X5.

- the insulating layer 132 that forms a gap G is laminated between them.

- the insulating layer 132 has a laminated region 100Y in which an insulating film 132A and an insulating film 132B made of different materials are laminated on a part of the plane, and the laminated region 100Y is provided between the wiring 123X1 and the wiring 123X5. It is provided above the formed gap G.

- the semiconductor device 100 has a configuration in which the first layer 110, the second layer 120, and the third layer 130 are laminated in this order on a support substrate 101 made of, for example, a silicon substrate.

- the first layer 110 and the second layer 120 have a wiring layer 113 and a wiring layer 123, each of which includes a plurality of wirings.

- the insulating layer 111 and the insulating layer 112 are laminated in this order, and the insulating layer 112 is formed by embedding a wiring layer 113 composed of a plurality of wirings (for example, wirings 113X1 to 113X5 and wirings 113Y).

- the insulating layer 111 is formed using, for example, silicon oxide (SiO x ) or silicon nitride (SiN x ).

- the insulating layer 112 is formed using, for example, a low dielectric constant material (Low-k material) having a relative dielectric constant (k) of 2.9 or less.

- the material of the insulating layer 112 include SiOC and the like.

- the wiring layer 113 is composed of, for example, a plurality of wirings extending in one direction, and is composed of, for example, wirings 113X1 to 113X5 and wirings 113Y extending in the Z-axis direction.

- the wirings 113X1 to 113X5 and the wiring 113Y are, for example, embedded in the opening 112H provided in the insulating layer 112, and for example, the barrier metal 113A and the metal for embedding the opening 112H formed in the side surface and the bottom surface of the opening 112H.

- the film 113B examples of the material of the barrier metal 113A include simple substances of Ti (titanium) or Ta (tantalum), alloys thereof, and the like.

- Examples of the material of the metal film 113B include a metal material mainly composed of a low resistance metal such as Cu (copper), W (tungsten) or aluminum (Al).

- an insulating layer 121 and an insulating layer 122 are laminated in this order, and a wiring layer 123 including a plurality of wirings (for example, wiring 123X1 to wiring 123X5 and wiring 123Y) is embedded and formed in the insulating layer 122.

- the wiring layer 123 corresponds to a specific but not limitative example of “first wiring layer” of the present disclosure.

- the insulating layer 121 is formed by using, for example, SiCN.

- the insulating layer 122 is formed by using, for example, a Low-k material having a relative permittivity (k) of 2.9 or less. Specifically, examples of the material of the insulating layer 122 include SiOC.

- the wiring layer 123 is composed of, for example, a plurality of wirings extending in one direction, and is composed of, for example, wirings 123X1 to 123X5 and wirings 123Y extending in the Z-axis direction, similarly to wirings 113X1 to 113X5 and wirings 113Y. ..

- the wirings 123X1 to 123X5 and the wiring 123Y are, for example, embedded in the opening 122H1 provided in the insulating layer 122, and for example, the barrier metal 123A and the metal for embedding the opening 122H1 formed in the side surface and the bottom surface of the opening 122H1. It is composed of a film 123B.

- the material of the barrier metal 123A include simple substances of Ti (titanium) or Ta (tantalum), alloys thereof, and the like.

- Examples of the material of the metal film 123B include a metal material mainly composed of a low resistance metal such as Cu (copper), W (tungsten) or aluminum (Al).

- Wiring 123X1 to 123X5 and wiring 123Y and wiring 113X1 to 113X5 and wiring 113Y of the wiring layer 113 are respectively laminated in the Y-axis direction, and are electrically stacked at a predetermined position via, for example, via V1. It is connected.

- the third layer 130 has an insulating layer 131 and an insulating layer 132 stacked in this order.

- the insulating layer 131 is formed by using, for example, SiCN.

- the insulating layer 122 constituting the second layer 120 is provided between the wirings of the wiring dense region 100X (for example, between the wirings 123X2 and 123X3, between the wirings 123X3 and 123X4, and the wirings 123X4 and wirings). Between 123X5) has an opening 122H2.

- the insulating layer 131 is continuously provided, for example, on the upper surfaces of the insulating layer 122 and the wirings 123X1 to 123X5 and the wiring 123Y, and the side surfaces and the bottom surface of the opening 122H2.

- the insulating layer 132 is provided on the insulating layer 131.

- the opening 122H2 provided between the wirings of the wiring dense region 100X of the second layer 120 is closed by the insulating layer 132.

- the gap G is formed between the wirings of the second layer 120 (for example, between the wiring 123X2 and the wiring 123X3, between the wiring 123X3 and the wiring 123X4, between the wiring 123X4 and the wiring 123X5).

- the opening 122H2 is formed so as to avoid the via V1 that electrically connects the wiring 113X1 to 113X5 and the wiring 123X1 to 123X5, that is, the region where the gap G is formed (the gap forming region 100Z). ) Is provided in the unformed region of the via V1 in the wiring dense region 100X in which the wirings 123X1 to 123X5 are formed in parallel, as shown in FIG.

- the insulating layer 132 has an insulating film 132 ⁇ /b>A and an insulating film 132 ⁇ /b>B that are partially made of different materials and are stacked in the plane.

- the insulating layer 132 corresponds to a specific example of the "first insulating layer" of the present disclosure, and the insulating film 132A and the insulating film 132B are the "first insulating film” and the "second insulating film” of the present disclosure, respectively.

- the insulating film 132A is formed of, for example, a Low-k material having a relative dielectric constant (k) of 2.9 or less.

- examples of the material of the insulating film 132A include SiOC and the like.

- the insulating film 132B As a material of the insulating film 132B, for example, a material having a higher polishing rate than that of the insulating film 132A is preferably used. Examples of such a material include silicon oxide (SiO x ), SiOC, SiOF or SiON.

- the insulating film 132B may be a single layer film made of any one of the above materials, or may be formed as a laminated film made of two or more kinds. As a result, as will be described in detail later, a part of the insulating film 132A enters along the side surface of the opening 122H2 so as to close the opening 122H2 provided between the wirings of the second layer 120, thereby above the opening 122H2. In other words, the step of the insulating film 132A formed above the void forming region 100Z is filled with the insulating film 132B. Therefore, the insulating layer 132 having a flat surface can be obtained.

- the third layer 130 may be formed by embedding a wiring layer composed of a plurality of wirings on the surface of the insulating layer 132.

- FIG. 3 illustrates another example of the semiconductor device 100 of the present disclosure.

- a wiring layer 133 composed of a plurality of wirings (for example, wirings 133X1 to 133X5 and wirings 133Y) is embedded in the insulating layer 132 constituting the third layer 130, and the third layer 130 is formed.

- a fourth layer 140 having a wiring layer 143 is further laminated on the layer 130.

- the wiring layer 133 is composed of, for example, a plurality of wirings extending in one direction, and is composed of, for example, wirings 133X1 to 133X5 and wirings 133Y extending in the Z-axis direction, similarly to wirings 113X1 to 113X5 and wirings 113Y. There is.

- the wiring layer 133 corresponds to a specific but not limitative example of “second wiring layer” of the present disclosure.

- At least a part of the wiring 133X1 to the wiring 133X5 is formed in, for example, a laminated region 100Y in which the above-mentioned insulating film 132A and the insulating film 132B are laminated.

- the wiring 133X1 to the wiring 133X5 and the wiring 133Y are, for example, embedded in the opening 132H provided in the insulating layer 132, and for example, the metal for embedding the barrier metal 133A and the opening 122H1 formed on the side surface and the bottom surface of the opening 132H.

- the film 133B examples of the material of the barrier metal 133A include simple substances of Ti (titanium) or Ta (tantalum), alloys thereof, and the like.

- Examples of the material of the metal film 133B include a metal material mainly composed of a low resistance metal such as Cu (copper), W (tungsten) or aluminum (Al).

- the wiring 133Y and the wiring 123Y of the wiring layer 123 are electrically connected to each other via, for example, via V2.

- the insulating layer 141 and the insulating layer 142 are laminated in this order, and the wiring layer 143 composed of a plurality of wirings (for example, wiring 143X1 to wiring 143X5 and wiring 143Y) is embedded in the insulating layer 142.

- the insulating layer 141 is formed using, for example, SiCN.

- the insulating layer 142 is formed by using, for example, a Low-k material having a relative permittivity (k) of 2.9 or less. Specifically, examples of the material of the insulating layer 142 include SiOC and the like.

- the wiring layer 143 is composed of, for example, a plurality of wirings extending in one direction, and is composed of, for example, wirings 143X1 to 143X5 and wirings 143Y extending in the Z-axis direction, similarly to wirings 113X1 to 113X5 and wirings 113Y. There is.

- Wiring 143X1 to Wiring 143X5 and Wiring 143Y are, for example, embedded in an opening 142H provided in an insulating layer 142, and for example, a metal for embedding a barrier metal 143A and an opening 142H formed on the side surface and the bottom surface of the opening 142H. It is composed of a film 143B.

- the material of the barrier metal 143A include simple substances of Ti (titanium) or Ta (tantalum), alloys thereof, and the like.

- Examples of the material of the metal film 143B include a metal material mainly composed of a low resistance metal such as Cu (copper), W (tungsten) or aluminum (Al).

- the wiring 143Y and the wiring 133Y of the wiring layer 133 are electrically connected to each other, for example, via the via V3.

- the insulating layer 111 and the insulating layer 112 are formed in order on the support substrate 101, and then the wiring layer 113 composed of the wirings 113X1 to 113X5 and the wirings 113Y is embedded in the insulating layer 112 to form the first layer 110. Then, the insulating layer 121 and the insulating layer 122 are sequentially formed on the first layer 110. Next, as shown in FIG. 4A, the insulating layer 122 is patterned by, for example, photolithography and etching to form an opening 122H1.

- a barrier metal 123A is formed on the side surface and the bottom surface of the opening 122H1 by sputtering, and then a metal film 123B is formed in the opening 122H1 by plating, and then the surface surface.

- the second layer 120 in which the wirings 123X1 to 123X5 and the wirings 123Y are embedded is formed on the surface of the insulating layer 122.

- the SiCN film 131A and the insulating layer 122 are patterned by, for example, photolithography and etching.

- An opening 122H2 is formed between the wiring 123X2 and the wiring 123X3, between the wiring 123X3 and the wiring 123X4, and between the wiring 123X4 and the wiring 123X5.

- an SiCN film is formed again on the second layer 120 and on the side surface and the bottom surface of the opening 122H2 by using, for example, CVD to form an insulating layer 131 having a film thickness of, for example, 30 nm to 50 nm.

- an insulating film 132A having a film thickness of, for example, 400 nm to 500 nm, which is made of, for example, SiOC, is formed on the entire surface of the second layer 120 by using, for example, CVD.

- the opening 122H2 is closed, and a gap G is formed between the wiring 123X2 and the wiring 123X3, between the wiring 123X3 and the wiring 123X4, and between the wiring 123X4 and the wiring 123X5.

- the insulating film 132B is polished by using, for example, a CMP (Chemical Mechanical Polishing) method.

- the surface of the insulating layer 132 is flattened, and for example, gaps G formed between the wiring 123X2 and the wiring 123X3, between the wiring 123X3 and the wiring 123X4, and between the wiring 123X4 and the wiring 123X5, respectively.

- a laminated region 100Y in which the insulating film 132A and the insulating film 132B are laminated is formed.

- the semiconductor device 100 shown in FIG. 1 is completed.

- the third layer 130 and the fourth layer 140 having the wiring layer 133 and the wiring layer 143 are formed in order on the second layer 120 as in the semiconductor device 100 shown in FIG. 3, for example, It is manufactured as follows.

- the insulating layer 132 is patterned by, for example, photolithography and etching to form an opening 132H.

- sputtering is used to form a barrier metal 133A on the side surface and the bottom surface of the opening 132H, and then, for example, plating is used to form a metal film 133B inside the opening 132H, and then to the surface.

- plating is used to form a metal film 133B inside the opening 132H, and then to the surface.

- the wiring layer 133 including the wirings 133X1 to 133X5 and the wiring 133Y is formed on the surface of the insulating layer 132.

- a SiCN film 141 having a film thickness of 30 nm to 50 nm, for example, 141 is formed on the third layer 130 by, for example, CVD, and then, for example, SiOC (an example of a material) is used.

- An insulating layer 142 having a film thickness of, for example, 400 nm to 500 nm is formed.

- the insulating layer 142 is patterned by photolithography and etching to form the opening 142H.

- the wiring layer 143 is formed by using the same method as the wiring layer 133.

- FIG. 6 illustrates an example of a vertical cross-sectional configuration of the imaging device (imaging device 1) according to the embodiment of the present disclosure.

- FIG. 7 shows an example of a schematic configuration of the image pickup apparatus 1 shown in FIG.

- the image pickup apparatus 1 has a first substrate 10 having a sensor pixel 12 that performs photoelectric conversion on the semiconductor substrate 11, and a readout circuit 22 that outputs an image signal based on the charge output from the sensor pixel 12 on the semiconductor substrate 21. It is an image pickup apparatus having a three-dimensional structure in which a second substrate 20 is laminated.

- the multilayer wiring structure described in the semiconductor device 100 is applied to the wiring layer 56 stacked on the semiconductor substrate 21, for example.

- the image pickup apparatus 1 is a stack of three substrates (first substrate 10, second substrate 20, and third substrate 30) in this order.

- the first substrate 10 includes the semiconductor substrate 11 and the plurality of sensor pixels 12 that perform photoelectric conversion.

- the semiconductor substrate 11 corresponds to a specific but not limitative example of “first semiconductor substrate” of the present disclosure.

- the plurality of sensor pixels 12 are arranged in a matrix in the pixel region 13 of the first substrate 10.

- the second substrate 20 includes, on the semiconductor substrate 21, one reading circuit 22 that outputs a pixel signal based on the charges output from the sensor pixels 12 for each of the four sensor pixels 12.

- the semiconductor substrate 21 corresponds to a specific but not limitative example of “second semiconductor substrate” of the present disclosure.

- the second substrate 20 has a plurality of pixel drive lines 23 extending in the row direction and a plurality of vertical signal lines 24 extending in the column direction.

- the third substrate 30 includes a semiconductor substrate 31 and a logic circuit 32 that processes pixel signals.

- the semiconductor substrate 31 corresponds to a specific but not limitative example of “third semiconductor substrate” of the present disclosure.

- the logic circuit 32 has, for example, a vertical drive circuit 33, a column signal processing circuit 34, a horizontal drive circuit 35, and a system control circuit 36.

- the logic circuit 32 (specifically, the horizontal drive circuit 35) outputs the output voltage Vout for each sensor pixel 12 to the outside.

- a low resistance region made of silicide formed by using a salicide (Self Aligned Silicide) process such as CoSi 2 or NiSi is formed on the surface of the impurity diffusion region in contact with the source electrode and the drain electrode. May be.

- the vertical drive circuit 33 sequentially selects a plurality of sensor pixels 12 row by row, for example.

- the column signal processing circuit 34 performs, for example, Correlated Double Sampling (CDS) processing on the pixel signals output from each sensor pixel 12 in the row selected by the vertical drive circuit 33.

- CDS Correlated Double Sampling

- the column signal processing circuit 34 extracts the signal level of the pixel signal by performing CDS processing, for example, and holds pixel data according to the amount of light received by each sensor pixel 12.

- the horizontal drive circuit 35 sequentially outputs the pixel data held in the column signal processing circuit 34 to the outside, for example.

- the system control circuit 36 controls, for example, the drive of each block (vertical drive circuit 33, column signal processing circuit 34, and horizontal drive circuit 35) in the logic circuit 32.

- FIG. 8 shows an example of the sensor pixel 12 and the readout circuit 22.

- shared means that the outputs of the four sensor pixels 12 are input to the common readout circuit 22.

- Each sensor pixel 12 has common constituent elements.

- identification numbers (1, 2, 3, 4) are given to the end of the reference numerals of the constituent elements of each sensor pixel 12.

- an identification number is added to the end of the code of the component of each sensor pixel 12, but the components of each sensor pixel 12 are distinguished from each other.

- the identification number at the end of the reference numeral of the constituent element of each sensor pixel 12 is omitted.

- Each sensor pixel 12 is, for example, a floating diffusion that temporarily holds the electric charge output from the photodiode PD, the transfer transistor TR electrically connected to the photodiode PD, and the electric charge output from the photodiode PD via the transfer transistor TR. It has an FD.

- the photodiode PD corresponds to a specific example of the "photoelectric conversion element" of the present disclosure.

- the photodiode PD performs photoelectric conversion to generate an electric charge according to the amount of received light.

- the cathode of the photodiode PD is electrically connected to the source of the transfer transistor TR, and the anode of the photodiode PD is electrically connected to the reference potential line (eg, ground).

- the drain of the transfer transistor TR is electrically connected to the floating diffusion FD, and the gate of the transfer transistor TR is electrically connected to the pixel drive line 23.

- the transfer transistor TR is, for example, a CMOS (Complementary Metal Oxide Semiconductor) transistor.

- the floating diffusion FDs of the sensor pixels 12 sharing one read circuit 22 are electrically connected to each other and are electrically connected to the input end of the common read circuit 22.

- the read circuit 22 has, for example, a reset transistor RST, a selection transistor SEL, and an amplification transistor AMP.

- the selection transistor SEL may be omitted if necessary.

- the source of the reset transistor RST (the input end of the read circuit 22) is electrically connected to the floating diffusion FD, and the drain of the reset transistor RST is electrically connected to the power line VDD and the drain of the amplification transistor AMP.

- the gate of the reset transistor RST is electrically connected to the pixel drive line 23.

- the source of the amplification transistor AMP is electrically connected to the drain of the selection transistor SEL, and the gate of the amplification transistor AMP is electrically connected to the source of the reset transistor RST.

- the source of the selection transistor SEL (the output end of the readout circuit 22) is electrically connected to the vertical signal line 24, and the gate of the selection transistor SEL is electrically connected to the pixel drive line 23.

- the transfer transistor TR transfers the charge of the photodiode PD to the floating diffusion FD when the transfer transistor TR is turned on.

- the gate of the transfer transistor TR (transfer gate TG) extends from the surface of the semiconductor substrate 11 to a depth that penetrates the p-well 42 and reaches the PD 41.

- the reset transistor RST resets the potential of the floating diffusion FD to a predetermined potential.

- the reset transistor RST is turned on, the potential of the floating diffusion FD is reset to the potential of the power supply line VDD.

- the selection transistor SEL controls the output timing of the pixel signal from the readout circuit 22.

- the amplification transistor AMP generates, as a pixel signal, a signal having a voltage corresponding to the level of the charge held in the floating diffusion FD.

- the amplification transistor AMP constitutes a source follower type amplifier, and outputs a pixel signal having a voltage corresponding to the level of electric charge generated by the photodiode PD.

- the selection transistor SEL When the selection transistor SEL is turned on, the amplification transistor AMP amplifies the potential of the floating diffusion FD and outputs a voltage corresponding to the potential to the column signal processing circuit 34 via the vertical signal line 24.

- the reset transistor RST, the amplification transistor AMP, and the selection transistor SEL are CMOS transistors, for example.

- the selection transistor SEL may be provided between the power supply line VDD and the amplification transistor AMP.

- the drain of the reset transistor RST is electrically connected to the power supply line VDD and the drain of the selection transistor SEL.

- the source of the selection transistor SEL is electrically connected to the drain of the amplification transistor AMP, and the gate of the selection transistor SEL is electrically connected to the pixel drive line 23.

- the source of the amplification transistor AMP (the output end of the readout circuit 22) is electrically connected to the vertical signal line 24, and the gate of the amplification transistor AMP is electrically connected to the source of the reset transistor RST.

- the FD transfer transistor FDG may be provided between the source of the reset transistor RST and the gate of the amplification transistor AMP.

- FD transfer transistor FDG is used when switching the conversion efficiency.

- FIG. 12 shows an example of a connection mode between the plurality of readout circuits 22 and the plurality of vertical signal lines 24.

- the plurality of read circuits 22 are arranged side by side in the extending direction (for example, the column direction) of the vertical signal lines 24, even if one of the plurality of vertical signal lines 24 is assigned to each read circuit 22. Good.

- the four vertical signal lines 24 are the read circuits 22. It may be assigned one for each.

- an identification number (1, 2, 3, 4) is added to the end of the code of each vertical signal line 24.

- the image pickup apparatus 1 has a configuration in which the first substrate 10, the second substrate 20, and the third substrate 30 are laminated in this order, and further, on the back surface (light incident surface) side of the first substrate 10. , A color filter 40 and a light receiving lens 50.

- the color filter 40 and the light receiving lens 50 are provided one by one for each sensor pixel 12, for example. That is, the imaging device 1 is a backside illumination type imaging device.

- the first substrate 10 is configured by laminating an insulating layer 46 on the surface (surface 11S1) of the semiconductor substrate 11.

- the first substrate 10 has an insulating layer 46 as a part of the interlayer insulating film 51.

- the insulating layer 46 is provided between the semiconductor substrate 11 and the semiconductor substrate 21 described later.

- the semiconductor substrate 11 is composed of a silicon substrate.

- the semiconductor substrate 11 has, for example, a p-well 42 in a part of the surface or in the vicinity thereof, and in a region other than the p-well 42 (a region deeper than the p-well 42), a conductive type PD 41 different from the p-well 42. have.

- the p well 42 is composed of a p-type semiconductor region.

- the PD 41 is composed of a semiconductor region of a conductivity type (specifically, n type) different from that of the p well 42.

- the semiconductor substrate 11 has a floating diffusion FD in the p-well 42 as a conductive type (specifically, n-type) semiconductor region different from the p-well 42.

- the first substrate 10 has a photodiode PD, a transfer transistor TR, and a floating diffusion FD for each sensor pixel 12.

- the first substrate 10 has a configuration in which a transfer transistor TR and a floating diffusion FD are provided on a part of the surface 11S1 side (the side opposite to the light incident surface side, the second substrate 20 side) of the semiconductor substrate 11. ..

- the first substrate 10 has an element isolation portion 43 that isolates each sensor pixel 12.

- the element isolation portion 43 is formed to extend in the normal direction of the semiconductor substrate 11 (direction perpendicular to the surface of the semiconductor substrate 11).

- the element isolation part 43 is provided between two sensor pixels 12 adjacent to each other.

- the element separating unit 43 electrically separates the sensor pixels 12 adjacent to each other.

- the element isolation portion 43 is made of, for example, silicon oxide.

- the element isolation portion 43 penetrates the semiconductor substrate 11, for example.

- the first substrate 10 further has, for example, a p-well layer 44 which is a side surface of the element separating portion 43 and is in contact with the surface on the photodiode PD side.

- the p well layer 44 is composed of a semiconductor region of a conductivity type (specifically, p type) different from that of the photodiode PD.

- the first substrate 10 further has, for example, a fixed charge film 45 in contact with the back surface (surface 11S2, other surface) of the semiconductor substrate 11.

- the fixed charge film 45 is negatively charged in order to suppress the generation of dark current due to the interface state on the light receiving surface side of the semiconductor substrate 11.

- the fixed charge film 45 is formed of, for example, an insulating film having a negative fixed charge.

- examples of the material for such an insulating film include hafnium oxide, zircon oxide, aluminum oxide, titanium oxide, and tantalum oxide.

- An electric field induced by the fixed charge film 45 forms a hole accumulation layer at the interface of the semiconductor substrate 11 on the light receiving surface side.

- the hole accumulation layer suppresses the generation of electrons from the interface.

- the color filter 40 is provided on the back surface side of the semiconductor substrate 11.

- the color filter 40 is provided, for example, in contact with the fixed charge film 45, and is provided at a position facing the sensor pixel 12 via the fixed charge film 45.

- the light receiving lens 50 is provided, for example, in contact with the color filter 40, and is provided at a position facing the sensor pixel 12 via the color filter 40 and the fixed charge film 45.

- the second substrate 20 is configured by laminating the insulating layer 52 on the semiconductor substrate 21.

- the second substrate 20 has the insulating layer 52 as a part of the interlayer insulating film 51.

- the insulating layer 52 is provided between the semiconductor substrate 21 and the semiconductor substrate 31.

- the semiconductor substrate 21 is composed of a silicon substrate.

- the second substrate 20 has one readout circuit 22 for every four sensor pixels 12.

- the second substrate 20 has a configuration in which the read circuit 22 is provided on a part of the front surface of the semiconductor substrate 21 (the surface 21S1 facing the third substrate 30, the one surface).

- the second substrate 20 is attached to the first substrate 10 with the back surface (surface 21S2) of the semiconductor substrate 21 facing the front surface (surface 11S1) of the semiconductor substrate 11.

- the second substrate 20 is bonded to the first substrate 10 by face-to-back.

- the second substrate 20 further has an insulating layer 53 penetrating the semiconductor substrate 21 in the same layer as the semiconductor substrate 21.

- the second substrate 20 has an insulating layer 53 as a part of the interlayer insulating film 51.

- the insulating layer 53 is provided so as to cover the side surface of the through wiring 54 described later.

- the laminate composed of the first substrate 10 and the second substrate 20 has an interlayer insulating film 51 and a through wiring 54 provided in the interlayer insulating film 51.

- the through wiring 54 corresponds to a specific example of the "first through wiring" of the present disclosure.

- the stacked body has one through wiring 54 for each sensor pixel 12.

- the through wiring 54 extends in the normal direction of the semiconductor substrate 21, and is provided so as to penetrate the portion of the interlayer insulating film 51 including the insulating layer 53.

- the first substrate 10 and the second substrate 20 are electrically connected to each other by a through wiring 54.

- the through wiring 54 is electrically connected to the floating diffusion FD and a connection wiring 55 described later.

- the stacked body including the first substrate 10 and the second substrate 20 further has through wirings 47 and 48 (see FIG. 13 described later) provided in the interlayer insulating film 51.

- the through wirings 47 and 48 correspond to a specific but not limitative example of “second through wiring” in the present disclosure.

- the laminated body has one through wiring 47 and one through wiring 48 for each sensor pixel 12.

- the through wirings 47 and 48 extend in the normal direction of the semiconductor substrate 21, respectively, and are provided so as to penetrate the portion of the interlayer insulating film 51 including the insulating layer 53.

- the first substrate 10 and the second substrate 20 are electrically connected to each other by through wirings 47 and 48.

- the through wiring 47 is electrically connected to the p well 42 of the semiconductor substrate 11 and the wiring in the second substrate 20.

- the through wiring 48 is electrically connected to the transfer gate TG and the pixel drive line 23.

- the second substrate 20 has, for example, a plurality of connecting portions 59 electrically connected to the readout circuit 22 and the semiconductor substrate 21 in the insulating layer 52.

- the second substrate 20 further has, for example, a wiring layer 56 on the insulating layer 52.

- the wiring layer 56 has, for example, an insulating layer 57, a plurality of pixel drive lines 23 provided in the insulating layer 57, and a plurality of vertical signal lines 24.

- the plurality of pixel drive lines 23 correspond to the wirings 113X1 to 113X5 in the semiconductor device 100

- the plurality of vertical signal lines 24 correspond to the wirings 123X1 to 123X5 in the semiconductor device 100.

- a gap G as shown in FIG.

- insulating layer 57 between the wirings of the plurality of vertical signal lines 24. Further, in the insulating layer 57, for example, a laminated region in which insulating films (insulating films 132A and 132B in FIG. 1) made of different materials are laminated on a part of the surface serving as a joint surface with the wiring layer 62 described later is provided. Have. This laminated region is provided between a plurality of pad electrodes 58 described later in FIG. 6, for example. The plurality of pad electrodes 58 correspond to, for example, the wirings 133X1 to 133X5 in the semiconductor device 100.

- the wiring layer 56 further has, for example, a plurality of connection wirings 55 in the insulating layer 57, one for each of the four sensor pixels 12.

- the connection wiring 55 electrically connects each through wiring 54 electrically connected to the floating diffusion FD included in the four sensor pixels 12 sharing the read circuit 22 to each other.

- the total number of the through wirings 54 and 48 is larger than the total number of the sensor pixels 12 included in the first substrate 10, and is twice the total number of the sensor pixels 12 included in the first substrate 10.

- the total number of the through wirings 54, 48, 47 is larger than the total number of the sensor pixels 12 included in the first substrate 10, and is three times the total number of the sensor pixels 12 included in the first substrate 10.

- the wiring layer 56 further has, for example, a plurality of pad electrodes 58 in the insulating layer 57.

- Each pad electrode 58 is made of, for example, a metal such as Cu (copper) or Al (aluminum).

- Each pad electrode 58 is exposed on the surface of the wiring layer 56.

- Each pad electrode 58 is used for electrical connection between the second substrate 20 and the third substrate 30 and for bonding the second substrate 20 and the third substrate 30.

- the plurality of pad electrodes 58 are provided, for example, one for each of the pixel drive line 23 and the vertical signal line 24.

- the total number of pad electrodes 58 (or the total number of bonds between the pad electrodes 58 and the pad electrodes 64 (described later) is smaller than the total number of sensor pixels 12 included in the first substrate 10 ).

- the third substrate 30 is configured by, for example, laminating an interlayer insulating film 61 on a semiconductor substrate 31. As will be described later, the third substrate 30 is attached to the second substrate 20 with the surfaces on the front side facing each other. Therefore, when explaining the configuration inside the third substrate 30, the upper and lower parts will be described. , It is the opposite of the vertical direction in the drawing.

- the semiconductor substrate 31 is composed of a silicon substrate.

- the third substrate 30 has a structure in which a logic circuit 32 is provided on a part of the front surface (face 31S1) of the semiconductor substrate 31.

- the third substrate 30 further has, for example, a wiring layer 62 on the interlayer insulating film 61.

- the wiring layer 62 has, for example, an insulating layer 63 and a plurality of pad electrodes 64 provided in the insulating layer 63.

- the plurality of pad electrodes 64 are electrically connected to the logic circuit 32.

- Each pad electrode 64 is formed of Cu (copper), for example.

- Each pad electrode 64 is exposed on the surface of the wiring layer 62.

- Each pad electrode 64 is used for electrical connection between the second substrate 20 and the third substrate 30 and for bonding the second substrate 20 and the third substrate 30. Further, the pad electrode 64 does not necessarily have to be plural, and even one pad electrode can be electrically connected to the logic circuit 32.

- the second substrate 20 and the third substrate 30 are electrically connected to each other by bonding the pad electrodes 58 and 64 to each other.

- the gate of the transfer transistor TR (transfer gate TG) is electrically connected to the logic circuit 32 via the through wiring 54 and the pad electrodes 58 and 64.

- the third substrate 30 is attached to the second substrate 20 with the surface (surface 31S1) of the semiconductor substrate 31 facing the surface (surface 21S1) side of the semiconductor substrate 21. That is, the third substrate 30 is attached to the second substrate 20 face to face.

- FIG. 13 and 14 show an example of the cross-sectional configuration of the image pickup apparatus 1 in the horizontal direction.

- 13 and FIG. 14 are diagrams showing an example of the cross-sectional configuration at the cross section Sec1 of FIG. 1, and the bottom diagrams of FIG. 13 and FIG. 14 are the cross-sectional configuration at the cross section Sec2 of FIG. It is a figure which shows an example.

- FIG. 13 illustrates a configuration in which two sets of 2 ⁇ 2 four sensor pixels 12 are arranged in the second direction H

- FIG. 14 shows four sets of 2 ⁇ 2 four sensor pixels 12. A configuration in which they are arranged in the first direction V and the second direction H is illustrated. In the upper sectional views of FIGS.

- FIGS. 13 and 14 a diagram showing an example of the surface configuration of the semiconductor substrate 11 is superimposed on a diagram showing an example of the cross-sectional configuration in the cross section Sec1 of FIG. 1, and the insulating layer 46 Is omitted. Further, in the lower sectional views of FIGS. 13 and 14, a diagram showing an example of the surface configuration of the semiconductor substrate 21 is superimposed on a diagram showing an example of the cross-sectional configuration in the cross-sectional section Sec2 of FIG.

- the plurality of through wirings 54, the plurality of through wirings 48, and the plurality of through wirings 47 are in the plane of the first substrate 10 in the first direction V (vertical direction in FIG. 13, FIG. 14 are arranged side by side in a strip shape.

- FIGS. 13 and 14 illustrate a case where a plurality of through wires 54, a plurality of through wires 48, and a plurality of through wires 47 are arranged side by side in two rows in the first direction V.

- the first direction V is parallel to one of the two arrangement directions (for example, the row direction and the column direction) of the plurality of sensor pixels 12 arranged in a matrix.

- the four floating diffusion FDs are arranged close to each other, for example, via the element separation unit 43.

- the four transfer gates TGs are arranged so as to surround the four floating diffusion FDs, and for example, the four transfer gates TGs form a ring shape. ing.

- the insulating layer 53 is composed of a plurality of blocks extending in the first direction V.

- the semiconductor substrate 21 is composed of a plurality of island-shaped blocks 21A extending in the first direction V and arranged side by side in the second direction H orthogonal to the first direction V via an insulating layer 53. ..

- Each block 21A is provided with, for example, a plurality of sets of reset transistors RST, amplification transistor AMP, and selection transistor SEL.

- One read-out circuit 22 shared by the four sensor pixels 12 is composed of, for example, a reset transistor RST, an amplification transistor AMP, and a selection transistor SEL in a region facing the four sensor pixels 12.

- One readout circuit 22 shared by the four sensor pixels 12 includes, for example, an amplification transistor AMP in the block 21A adjacent to the left of the insulating layer 53, a reset transistor RST in the block 21A adjacent to the right of the insulating layer 53, and a selection transistor RST. It is composed of a transistor SEL.

- FIG. 15, FIG. 16, FIG. 17, and FIG. 18 show an example of the wiring layout in the horizontal plane of the image pickup apparatus 1.

- 15 to 18 illustrate a case where one readout circuit 22 shared by the four sensor pixels 12 is provided in a region facing the four sensor pixels 12.

- the wirings shown in FIGS. 15 to 18 are provided in different layers of the wiring layer 56, for example.

- the four through wires 54 adjacent to each other are electrically connected to the connection wiring 55, for example, as shown in FIG.

- the four penetrating wirings 54 adjacent to each other are further connected to the gate of the amplification transistor AMP included in the left adjacent block 21A of the insulating layer 53 via the connecting wiring 55 and the connecting portion 59, as shown in FIG. 15, for example.

- And is electrically connected to the gate of the reset transistor RST included in the right adjacent block 21A of the insulating layer 53.

- the power supply line VDD is arranged at a position facing each read circuit 22 arranged side by side in the second direction H.

- the power line VDD is electrically connected to the drain of the amplification transistor AMP and the drain of the reset transistor RST of each readout circuit 22 arranged side by side in the second direction H via the connection portion 59. Is connected.

- the two pixel drive lines 23 are arranged at positions facing each of the read-out circuits 22 arranged side by side in the second direction H.

- One pixel drive line 23 (second control line) is electrically connected to the gate of the reset transistor RST of each read circuit 22 arranged side by side in the second direction H, for example, as shown in FIG. Wiring RSTG.

- the other pixel drive line 23 (third control line) is electrically connected to the gate of the selection transistor SEL of each readout circuit 22 arranged side by side in the second direction H, for example, as shown in FIG. Wiring SELG.

- the source of the amplification transistor AMP and the drain of the selection transistor SEL are electrically connected to each other via the wiring 25, for example, as shown in FIG.

- the two power supply lines VSS are arranged at positions facing the respective read circuits 22 arranged side by side in the second direction H, as shown in FIG. 17, for example.

- each power line VSS is electrically connected to a plurality of through wirings 47 at a position facing each sensor pixel 12 arranged side by side in the second direction H, for example.

- the four pixel drive lines 23 are arranged at positions facing the respective readout circuits 22 arranged side by side in the second direction H.

- Each of the four pixel drive lines 23 is, for example, one of the four sensor pixels 12 corresponding to the respective readout circuits 22 arranged side by side in the second direction H, as shown in FIG.

- the wiring TRG is electrically connected to the twelve through wirings 48.

- the four pixel drive lines 23 are electrically connected to the gate (transfer gate TG) of the transfer transistor TR of each sensor pixel 12 arranged side by side in the second direction H. ..

- an identifier (1, 2, 3, 4) is given to the end of each wiring TRG.

- the vertical signal line 24 is arranged at a position facing each read circuit 22 arranged side by side in the first direction V.

- the vertical signal line 24 (output line) is electrically connected to the output end (source of the amplification transistor AMP) of each read circuit 22 arranged side by side in the first direction V. ing.

- the p well 42, the element isolation portion 43, and the p well layer 44 are formed on the semiconductor substrate 11.

- the photodiode PD, the transfer transistor TR, and the floating diffusion FD are formed on the semiconductor substrate 11 (FIG. 19A).

- the sensor pixel 12 is formed on the semiconductor substrate 11.

- a material having high heat resistance include polysilicon.

- the insulating layer 46 is formed on the semiconductor substrate 11 (FIG. 19A). In this way, the first substrate 10 is formed.

- the semiconductor substrate 21 is bonded onto the first substrate 10 (insulating layer 46B) (FIG. 19B). Then, the semiconductor substrate 21 is thinned if necessary. At this time, the thickness of the semiconductor substrate 21 is set to a film thickness required for forming the readout circuit 22.

- the thickness of the semiconductor substrate 21 is generally about several hundreds nm. However, depending on the concept of the read circuit 22, an FD (Fully Depletion) type is also possible, and in that case, the thickness of the semiconductor substrate 21 can be in the range of several nm to several ⁇ m.

- the insulating layer 53 is formed in the same layer as the semiconductor substrate 21 (FIG. 19C).

- the insulating layer 53 is formed, for example, at a position facing the floating diffusion FD.

- a slit (opening 21H) penetrating the semiconductor substrate 21 is formed in the semiconductor substrate 21 to separate the semiconductor substrate 21 into a plurality of blocks 21A.

- the insulating layer 53 is formed so as to fill the slit.

- a readout circuit 22 including an amplification transistor AMP and the like is formed in each block 21A of the semiconductor substrate 21 (FIG. 19C).

- the gate insulating film of the readout circuit 22 can be formed by thermal oxidation.

- the insulating layer 52 is formed on the semiconductor substrate 21.

- the interlayer insulating film 51 composed of the insulating layers 46, 52, 53 is formed.

- through holes 51A and 51B are formed in the interlayer insulating film 51 (FIG. 19D).