WO2013018811A1 - パワー半導体モジュール - Google Patents

パワー半導体モジュール Download PDFInfo

- Publication number

- WO2013018811A1 WO2013018811A1 PCT/JP2012/069512 JP2012069512W WO2013018811A1 WO 2013018811 A1 WO2013018811 A1 WO 2013018811A1 JP 2012069512 W JP2012069512 W JP 2012069512W WO 2013018811 A1 WO2013018811 A1 WO 2013018811A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- conductive layer

- transistor

- semiconductor module

- power semiconductor

- ceramic substrate

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/07—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L29/00

- H01L25/072—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L29/00 the devices being arranged next to each other

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48135—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/48137—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being arranged next to each other, e.g. on a common substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4911—Disposition the connectors being bonded to at least one common bonding area, e.g. daisy chain

- H01L2224/49111—Disposition the connectors being bonded to at least one common bonding area, e.g. daisy chain the connectors connecting two common bonding areas, e.g. Litz or braid wires

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4912—Layout

- H01L2224/49175—Parallel arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L24/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L24/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/73—Means for bonding being of different types provided for in two or more of groups H01L24/10, H01L24/18, H01L24/26, H01L24/34, H01L24/42, H01L24/50, H01L24/63, H01L24/71

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/18—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof the devices being of types provided for in two or more different subgroups of the same main group of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/102—Material of the semiconductor or solid state bodies

- H01L2924/1025—Semiconducting materials

- H01L2924/1026—Compound semiconductors

- H01L2924/1027—IV

- H01L2924/10272—Silicon Carbide [SiC]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/102—Material of the semiconductor or solid state bodies

- H01L2924/1025—Semiconducting materials

- H01L2924/1026—Compound semiconductors

- H01L2924/1032—III-V

- H01L2924/1033—Gallium nitride [GaN]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1203—Rectifying Diode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1305—Bipolar Junction Transistor [BJT]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1305—Bipolar Junction Transistor [BJT]

- H01L2924/13055—Insulated gate bipolar transistor [IGBT]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1306—Field-effect transistor [FET]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/191—Disposition

- H01L2924/19101—Disposition of discrete passive components

- H01L2924/19107—Disposition of discrete passive components off-chip wires

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/30107—Inductance

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M7/00—Conversion of ac power input into dc power output; Conversion of dc power input into ac power output

- H02M7/003—Constructional details, e.g. physical layout, assembly, wiring or busbar connections

Definitions

- the present invention relates to a power semiconductor module used for a power converter or the like.

- IGBT Insulated Gate Bipolar Transistor

- FET Field Effect Transistor

- This invention is made

- the power semiconductor module of the present invention includes a first ceramic substrate, a first conductive layer disposed on one main surface of the first ceramic substrate, and the first conductive layer on the other main surface of the first ceramic substrate.

- a second conductive layer disposed in a region opposite to the substrate, a transistor having a wider bandgap than silicon and disposed on the surface of the first conductive layer, and switching the transistor to switch the first conductive layer and A connecting member that electrically connects the first conductive layer and the second conductive layer so that a reverse current change occurs in the second conductive layer; and one main surface on the surface of the second conductive layer.

- a second ceramic substrate disposed so as to be in contact; and a third conductive layer disposed on the other main surface of the second ceramic substrate so as to be insulated from the second conductive layer.

- the electrical resistance (on-resistance) in the conduction state of the transistor is reduced, and a desired operation can be performed even at a high temperature.

- a power semiconductor module that can operate without using a large heat radiating member can be realized.

- a surge voltage can be suppressed by reducing the inductive reactance of a circuit by mutual inductance.

- a power semiconductor module capable of maximizing the performance of the transistor can be realized.

- a heat radiating member in contact with the surface of the third conductive layer may be provided. According to this configuration, since the heat dissipation member is disposed on the surface of the third conductive layer separated from the second conductive layer by the second ceramic substrate, the heat dissipation member can be insulated from the second conductive layer. Thereby, the safety

- the transistor is preferably a field effect transistor or IGBT.

- a field effect transistor By using a field effect transistor, a low-loss power semiconductor module can be realized.

- the transistor is preferably made of a wide band gap material that can be used at a temperature of 200 ° C. or higher. If it can be used under such temperature conditions, the heat dissipation member can be sufficiently downsized.

- the first conductive layer includes a first member and a second member disposed apart from the first member, and the first transistor and the second member are disposed on a surface of the first member. 1 diode is disposed, the first transistor and the first diode are connected by a first conductive wire, and the first transistor and the second member are connected by a second conductive wire. preferable. According to this configuration, since the first diode and the second member are connected via the first transistor, the power semiconductor module is reduced in size as compared with the case where the first diode and the second member are directly connected. It is possible to

- the first conductive layer includes a first member and a second member separated from the first member, and a first transistor and a first diode are disposed on the surface of the first member.

- a second transistor and a second diode are disposed on a surface of the second member; the first member is connected to a first terminal of the first transistor and a first terminal of the first diode;

- a second terminal of one transistor and a second terminal of the first diode are connected to the second member, and the second member is connected to a first terminal of the second transistor and a first terminal of the second diode.

- the second terminal of the second transistor and the second terminal of the second diode may be connected to the connection member.

- a power semiconductor module capable of exhibiting high performance without using a large heat radiating member can be provided.

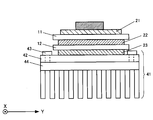

- FIG. 1 is a schematic diagram illustrating a configuration example of a power semiconductor module according to the present embodiment.

- FIG. 1A is a schematic plan view seen from the element arrangement surface side

- FIG. 1B is a schematic cross-sectional view showing a conductive wire.

- the power semiconductor module 1 includes a first ceramic substrate 11 serving as a support member.

- the first ceramic substrate 11 is a substrate having a substantially rectangular planar shape made of an insulating material such as silicon nitride, aluminum nitride, or aluminum oxide.

- a first conductive layer 21 made of a plurality of metal plates is provided on one main surface (upper side) which is the element arrangement surface side of the first ceramic substrate 11, and the other main surface of the first ceramic substrate 11.

- a second conductive layer 22 made of a metal plate is provided on the lower side.

- the metal plates constituting the first conductive layer 21 and the second conductive layer 22 are made of a metal material such as copper or aluminum and are brazed to the first ceramic substrate 11.

- the first conductive layer 21 may be a conductive member made of a conductive material other than metal.

- the first conductive layer 21 is composed of metal plates 21a to 21f that are spaced apart from each other.

- An external connection terminal 31a for power supply is connected to the metal plate 21a

- an external connection terminal 31b for power supply is connected to the metal plate 21b

- an output terminal 36 is connected to the metal plate 21c.

- the second conductive layer 22 is composed of a single metal plate.

- a diode 32a as a rectifying element and a transistor 33a as a switching element are arranged on the metal plate 21b. Terminals are formed on the lower surfaces of the diode 32a and the transistor 33a so as to be exposed, and the terminals and the metal plate 21b are electrically connected by solder. Further, terminals are respectively formed on the upper surfaces of the diode 32a and the transistor 33a, and conductive wires 34a to 34c are connected to the terminals so as to form a connection relationship described later.

- a diode 32b as a rectifying element and a transistor 33b as a switching element are arranged on the metal plate 21c. Terminals are respectively formed on the lower surfaces of the diode 32b and the transistor 33b so that the terminals are electrically connected to the metal plate 21c by soldering. In addition, terminals are formed on the upper surfaces of the diode 32b and the transistor 33b so that the terminals are exposed, and conductive wires 34d to 34f are connected to the terminals so as to form a connection relationship described later.

- the transistors 33a and 33b and the diodes 32a and 32b described above are made of a semiconductor material having a wider band gap than silicon. Since the transistors 33a and 33b and the diodes 32a and 32b made of such a semiconductor material can have lower on-resistance than transistors made of silicon, conduction loss can be reduced. Further, the transistors 33a and 33b and the diodes 32a and 32b made of such a semiconductor material can operate at a relatively high temperature of 200 ° C. or higher. As such a wide band gap semiconductor material, for example, silicon carbide (SiC) or gallium nitride (GaN) can be used.

- SiC silicon carbide

- GaN gallium nitride

- the transistors 33a and 33b are preferably, for example, FETs. By using FETs as the transistors 33a and 33b, the switching speed can be increased, and the conversion efficiency of the power converter when the power semiconductor module 1 is used can be increased. However, the transistors 33a and 33b are not limited to FETs.

- a second ceramic substrate 12 having substantially the same shape as the first ceramic substrate 11 is provided on the lower surface of the second conductive layer 22.

- the second ceramic substrate 12 is made of silicon nitride, aluminum nitride, aluminum oxide, or the like so that the lower surface of the second conductive layer 22 and the upper surface of the second ceramic substrate 12 are in contact with each other.

- the entire lower surface of the second conductive layer 22 is brazed.

- a third conductive layer 23 made of a metal plate is provided on the lower surface of the second ceramic substrate 12.

- the third conductive layer 23 is made of a metal material such as copper or aluminum, and is soldered to the second ceramic substrate 12 so that the lower surface of the second ceramic substrate 12 and the upper surface of the third conductive layer 23 are in contact with each other. ing.

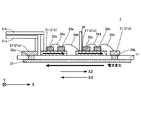

- FIG. 2 is a view of the power semiconductor module with the heat dissipation member attached as viewed from the direction of the arrow X1 shown in FIGS. 1A and 1B. However, in FIG. 2, a part of the configuration of the power semiconductor module is omitted.

- a copper base 42 of the heat dissipation member 41 is soldered to the lower surface of the third conductive layer 23.

- the cooling fins 44 are fixed to the copper base 42 by bolts 43 screwed from the upper surface of the copper base 42 in a state where the lower surface of the copper base 42 and the upper surface of the cooling fin 44 are in contact with each other. Thereby, the power semiconductor module 1 can be kept in an operable temperature range.

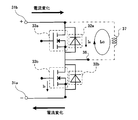

- FIG. 3 is a circuit configuration diagram of the power semiconductor module according to the present embodiment.

- a transistor 33a that is an n-channel FET and a transistor 33b that is an n-channel FET are provided in the power semiconductor module 1, between the external connection terminal 31a for power supply and the external connection terminal 31b.

- a transistor 33a that is an n-channel FET and a transistor 33b that is an n-channel FET are provided in the power semiconductor module 1, between the external connection terminal 31a for power supply and the external connection terminal 31b.

- a transistor 33a that is an n-channel FET and a transistor 33b that is an n-channel FET are provided in series.

- the drain terminal exposed on the lower surface of the transistor 33a is connected to the metal plate 21b, and a high potential from the power source is applied through the external connection terminal 31b.

- the source terminal exposed on the upper surface of the transistor 33b is connected to the metal plate 21d by a conductive wire 34e. Further, the metal plate 21 d is electrically connected to the metal plate constituting the second conductive layer 22 by the connection member 35 b provided in the through hole of the first ceramic substrate 11, and constitutes the second conductive layer 22. The metal plate is electrically connected to the metal plate 21 a by a connection member 35 a provided in the through hole of the first ceramic substrate 11. Thereby, a low potential is applied to the source terminal of the transistor 33b through the external connection terminal 31a.

- the source terminal exposed on the upper surface of the transistor 33a is connected to the metal plate 21c by the conductive wire 34b.

- the drain terminal exposed on the lower surface of the transistor 33b is connected to the metal plate 21c. Thereby, the source terminal of the transistor 33a and the drain terminal of the transistor 33b are connected to the common output terminal 36 connected to the metal plate 21c.

- the gate terminal exposed on the upper surface of the transistor 33a is connected to the metal plate 21e by the conductive wire 34c, and a control potential for controlling the switching of the transistor 33a is applied from the outside through the metal plate 21e and the conductive wire 34c. It is like that.

- the gate terminal exposed on the upper surface of the transistor 33b is connected to the metal plate 21f by the conductive wire 34f, and a control potential for controlling the switching of the transistor 33b is applied from the outside through the metal plate 21f and the conductive wire 34f. It has come to be.

- the transistors 33a and 33b are n-channel FETs, they are turned on when the potential difference generated between the gate and the source is larger than the threshold voltage, and turned off when the potential difference generated between the gate and the source is smaller than the threshold voltage. It becomes.

- a diode 32a is connected in parallel to the transistor 33a. Specifically, the cathode exposed on the lower surface of the diode 32a is connected to the metal plate 21b, and the anode exposed on the upper surface of the diode 32a is connected to the drain terminal exposed on the upper surface of the transistor 33a by the conductive wire 34a. Has been. Thereby, the reverse bias is applied to the diode 32a from the power source.

- a diode 32b is connected in parallel to the transistor 33b. Specifically, the cathode exposed on the lower surface of the diode 32b is connected to the metal plate 21c, and the anode exposed on the upper surface of the diode 32b is connected to the drain terminal exposed on the upper surface of the transistor 33b by the conductive wire 34d. Has been. Thereby, the reverse bias is applied to the diode 32b from the power source.

- a predetermined high potential is applied to the gate of the transistor 33a to turn on the transistor 33a, or a predetermined high potential is applied to the gate of the transistor 33b to cause the transistor 33b.

- a predetermined high potential is applied to the gate of the transistor 33a to turn on the transistor 33a

- a predetermined high potential is applied to the gate of the transistor 33b to cause the transistor 33b.

- it is possible to control the voltage appearing at the output terminal 36 according to whether the transistors 33a and 33b are on or off.

- it is used as an inverter that converts direct current into alternating current (single-phase alternating current when there are two power semiconductor modules 1 and three-phase alternating current when there are two). Can do.

- the temperature of each part of the power semiconductor module is simulated when using conventional silicon (Si) and when using silicon carbide (SiC) for the transistor. did.

- a simulation was performed for two conditions of an element A1 using silicon carbide (SiC) and an element A2 using silicon (Si).

- simulation was performed on two conditions of the structure B1 having the second ceramic substrate and the third conductive layer, and the structure B2 having no second conductive substrate.

- ⁇ T (j ⁇ c) represents a temperature difference from the contact surface between the transistor and the metal plate in the semiconductor module to the contact surface between the heat dissipation member and the semiconductor module

- ⁇ T (c ⁇ a) represents the temperature difference in the heat dissipation member.

- the temperature difference from the contact surface with the semiconductor module to the atmosphere is shown.

- the atmospheric temperature was 40 ° C.

- a second ceramic substrate that is thermally disadvantageous is provided to prevent charging of the heat dissipation member, but a structure that does not include the second ceramic substrate (Comparative 1).

- the change in Rth (ca) remains at about 5%.

- the power semiconductor module 1 according to the present embodiment has a large heat dissipation member despite the thermally disadvantageous two-layer substrate structure (two-layer structure of the first ceramic substrate and the second ceramic substrate). It is not necessary to use a thermal design, and it is not necessary to change the thermal design greatly.

- the power semiconductor module 1 has a thermal margin in spite of adopting a thermally disadvantageous two-layer substrate structure to prevent the heat radiation member from being charged. It can operate sufficiently without using a large heat dissipation member.

- the power semiconductor module using silicon since the power semiconductor module using silicon has no thermal margin, if the two-layer substrate structure is adopted, the heat dissipation member must be enlarged.

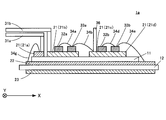

- FIG. 5 is a schematic diagram showing the direction of current change of the power semiconductor module according to the present embodiment.

- the metal plate 21 a provided on the upper surface of the first ceramic substrate 11 is provided on the lower surface of the first ceramic substrate 11 by the connection member 35 a provided in the through hole of the first ceramic substrate 11.

- Two conductive layers 22 are connected.

- the metal plate 21 d provided on the upper surface of the first ceramic substrate 11 is connected to the second conductive layer 22 by a connection member 35 b provided in the through hole of the first ceramic substrate 11.

- the external connection terminal 31b, the metal plate 21b, the metal plate 21c, and the metal plate 21d on the upper surface of the first ceramic substrate 11 are connected to the second conductive layer 22 on the lower surface of the first ceramic substrate 11 by the connection member 35b.

- the second conductive layer 22 on the lower surface of the first ceramic substrate 11 and the metal plate 21a and the external connection terminal 31a on the upper surface of the first ceramic substrate 11 are connected by the connection member 35a to form a circuit. .

- the metal plate constituting the second conductive layer 22 Since the change of the current transmitted to the second conductive layer 22 is transmitted to the low potential external connection terminal 31a through the connection member 35a and the conductive member 21a, the metal plate constituting the second conductive layer 22 is directed leftward (arrow X3). Change in current (increase in current) occurs. In other words, the switching of the transistor 33b causes reverse current changes in the metal plates 21b and 21c constituting the first conductive layer 21 and the second conductive layer 22 opposed thereto. More specifically, a reverse current change occurs in the opposing region of the metal plate 21b and the second conductive layer 22, and a reverse current change occurs in the opposing region of the metal plate 21c and the second conductive layer 22.

- the current change in the reverse direction is performed between the metal plates 21 b and 21 c constituting the first conductive layer 21 and the metal plate constituting the second conductive layer 22. Is configured to occur. For this reason, the inductive reactance (inductance) of the circuit is reduced by the mutual inductance between the metal plates 21 b and 21 c constituting the first conductive layer 21 and the metal plate constituting the second conductive layer 22. For example, in the power semiconductor module 1 according to the present embodiment, it has been confirmed that the inductance of the circuit can be reduced to about 1/10. Thus, the surge voltage in the power semiconductor module 1 can be suppressed by reducing the inductance of the circuit. Note that the direction of the current change in the metal plates 21b and 21c and the direction of the current change in the metal plate constituting the second conductive layer 22 need not be opposite to 180 ° if the circuit inductance can be reduced. good.

- the surge voltage generated in the above circuit increases as the switching speed increases. This is because the surge voltage depends on the product of the inductive reactance and the time derivative (di / dt) of the current.

- the transistors 33a and 33b are FETs, the switching speed increases, so that the time differentiation of the current at the time of switching increases.

- the reverse current flows in the opposing regions.

- the third conductive layer 23 is insulated from the first conductive layer 21 and the second conductive layer 22 by the second ceramic substrate 12. Thereby, the conduction

- Such electric shock prevention measures are particularly effective in fields where safety is important, such as railway vehicles and automobiles.

- the third conductive layer 23 is preferably connected to the ground.

- the anode exposed on the upper surface of the diode 32a and the metal plate 21c are connected to the source terminal exposed on the upper surface of the transistor 33a.

- the anode exposed on the upper surface of the diode 32b and the metal plate 21d are connected to the source terminal exposed on the upper surface of the transistor 33b.

- the metal plate 21d when the anode of the diode 32b and the metal plate 21d are directly connected, the metal plate 21d includes a conductive wire that connects the source terminal of the transistor 33b and the metal plate 21d, and the anode of the diode 32b. Since a conductive wire that connects the metal plate 21d is connected, the metal plate 21d requires a certain area. On the other hand, in the configuration according to the present embodiment, since only the conductive wire that connects the source terminal of the transistor 33b and the metal plate 21d is connected to the metal plate 21d, the area of the metal plate 21d can be reduced. Thereby, it is possible to reduce the size of the power semiconductor module.

- FIG. 6 is a schematic diagram showing a modification of the power semiconductor module according to the present embodiment.

- the basic configuration of the power semiconductor module 1 a shown in FIG. 6 is the same as that of the power semiconductor module 1.

- the main differences between the power semiconductor module 1a according to the present embodiment and the power semiconductor module 1 are the size of the first ceramic substrate 11 and the structure of the connection portion between the first conductive layer 21 and the second conductive layer 22. It is.

- the first ceramic substrate 11 is slightly smaller than the second ceramic substrate 12, and the width in the horizontal direction (X direction) in the drawing is short. Thereby, part of the upper surface is exposed at both ends of the second conductive layer 22. Further, the conductive wire 34e connects the source terminal of the transistor 33b and the exposed portion at one end of the metal plate constituting the second conductive layer 22, and accordingly, the metal plate 21d is omitted. Has been. In addition, a portion exposed at the other end of the metal plate constituting the second conductive layer 22 and the metal plate 21a are connected by the conductive wire 34g. That is, in the present embodiment, the conductive wire 34e and the conductive wire 34g function as connection members. As described above, when the first conductive layer 21 and the second conductive layer 22 are electrically connected by wire bonding, it is not necessary to provide a through hole and a connection member in the first ceramic substrate, thereby simplifying the manufacturing process. Is possible.

- the same effect as that of the power semiconductor module 1 can be obtained in the power semiconductor module 1a having such a configuration.

- the configuration of the present invention by using a transistor formed of a material having a wider band gap than silicon, the on-resistance is reduced, and a desired operation is possible even at a high temperature.

- a power semiconductor module that can be operated without being used can be realized.

- the inductive reactance of the circuit can be reduced by the mutual inductance and the surge voltage can be suppressed. Thereby, it is possible to realize a power semiconductor module capable of fully utilizing the characteristics of the transistor and exhibiting high performance.

- the present invention is not limited to the above embodiment, and can be implemented with various modifications.

- an IGBT may be used as the transistor.

- the size, shape, and the like illustrated in the accompanying drawings are not limited thereto, and can be appropriately changed within a range in which the effect of the present invention is exhibited.

- various modifications can be made without departing from the scope of the object of the present invention.

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Inverter Devices (AREA)

- Dc-Dc Converters (AREA)

Abstract

大型の放熱部材を用いることなく高い性能を発揮可能なパワー半導体モジュールを提供すること。本発明のパワー半導体モジュール(1)は、第1セラミック基板(11)と、第1セラミック基板の一方の主面に配置された第1導電層(21)と、第1セラミック基板の他方の主面において第1導電層と対向する領域に配置された第2導電層(22)と、シリコンよりバンドギャップの広い材料で構成され、第1導電層の表面に配置されたトランジスタ(33a、33b)と、前記トランジスタのスイッチングによって第1導電層及び第2導電層に逆向きの電流変化が発生するように第1導電層と第2導電層とを電気的に接続する接続部材(35a)と、第2導電層の表面に一方の主面が接触するように配置された第2セラミック基板(12)と、第2導電層と絶縁されるように第2セラミック基板の他方の主面に配置された第3導電層(23)と、を備える。

Description

本発明は、電力変換器などに用いられるパワー半導体モジュールに関する。

電力用の半導体素子として、IGBT(Insulated Gate Bipolar Transistor)と呼ばれるものが知られている。このIGBTは、電界効果型トランジスタ(FET:Field Effect Transister)とバイポーラトランジスタとを組み合わせた構造を有しており、これによって、FETの高いスイッチング特性と、バイポーラトランジスタの低い発熱特性とを実現している。

このようなIGBTを用いるパワー半導体モジュールとして、流れる電流の方向が逆である2本のパワーラインをセラミック基板の両主面に対向配置させて、その相互インダクタンスにより回路のリアクタンスを低減させる構造が提案されている(例えば、特許文献1参照)。このように回路のリアクタンスを低減させることで、スイッチング時におけるサージ電圧を低減して半導体素子の破壊などを防止できる。

ところで、近年では、変換効率の高い電力変換器が求められている。電力変換器の変換効率を高めるための方法として、例えば、使用する半導体素子のスイッチング速度を高めてスイッチング時の損失を低減する方法が考えられる。IGBTより高いスイッチング速度を実現できる構造の半導体素子としては、例えば、FETが挙げられる。

しかしながら、シリコンを用いたFETはオン抵抗が大きいため、高電圧が適用される電力変換器などに用いると、かえって導通損失が増大してしまう。また、オン抵抗による発熱量が大きいため、大型の放熱部材を用いて冷却効率を高めなくてはならず、半導体モジュールが大型化してしまう。さらに、スイッチング速度が高くなるとそれに応じてサージ電圧も大きくなるため、素子の破壊に対して十分に余裕をもった設計を行わなくてはならなくなり、その結果、半導体素子の性能を十分に発揮させることができなくなる。また、IGBTであっても電流が100Aを超えるような大容量変換器の場合、大きな電流をオン、オフさせるために、100A以下の小容量の場合と異なり、FETと同様に大きなサージ電圧が発生するという問題がある。

本発明は、かかる点に鑑みてなされたものであり、大型の放熱部材を用いることなく高い性能を発揮可能なパワー半導体モジュールを提供することを目的とする。

本発明のパワー半導体モジュールは、第1セラミック基板と、前記第1セラミック基板の一方の主面に配置された第1導電層と、前記第1セラミック基板の他方の主面において前記第1導電層と対向する領域に配置された第2導電層と、シリコンよりバンドギャップの広い材料で構成され、前記第1導電層の表面に配置されたトランジスタと、前記トランジスタのスイッチングによって前記第1導電層及び前記第2導電層に逆向きの電流変化が生じるように前記第1導電層と前記第2導電層とを電気的に接続する接続部材と、前記第2導電層の表面に一方の主面が接触するように配置された第2セラミック基板と、前記第2導電層と絶縁されるように前記第2セラミック基板の他方の主面に配置された第3導電層と、を備えたことを特徴とする。

この構成によれば、シリコンよりバンドギャップの広い材料で構成されたトランジスタを用いることにより、トランジスタの導通状態における電気抵抗(オン抵抗)が小さくなり、高温においても所望の動作が可能になるため、大型の放熱部材を用いることなく動作可能なパワー半導体モジュールを実現できる。また、対向する第1導電層及び第2導電層に逆向きの電流変化が生じるように構成されているため、相互インダクタンスにより回路の誘導リアクタンスを低減してサージ電圧を抑制できる。これにより、トランジスタの性能を最大限に発揮可能なパワー半導体モジュールを実現できる。

本発明のパワー半導体モジュールにおいて、前記第3導電層の表面に接する放熱部材を備えても良い。この構成によれば、第2セラミック基板によって第2導電層と隔てられた第3導電層の表面に放熱部材が配置されるため、放熱部材を第2導電層から絶縁することができる。これにより、パワー半導体モジュールの安全性を高めることができる。

本発明のパワー半導体モジュールにおいて、前記トランジスタは、電界効果型トランジスタ又はIGBTであることが好ましい。電界効果型トランジスタを用いることにより、低損失のパワー半導体モジュールを実現できる。

本発明のパワー半導体モジュールにおいて、前記トランジスタは、200℃以上の温度条件において使用可能なワイドバンドギャップ材料で構成されることが好ましい。このような温度条件で使用可能であれば、放熱部材を十分に小型化可能である。

本発明のパワー半導体モジュールにおいて、前記第1導電層は、第1部材及び当該第1部材と離間して配置された第2部材で構成され、前記第1部材の表面には第1トランジスタ及び第1ダイオードが配置され、前記第1トランジスタと前記第1ダイオードとは、第1導電性ワイヤにより接続され、前記第1トランジスタと第2部材とは、第2導電性ワイヤにより接続されていることが好ましい。この構成によれば、第1ダイオードと第2部材とが第1トランジスタを介して接続されるため、第1ダイオードと第2部材とを直接的に接続する場合と比較してパワー半導体モジュールを小型化することが可能である。

本発明のパワー半導体モジュールにおいて、前記第1導電層は、第1部材及び当該第1部材と分離した第2部材で構成され、前記第1部材の表面には第1トランジスタ及び第1ダイオードが配置され、前記第2部材の表面には第2トランジスタ及び第2ダイオードが配置され、前記第1部材は、前記第1トランジスタの第1端子及び前記第1ダイオードの第1端子と接続され、前記第1トランジスタの第2端子及び前記第1ダイオードの第2端子は、前記第2部材と接続され、前記第2部材は、前記第2トランジスタの第1端子及び前記第2ダイオードの第1端子と接続され、前記第2トランジスタの第2端子及び前記第2ダイオードの第2端子は、前記接続部材と接続されていても良い。

本発明によれば、大型の放熱部材を用いることなく高い性能を発揮可能なパワー半導体モジュールを提供することができる。

(実施の形態1)

以下、本発明の実施の形態について添付図面を参照して詳細に説明する。図1は、本実施の形態に係るパワー半導体モジュールの構成例を示す模式図である。図1Aは素子配置面側から見た平面模式図であり、図1Bは導電性ワイヤを含むように示した断面模式図である。図1に示すように、パワー半導体モジュール1は、支持部材となる第1セラミック基板11を含んで構成されている。第1セラミック基板11は、窒化ケイ素、窒化アルミニウム、又は酸化アルミニウムなどの絶縁性の材料で構成された平面形状が略長方形の基板である。

以下、本発明の実施の形態について添付図面を参照して詳細に説明する。図1は、本実施の形態に係るパワー半導体モジュールの構成例を示す模式図である。図1Aは素子配置面側から見た平面模式図であり、図1Bは導電性ワイヤを含むように示した断面模式図である。図1に示すように、パワー半導体モジュール1は、支持部材となる第1セラミック基板11を含んで構成されている。第1セラミック基板11は、窒化ケイ素、窒化アルミニウム、又は酸化アルミニウムなどの絶縁性の材料で構成された平面形状が略長方形の基板である。

第1セラミック基板11の素子配置面側となる一方の主面(上側)には複数の金属板で構成された第1導電層21が設けられており、第1セラミック基板11の他方の主面(下側)には金属板による第2導電層22が設けられている。第1導電層21、及び第2導電層22を構成する金属板は、銅、アルミニウムなどの金属材料で構成されており、第1セラミック基板11にろう接されている。なお、第1導電層21は、金属以外の導電材料で構成された導電部材であっても良い。

第1導電層21は、互いに離間して配置された金属板21a~21fによって構成されている。金属板21aには、電力供給用の外部接続端子31aが接続されており、金属板21bには電力供給用の外部接続端子31bが接続されおり、金属板21cには出力端子36が接続されている。第2導電層22は、1枚の金属板によって構成されている。

金属板21b上には、整流素子であるダイオード32a及びスイッチング素子であるトランジスタ33aが配置されている。ダイオード32a及びトランジスタ33aの下面にはそれぞれ端子が露出するように形成されており、半田によって、この端子と金属板21bとが電気的に接続されている。また、ダイオード32a及びトランジスタ33aの上面にはそれぞれ端子が露出するように形成されており、当該端子には後述する接続関係を形成するように導電性ワイヤ34a~34cが接続されている。

また、金属板21c上には、整流素子であるダイオード32b及びスイッチング素子であるトランジスタ33bが配置されている。ダイオード32b及びトランジスタ33bの下面にはそれぞれ端子が露出するように形成されており、半田によって、この端子と金属板21cとが電気的に接続されている。また、ダイオード32b及びトランジスタ33bの上面にはそれぞれ端子が露出するように形成されており、当該端子には後述する接続関係を構成するように導電性ワイヤ34d~34fが接続されている。

上述したトランジスタ33a、33b、ダイオード32a、32bは、シリコンよりバンドギャップの広い半導体材料で構成されている。このような半導体材料で構成されたトランジスタ33a、33b、ダイオード32a、32bは、シリコンで構成されたトランジスタよりオン抵抗を小さくすることができるため、導通損失を低減できる。また、このような半導体材料で構成されたトランジスタ33a、33b、ダイオード32a、32bは、200℃以上の比較的高い温度でも動作可能である。このようなワイドバンドギャップ半導体材料としては、例えば、炭化ケイ素(SiC)又は窒化ガリウム(GaN)などを用いることができる。

トランジスタ33a、33bは、例えば、FETであることが好ましい。トランジスタ33a、33bとしてFETを用いることによりスイッチング速度の高速化が実現され、パワー半導体モジュール1を用いて構成した場合の電力変換器の変換効率を高めることができる。ただし、トランジスタ33a、33bはFETに限られない。

第2導電層22の下面には、第1セラミック基板11と略同形状の第2セラミック基板12が設けられている。第2セラミック基板12は、第1セラミック基板11と同様、窒化ケイ素、窒化アルミニウム、又は酸化アルミニウムなどで構成されており、第2導電層22の下面と第2セラミック基板12の上面とが接するように、第2導電層22の下面全体にろう接されている。また、第2セラミック基板12の下面には金属板により構成された第3導電層23が設けられている。第3導電層23は、銅、アルミニウムなどの金属材料で構成されており、第2セラミック基板12の下面と第3導電層23の上面とが接するように、第2セラミック基板12にろう接されている。

第3導電層23の下面には放熱部材が取り付けられる。図2は、放熱部材が取り付けられた状態のパワー半導体モジュールを、図1A、Bに示す矢印X1の方向から見た図である。ただし、図2では、パワー半導体モジュールの一部の構成は省略して示している。図2に示すように、第3導電層23の下面には、放熱部材41の銅ベース42が半田付けされている。銅ベース42には、銅ベース42の下面と冷却フィン44の上面とが接した状態で銅ベース42の上面からねじ込まれたボルト43により冷却フィン44が固定されている。これにより、パワー半導体モジュール1を、動作可能な温度範囲に保つことができるようになっている。

図3は、本実施の形態に係るパワー半導体モジュールの回路構成図である。以下、図1及び図3を参照して説明する。図3に示すように、パワー半導体モジュール1において、電力供給用の外部接続端子31aと外部接続端子31bとの間には、nチャネル型FETであるトランジスタ33aと、nチャネル型FETであるトランジスタ33bとが直列に接続されている。具体的には、トランジスタ33aの下面において露出するドレイン端子は、金属板21bと接続されており、外部接続端子31bを通じて電源からの高電位が与えられるようになっている。

トランジスタ33bの上面において露出するソース端子は、導電性ワイヤ34eによって金属板21dと接続されている。また、金属板21dは、第1セラミック基板11のスルーホールに設けられた接続部材35bによって第2導電層22を構成する金属板と電気的に接続されており、第2導電層22を構成する金属板は、第1セラミック基板11のスルーホールに設けられた接続部材35aによって金属板21aと電気的に接続されている。これにより、トランジスタ33bのソース端子には外部接続端子31aを通じて低電位が与えられるようになっている。

トランジスタ33aの上面において露出するソース端子は、導電性ワイヤ34bによって金属板21cと接続されている。また、トランジスタ33bの下面において露出するドレイン端子は、金属板21cと接続されている。これにより、トランジスタ33aのソース端子及びトランジスタ33bのドレイン端子は、金属板21cと接続された共通の出力端子36に接続されている。

トランジスタ33aの上面において露出するゲート端子は、導電性ワイヤ34cによって金属板21eと接続されており、金属板21e及び導電性ワイヤ34cを通じて、外部からトランジスタ33aのスイッチングを制御する制御電位が印加されるようになっている。また、トランジスタ33bの上面において露出するゲート端子は、導電性ワイヤ34fによって金属板21fと接続されており、金属板21f及び導電性ワイヤ34fを通じて、外部からトランジスタ33bのスイッチングを制御する制御電位が印加されるようになっている。トランジスタ33a、33bはnチャネル型のFETであるから、ゲート-ソース間に生じる電位差がしきい値電圧より大きい場合にオンとなり、ゲート-ソース間に生じる電位差がしきい値電圧より小さい場合にオフとなる。

また、図3に示すように、トランジスタ33aに対して並列にダイオード32aが接続されている。具体的には、ダイオード32aの下面において露出するカソードは、金属板21bと接続されており、ダイオード32aの上面において露出するアノードは、導電性ワイヤ34aによってトランジスタ33aの上面において露出するドレイン端子と接続されている。これにより、ダイオード32aは、電源から逆方向バイアスが印加されるようになっている。

同様に、トランジスタ33bに対して並列にダイオード32bが接続されている。具体的には、ダイオード32bの下面において露出するカソードは、金属板21cと接続されており、ダイオード32bの上面において露出するアノードは、導電性ワイヤ34dによってトランジスタ33bの上面において露出するドレイン端子と接続されている。これにより、ダイオード32bは、電源から逆方向バイアスが印加されるようになっている。

このように構成されたパワー半導体モジュール1において、例えば、トランジスタ33aのゲートに所定の高電位が印加されてトランジスタ33aがオンになり、又はトランジスタ33bのゲートに所定の高電位が印加されてトランジスタ33bがオンになると、トランジスタ33aのソースとドレインとの間、又はトランジスタ33bのソースとドレインとの間には、実質的な電位差が無くなる。このため、トランジスタ33a、33bのオン、オフに応じて出力端子36に現れる電圧を制御することが可能である。例えば、このようなパワー半導体モジュール1を複数使用することにより、直流を交流に変換するインバータ(パワー半導体モジュール1が2個の場合は単相交流、3個の場合は三相交流)として用いることができる。

次に、図3及び図4を参照してインバータ駆動における回路動作を説明する。ここでは、トランジスタ33aのドレイン端子と出力端子36との間にインダクタンス負荷37を加えた場合の動作について説明する。なお、ダイオード32aを流れる電流Ia及びトランジスタ33bを流れる電流Ibは、図3及び図4において矢印で示す方向を正方向とする。初期状態において、トランジスタ33a、33bはいずれもオフであり、ダイオード32aにはインダクタンス負荷37による負方向の還流電流Ia0が流れているものとする。

トランジスタ33bがオフからオンになると、トランジスタ33bには外部接続端子31bからインダクタンス負荷37を通じて電流が流れる。一方、トランジスタ33bのオンに伴いダイオード32aのカソード側の電位が低下するため、ダイオード32aに流れていた還流電流Ia0は減少する。この場合、ダイオード32aを流れる電流Iaは正方向に増加するよう変化する。また、トランジスタ33bがオフからオンになるため、トランジスタ33bを流れる電流Ibは正方向に増加するよう変化する。つまり、ダイオード32aの電流変化とトランジスタ33bの電流変化とは正方向の増加(負方向の減少)で一致する。

その後、トランジスタ33bがオンからオフになると、トランジスタ33bを流れる電流が減少する。この場合、インダクタンス負荷37は電流を流し続けようとするので、ダイオード32aのアノード側の電位が上昇して負方向の還流電流が流れ始める。つまり、ダイオード32aの電流変化とトランジスタ33bの電流変化とは負方向の増加(正方向の減少)で一致する。このようにトランジスタ33bのスイッチングによってトランジスタに電流変化が生じる場合、ダイオード32aには、正負の方向及び増減が同じ電流変化が生じる。

なお、ここでは、トランジスタ33aのドレイン端子(高電位の外部接続端子31b)と出力端子36との間にインダクタンス負荷37を挿入してトランジスタ33bをスイッチングさせる場合の回路動作を説明したが、トランジスタ33bのソース端子(低電位の外部接続端子31a)と出力端子36との間にインダクタンス負荷37を挿入してトランジスタ33aをスイッチングさせる場合、トランジスタ33aとダイオード32bに正負の方向及び増減が同じ電流変化が生じる。

本実施の形態に係るパワー半導体モジュール1の特性を確認するため、トランジスタに従来のシリコン(Si)を用いる場合と、炭化ケイ素(SiC)を用いる場合とにおいて、パワー半導体モジュールの各部の温度をシミュレーションした。ここでは、炭化ケイ素(SiC)を用いた素子A1、及びシリコン(Si)を用いた素子A2の2条件についてシミュレーションを行った。また、第2セラミック基板及び第3導電層を有する構造B1、及びこれらを有しない構造B2の2条件についてシミュレーションを行った。すなわち、素子A1と構造B1との組み合わせ(実施の形態)、素子A1と構造B2との組み合わせ(比較1)、素子A2と構造B1との組み合わせ(比較2)、素子A2と構造B2との組み合わせ(比較3)の計4条件でシミュレーションを行った。

シミュレーションにおいて、炭化ケイ素(SiC)を用いたトランジスタの損失は20W、使用可能な温度の上限は250℃と仮定した。また、シリコン(Si)を用いたトランジスタの損失は60W、使用可能な温度の上限は150℃と仮定した。シミュレーション結果を表1に示す。なお、表1において、Rth(j-c)は、半導体モジュールにおけるトランジスタと金属板との接触表面から、放熱部材と半導体モジュールとの接触表面までの熱抵抗を示し、Rth(c-a)は、放熱部材と半導体モジュールとの接触表面から、大気までの熱抵抗を示す。また、ΔT(j-c)は、半導体モジュールにおけるトランジスタと金属板との接触表面から、放熱部材と半導体モジュールとの接触表面までの温度差を示し、ΔT(c-a)は、放熱部材における半導体モジュールとの接触表面から、大気までの温度差を示す。大気の温度は40℃とした。

表1に示すように、本実施の形態においては、放熱部材の帯電を防止するために熱的に不利な第2セラミック基板を備えているが、第2セラミック基板を備えない構造(比較1)と比較して、Rth(c-a)の変化は5%程度に留まっている。このため、本実施の形態に係るパワー半導体モジュール1は、熱的に不利な2層基板構造(第1セラミック基板と第2セラミック基板の2層構造)であるにもかかわらず、大型の放熱部材を用いる必要がなく、熱設計を大きく変更する必要もない。

一方で、シリコンを用いたパワー半導体モジュールにおいて第2セラミック基板を備える場合(比較2)、第2セラミック基板を備えない構造(比較3)と比較して、Rth(c-a)の変化は40%に達する。このため、シリコンを用いたパワー半導体モジュールにおいて2層基板構造を適用すると、放熱部材を大型化しなくてはならず、熱設計を抜本的に見直さなくてはならない。

このように、本実施の形態に係るパワー半導体モジュール1は、放熱部材の帯電を防止するため熱的に不利な2層基板構造を採用しているにもかかわらず、熱的に余裕があるため大型の放熱部材を用いなくとも十分に動作可能である。これに対し、シリコンを用いたパワー半導体モジュールにおいては熱的に余裕がないため、2層基板構造を採用すると放熱部材を大型化しなくてはならない。

図5は、本実施の形態に係るパワー半導体モジュールの電流変化の向きを示す模式図である。上述したように、第1セラミック基板11の上面に設けられた金属板21aは、第1セラミック基板11のスルーホールに設けられた接続部材35aにより、第1セラミック基板11の下面に設けられた第2導電層22と接続されている。また、第1セラミック基板11の上面に設けられた金属板21dは、第1セラミック基板11のスルーホールに設けられた接続部材35bにより、第2導電層22と接続されている。これにより、第1セラミック基板11の上面における外部接続端子31b、金属板21b、金属板21c、及び金属板21dと、第1セラミック基板11の下面における第2導電層22とが接続部材35bによって接続され、第1セラミック基板11の下面における第2導電層22と、第1セラミック基板11の上面における金属板21a及び外部接続端子31aとが接続部材35aによって接続されて一巡の回路が構成されている。

例えば、高電位の外部接続端子31bと出力端子36との間に図示しないインダクタンス負荷が接続されてダイオード32aに還流電流が流れている場合、金属板21f及び導電性ワイヤ34fを通じてトランジスタ33bのゲート端子に所定の高電位が印加されると、トランジスタ33bのドレイン端子には高電位の外部接続端子31bからインダクタンス負荷を通じて電流が流れ込む。このとき、金属板21b、21cには、図5に示すような図面右向き(矢印X2)の電流の変化(電流の増加)が発生する(図3参照)。この電流の変化は、導電ワイヤ34e、導電部材21d、及び接続部材35bを通じて第2導電層22に伝わる。第2導電層22に伝わった電流の変化は接続部材35a及び導電部材21aを通じて低電位の外部接続端子31aに伝わるので、第2導電層22を構成する金属板には、図面左向き(矢印X3)の電流の変化(電流の増加)が発生する。つまり、トランジスタ33bのスイッチングによって、第1導電層21を構成する金属板21b、21cと、これに対向する第2導電層22には、逆向きの電流変化が生じる。より詳細には、金属板21b及び第2導電層22の対向領域には逆向きの電流変化が生じ、金属板21c及び第2導電層22の対向領域には逆向きの電流変化が生じる。

このように、本実施の形態に係るパワー半導体モジュール1は、第1導電層21を構成する金属板21b、21cと、第2導電層22を構成する金属板との間に逆向きの電流変化が発生するように構成されている。このため、第1導電層21を構成する金属板21b、21cと、第2導電層22を構成する金属板との相互インダクタンスにより、回路の誘導リアクタンス(インダクタンス)は低減される。例えば、本実施の形態に係るパワー半導体モジュール1では、回路のインダクタンスを1/10程度に低減できることを確認している。このように、回路のインダクタンスを低減することにより、パワー半導体モジュール1におけるサージ電圧を抑制できる。なお、金属板21b、21cにおける電流変化の向きと、第2導電層22を構成する金属板における電流変化の向きとは、回路のインダクタンスを低減可能であれば、180°の逆向きでなくとも良い。

上述した回路において生じるサージ電圧は、スイッチング速度が高くなるほど大きくなる。これは、サージ電圧が、誘導リアクタンスと電流の時間微分(di/dt)との積に依存するためである。トランジスタ33a、33bがFETの場合、スイッチング速度が高くなるためスイッチング時における電流の時間微分は増大するが、本実施の形態に係るパワー半導体モジュール1のように、対向する領域において逆向きの電流が流れるような構成を採用することで、回路の誘導リアクタンスを十分に低減してサージ電圧を抑制できる。このため、当該構成は、スイッチング速度が高いトランジスタを用いる場合に特に効果的である。

本実施の形態に係るパワー半導体モジュール1において、第3導電層23は、第2セラミック基板12によって第1導電層21及び第2導電層22と絶縁されている。これにより、第3導電層23と、第1導電層21及び第2導電層22との導通を遮断でき、放熱部材41への接触による感電を防止できる。このような感電防止対策は、鉄道車両や自動車などの安全性が重要な分野において特に有効である。なお、感電を確実に防止するためには、第3導電層23はグランドに接続しておくことが好ましい。

本実施の形態に係るパワー半導体モジュール1では、ダイオード32aの上面において露出するアノードと、金属板21cとが、トランジスタ33aの上面において露出するソース端子と接続されている。また、ダイオード32bの上面において露出するアノードと、金属板21dとが、トランジスタ33bの上面において露出するソース端子と接続されている。これにより、ダイオード32aのアノードと金属板21cとを直接的に接続する場合、又はダイオード32bのアノードと金属板21dとを直接的に接続する場合と比較して、ワイヤボンディングの面積を縮小できる。例えば、ダイオード32bのアノードと金属板21dとが直接的に接続されている場合、金属板21dには、トランジスタ33bのソース端子と金属板21dとを接続する導電性ワイヤ、及びダイオード32bのアノードと金属板21dとを接続する導電性ワイヤが接続されるため、金属板21dにはある程度の面積が必要になる。一方、本実施の形態に係る構成の場合、金属板21dには、トランジスタ33bのソース端子と金属板21dとを接続する導電性ワイヤのみが接続されるため、金属板21dの面積を縮小できる。これにより、パワー半導体モジュールを小型化することが可能である。

図6は、本実施の形態に係るパワー半導体モジュールの変形例を示す模式図である。図6に示されるパワー半導体モジュール1aの基本的な構成は、パワー半導体モジュール1と共通している。本実施の形態に係るパワー半導体モジュール1aと、パワー半導体モジュール1との主要な相違点は、第1セラミック基板11の大きさ、及び第1導電層21と第2導電層22の接続部分の構造である。

本実施の形態に係るパワー半導体モジュール1aにおいて、第1セラミック基板11は、第2セラミック基板12より一回り小さくなっており、図面の左右方向(X方向)の幅が短い。これにより、第2導電層22の両端部において上面の一部が露出している。また、導電性ワイヤ34eによって、トランジスタ33bのソース端子と、第2導電層22を構成する金属板の一端部において露出している部分とが接続されており、これに伴い、金属板21dが省略されている。また、導電性ワイヤ34gによって、第2導電層22を構成する金属板の他端部において露出している部分と、金属板21aとが接続されている。つまり、本実施の形態において、導電性ワイヤ34e、及び導電性ワイヤ34gが接続部材として機能する。このように、ワイヤボンディングによって第1導電層21と第2導電層22とを電気的に接続する場合、第1セラミック基板においてスルーホール、及び接続部材を設けずに済むため、製造工程を簡略化することが可能である。

このような構成のパワー半導体モジュール1aにおいてもパワー半導体モジュール1と同様の効果を得ることができる。

以上、本発明の構成によれば、シリコンよりバンドギャップの広い材料で構成されたトランジスタを用いることにより、オン抵抗が小さくなり、高温においても所望する動作が可能になるため、大型の放熱部材を用いることなく動作可能なパワー半導体モジュールを実現できる。また、第1導電層、及び第2導電層の対向する部分に略逆向きの電流変化が生じるように構成されているため、相互インダクタンスにより回路の誘導リアクタンスを低減してサージ電圧を抑制できる。これにより、トランジスタの持つ特性を十分に活かし、高い性能を発揮可能なパワー半導体モジュールを実現できる。

なお、本発明は上記実施の形態に限定されず、さまざまに変更して実施可能である。例えば、トランジスタとしてIGBTを用いても良い。上記実施の形態において、添付図面に図示されている大きさや形状などについては、これに限定されず、本発明の効果を発揮する範囲内で適宜変更が可能である。その他、本発明の目的の範囲を逸脱しない限りにおいて適宜変更して実施可能である。

本出願は、2011年8月1日出願の特願2011-168469に基づく。この内容は、全てここに含めておく。

Claims (6)

- 第1セラミック基板と、

前記第1セラミック基板の一方の主面に配置された第1導電層と、

前記第1セラミック基板の他方の主面において前記第1導電層と対向する領域に配置された第2導電層と、

シリコンよりバンドギャップの広い材料で構成され、前記第1導電層の表面に配置されたトランジスタと、

前記トランジスタのスイッチングによって前記第1導電層及び前記第2導電層に逆向きの電流変化が発生するように前記第1導電層と前記第2導電層とを電気的に接続する接続部材と、

前記第2導電層の表面に一方の主面が接触するように配置された第2セラミック基板と、

前記第2導電層と絶縁されるように前記第2セラミック基板の他方の主面に配置された第3導電層と、を備えたことを特徴とするパワー半導体モジュール。 - 前記第3導電層の表面に接する放熱部材を備えたことを特徴とする請求項1に記載のパワー半導体モジュール。

- 前記トランジスタは、電界効果型トランジスタ又はIGBTであることを特徴とする請求項1に記載のパワー半導体モジュール。

- 前記トランジスタは、200℃以上の温度条件において使用可能なワイドバンドギャップ材料で構成されたことを特徴とする請求項1に記載のパワー半導体モジュール。

- 前記第1導電層は、第1部材及び当該第1部材と離間して配置された第2部材とで構成され、

前記第1部材の表面には第1トランジスタ及び第1ダイオードが配置され、

前記第1トランジスタと前記第1ダイオードとは、第1導電性ワイヤにより接続され、

前記第1トランジスタと第2部材とは、第2導電性ワイヤにより接続されていることを特徴とする請求項1から請求項4のいずれかに記載のパワー半導体モジュール。 - 前記第1導電層は、第1部材及び当該第1部材と離間して配置された第2部材とで構成され、

前記第1部材の表面には第1トランジスタ及び第1ダイオードが配置され、

前記第2部材の表面には第2トランジスタ及び第2ダイオードが配置され、

前記第1部材は、前記第1トランジスタの第1端子及び前記第1ダイオードの第1端子と接続され、

前記第1トランジスタの第2端子及び前記第1ダイオードの第2端子は、前記第2部材と接続され、

前記第2部材は、前記第2トランジスタの第1端子及び前記第2ダイオードの第1端子と接続され、

前記第2トランジスタの第2端子及び前記第2ダイオードの第2端子は、前記接続部材と接続されていることを特徴とする請求項1から請求項4のいずれかに記載のパワー半導体モジュール。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011168469A JP2013033812A (ja) | 2011-08-01 | 2011-08-01 | パワー半導体モジュール |

| JP2011-168469 | 2011-08-01 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| WO2013018811A1 true WO2013018811A1 (ja) | 2013-02-07 |

Family

ID=47629332

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| PCT/JP2012/069512 WO2013018811A1 (ja) | 2011-08-01 | 2012-07-31 | パワー半導体モジュール |

Country Status (2)

| Country | Link |

|---|---|

| JP (1) | JP2013033812A (ja) |

| WO (1) | WO2013018811A1 (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2014091608A1 (ja) * | 2012-12-13 | 2014-06-19 | 株式会社 日立製作所 | パワー半導体モジュール及びこれを用いた電力変換装置 |

| WO2014184030A1 (de) * | 2013-05-14 | 2014-11-20 | Audi Ag | Vorrichtung und elektrische baugruppe zum wandeln einer gleichspannung in eine wechselspannung |

| CN110783323A (zh) * | 2019-09-10 | 2020-02-11 | 杭州泰昕微电子有限公司 | 一种应用于逆变焊机的大功率集成器件 |

| US10811329B2 (en) | 2015-02-17 | 2020-10-20 | Koninklijke Philips N.V. | Ceramic substrate and method for producing a ceramic substrate |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5566354B2 (ja) * | 2011-09-06 | 2014-08-06 | 三菱電機株式会社 | 電力用半導体スイッチおよび電力変換装置 |

| JP6331543B2 (ja) * | 2014-03-24 | 2018-05-30 | 日産自動車株式会社 | ハーフブリッジパワー半導体モジュール及びその製造方法 |

| WO2016002385A1 (ja) * | 2014-07-03 | 2016-01-07 | 日産自動車株式会社 | ハーフブリッジパワー半導体モジュール及びその製造方法 |

| CN107155372B (zh) | 2014-11-28 | 2019-10-01 | 日产自动车株式会社 | 半桥功率半导体模块及其制造方法 |

| WO2017002390A1 (ja) * | 2015-06-30 | 2017-01-05 | シャープ株式会社 | 回路モジュール |

| JP6468984B2 (ja) | 2015-10-22 | 2019-02-13 | 三菱電機株式会社 | 半導体装置 |

| WO2017090281A1 (ja) * | 2015-11-25 | 2017-06-01 | シャープ株式会社 | モジュール基板 |

| JP6623283B2 (ja) * | 2016-03-24 | 2019-12-18 | 株式会社日立製作所 | パワー半導体モジュール |

| JP7337711B2 (ja) * | 2020-01-09 | 2023-09-04 | 三菱電機株式会社 | 半導体装置 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002373971A (ja) * | 2001-03-30 | 2002-12-26 | Hitachi Ltd | 半導体装置 |

| JP2003168777A (ja) * | 2001-11-30 | 2003-06-13 | Kyocera Corp | インバータ制御モジュール |

| JP2009182261A (ja) * | 2008-01-31 | 2009-08-13 | Rohm Co Ltd | 半導体装置 |

| JP2011142172A (ja) * | 2010-01-06 | 2011-07-21 | Mitsubishi Electric Corp | 電力用半導体装置 |

-

2011

- 2011-08-01 JP JP2011168469A patent/JP2013033812A/ja not_active Withdrawn

-

2012

- 2012-07-31 WO PCT/JP2012/069512 patent/WO2013018811A1/ja active Application Filing

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002373971A (ja) * | 2001-03-30 | 2002-12-26 | Hitachi Ltd | 半導体装置 |

| JP2003168777A (ja) * | 2001-11-30 | 2003-06-13 | Kyocera Corp | インバータ制御モジュール |

| JP2009182261A (ja) * | 2008-01-31 | 2009-08-13 | Rohm Co Ltd | 半導体装置 |

| JP2011142172A (ja) * | 2010-01-06 | 2011-07-21 | Mitsubishi Electric Corp | 電力用半導体装置 |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2014091608A1 (ja) * | 2012-12-13 | 2014-06-19 | 株式会社 日立製作所 | パワー半導体モジュール及びこれを用いた電力変換装置 |

| WO2014184030A1 (de) * | 2013-05-14 | 2014-11-20 | Audi Ag | Vorrichtung und elektrische baugruppe zum wandeln einer gleichspannung in eine wechselspannung |

| US9742312B2 (en) | 2013-05-14 | 2017-08-22 | Audi Ag | Apparatus and electrical assembly for converting a direct voltage into an alternating voltage |

| US10811329B2 (en) | 2015-02-17 | 2020-10-20 | Koninklijke Philips N.V. | Ceramic substrate and method for producing a ceramic substrate |

| CN110783323A (zh) * | 2019-09-10 | 2020-02-11 | 杭州泰昕微电子有限公司 | 一种应用于逆变焊机的大功率集成器件 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2013033812A (ja) | 2013-02-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| WO2013018811A1 (ja) | パワー半導体モジュール | |

| JP6513303B2 (ja) | 電力用半導体モジュールおよび電力変換装置 | |

| US8987777B2 (en) | Stacked half-bridge power module | |

| CN103782380B (zh) | 半导体模块 | |

| US20170345792A1 (en) | Half-bridge power semiconductor module and method of manufacturing same | |

| WO2016002385A1 (ja) | ハーフブリッジパワー半導体モジュール及びその製造方法 | |

| JP2010016947A (ja) | 電力変換装置のパワーモジュール | |

| US10943891B2 (en) | Semiconductor module and power conversion apparatus | |

| US9812411B2 (en) | Semiconductor device, inverter circuit, and drive device | |

| US20220263425A1 (en) | Electric circuit device | |

| JP2007215302A (ja) | インバータ装置 | |

| JP2007281090A (ja) | ワイドギャップ複合半導体装置 | |

| JP2021141221A (ja) | 半導体モジュール | |

| EP1657750B1 (en) | Semiconductor device | |

| US11973064B2 (en) | Semiconductor power module | |

| JP6763246B2 (ja) | 半導体装置 | |

| US10855196B2 (en) | Semiconductor device | |

| WO2020174741A1 (ja) | 半導体装置 | |

| JP5925328B2 (ja) | パワー半導体モジュール | |

| JP6665804B2 (ja) | 半導体装置 | |

| JP2014072385A (ja) | 半導体装置 | |

| KR102413991B1 (ko) | Pcb 일체형 고속 스위칭 전력변환 장치 | |

| JP7421259B2 (ja) | 電力変換装置 | |

| US20240282662A1 (en) | Power module | |

| US11276627B2 (en) | Semiconductor device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| 121 | Ep: the epo has been informed by wipo that ep was designated in this application |

Ref document number: 12820678 Country of ref document: EP Kind code of ref document: A1 |

|

| NENP | Non-entry into the national phase |

Ref country code: DE |

|

| 122 | Ep: pct application non-entry in european phase |

Ref document number: 12820678 Country of ref document: EP Kind code of ref document: A1 |