WO2010100848A1 - 符号化器、復号化器及び符号化方法 - Google Patents

符号化器、復号化器及び符号化方法 Download PDFInfo

- Publication number

- WO2010100848A1 WO2010100848A1 PCT/JP2010/001099 JP2010001099W WO2010100848A1 WO 2010100848 A1 WO2010100848 A1 WO 2010100848A1 JP 2010001099 W JP2010001099 W JP 2010001099W WO 2010100848 A1 WO2010100848 A1 WO 2010100848A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- information

- coding rate

- ldpc

- parity

- time

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Ceased

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/033—Theoretical methods to calculate these checking codes

- H03M13/036—Heuristic code construction methods, i.e. code construction or code search based on using trial-and-error

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/11—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits using multiple parity bits

- H03M13/1102—Codes on graphs and decoding on graphs, e.g. low-density parity check [LDPC] codes

- H03M13/1105—Decoding

- H03M13/1111—Soft-decision decoding, e.g. by means of message passing or belief propagation algorithms

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/11—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits using multiple parity bits

- H03M13/1102—Codes on graphs and decoding on graphs, e.g. low-density parity check [LDPC] codes

- H03M13/1148—Structural properties of the code parity-check or generator matrix

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/11—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits using multiple parity bits

- H03M13/1102—Codes on graphs and decoding on graphs, e.g. low-density parity check [LDPC] codes

- H03M13/1148—Structural properties of the code parity-check or generator matrix

- H03M13/1154—Low-density parity-check convolutional codes [LDPC-CC]

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/25—Error detection or forward error correction by signal space coding, i.e. adding redundancy in the signal constellation, e.g. Trellis Coded Modulation [TCM]

- H03M13/255—Error detection or forward error correction by signal space coding, i.e. adding redundancy in the signal constellation, e.g. Trellis Coded Modulation [TCM] with Low Density Parity Check [LDPC] codes

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/37—Decoding methods or techniques, not specific to the particular type of coding provided for in groups H03M13/03 - H03M13/35

- H03M13/3723—Decoding methods or techniques, not specific to the particular type of coding provided for in groups H03M13/03 - H03M13/35 using means or methods for the initialisation of the decoder

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/63—Joint error correction and other techniques

- H03M13/635—Error control coding in combination with rate matching

- H03M13/6362—Error control coding in combination with rate matching by puncturing

- H03M13/6368—Error control coding in combination with rate matching by puncturing using rate compatible puncturing or complementary puncturing

- H03M13/6393—Rate compatible low-density parity check [LDPC] codes

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/65—Purpose and implementation aspects

- H03M13/6508—Flexibility, adaptability, parametrability and configurability of the implementation

- H03M13/6516—Support of multiple code parameters, e.g. generalized Reed-Solomon decoder for a variety of generator polynomials or Galois fields

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/0001—Systems modifying transmission characteristics according to link quality, e.g. power backoff

- H04L1/0009—Systems modifying transmission characteristics according to link quality, e.g. power backoff by adapting the channel coding

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0041—Arrangements at the transmitter end

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0045—Arrangements at the receiver end

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0056—Systems characterized by the type of code used

- H04L1/0057—Block codes

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0056—Systems characterized by the type of code used

- H04L1/0057—Block codes

- H04L1/0058—Block-coded modulation

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0056—Systems characterized by the type of code used

- H04L1/0059—Convolutional codes

Definitions

- the present invention relates to an encoder, a decoder, and an encoding method using a low density parity check convolutional code (LDPC-CC: Low Density Parity Check-Convolutional Codes) that can support a plurality of coding rates.

- LDPC-CC Low Density Parity Check-Convolutional Codes

- LDPC low density parity check

- the LDPC code is an error correction code defined by a low-density parity check matrix H.

- the LDPC code is a block code having a block length equal to the number N of columns of the parity check matrix H.

- Non-Patent Document 1, Non-Patent Document 2, Non-Patent Document 3, and Non-Patent Document 4 propose a random LDPC code, Array LDPC code, and QC-LDPC code (QC: Quasi-Cyclic).

- LDPC-BC Low-Density Parity-Check Block Code

- LDPC-CC Low-Density Parity-Check Convolutional Codes

- LDPC-CC is a convolutional code defined by a low-density parity check matrix.

- M represents the memory length in the LDPC-CC

- n represents the length of the code word in the LDPC-CC.

- 1 is arranged only in the diagonal term of the matrix and its neighboring elements, the lower left and upper right elements of the matrix are zero, and the parallelogram There is a feature that it is a matrix of shape.

- the LDPC-CC encoder defined by the parity check matrix H T [0, n] T Is represented in FIG.

- the LDPC-CC encoder includes a shift register M + 1 with a bit length c and a mod2 adder (exclusive OR operator).

- the LDPC-CC encoder is realized by a very simple circuit compared to a circuit that performs multiplication of a generator matrix and an LDPC-BC encoder that performs an operation based on the backward (forward) substitution method.

- FIG. 2 shows a convolutional code encoder, it is not necessary to divide the information sequence into fixed-length blocks and encode it, and an information sequence of an arbitrary length can be encoded.

- Non-Patent Document 8 shows that puncturing is used to support a plurality of coding rates.

- a base code that is, a mother code

- an encoded sequence in the mother code is created, and transmission is not performed from the encoded sequence (puncture).

- Select a bit By changing the number of bits that are not transmitted, a plurality of coding rates are supported.

- both the encoder and the decoder can cope with all coding rates by using the encoder and decoder for the mother code, which has the advantage that the operation scale (circuit scale) can be reduced. .

- a method for dealing with a plurality of coding rates there is a method of preparing different codes for each coding rate (Distributed Codes).

- distributed Codes distributed Codes

- a method of dealing with a plurality of coding rates with a plurality of codes is general because of the flexibility of easily configuring various code lengths and coding rates.

- the operation scale circuit scale

- the data reception quality is very good as compared with the case where a plurality of coding rates are supported by puncturing.

- the operation scale of the encoder and the decoder is ensured while ensuring the reception quality of the data by preparing a plurality of codes to cope with a plurality of coding rates.

- LDPC code generation methods that can reduce the amount of data, and if an LDPC code creation method that can achieve this is established, improvement of data reception quality and reduction of the computation scale, which have been difficult to achieve until now, have been achieved. Coexistence is possible.

- LDPC-CC is a kind of convolutional code

- termination and tail biting are required to ensure reliability in decoding information bits.

- sufficient studies have not been made on the LDPC-CC and its encoder and decoder that can reduce the number of terminations as much as possible while ensuring the data reception quality.

- An object of the present invention is to prevent deterioration in error correction capability and avoid reduction in information transmission efficiency even when termination is performed in an encoder and a decoder using LDPC-CC.

- An encoder, a decoder, and an encoding method are provided.

- An encoder is an encoder that performs LDPC-CC encoding, and includes a termination sequence transmitted after being added to the tail of the information sequence according to the information length and coding rate of the information sequence.

- a determination means for determining a sequence length; and LDPC-CC encoding is performed on the information sequence and a known information sequence necessary for generating the termination sequence for the determined sequence length, and a parity sequence is calculated And a calculating means.

- the decoder of the present invention is a decoder that decodes LDPC-CC using reliability propagation, and includes a coding rate, a sequence length of a termination sequence transmitted after being added to the tail of an information sequence, and And a decoding unit that performs reliability propagation decoding on the information sequence based on the coding rate and the termination sequence length.

- the encoding method of the present invention determines a sequence length of a termination sequence to be transmitted by adding to the tail of the information sequence according to an information length and a coding rate of the information sequence, and determines the information sequence and

- the parity information is calculated by applying LDPC-CC coding to the known information sequence necessary for generating the termination sequence for the sequence length.

- the encoder the decoder and the encoding method of the present invention, even when termination is performed, the error correction capability is not deteriorated and a decrease in information transmission efficiency can be avoided.

- the figure which shows the parity check matrix of LDPC-CC The figure which shows the structure of a LDPC-CC encoder The figure which shows an example of a structure of the parity check matrix of LDPC-CC of time-varying period 4 The figure which shows the structure of the parity check polynomial and parity check matrix H of LDPC-CC of time-varying period 3 The figure which shows the relationship of the reliability propagation

- FIG. 9 is a block diagram showing a main configuration of a parity operation unit according to the third embodiment.

- FIG. 9 is a block diagram showing another main configuration of the encoder according to Embodiment 3.

- FIG. 9 is a block diagram showing a main configuration of a decoder according to the third embodiment.

- FIG. Diagram showing an example of transmission format The figure which shows an example of a structure of the communication apparatus carrying the encoder which concerns on Embodiment 3.

- FIG. Diagram showing an example of transmission format The figure which shows an example of a structure of the communication apparatus carrying the decoder which concerns on Embodiment 3.

- FIG. The figure which shows an example of the relationship between information size and the number of terminations

- the figure which shows an example of the relationship between information size and the number of terminations The block diagram which shows the principal part structure of the communication apparatus carrying the encoder which concerns on Embodiment 5 of this invention. Diagram for explaining how to determine the termination sequence length Diagram for explaining how to determine the termination sequence length Diagram showing an example of transmission format

- FIG. 7 is a block diagram showing a main configuration of a communication apparatus equipped with a decoder according to the fifth embodiment.

- the figure which shows an example of the flow of the information between the communication apparatus which mounts an encoder, and the communication apparatus which mounts a decoder The figure which shows an example of the flow of the information between the communication apparatus which mounts an encoder, and the communication apparatus which mounts a decoder

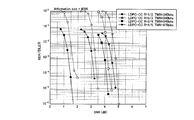

- the figure which shows an example of the correspondence table which shows the relationship between information size and the number of terminations The figure which shows the BER / BLER characteristic at the time of adding a termination series to the information series whose information size is 512 bits

- the figure which shows the BER / BLER characteristic at the time of adding a termination series to the information series whose information size is 1024 bits

- the figure which shows the BER / BLER characteristic at the time of adding a termination series to the information series whose information size is 2048 bits

- FIG. 9 is a block diagram showing a main configuration of a communication apparatus equipped with a decoder according to the sixth embodiment.

- the block diagram which shows the principal part structure of the encoder based on Embodiment 7 of this invention

- the block diagram which shows the principal part structure of the decoder which concerns on Embodiment 7.

- the block diagram which shows the principal part structure of the encoder which concerns on Embodiment 8 of this invention.

- LDPC-CC with good characteristics The LDPC-CC having a time varying period g with good characteristics will be described below.

- Formulas (1-1) to (1-4) are considered as parity check polynomials for LDPC-CC with a time-varying period of 4.

- X (D) is a polynomial expression of data (information)

- P (D) is a polynomial expression of parity.

- the parity check polynomial is such that there are four terms in each of X (D) and P (D). This is because it is preferable to obtain four terms.

- a1, a2, a3, and a4 are integers (however, a1 ⁇ a2 ⁇ a3 ⁇ a4, and all of a1 to a4 are different).

- X, Y,. B1, b2, b3, and b4 are integers (where b1 ⁇ b2 ⁇ b3 ⁇ b4).

- the parity check polynomial of equation (1-1) is referred to as “check equation # 1”, and a sub-matrix based on the parity check polynomial of equation (1-1) is defined as a first sub-matrix H 1 .

- A1, A2, A3, and A4 are integers (however, A1 ⁇ A2 ⁇ A3 ⁇ A4).

- B1, B2, B3, and B4 are integers (B1 ⁇ B2 ⁇ B3 ⁇ B4).

- check equation # 2 the sub-matrix based on a parity check polynomial of equation (1-2), the second sub-matrix H 2.

- Equation (1-3) ⁇ 1, ⁇ 2, ⁇ 3, and ⁇ 4 are integers (where ⁇ 1 ⁇ ⁇ 2 ⁇ ⁇ 3 ⁇ ⁇ 4). ⁇ 1, ⁇ 2, ⁇ 3, and ⁇ 4 are integers (where ⁇ 1 ⁇ ⁇ 2 ⁇ ⁇ 3 ⁇ ⁇ 4).

- the parity check polynomial of equation (1-3) is called “check equation # 3”, and the sub-matrix based on the parity check polynomial of equation (1-3) is referred to as a third sub-matrix H 3 .

- Equation (1-4) E1, E2, E3, and E4 are integers (however, E1 ⁇ E2 ⁇ E3 ⁇ E4). Further, F1, F2, F3, and F4 are integers (where F1 ⁇ F2 ⁇ F3 ⁇ F4).

- the parity check polynomial of equation (1-4) is called “check equation # 4”, and the sub-matrix based on the parity check polynomial of equation (1-4) is referred to as a fourth sub-matrix H 4 .

- an LDPC-CC with a time varying period of 4 that generates a parity check matrix as shown in FIG. 3 from the first sub-matrix H 1 , the second sub-matrix H 2 , the third sub-matrix H 3 , and the fourth sub-matrix H 4 think about.

- each order The remainder k obtained by dividing (a1, a2, a3, a4) by 4 becomes (0, 3, 2, 1), and the remainder (k) 0, 1, 2, 3 is one by one in the four coefficient sets. To be included.

- a regular LDPC code can be formed in which the column weight of the parity check matrix H composed of the equations (1-1) to (1-4) is 4 in all columns.

- the regular LDPC code is an LDPC code defined by a parity check matrix in which each column weight is constant, and has characteristics that characteristics are stable and an error floor is difficult to occur.

- the column weight is 4, the characteristics are good, so that LDPC-CC with good reception performance can be obtained by generating LDPC-CC as described above.

- Table 1 is an example of LDPC-CC (LDPC-CC # 1 to # 3) having a time-varying period of 4 and a coding rate of 1 ⁇ 2, in which the condition regarding the “remainder” is satisfied.

- an LDPC-CC with a time varying period of 4 is defined by four parity check polynomials of “check polynomial # 1”, “check polynomial # 2”, “check polynomial # 3”, and “check polynomial # 4”.

- the case where the coding rate is 1 ⁇ 2 has been described as an example.

- the coding rate is (n ⁇ 1) / n

- the information X1 (D), X2 (D) In each of the four coefficient sets in 1 (D), if the above-mentioned condition relating to the “remainder” is satisfied, it becomes a regular LDPC code, and good reception quality can be obtained.

- equations (2-1) and (2-2) are considered.

- X (D) is a polynomial expression of data (information)

- P (D) is a polynomial expression of parity.

- the parity check polynomial is such that four terms exist in each of X (D) and P (D). This is because it is preferable to obtain four terms in order to obtain.

- a1, a2, a3, and a4 are integers (where a1 ⁇ a2 ⁇ a3 ⁇ a4).

- B1, b2, b3, and b4 are integers (where b1 ⁇ b2 ⁇ b3 ⁇ b4).

- the parity check polynomial of equation (2-1) is referred to as “check equation # 1”, and the sub-matrix based on the parity check polynomial of equation (2-1) is defined as a first sub-matrix H 1 .

- A1, A2, A3, and A4 are integers (however, A1 ⁇ A2 ⁇ A3 ⁇ A4).

- B1, B2, B3, and B4 are integers (B1 ⁇ B2 ⁇ B3 ⁇ B4).

- check equation # 2 the sub-matrix based on a parity check polynomial of equation (2-2), the second sub-matrix H 2.

- each order The remainder k obtained by dividing (a1, a2, a3, a4) by 4 becomes (0, 3, 2, 1), and the remainder (k) 0, 1, 2, 3 is one by one in the four coefficient sets. To be included.

- a regular LDPC code can be formed in which the column weights of the parity check matrix H composed of equations (2-1) and (2-2) are 4 in all columns.

- the regular LDPC code is an LDPC code defined by a parity check matrix in which each column weight is constant, and has characteristics that characteristics are stable and an error floor is difficult to occur.

- the row weight is 8

- the characteristics are good, so that the LDPC-CC that can further improve the reception performance can be obtained by generating the LDPC-CC as described above.

- Table 2 shows an example of LDPC-CC (LDPC-CC # 1, # 2) with a time-varying period of 2 and a coding rate of 1 ⁇ 2, in which the condition regarding the “remainder” is satisfied.

- an LDPC-CC with a time-varying period of 2 is defined by two parity check polynomials of “check polynomial # 1” and “check polynomial # 2”.

- Formulas (3-1) to (3-3) are considered as parity check polynomials for LDPC-CC with a time-varying period of 3.

- X (D) is a polynomial expression of data (information)

- P (D) is a polynomial expression of parity.

- the parity check polynomial is such that three terms exist in each of X (D) and P (D).

- a1, a2, and a3 are integers (where a1 ⁇ a2 ⁇ a3).

- B1, b2, and b3 are integers (where b1 ⁇ b2 ⁇ b3).

- the parity check polynomial of equation (3-1) is referred to as “check equation # 1”, and the sub-matrix based on the parity check polynomial of equation (3-1) is referred to as a first sub-matrix H 1 .

- equation (3-2) A1, A2, and A3 are integers (where A1 ⁇ A2 ⁇ A3).

- B1, B2, and B3 are integers (B1 ⁇ B2 ⁇ B3).

- check equation # 2 the sub-matrix based on a parity check polynomial of equation (3-2), the second sub-matrix H 2.

- ⁇ 1, ⁇ 2, and ⁇ 3 are integers (where ⁇ 1 ⁇ ⁇ 2 ⁇ ⁇ 3).

- ⁇ 1, ⁇ 2, and ⁇ 3 are integers (where ⁇ 1 ⁇ ⁇ 2 ⁇ ⁇ 3).

- the parity check polynomial of equation (3-3) is called “check equation # 3”, and the sub-matrix based on the parity check polynomial of equation (3-3) is referred to as a third sub-matrix H 3 .

- FIG. 4A shows a configuration of an LDPC-CC parity check polynomial and parity check matrix H of time-varying period 3.

- the example of the LDPC-CC with the time-varying period 3 shown in FIG. 4A is the above-mentioned condition relating to the “remainder”, that is, (a1% 3, a2% 3, a3% 3), (b1% 3, b2% 3, b3% 3), (A1% 3, A2% 3, A3% 3), (B1% 3, B2% 3, B3% 3), ( ⁇ 1% 3, ⁇ 2% 3, ⁇ 3% 3), ( ⁇ 1% 3, ⁇ 2% 3, ⁇ 3% 3) are (0, 1, 2), (0, 2, 1), (1, 0, 2), (1, 2, 0), (2, 0 1), (2, 1, 0) is satisfied.

- “1” in the region 6502 in which the remainder is 1 in the coefficient of “check equation # 1” is a region in which the remainder is 2 in the coefficient of “check equation # 2” in the column calculation of the column 6509 in BP decoding.

- the reliability is propagated from “1” of 6507 “1” and “1” of the region 6508 in which the remainder is 0 in the coefficient of “checking formula # 3”.

- “1” in the region 6503 in which the remainder is 2 in the coefficient of “check equation # 1” is a region in which the remainder is 0 in the coefficient of “check equation # 2” in the column calculation of the column 6512 in BP decoding.

- the reliability is propagated from “1” of 6510 “1” and “1” of the region 6511 in which the remainder is 1 in the coefficient of “check equation # 3”.

- FIG. 4B shows the relationship of reliability propagation between the terms relating to X (D) of “checking formula # 1” to “checking formula # 3” in FIG. 4A.

- the terms (a3, A3, ⁇ 3) enclosed by squares indicate coefficients with a remainder of 0 divided by 3. Further, the terms (a2, A2, ⁇ 1) surrounded by circles indicate a coefficient whose remainder is 1 after dividing by 3. In addition, the terms (a1, A1, ⁇ 2) surrounded by rhombuses indicate coefficients with a remainder of 2 divided by 3.

- FIG. 4B shows the relationship of reliability propagation between the terms related to X (D) of “checking formula # 1” to “checking formula # 3”, but the same applies to the terms related to P (D). I can say that.

- the reliability is propagated to the “checking formula # 1” from the coefficients having the remainders of 0, 1, and 2 divided by 3 among the coefficients of the “checking formula # 2”. That is, the reliability is propagated to the “checking formula # 1” from the coefficients of the “checking formula # 2” that are all different in the remainder after division by 3. Therefore, all the reliability levels with low correlation are propagated to “check formula # 1”.

- the reliability is propagated to the “checking formula # 2” from the coefficients of the “checking formula # 1” whose remainders obtained by dividing by 3 are 0, 1, and 2. That is, the reliability is propagated to the “check equation # 2” from the coefficients of the “check equation # 1”, all of which have different remainders after division by 3. Also, the reliability is propagated to “check formula # 2” from the coefficients of which the remainder obtained by dividing by 3 is 0, 1, and 2 among the coefficients of “check formula # 3”. That is, the reliability is propagated to the “check equation # 2” from the coefficients of the “check equation # 3”, all of which have different remainders after division by 3.

- the reliability is propagated to the “checking formula # 3” from the coefficients of which the remainder obtained by dividing by 3 is 0, 1, 2, among the coefficients of the “checking formula # 1”. That is, the reliability is propagated to the “check equation # 3” from the coefficients of the “check equation # 1”, all of which have different remainders after division by 3. Also, the reliability is propagated to “check formula # 3” from the coefficients of which the remainder obtained by dividing by 3 becomes 0, 1 and 2 among the coefficients of “check formula # 2”. That is, the reliability is propagated to the “checking formula # 3” from the coefficients of the “checking formula # 2”, all of which have different remainders after division by 3.

- the reliability is always ensured in all column operations. Since it is propagated, the reliability can be propagated efficiently in all the check expressions, and the error correction capability can be further increased.

- the LDPC-CC having the time varying period 3 has been described by taking the case of the coding rate 1/2 as an example, but the coding rate is not limited to 1/2.

- coding rate (n ⁇ 1) / n (n is an integer of 2 or more)

- each of the three coefficients in information X1 (D), X2 (D),... Xn ⁇ 1 (D) If the condition regarding the “remainder” is satisfied in the set, it becomes a regular LDPC code, and good reception quality can be obtained.

- equations (4-1) to (4-3) are considered.

- X 1 (D), X 2 (D), ⁇ X n-1 (D) is data (information) X 1, X 2, a polynomial representation of ⁇ X n-1

- P (D) is a polynomial expression of parity.

- X 1 (D), X 2 (D),... X n-1 (D), P (D) each have three terms.

- B1, b2, and b3 are integers (where b1 ⁇ b2 ⁇ b3).

- the parity check polynomial of equation (4-1) is referred to as “check equation # 1”, and the sub-matrix based on the parity check polynomial of equation (4-1) is defined as a first sub-matrix H 1 .

- the parity check polynomial of equation (4-2) is “check equation # 2”. call, the sub-matrix based on a parity check polynomial of equation (4-2), the second sub-matrix H 2.

- a sub-matrix based on the parity check polynomial of Equation (4-3) is referred to as a third sub-matrix H 3 .

- Table 3 shows an example of an LDPC-CC (LDPC-CC # 1, # 2, # 3, # 4, # 5) with a time-varying period of 3 and a coding rate of 1 ⁇ 2, where the above-mentioned condition relating to “remainder” holds. , # 6).

- the LDPC-CC with time-varying period 3 is represented by three parity check polynomials of “check (multinomial) equation # 1”, “check (multinomial) equation # 2”, and “check (multinomial) equation # 3”. Defined.

- the following conditions regarding “remainder” are applied to LDPC-CC whose time-varying period is a multiple of 3 (for example, the time-varying period is 6, 9, 12,). Then, it was confirmed that a code with good characteristics can be searched.

- an LDPC-CC having a multiple of the time-varying period 3 having good characteristics will be described. In the following, a case of LDPC-CC with a coding rate of 1/2 and a time varying period of 6 will be described as an example.

- Equations (5-1) to (5-6) are considered as LDPC-CC parity check polynomials with a time-varying period of 6.

- X (D) is a polynomial expression of data (information)

- P (D) is a polynomial expression of parity.

- a1,1, a1,2, a1,3 are integers (where a1,1 ⁇ a1,2 ⁇ a1,3).

- b1,1, b1,2, b1,3 are integers (where b1,1 ⁇ b1,2 ⁇ b1,3).

- the parity check polynomial of equation (5-1) is referred to as “check equation # 1”, and a sub-matrix based on the parity check polynomial of equation (5-1) is referred to as a first sub-matrix H 1 .

- a2, 1, a2, 2, a2, 3 are integers (where a2, 1 ⁇ a2, 2 ⁇ a2, 3).

- b2,1, b2,2, b2,3 are integers (where b2,1 ⁇ b2,2 ⁇ b2,3).

- a3, 1, a3, 2, a3, 3 are integers (where a3, 1 ⁇ a3, 2 ⁇ a3, 3).

- b3, 1, b3, 2, b3, 3 are integers (where b3, 1 ⁇ b3, 2 ⁇ b3, 3).

- the parity check polynomial of equation (5-3) is called “check equation # 3”, and the sub-matrix based on the parity check polynomial of equation (5-3) is referred to as a third sub-matrix H 3 .

- a4, 1, a4, 2, a4, 3 are integers (where a4, 1 ⁇ a4, 2 ⁇ a4, 3).

- b4, 1, b4, 2, b4, 3 are integers (where b4, 1 ⁇ b4, 2 ⁇ b4, 3).

- the parity check polynomial of equation (5-4) is called “check equation # 4”, and the sub-matrix based on the parity check polynomial of equation (5-4) is referred to as a fourth sub-matrix H 4 .

- Equation (5-5) a5, 1, a5, 2, and a5, 3 are integers (where a5, 1 ⁇ a5, 2 ⁇ a5, 3). Also, b5, 1, b5, 2, and b5, 3 are integers (where b5, 1 ⁇ b5, 2 ⁇ b5, 3). Referred to parity check polynomial of equation (5-5) and "check equation # 5", a sub-matrix based on a parity check polynomial of equation (5-5), the fifth sub-matrix H 5.

- a6, 1, a6, 2, a6, 3 are integers (where a6, 1 ⁇ a6, 2 ⁇ a6, 3).

- B6, 1, b6, 2, b6, 3 are integers (where b6, 1 ⁇ b6, 2 ⁇ b6, 3).

- the parity check polynomial of equation (5-6) is called “check equation # 6”, and the sub-matrix based on the parity check polynomial of equation (5-6) is referred to as a sixth sub-matrix H 6 .

- the first sub-matrix H 1, second sub-matrix H 2, third sub-matrix H 3, fourth sub-matrix H 4, fifth sub-matrix H 5, varying period 6 when generating the sixth sub-matrix H 6 Think about LDPC-CC.

- the reliability in “inspection formula # 1 or inspection formula # 4” is accurately compared with “inspection formula # 3”. Or, the reliability in the inspection formula # 6 ”is accurately propagated.

- the reliability in “inspection formula # 1 or inspection formula # 4” is accurately determined, “inspection formula # 2, Or, the reliability in the inspection formula # 5 ”is accurately transmitted.

- the LDPC-CC having the time varying period 6 retains better error correction capability as in the case where the time varying period is 3.

- FIG. 4C shows the relationship of reliability propagation between the terms relating to X (D) of “check equation # 1” to “check equation # 6”.

- FIG. 4C shows the relationship of reliability propagation between the terms related to X (D) in “checking formula # 1” to “checking formula # 6”, but the same applies to the terms related to P (D). I can say that.

- the LDPC-CC with the time varying period 6 has been described by taking the case of the coding rate 1/2 as an example, but the coding rate is not limited to 1/2.

- coding rate (n ⁇ 1) / n (n is an integer of 2 or more)

- each of information X 1 (D), X 2 (D),... X n ⁇ 1 (D) If the condition regarding the “remainder” is satisfied in the three coefficient sets, the possibility of obtaining good reception quality is increased.

- equations (7-1) to (7-6) are considered.

- X 1 (D), X 2 (D),... X n-1 (D) is a polynomial expression of data (information) X1, X2,... Xn-1

- P (D) Is a polynomial representation of parity.

- X 1 (D), X 2 (D),... X n-1 (D), P (D) each have three terms. Let the parity check polynomial exist.

- the parity at time i is Pi and the information is X i, 1 , X i, 2 , ..., represented by X i, n-1 .

- X 1 (D), X 2 (D), ⁇ X n-1 (D) is data (information) X 1, X 2, a polynomial representation of ⁇ X n-1

- P (D) is a polynomial expression of parity.

- X 1 (D), X 2 (D),... X n-1 (D), P (D) each have three terms. Let the parity check polynomial exist.

- the time varying period 3g represented by the parity check polynomials of the equations (9-1) to (9-3g), the coding rate In an LDPC-CC of (n ⁇ 1) / n (n is an integer of 2 or more), if the following condition ( ⁇ condition # 2>) is satisfied, the possibility that higher error correction capability can be obtained increases.

- X 1 (D), X 2 (D), ⁇ X n-1 (D) is data (information) X 1, X 2, a polynomial representation of ⁇ X n-1, P (D) is a polynomial expression of parity.

- X 1 (D), X 2 (D),... X n-1 (D), P (D) each have three terms. Let the parity check polynomial exist.

- a # k, p, 1 % 3, a # k, p, 2 % 3, a # k, p, 3 % 3), ..., (A # k, n-1,1 % 3, a # k, n-1,2 % 3, a # k, n-1,3 % 3) is Any one of (0, 1, 2), (0, 2, 1), (1, 0, 2), (1, 2, 0), (2, 0, 1), (2, 1, 0) Become.

- ⁇ Condition # 3> for Expressions (11-1) to (11-3g) has the same relationship as ⁇ Condition # 2> for Expressions (9-1) to (9-3g). Adding the following condition ( ⁇ condition # 4>) in addition to ⁇ condition # 3> to formulas (11-1) to (11-3g) creates an LDPC-CC with higher error correction capability The possibility of being able to do increases.

- X 1 (D), X 2 (D), ⁇ X n-1 (D) is data (information) X 1, X 2, a polynomial representation of ⁇ X n-1, P (D) is a polynomial expression of parity.

- equations (13-1) to (13-3g) there are three terms in each of X 1 (D), X 2 (D),... X n-1 (D), P (D)

- a term of D 0 exists in X 1 (D), X 2 (D),... X n-1 (D), P (D).

- K 1, 2, 3, ..., 3g

- a # 3g-2, n-1,1 % 3, a # 3g-2, n-1,2 % 3) is One of (1, 2) and (2, 1).

- P 1, 2, 3,..., N ⁇ 1

- a # 3g-1,1,1 % 3, a # 3g-1,1,2 % 3 is One of (1, 2) and (2, 1).

- a # 3g-1,2,1 % 3, a # 3g-1,2,2 % 3) is One of (1, 2) and (2, 1).

- ⁇ Condition # 5> for Expressions (13-1) to (13-3g) has the same relationship as ⁇ Condition # 2> for Expressions (9-1) to (9-3g). If the following condition ( ⁇ condition # 6>) is added to the expressions (13-1) to (13-3g) in addition to ⁇ condition # 5>, an LDPC-CC having high error correction capability can be created. The possibility increases.

- P 1, 2, 3, ..., 3g

- the following conditions are satisfied in the order of X 3 (D) in the equations (13-1) to (13-3g).

- P 1, 2, 3, ..., 3g

- K 1, 2, 3,..., N ⁇ 1

- the following conditions are satisfied in the order of X n-1 (D) in the equations (13-1) to (13-3g).

- ⁇ Condition # 6> instead of ⁇ Condition # 6>, ⁇ Condition # 6 ′> is used, that is, even if ⁇ Condition # 6 ′> is added in addition to ⁇ Condition # 5>, a higher error correction is possible. There is a high possibility that an LDPC-CC having the capability can be created.

- P 1, 2, 3, ..., 3g

- the following conditions are satisfied in the order of X 3 (D) in the equations (13-1) to (13-3g).

- P 1, 2, 3, ..., 3g

- K 1, 2, 3,..., N ⁇ 1 Or ⁇ ⁇ ⁇ Or The following conditions are satisfied in the order of X n-1 (D) in the equations (13-1) to (13-3g).

- the LDPC-CC having a time varying period of 3 g and a coding rate (n ⁇ 1) / n (n is an integer of 2 or more) has been described above.

- X (D) is a polynomial expression of data (information) X

- P (D) is a polynomial expression of parity.

- the parity check polynomial is such that three terms exist in each of X (D) and P (D).

- X (D) is a polynomial expression of data (information) X

- P (D) is a polynomial expression of parity.

- the parity check polynomial is such that three terms exist in each of X and P (D).

- the parity at time i is represented by Pi and the information is represented by X i, 1 .

- (A # 3,1,1 % 3, a # 3,1,2 % 3, a # 3,1,3 % 3) is (0,1,2), (0,2,1), ( 1, 0, 2), (1, 2, 0), (2, 0, 1), (2, 1, 0).

- (A # k, 1,1 % 3, a # k, 1,2 % 3, a # k, 1,3 % 3) is (0,1,2), (0,2,1), ( 1, 0, 2), (1, 2, 0), (2, 0, 1), (2, 1, 0).

- (Thus, k 1, 2, 3,..., 3g) And, ⁇ ⁇ ⁇ And, (A # 3g-2,1,1% 3 , a # 3g-2,1,2% 3, a # 3g-2,1,3% 3) is (0,1,2), (0, 2, 1), (1, 0, 2), (1, 2, 0), (2, 0, 1), (2, 1, 0). And, (A # 3g-1,1,1 % 3, a # 3g-1,1,2 % 3, a # 3g-1,1,3 % 3) is (0,1,2), (0, 2, 1), (1, 0, 2), (1, 2, 0), (2, 0, 1), (2, 1, 0).

- (A # 3g, 1,1 % 3, a # 3g, 1,2 % 3, a # 3g, 1,3 % 3) is (0,1,2), (0,2,1), ( 1, 0, 2), (1, 2, 0), (2, 0, 1), (2, 1, 0).

- the combination of the orders of P (D) satisfies the following condition. (B # 1,1 % 3, b # 1,2 % 3), (B # 2,1 % 3, b # 2,2 % 3), (B # 3, 1 % 3, b # 3, 2 % 3), ... (B # k, 1 % 3, b # k, 2 % 3), ...

- ⁇ Condition # 3-1> for Expressions (17-1) to (17-3g) has the same relationship as ⁇ Condition # 2-1> for Expressions (15-1) to (15-3g). If the following condition ( ⁇ condition # 4-1>) is added to the expressions (17-1) to (17-3g) in addition to ⁇ condition # 3-1>, LDPC having higher error correction capability -Increased possibility of creating CC.

- X (D) is a polynomial expression of data (information) X

- P (D) is a polynomial expression of parity.

- the parity check polynomial is such that three terms exist in each of X (D) and P (D), and X (D) and P (D) Will have a term of D 0 .

- K 1, 2, 3, ..., 3g

- (Thus, k 1, 2, 3,..., 3g) And, ⁇ ⁇ ⁇ And, (A # 3g-2,1,1% 3 , a # 3g-2,1,2% 3) is a one of the (1,2), (2,1). And, (A # 3g-1,1,1 % 3, a # 3g-1,1,2 % 3) is either (1,2) or (2,1). And, (A # 3g, 1,1 % 3, a # 3g, 1,2 % 3) is either (1,2) or (2,1).

- ⁇ Condition # 5-1> for Expressions (19-1) to (19-3g) has the same relationship as ⁇ Condition # 2-1> for Expressions (15-1) to (15-3g).

- ⁇ Condition # 6-1> When the following condition ( ⁇ condition # 6-1>) is added to the expressions (19-1) to (19-3g) in addition to ⁇ condition # 5-1>, LDPC having higher error correction capability -Increased possibility of creating CC.

- the parity check matrix if there is a regularity at the position where “1” exists, there is a high possibility that a good error correction capability can be obtained.

- the parity check matrix is given randomness while having regularity at the position where “1” exists. Therefore, the possibility that a better error correction capability can be obtained increases.

- ⁇ Condition # 6-1> instead of ⁇ Condition # 6-1>, ⁇ Condition # 6'-1> is used. In other words, ⁇ Condition # 6'-1> is added in addition to ⁇ Condition # 5-1> to create a code. Even so, the possibility that an LDPC-CC having higher error correction capability can be created increases.

- Table 4 lists LDPC-CC having a good error correction capability and a coding rate of 1/2 and a time varying period of 6.

- LDPC-CC having a time varying period g with good characteristics has been described above.

- the generation matrix G is obtained corresponding to a parity check matrix H designed in advance.

- FIG. 5 describes information related to the (7, 5) convolutional code.

- the data at the time point i is represented as X i

- the parity is represented as P i

- the transmission sequence W i (X i , P i ).

- a transmission vector w (X 1 , P 1 , X 2 , P 2 ,..., X i , P i ...) T is expressed.

- the parity check matrix H can be expressed as shown in FIG. At this time, the following relational expression (23) is established.

- the parity check matrix H is used, and BP (Belief Propagation) (reliability propagation) decoding as shown in Non-Patent Document 5 to Non-Patent Document 7 and min-sum decoding approximating BP decoding.

- BP Belief Propagation

- Offset BP decoding Normalized BP decoding, shuffled BP decoding, and other decoding using reliability propagation can be performed.

- time-invariant / time-varying LDPC-CC based on convolutional code (coding rate (n-1) / n) (n: natural number))

- coding rate (n-1) / n) (n: natural number)

- the code defined by the parity check matrix based on the parity check polynomial of Equation (24) is referred to herein as time invariant LDPC-CC.

- the information X 1, j , X 2, j ,..., X n ⁇ 1, j and the parity P j at the time point j satisfy the parity check polynomial of Expression (26).

- “j mod m” is a remainder obtained by dividing j by m.

- a code defined by a parity check matrix based on the parity check polynomial of Equation (26) is referred to herein as time-varying LDPC-CC.

- the time-invariant LDPC-CC defined by the parity check polynomial of Equation (24) and the time-varying LDPC-CC defined by the parity check polynomial of Equation (26) sequentially register and exclude parity. It can be easily obtained by logical OR.

- FIG. 6 shows the configuration of an LDPC-CC parity check matrix H with a coding rate of 2/3 and a time-varying period of 2 based on Equations (24) to (26).

- the two check polynomials having different time-varying periods 2 based on the formula (26) are named “check formula # 1” and “check formula # 2”.

- (Ha, 111) is a portion corresponding to “checking formula # 1”

- (Hc, 111) is a portion corresponding to “checking formula # 2”.

- (Ha, 111) and (Hc, 111) are defined as sub-matrices.

- the LDPC-CC parity check matrix H of the proposed time-varying period 2 is divided into the first sub-matrix representing the parity check polynomial of “check equation # 1” and the parity check polynomial of “check equation # 2”. And a second sub-matrix that represents Specifically, in the parity check matrix H, the first sub-matrix and the second sub-matrix are alternately arranged in the row direction. In the case of a coding rate of 2/3, as shown in FIG. 6, in the i-th row and the i + 1-th row, the sub-matrix is shifted to the right by 3 columns.

- the i-th row sub-matrix and the i + 1-th row sub-matrix are different sub-matrices. That is, one of the sub-matrices (Ha, 111) or (Hc, 111) is the first sub-matrix, and the other is the second sub-matrix.

- the parity P mi + 1 at the time point mi + 1 is obtained using the “check equation # 1”

- the parity P mi + 2 at the time point mi + 2 is obtained using the “check equation # 2”

- the parity P mi + m at the time point mi + m is obtained.

- an LDPC-CC obtained using “checking formula #m”.

- Such an LDPC-CC code is The encoder can be easily configured, and the parity can be obtained sequentially. The advantage is that the termination bit can be reduced and the reception quality at the time of puncturing can be improved.

- FIG. 7 shows the configuration of the above parity check matrix of LDPC-CC with a coding rate of 2/3 and a time-varying period m.

- (H 1 , 111) is a portion corresponding to “checking formula # 1”

- (H 2 , 111) is a portion corresponding to “checking formula # 2”

- (H m , 111) is a portion corresponding to “inspection formula #m”.

- (H 1 , 111) is defined as the first sub-matrix

- (H 2 , 111) is defined as the second sub-matrix

- (H m , 111) is defined as the m-th sub-matrix.

- the LDPC-CC parity check matrix H of the proposed time-varying period m is the first sub-matrix representing the parity check polynomial of “check equation # 1” and the parity check polynomial of “check equation # 2”.

- the second sub-matrix can be defined by the m-th sub-matrix representing the parity check polynomial of “check equation #m”.

- the first sub-matrix to the m-th sub-matrix are periodically arranged in the row direction (see FIG. 7). In the case of a coding rate of 2/3, the sub-matrix is shifted to the right by three columns in the i-th row and the i + 1-th row (see FIG. 7).

- the case of the coding rate 2/3 has been described as an example of the time-invariant / time-varying LDPC-CC based on the convolutional code of the coding rate (n ⁇ 1) / n.

- a parity check matrix of time-invariant / time-variant LDPC-CC based on a convolutional code with a coding rate (n ⁇ 1) / n can be created.

- (H 1 , 111) is a portion (first sub-matrix) corresponding to “check equation # 1”, and (H 2 , 111) is “check A part (second sub-matrix) corresponding to “Expression # 2”,..., (H m , 111) is a part (m-th sub-matrix) corresponding to “check expression #m”,

- the number of “1” s excluding H k is n.

- the sub-matrix is shifted to the right by n columns in the i-th row and the i + 1-th row (see FIG. 8).

- the transmit vector u, u (X 1,0, X 2,0, ⁇ , X n-1,0, P 0, X 1,1, X 2,1, ⁇ , X n-1 , 1, P 1, ⁇ , X 1, k, X 2, k, ⁇ , X n-1, k, P k, ⁇ )

- Hu 0 is satisfied ( (Refer Formula (23)).

- the LDPC-CC encoder 100 mainly includes a data operation unit 110, a parity operation unit 120, a weight control unit 130, and a mod2 adder (exclusive OR operation) unit 140.

- the data operation unit 110 includes shift registers 111-1 to 111-M and weight multipliers 112-0 to 112-M.

- the parity operation unit 120 includes shift registers 121-1 to 121-M and weight multipliers 122-0 to 122-M.

- the weight multipliers 112-0 to 112-M and 122-0 to 122-M set the values of h 1 (m) and h 2 (m) to 0/1 according to the control signal output from the weight control unit 130. Switch to.

- the weight control unit 130 outputs the values of h 1 (m) and h 2 (m) at the timing based on the parity check matrix held therein, and the weight multipliers 112-0 to 112-M, 122- Supply toward 0-122-M.

- the mod2 adder 140 adds all the mod2 calculation results to the outputs of the weight multipliers 112-0 to 112-M, 122-0 to 122-M, and calculates p i .

- the LDPC-CC encoder 100 can perform LDPC-CC encoding according to a parity check matrix.

- the LDPC-CC encoder 100 is a time-varying convolutional encoder.

- LDPC-CC with a coding rate (q-1) / q (q-1) data operation units 110 are provided, and a mod2 adder 140 adds mod2 outputs (mod2 addition) (Exclusive OR operation) may be performed.

- an LDPC-CC search method capable of supporting a plurality of coding rates with a low computation scale in the encoder / decoder will be described.

- the decoder can achieve high data reception quality.

- the LDPC-CC search method in the present embodiment is based on, for example, LDPC-CC with a coding rate of 1/2 among LDPC-CCs having good characteristics as described above, and coding rate 2/3, Search sequentially for LDPC-CC of 3/4, 4/5,..., (Q ⁇ 1) / q.

- LDPC-CC coding rate of 1/2 among LDPC-CCs having good characteristics as described above, and coding rate 2/3

- an LDPC-CC with a time varying period of 3 is used as an example.

- the LDPC-CC with the time-varying period 3 has a very good error correction capability.

- LDPC-CC search method (1) Coding rate 1/2 First, an LDPC-CC with a coding rate of 1/2 is selected as a base LDPC-CC. As the base LDPC-CC with a coding rate of 1/2, an LDPC-CC with good characteristics as described above is selected.

- an LDPC-CC parity check polynomial with a coding rate of 2/3 is created based on a parity check polynomial with a coding rate of 1/2 with good characteristics.

- an LDPC-CC parity check polynomial with a coding rate of 2/3 includes a parity check polynomial with a basic coding rate of 1/2.

- a parity check polynomial of an LDPC-CC with a coding rate of 2/3 when the equations (27-1) to (27-3) are used for the base LDPC-CC with a coding rate of 1/2 is expressed by the equation (28-). It can be expressed as 1) to formula (28-3).

- the parity check polynomials shown in the equations (28-1) to (28-3) adopt a configuration in which the term X 2 (D) is added to the equations (27-1) to (27-3), respectively.

- the parity check polynomial of the coding rate 2/3 LDPC-CC using the equations (28-1) to (28-3) is the basis of the parity checking polynomial of the coding rate 3/4 described later.

- the information X 1 and X 2 at the time point j are expressed as X 1, j and X 2, j, and the parity P at the time point j is set as P j

- u j (X 1, j , X 2, j , Pj) T.

- an LDPC-CC parity check polynomial with a coding rate of 3/4 is created based on the parity check polynomial with a coding rate of 2/3.

- an LDPC-CC parity check polynomial with a coding rate of 3/4 includes a parity check polynomial with a basic coding rate of 2/3.

- a parity check polynomial of an LDPC-CC with a coding rate of 3/4 when the equations (28-1) to (28-3) are used for the base LDPC-CC with a coding rate of 2/3 is given by the equation (29- 1) to formula (29-3).

- the parity check polynomials shown in Expressions (29-1) to (29-3) employ a configuration in which the term X 3 (D) is added to Expressions (28-1) to (28-3), respectively. .

- each order of X 3 (D), ( ⁇ 1, ⁇ 1), ( ⁇ 2, ⁇ 2), ( ⁇ 3, ⁇ 3) is LDPC with good characteristics.

- LDPC-CC with good characteristics can be obtained even at a coding rate of 3/4 .

- the information X 1, X 2, X 3 at the time point j is expressed as X 1, j, X 2, j, X 3, j .

- the relationship between the check polynomial and the parity check matrix is the same as that described in the above (LDPC-CC having good characteristics).

- Formulas (30-1) to (30- (q-1)) show general formulas of the parity check polynomial of the LDPC-CC having the time-varying period g when searching as described above.

- Expression (30-1) is expressed by a general expression, it is expressed as the expression (30-1), but as described above (LDPC-CC having good characteristics).

- Expression (30-1) is expressed by g parity check polynomials. (As described in the present embodiment, for example, in the case of time varying period 3, it is expressed by three parity check polynomials as in equations (27-1) to (27-3).)

- the equations (30-2) to (30- (q-1)) are also expressed by g parity check polynomials because the time-varying period is g.

- Equation (30-1) g parity check polynomials of Equation (30-1) are represented by Equation (30-1-0), Equation (30-1-1), Equation (30-1-2),. 30-1- (g-2)) and the expression (30-1- (g-1)).

- g parity check polynomials of the equation (30-w) are expressed by the equation (30-w-0), the equation (30-w-1), the equation (30-w-2),. 30-w- (g-2)) and expression (30-w- (g-1)).

- X 1, i , X 2, i ,..., X q ⁇ 1, i are information X 1 , X 2 ,..., X q ⁇ 1

- P i indicates the parity P at time i.

- Equation (30-1) is an LDPC-CC parity check polynomial of time varying period g corresponding to coding rate 1/2

- Equation (30-2) corresponds to coding rate 2/3

- Equation (30- (q-1)) is LDPC- of time-varying period g corresponding to coding rate (q-1) / q. It is a parity check polynomial of CC.

- Equation (30-1) which is an LDPC-CC parity check polynomial with good coding rate 1/2

- Equation (302) a parity check polynomial of LDPC-CC with coding rate 2/3 ( 30-2) is generated.

- an LDPC-CC parity check polynomial (30-3) with a coding rate of 3/4 is generated based on an LDPC-CC parity check polynomial (30-2) with a coding rate of 2/3.

- Another expression is used for the above parity check polynomial construction method.

- the maximum coding rate is (q ⁇ 1) / q among the coding rates for the common use of the encoder circuit and the common use of the decoder circuit, and g is 2 or more.

- An integer, y is an integer of 2 or more, z is an integer of 2 or more, and a relationship of y ⁇ z ⁇ q is established.

- the sharing of the circuit of the encoder is the sharing of the circuit inside the encoder, not the sharing of the circuit of the encoder and the decoder.

- an LDPC-CC encoder with a time varying period g at a coding rate (y ⁇ 1) / y and a time varying period g at a coding rate (z ⁇ 1) / z

- An LDPC-CC encoder can share a circuit, and an LDPC-CC decoder having a time-varying period g at a coding rate (y-1) / y, and a coding rate (z- 1)

- An LDPC-CC decoder having a time-varying period g at / z can share a circuit.

- the conditions are as follows.

- B 0 and (D) is of formula (31-1) B 0 of (D) and Formula (32-1), equality is established.”

- An LDPC-CC encoder can share a circuit, and an LDPC-CC decoder and a coding rate (z-1) with a time-varying period g at a coding rate (y-1) / y.

- the circuit can be shared with an LDPC-CC decoder having a time-varying period g at) / z.

- the method for sharing the encoder circuit and the method for sharing the decoder circuit will be described in detail later (configuration of the encoder and decoder).

- Table 5 shows an example of an LDPC-CC parity check polynomial satisfying the above-mentioned conditions and having a time-varying period of 3 and corresponding coding rates of 1/2, 2/3, 3/4, and 5/6.

- the format of the parity check polynomial is represented in the same format as that in Table 3.

- a X1,0 (D) in the equation (31-1) becomes D 373 + D 56 +1, and the coding rate in Table 5 is obtained.

- a X1,0 (D) in equation (32-1) becomes D 373 + D 56 +1

- a X1,0 (D) in the equation (32-1) is an equal sign.

- B 0 (D) in Equation (31-1) becomes D 406 + D 218 +1

- a X1,2 (D) in Expression (31-3) becomes D 485 + D 70 +1, and the coding in Table 5 is performed.

- a X1,2 (D) in the equation (32-3) D 485 + D 70 +1, and “A X1,2 in the equation (31-3) ( D) and A X1,2 (D) in equation (32-3) are equal.

- B 2 (D) in the equation (31-3) becomes D 236 + D 181 +1

- the coding rate 2 / 3 B 2 (D) in the equation (32-3) becomes D 236 + D 181 +1

- the LDPC-CC with the time-varying period 3 at the coding rate 1/2 in Table 5 and the LDPC-CC with the time-varying period 3 in the coding rate 2/3 in Table 5 are the above conditions. Can be confirmed.

- the time varying period 3 of two different coding rates out of the coding rates 1/2, 2/3, 3/4, and 5/6. If the LDPC-CC is selected and verification is made as to whether the above condition is satisfied, it can be confirmed that the above condition is satisfied in any selection pattern.

- LDPC-CC is a kind of convolutional code

- termination and tail biting are required to ensure reliability in decoding of information bits.

- Information-zero-termination a method of setting the state of data (information) X to zero (hereinafter referred to as “Information-zero-termination”) is considered.

- Figure 10 shows the “Information-zero-termination” method.

- the information bit (final transmission bit) to be transmitted last in the information sequence to be transmitted is Xn (110).

- the transmission apparatus transmits data only up to the parity bit generated by the encoder in accordance with the final information bit Xn (110)

- the reception apparatus performs decoding, the reception quality of information is greatly deteriorated.

- encoding is performed assuming that the information bits after the last information bit Xn (110) (referred to as “virtual information bits”) are “0”, and a parity bit (130) is generated. To do.

- parity bits (120) generated by virtual information bits (120) while ensuring data reception quality. 130) should be as small as possible.

- LDPC-CC when the time varying period m (m is an integer and m ⁇ 2) and the coding rate is 1/2 will be described as an example.

- the time-varying period is m

- B i (D) D 18 + D 4 + D 0

- the orders that exist for D are all composed of orders of 0 or more, such as 18, 4 , 0).

- the highest order of D in B 1 (D) is ⁇ 1

- the highest order of D in B 2 (D) is ⁇ 2

- the highest order of ⁇ i (D) is the highest order of D in ⁇ m ⁇ 1 .

- ⁇ is 1/2 or less of ⁇ .

- LDPC-CC when the time-varying period m (m is an integer and m ⁇ 2) and the coding rate is 4/5 will be described as an example.

- the required m parity check polynomials are expressed by the following equations.

- i 0, 1,..., M ⁇ 1.

- a X1,2 (D) has the highest order of D as ⁇ 1,2 ,.

- the highest order of D in A X1, i (D) is ⁇ 1, i ,...,

- the highest order of D in A X1, m-1 (D) is ⁇ 1, m-1 .

- the highest order of D in B 1 (D) is ⁇ 1

- the highest order of D in B 2 (D) is ⁇ 2

- B i (D) is the highest in D the degree ⁇ i, ⁇

- the highest order of D in B m-1 (D) and beta m-1 is ⁇ .

- ⁇ is 1/2 or less of ⁇ 1 and ⁇ is ⁇ 2 . It is good to say that it is 1/2 or less, ⁇ is 1/2 or less of ⁇ 3 , and ⁇ is 1/2 or less of ⁇ 4 .

- ⁇ is 1/2 or less of ⁇ 1 or ⁇ is 1/2 or less of ⁇ 2 or ⁇ is 1/2 or less of ⁇ 3 or ⁇ is 1/2 or less of ⁇ 4 ”

- the number of parity bits generated by the virtual information bits can be reduced as much as possible, but there is a possibility that the data reception quality will be slightly reduced (however, However, this does not necessarily lead to a decrease in data reception quality.)

- the required m parity check polynomials are expressed by the following equations.

- i 0, 1,..., M ⁇ 1.

- a X1,2 (D) has the highest order of D as ⁇ 1,2 ,.

- the highest order of D in A X1, i (D) is ⁇ 1, i ,...,

- the highest order of D in A X1, m-1 (D) is ⁇ 1, m-1 .

- the highest order of D in B 1 (D) is ⁇ 1

- the highest order of D in B 2 (D) is ⁇ 2

- B i (D) is the highest in D the degree ⁇ i, ⁇

- the highest order of D in B m-1 (D) and beta m-1 is ⁇ .

- ⁇ is 1 ⁇ 2 or less of ⁇ 1

- ⁇ is 1 ⁇ 2 or less of ⁇ 2

- ⁇ is 1 ⁇ 2 or less of ⁇ u

- Is 1/2 or less of ⁇ n ⁇ 1 (u 1, 2, 3,..., N ⁇ 2, n ⁇ 1) ”

- u 1, 2, 3,..., N ⁇ 2, n ⁇ 1

- Table 6 shows LDPC-CCs with a time-varying period of 3, a coding rate of 1/2, 2/3, 3/4, and 4/5 that can reduce the number of redundant bits while ensuring data reception quality.

- An example of a parity check polynomial is shown.

- the LDPC-CC with time varying period 3 in Table 6 the LDPC-CC with time varying period 3 of two different coding rates out of the coding rates 1/2, 2/3, 3/4, and 4/5.

- the number of redundant bits (redundant bits added for “Information-zero-termination”) required for the code of coding rate (n ⁇ 1) / n is the coding rate (m ⁇ 1) / m. It tends to be more than the number of redundant bits required for a code (redundant bits added for “Information-zero-termination”), and the redundancy required for a code of coding rate (n ⁇ 1) / n When the information size is small, the number of bits tends to be larger than the number of redundant bits necessary for a code of coding rate (m ⁇ 1) / m. However, this is not necessarily the case.

- the maximum coding rate is (q ⁇ 1) / q among the coding rates for the common use of the encoder circuit and the common use of the decoder circuit, and the coding rate (r ⁇ 1)

- At least an LDPC-CC encoder with a time-varying period g of a coding rate (y-1) / y and an LDPC-CC encoder with a time-varying period g of a coding rate (z-1) / z are provided.

- the reception apparatus including the decoder, the method of generating the parity check polynomial of the LDPC-CC having the time-varying period g capable of reducing the operation scale (circuit scale), and the characteristics of the parity check polynomial have been described.

- the transmission apparatus transmits a modulation signal for transmitting an LDPC-CC encoded sequence having at least a coding rate (y ⁇ 1) / y with a time varying period g, or a coding rate (z ⁇ 1) / y

- a modulation signal for transmitting an LDPC-CC encoded sequence having at least a coding rate (y ⁇ 1) / y with a time varying period g, or a coding rate (z ⁇ 1) / y

- the receiving apparatus receives at least a received signal including an LDPC-CC encoded sequence having a time-varying period g of encoding rate (y-1) / y, or encoding rate (z-1) / z.

- This is a receiving apparatus that demodulates and decodes any received signal including an LDPC-CC encoded sequence of variable period g.

- the LDPC-CC having the time-varying period g proposed in the present invention, it is possible to reduce the operation scale (circuit scale) between the transmission apparatus including the encoder and the reception apparatus including the decoder (The circuit can be shared).

- the receiving apparatus can obtain high data reception quality at any coding rate.

- the configuration of the encoder, the configuration of the decoder, and the operation thereof will be described in detail below.

- the coding rate is 1/2, 2/3, 3/4,..., (Q-1) / q.

- the transmission apparatus including the encoder and the reception apparatus including the decoder have the coding rates 1/2, 2/3, 3/4,. It is not necessary to support all of (q-1) / q, and if at least two different coding rates are supported, the operation scale (circuit scale) of the transmission apparatus and the reception apparatus is reduced (encoding And a common circuit of the decoder and the decoder) and an effect that the receiving apparatus can obtain high data reception quality.

- the description is based on the code of (LDPC-CC having good characteristics) described in Embodiment 1, but it is not necessarily described by the above (LDPC-CC having good characteristics).

- the present embodiment is similarly implemented if the LDPC-CC has a time-varying period g based on the parity check polynomial of the format described in (LDPC-CC having good characteristics) described above. (G is an integer of 2 or more). This is clear from the relationship between (31-1) to (31-g) and (32-1) to (32-g).

- the transmission / reception apparatus supports coding rates 1/2, 2/3, 3/4, 5/6, and coding rates 1/2

- 2/3, 3/4 use LDPC-CC based on the above rule

- a coding rate of 5/6 uses a code not based on the above rule

- an encoder / decoder The circuit can be shared for coding rates 1/2, 2/3, and 3/4, and the circuit sharing is difficult for coding rates 5/6.

- the highest coding rate among the coding rates for sharing the encoder circuit and sharing the decoder circuit is (q ⁇ 1) / q (for example, When the encoding rate corresponding to the transmission / reception apparatus is 1/2, 2/3, 3/4, 5/6, the codes of the encoding rates 1/2, 2/3, and 3/4 are encoded by the encoder / In the decoder, the circuit is shared, and the coding rate of 5/6 is not to be shared by the encoder / decoder, and the highest coding rate (q ⁇ 1) / q is 3/4.), LDPC with a time-varying period g (g is a natural number) that can correspond to a plurality of coding rates (r-1) / r (r is an integer of 2 to q) -Describes the encoder that creates the CC.

- g is a natural number

- FIG. 11 is a block diagram showing an example of a main configuration of the encoder according to the present embodiment.

- the encoder 200 shown in FIG. 11 is an encoder that can handle coding rates of 1/2, 2/3, and 3/4.

- 11 includes an information generating unit 210, a first information calculating unit 220-1, a second information calculating unit 220-2, a third information calculating unit 220-3, a parity calculating unit 230, an adding unit 240, It mainly includes a coding rate setting unit 250 and a weight control unit 260.

- the information generation unit 210 sets the information X 1, i , the information X 2, i , and the information X 3, i at the time point i according to the coding rate specified by the coding rate setting unit 250. For example, when the coding rate setting unit 250 sets the coding rate to 1 ⁇ 2, the information generation unit 210 sets the input information data S j to the information X 1, i at the time point i, and the information X at the time point i. 2, the information of i and time i X 3, i is set to 0.

- the information generation unit 210 sets the input information data S j to the information X 1, i at the time point i, and the input information data S j + 1 to the information X 2, i at the time point i. Set, and set the information X 3, i at time i to 0.

- the information generation unit 210 sets the input information data S j to the information X 1, i at the time point i, and the input information data S j + 1 to the information X 2, i at the time point i. Then, the input information data S j + 2 is set to the information X 3, i at the time point i.

- the information generating unit 210 according to the coding rate coding rate set by the setting unit 250, information X 1 of point in time i to input information data, i, information X 2, i, information X 3 , I are set, the set information X 1, i is output to the first information calculation unit 220-1, and the set information X 2, i is output to the second information calculation unit 220-2. Then, the set information X 3, i is output to the third information calculation unit 220-3.

- the first information calculation unit 220-1 calculates X 1 (D) according to A X1, k (D) in Expression (30-1).

- the second information calculation unit 220-2 calculates X 2 (D) according to A X2, k (D) in Expression (30-2).

- the third information calculation unit 220-3 calculates X 3 (D) according to A X3, k (D) in Expression (30-3).

- the above operation is performed on the basis of the configuration of the encoder with the highest coding rate among the coding rates that can be shared by the encoder circuit. It is possible to cope with other coding rates. That is, the first information calculation unit 220-1, the second information calculation unit 220-2, and the third information calculation unit 220-3, which are main parts of the encoder, are shared regardless of the coding rate.

- the LDPC-CC described in Embodiment 2 has the advantage that it can be used.

- the LDPC-CC shown in Table 5 has the advantage of providing good data reception quality regardless of the coding rate.

- FIG. 12 shows the internal configuration of the first information calculation unit 220-1. 12 includes shift registers 221-1 to 221-M, weight multipliers 222-0 to 222-M, and an adder 223.

- Weight multipliers 222-0 to 222 -M switch the value of h 1 (m) to 0 or 1 according to the control signal output from weight control section 260.

- the adder 223 performs an exclusive OR operation on the outputs of the weight multipliers 222-0 to 222-M, calculates the operation result Y 1, i, and calculates the calculated Y 1, i in FIG. Output to the adder 240.

- the internal configuration of the second information calculation unit 220-2 and the third information calculation unit 220-3 is the same as that of the first information calculation unit 220-1, and thus the description thereof is omitted. Similar to the first information calculation unit 220-1, the second information calculation unit 220-2 calculates the calculation result Y 2, i and outputs the calculated Y 2, i to the addition unit 240. The third information calculation unit 220-3 calculates the calculation result Y 3, i in the same manner as the first information calculation unit 220-1, and sends the calculated Y 3, i to the addition unit 240 in FIG. Output.

- the parity calculation unit 230 in FIG. 11 calculates P (D) according to B k (D) in Expressions (30-1) to (30-3).

- FIG. 13 shows an internal configuration of the parity calculation unit 230 of FIG. 13 includes shift registers 231-1 to 231-M, weight multipliers 232-0 to 232-M, and an adder 233.

- Weight multipliers 232-0 to 232-M switch the value of h 2 (m) to 0 or 1 according to the control signal output from weight control section 260.

- the adder 233 performs an exclusive OR operation on the outputs of the weight multipliers 232-0 to 232-M, calculates an operation result Z i, and outputs the calculated Z i to the adder 240 in FIG. Output.

- the adder 240 calculates the computations output from the first information computation unit 220-1, the second information computation unit 220-2, the third information computation unit 220-3, and the parity computation unit 230.

- the result Y 1, i , Y 2, i , Y 3, i , Z i is subjected to an exclusive OR operation to obtain and output a parity P i at time i.

- the adder 240 also outputs the parity P i at time i to the parity calculator 230.

- the coding rate setting unit 250 sets the coding rate of the encoder 200, and outputs the coding rate information to the information generation unit 210.

- the weight control unit 260 uses the equations (30-1) to (30-3) based on the parity check matrix corresponding to the equations (30-1) to (30-3) held in the weight control unit 260.

- the value of h 1 (m) at time i based on the parity check polynomial is stored in the first information calculation unit 220-1, the second information calculation unit 220-2, the third information calculation unit 220-3, and the parity calculation unit 230. Output toward.

- the weight control unit 260 determines the value of h 2 (m) at the timing based on the parity check matrix corresponding to the equations (30-1) to (30-3) held in the weight control unit 260. Output to 232-0 to 232-M.

- FIG. 14 shows another configuration example of the encoder according to the present embodiment.

- the same reference numerals as those in FIG. 11 are given to the components common to the encoder of FIG.

- the coding rate setting unit 250 converts the coding rate information into the first information calculation unit 220-1, the second information calculation unit 220-2, the third information calculation unit 220-3, And it is different from the encoder 200 of FIG. 11 in that it is output toward the parity calculation unit 230.

- the second information calculation unit 220-2 When the coding rate is 1/2, the second information calculation unit 220-2 outputs 0 to the addition unit 240 as the calculation result Y2 , i without performing the calculation process. In addition, when the coding rate is 1/2 or 2/3, the third information calculation unit 220-3 does not perform the calculation process and directs 0 as the calculation result Y 3, i to the addition unit 240. Output.

- the information generation unit 210 sets the information X 2, i and the information X 3, i at the time point i to 0 according to the coding rate, whereas FIG.

- the second information calculation unit 220-2 and the third information calculation unit 220-3 stop the calculation process according to the coding rate, and calculate the calculation results Y 2, i , Y 3, i. Since 0 is output, the obtained calculation result is the same as that of the encoder 200 of FIG.

- the second information calculation unit 220-2 and the third information calculation unit 220-3 stop the calculation process according to the coding rate. Computational processing can be reduced compared to the generator 200.

- FIG. 15 is a block diagram showing a main configuration of the decoder according to the present embodiment.

- the decoder 300 shown in FIG. 15 is a decoder that can handle coding rates of 1/2, 2/3, and 3/4.

- the decoder 300 of FIG. 14 mainly includes a log likelihood ratio setting unit 310 and a matrix processing calculation unit 320.

- Log-likelihood ratio setting section 310 receives a received log-likelihood ratio and a coding rate calculated by a log-likelihood ratio calculation section (not shown), and is known to the received log-likelihood ratio according to the coding rate. Insert log-likelihood ratio.

- the log likelihood ratio setting unit 310 receives the received log likelihood ratios LLR X1, i , LLR Pi corresponding to X 1, i and P i as inputs. To do. Accordingly, the log likelihood ratio setting unit 310 inserts the received log likelihood ratios LLR X2, i , LLR 3, i corresponding to X 2, i , X 3, i .

- the reception log likelihood ratio surrounded by a dotted circle indicates the reception log likelihood ratio LLR X2, i , LLR 3, i inserted by the log likelihood ratio setting unit 310.

- Log likelihood ratio setting section 310 inserts a log likelihood ratio of a fixed value as reception log likelihood ratio LLR X2, i , LLR 3, i .

- the log likelihood ratio setting unit 310 determines the known bit “0”. Is inserted as a log likelihood ratio of X 3, i , and the log likelihood ratio after the insertion is output to the matrix processing operation unit 320.

- log likelihood ratio setting section 310 inserts received log likelihood ratio LLR 3, i corresponding to X 3, i .

- the reception log likelihood ratio surrounded by a dotted circle represents the reception log likelihood ratio LLR 3, i inserted by the log likelihood ratio setting unit 310.

- Log-likelihood ratio setting section 310 inserts a log-likelihood ratio of a fixed value as reception log-likelihood ratio LLR 3, i .

- 15 includes a storage unit 321, a row processing calculation unit 322, and a column processing calculation unit 323.

- the storage unit 321 holds the reception log likelihood ratio, the external value ⁇ mn obtained by row processing, and the prior value ⁇ mn obtained by column processing.

- the row processing calculation unit 322 holds a weight pattern in the row direction of the parity check matrix H of the LDPC-CC having the maximum coding rate 3/4 among the coding rates supported by the encoder 200.

- the row processing calculation unit 322 reads the necessary prior value ⁇ mn from the storage unit 321 according to the weight pattern in the row direction, and performs row processing calculation.