KR20160006709A - 고성능 및 저비용 플래시 변환 계층을 위한 시스템 및 방법 - Google Patents

고성능 및 저비용 플래시 변환 계층을 위한 시스템 및 방법 Download PDFInfo

- Publication number

- KR20160006709A KR20160006709A KR1020157033238A KR20157033238A KR20160006709A KR 20160006709 A KR20160006709 A KR 20160006709A KR 1020157033238 A KR1020157033238 A KR 1020157033238A KR 20157033238 A KR20157033238 A KR 20157033238A KR 20160006709 A KR20160006709 A KR 20160006709A

- Authority

- KR

- South Korea

- Prior art keywords

- flash memory

- memory device

- copy

- host device

- ftl

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/0223—User address space allocation, e.g. contiguous or non contiguous base addressing

- G06F12/023—Free address space management

- G06F12/0238—Memory management in non-volatile memory, e.g. resistive RAM or ferroelectric memory

- G06F12/0246—Memory management in non-volatile memory, e.g. resistive RAM or ferroelectric memory in block erasable memory, e.g. flash memory

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/0223—User address space allocation, e.g. contiguous or non contiguous base addressing

- G06F12/0292—User address space allocation, e.g. contiguous or non contiguous base addressing using tables or multilevel address translation means

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/72—Details relating to flash memory management

- G06F2212/7201—Logical to physical mapping or translation of blocks or pages

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/72—Details relating to flash memory management

- G06F2212/7203—Temporary buffering, e.g. using volatile buffer or dedicated buffer blocks

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Techniques For Improving Reliability Of Storages (AREA)

- Information Retrieval, Db Structures And Fs Structures Therefor (AREA)

- Memory System (AREA)

- Memory System Of A Hierarchy Structure (AREA)

- Read Only Memory (AREA)

Abstract

본 양태들은 플래시 메모리 디바이스의 플래시 변환 계층 (FTL) 의 성능을 증가시키는 시스템들 및 방법들을 포함한다. 플래시 메모리 디바이스 상에 저장된 FTL 테이블들의 복사본은 호스트 디바이스의 메모리에 복사될 수도 있다. FTL 테이블들의 복사본은 플래시 메모리 디바이스의 플래시 메모리로/로부터의 판독/기록 동작들을 위해 호스트 디바이스에 의해 제공되는 논리 어드레스들과, 플래시 메모리의 각각의 물리 어드레스들 사이에 변환하기 위해, 플래시 메모리 디바이스에 의해 직접 액세스될 수도 있다. 플래시 메모리 디바이스는 FTL 테이블들의 복사본이 저장된 호스트 디바이스의 메모리의 부분에의 직접 메모리 액세스를 승인받는다. 플래시 메모리 디바이스는 플래시 메모리 디바이스를 호스트 디바이스의 메모리에 접속하는 통신 버스들을 버스 마스터링한다.

Description

관리된 플래시 스토리지 성능이 점점 더 요구되고 있다. 스마트폰들, 태블릿들, 및 게이밍 디바이스들과 같은, 컴팩트한 가전제품은 비용 효과적 및 저 전력 스토리지 솔루션들을 필요로 한다. 관리된 부정 AND 또는 NOT AND (NAND) 플래시 저장 디바이스들의 예들은 내장 MultiMediaCard들 (eMMC), 범용 플래시 스토리지 (UFS), eSATA (External Serial Advanced Technology Attachment), 볼 그리드 어레이 (BGA) SATA, 범용 시리얼 버스 (USB) 드라이브, 보안 디지털 (SD) 카드, 범용 가입자 식별 모듈 (USIM) 카드, 및 컴팩트 플래시 카드를 포함한다. NAND 디바이스들은, 그들이 저비용 및 저전력이기 때문에, 모바일 애플리케이션들에 인기가 있다.

기존 관리된 NAND 플래시 저장 디바이스들은 NAND 플래시 메모리 내에 포함되는 큰 파일 변환 계층 (FTL) 테이블들에 의존하며, 단지 온칩 정적 랜덤 액세스 메모리 (SRAM) 에서의 테이블들의 작은 부분만을 캐싱한다. 관리된 NAND 디바이스에 대한 판독 및 기록 액세스들은 FTL 테이블로부터의 정보를 이용하여 물리 NAND 어드레스들로 변환되어야 하는 논리 어드레스들로 이루어진다. 이것은 NAND 메모리로부터 FTL 테이블 엔트리들을 판독할 때 긴 지연들 (대략 수십의 마이크로초) 을 초래하여, 이들 유형들의 스토리지의 전체 성능을 열화시킨다. 따라서, NAND 메모리 디바이스들에서 저비용 및 낮은 소비 전력에 대한 불이익은 메모리 액세스 시간 성능에 있어서의 감소이다.

플래시 메모리 디바이스에 의해, 플래시 메모리 디바이스의 FTL 테이블의 복사본을 호스트 디바이스의 휘발성 메모리에 저장하는 것; 플래시 메모리 디바이스에 의해, 호스트 디바이스의 휘발성 메모리에 저장된 FTL 테이블의 복사본에의 액세스를 수신하는 것; 및 판독 동작 및 기록 동작 중 적어도 하나의 부분으로서, 플래시 메모리 디바이스에 의해, 호스트 디바이스의 휘발성 메모리에 저장된 플래시 메모리 디바이스의 FTL 테이블의 복사본에 액세스하는 것을 포함하는, 여러 양태들의 방법들 및 시스템들이, 플래시 메모리 디바이스의 플래시 변환 계층 (FTL) 의 성능을 증가시키기 위해, 제공된다. 일 양태 방법은 플래시 메모리 디바이스에서 호스트 디바이스로부터 FTL 테이블의 사이즈에 대한 쿼리를 수신하는 단계, FTL 테이블의 사이즈를 플래시 메모리 디바이스로부터 호스트 디바이스로 반환하는 단계, 호스트 디바이스에서 플래시 메모리 디바이스로부터 FTL 테이블의 사이즈를 수신하는 단계; 및 호스트 디바이스에 의해, 호스트 디바이스의 휘발성 메모리가 FTL 테이블의 모두를 저장할 수 있는지 여부를 결정하는 단계를 더 포함할 수도 있다. 일 양태 방법은 호스트 디바이스에 의해 호스트 디바이스의 휘발성 메모리를 재분할하는 단계로서, 재분할 부분 (subdivision) 의 사이즈는 FTL 테이블의 사이즈에 기초하는, 상기 재분할하는 단계; 플래시 메모리 디바이스에 의해, FTL 테이블의 복사본이 저장된 호스트 디바이스의 휘발성 메모리의 재분할 부분에 대한 직접 메모리 액세스 판독 특권들을 수신하는 단계; 및 플래시 메모리 디바이스에 의해, FTL 테이블의 복사본이 저장되는 호스트 디바이스의 휘발성 메모리의 재분할 부분에 대한 직접 메모리 액세스 기록 특권들을 수신하는 단계를 더 포함하며, 상기 FTL 테이블의 복사본을 저장하는 단계는 플래시 메모리 디바이스에 의해, 호스트 디바이스의 휘발성 메모리의 재분할 부분에서의 FTL 테이블의 복사본을 저장하는 단계를 더 포함한다.

일 양태에서, FTL 테이블의 복사본에 액세스하는 단계는, 플래시 메모리 디바이스에 의해, 호스트 디바이스의 휘발성 메모리 및 플래시 메모리 디바이스를 통신가능하게 접속하는 통신 버스를 버스 마스터링하는 단계를 더 포함할 수 있다.

일 양태에서, FTL 테이블의 복사본에 액세스하는 단계는, 플래시 메모리 디바이스에서, 호스트 디바이스로부터 논리 어드레스에 대한 판독 동작 요청을 수신하는 단계; 플래시 메모리 디바이스에 의해 판독 동작을 개시하는 단계; 플래시 메모리 디바이스에 의해 FTL 테이블의 복사본 중 적어도 일부분을 판독하는 단계; 플래시 메모리 디바이스에 의해 논리 어드레스에 대응하는 물리 어드레스를 결정하는 단계; 플래시 메모리 디바이스에 의해, 플래시 메모리 디바이스의 메모리의 물리 어드레스에 로케이트된 데이터를 취출하는 단계; 및 플래시 메모리 디바이스에 의해 데이터를 호스트 디바이스로 반환하는 단계를 포함할 수도 있다.

일 양태에서, FTL 테이블의 복사본에 액세스하는 단계는, 플래시 메모리 디바이스에 의해 호스트 디바이스로부터 논리 어드레스에 대한 기록 동작 요청을 수신하는 단계; 플래시 메모리 디바이스에 의해 기록 동작을 개시하는 단계; 플래시 메모리 디바이스에 의해 데이터를 플래시 메모리 디바이스의 메모리의 물리 어드레스에 기록하는 단계; 데이터가 기록되었을 때 플래시 메모리 디바이스의 메모리에 대해 이루어진 변화들에 일치하도록 FTL 테이블의 복사본을 업데이트하기 위해, 플래시 메모리 디바이스에 의해, FTL 테이블의 복사본에 기록하는 단계; 및 플래시 메모리 디바이스에 의해 기록 동작의 완료의 통지를 호스트 디바이스로 전송하는 단계를 포함할 수도 있다. 일 양태 방법은 플래시 메모리 디바이스에 의해 FTL 테이블의 복사본 중 적어도 일부분을 판독하는 단계, 및 플래시 메모리 디바이스에 의해 논리 어드레스에 대응하는 물리 어드레스를 결정하는 단계를 더 포함할 수 있다. 일 양태 방법은 플래시 메모리 디바이스에 의해 플래시 메모리 디바이스의 SRAM 을 판독하는 단계; 및 플래시 메모리 디바이스에 의해, 플래시 메모리 디바이스의 메모리에서의 자유 저장 공간의 로케이션을 나타내는 물리 어드레스를 결정하는 단계를 더 포함할 수 있다. 일 양태 방법은 플래시 메모리 디바이스에 의해, FTL 테이블의 복사본을 호스트 디바이스의 휘발성 메모리에 저장하는 것의 완료를 나타내는 통지를 호스트 디바이스로 전송하는 단계를 더 포함할 수 있다. 일 양태 방법은 기록 동작의 완료, 가용 리소스들, 및 스케쥴로 이루어진 그룹으로부터 선택된 파라미터에 기초하여, 플래시 메모리 디바이스에 의해, 플래시 메모리 디바이스의 FTL 테이블을 FTL 의 복사본으로 업데이트하는 단계를 더 포함할 수 있다. 일 양태 방법은 호스트 디바이스에 의해, 플래시 메모리 디바이스가 호스트 디바이스의 휘발성 메모리에서의 FTL 테이블의 복사본의 호스트 캐싱을 지원하는지 여부를 결정하는 단계를 더 포함할 수 있다. 일 양태 방법은 호스트 디바이스에서, 플래시 메모리 디바이스로부터 FTL 테이블의 복사본을 저장하는 것의 완료의 통지를 수신하는 단계를 더 포함할 수 있다.

일 양태는 플래시 메모리 디바이스에 의해 호스트 디바이스의 휘발성 메모리 상에 플래시 메모리 디바이스의 FTL 테이블의 복사본을 저장하고, 그리고 플래시 메모리 디바이스에 의해, 호스트 디바이스의 휘발성 메모리에 저장된 FTL 테이블의 복사본에의 액세스를 수신함으로써, 시스템으로 하여금, 시스템의 플래시 메모리 디바이스의 플래시 변환 계층의 성능을 증가시키도록 구성된 프로세서-실행가능한 소프트웨어 명령들을 안에 저장하고 있는 비일시적 프로세서-판독가능 저장 매체를 포함한다. 또한, 저장된 명령들은 판독 동작 및 기록 동작 중 적어도 하나의 부분으로서, 플래시 메모리 디바이스에 의해, 호스트 디바이스의 휘발성 메모리에 저장된 플래시 메모리 디바이스의 FTL 테이블의 복사본에 액세스하는 명령들을 포함할 수도 있다. 비일시적 프로세서-판독가능 저장 매체는 시스템으로 하여금, 위에서 설명된 양태 방법들의 다른 동작들을 수행하도록 구성된 프로세서-실행가능한 소프트웨어 명령들을 안에 저장하고 있을 수도 있다.

일 양태는 휘발성 메모리 및 휘발성 메모리에 커플링된 제 1 프로세서를 갖는 호스트 디바이스; 및 플래시 메모리 디바이스를 포함하는 컴퓨팅 시스템을 포함하며, 상기 시스템은 플래시 메모리 디바이스에 의해 호스트 디바이스의 휘발성 메모리에 플래시 메모리 디바이스의 FTL 테이블의 복사본을 저장하고; 플래시 메모리 디바이스에 의해, 호스트 디바이스의 휘발성 메모리에 저장된 FTL 테이블의 복사본에의 액세스를 수신하고, 그리고 판독 동작 및 기록 동작 중 적어도 하나의 부분으로서, 플래시 메모리 디바이스에 의해, 호스트 디바이스의 휘발성 메모리에 저장된 플래시 메모리 디바이스의 FTL 테이블의 복사본에 액세스함으로써, 플래시 메모리 디바이스의 증가된 성능을 가능하게 한다.

일 양태는 플래시 메모리 디바이스에 의해 호스트 디바이스의 휘발성 메모리에 플래시 메모리 디바이스의 FTL 테이블의 복사본을 저장하는 수단을 포함하고, 플래시 메모리 디바이스의 플래시 변환 계층의 성능을 증가시키도록 구성된 시스템을 포함한다. 상기 시스템은 또한 플래시 메모리 디바이스에 의해, 호스트 디바이스의 휘발성 메모리에 저장된 FTL 테이블의 복사본에의 액세스를 수신하는 수단; 및 판독 동작 및 기록 동작 중 적어도 하나의 부분으로서, 플래시 메모리 디바이스에 의해, 호스트 디바이스의 휘발성 메모리에 저장된 플래시 메모리 디바이스의 FTL 테이블의 복사본에 액세스하는 수단을 포함할 수도 있다.

추가 양태는 논리 어드레스와 물리 어드레스 사이에 변환할 때에 사용을 위한 FTL 테이블을 포함하는 데이터를 저장하도록 구성된 플래시 메모리; 및 플래시 메모리에 커플링된 프로세서를 포함하는, 호스트 디바이스에 커플링하도록 구성된 플래시 메모리 디바이스를 포함하며, 상기 프로세서는 호스트 디바이스의 휘발성 메모리에 플래시 변환 계층 플래시 메모리 디바이스의 FTL 테이블의 복사본을 저장하는 것, 호스트 디바이스의 휘발성 메모리에 저장된 FTL 테이블의 복사본에의 액세스를 수신하는 것, 및 판독 동작 및 기록 동작 중 적어도 하나의 부분으로서 호스트 디바이스의 휘발성 메모리에 저장된 플래시 메모리 디바이스의 FTL 테이블의 복사본에 액세스하는 것을 포함하는 동작들을 수행하는 프로세서-실행가능한 명령들로 구성된다.

추가 양태는 호스트 디바이스의 휘발성 메모리에 플래시 메모리 디바이스의 FTL 테이블의 복사본을 저장하는 수단; 호스트 디바이스의 휘발성 메모리에 저장된 FTL 테이블의 복사본에의 액세스를 수신하는 수단; 및 판독 동작 및 기록 동작 중 적어도 하나의 부분으로서 호스트 디바이스의 휘발성 메모리에 저장된 플래시 메모리 디바이스의 FTL 테이블의 복사본에 액세스하는 수단을 포함하는 호스트 디바이스에 커플링된 디바이스를 포함한다.

추가 양태는 휘발성 메모리; 호스트 디바이스의 휘발성 메모리에 통신가능하게 접속하며 호스트 디바이스에 커플링될 때 플래시 메모리 디바이스와 통신하도록 구성된 통신 버스; 및 플래시 메모리 디바이스가 휘발성 메모리에서의 플래시 메모리 디바이스의 FTL 테이블의 복사본의 호스트 캐싱을 지원하는지 여부를 결정하는 것, FTL 테이블의 복사본을 저장하기 위한 휘발성 메모리의 부분을 할당하는 것, 및 통신 버스를 통해서플래시 메모리 디바이스에게 휘발성 메모리의 부분에 대한 직접 메모리 액세스 판독 및 기록 특권들을 승인하는 것을 포함하는 동작들을 수행하는 프로세서-실행가능한 명령들로 구성되는 프로세서를 포함하는, 플래시 메모리 디바이스에 커플링된 호스트 디바이스를 포함한다.

본원에 포함되어 본 명세서의 부분을 구성하는, 첨부 도면들은, 본 발명의 예시적인 양태들을 예시하며, 위에서 주어진 일반적인 설명 및 아래에 주어지는 상세한 설명과 함께, 본 발명의 특징들을 설명하는 것을 돕는다.

도 1 은 일 양태에 따른, 플래시 메모리 디바이스에 통신가능하게 접속된 호스트 디바이스를 갖는 시스템을 예시하는 구성요소 블록도이다.

도 2 는 여러 양태들과 사용하기에 적합한 예시적인 모바일 디바이스의 구성요소 다이어그램이다.

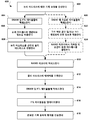

도 3 은 FTL 호스트 캐싱을 초기화하는 양태 방법을 예시하는 프로세스 흐름도이다.

도 4 는 FTL 호스트 캐싱을 초기화하는 양태 방법을 예시하는 프로세스 흐름도이다.

도 5 는 FTL 호스트 캐싱에 의해 판독 동작을 실행하는 양태 방법을 예시하는 프로세스 흐름도이다.

도 6 은 FTL 호스트 캐싱에 의해 기록 동작을 실행하는 양태 방법을 예시하는 프로세스 흐름도이다.

도 7 은 FTL 호스트 캐싱을 초기화하는 양태 방법을 예시하는 프로세스 흐름도이다.

도 8 은 FTL 호스트 캐싱에 의해 판독 동작을 실행하는 양태 방법을 예시하는 프로세스 흐름도이다.

도 9 는 FTL 호스트 캐싱에 의해 기록 동작을 실행하는 양태 방법을 예시하는 프로세스 흐름도이다.

도 10 은 FTL 호스트 캐싱에 의해 기록 동작을 실행하는 양태 방법을 예시하는 프로세스 흐름도이다.

도 1 은 일 양태에 따른, 플래시 메모리 디바이스에 통신가능하게 접속된 호스트 디바이스를 갖는 시스템을 예시하는 구성요소 블록도이다.

도 2 는 여러 양태들과 사용하기에 적합한 예시적인 모바일 디바이스의 구성요소 다이어그램이다.

도 3 은 FTL 호스트 캐싱을 초기화하는 양태 방법을 예시하는 프로세스 흐름도이다.

도 4 는 FTL 호스트 캐싱을 초기화하는 양태 방법을 예시하는 프로세스 흐름도이다.

도 5 는 FTL 호스트 캐싱에 의해 판독 동작을 실행하는 양태 방법을 예시하는 프로세스 흐름도이다.

도 6 은 FTL 호스트 캐싱에 의해 기록 동작을 실행하는 양태 방법을 예시하는 프로세스 흐름도이다.

도 7 은 FTL 호스트 캐싱을 초기화하는 양태 방법을 예시하는 프로세스 흐름도이다.

도 8 은 FTL 호스트 캐싱에 의해 판독 동작을 실행하는 양태 방법을 예시하는 프로세스 흐름도이다.

도 9 는 FTL 호스트 캐싱에 의해 기록 동작을 실행하는 양태 방법을 예시하는 프로세스 흐름도이다.

도 10 은 FTL 호스트 캐싱에 의해 기록 동작을 실행하는 양태 방법을 예시하는 프로세스 흐름도이다.

여러 양태들이 첨부 도면들을 참조하여 자세히 설명된다. 가능한 경우에는 언제나, 동일한 또는 유사한 부재들을 지칭하기 위해서 동일한 참조 번호들이 도면들 전반에 걸쳐서 사용된다. 특정의 예들 및 구현예들에 대한 언급들은 예시적인 목적들을 위한 것이며, 본 발명 또는 청구항들의 범위에 한정하려고 의도되지 않는다.

단어 "예시적인" 은 "일 예, 사례, 또는 예시로서 기능하는 것" 을 의미하도록 본원에서 사용된다. 본원에서 "예시적인" 으로서 설명하는 임의의 구현예는 다른 구현예들보다 바람직하거나 또는 유리한 것으로 반드시 해석해서는 안된다.

용어들 "모바일 컴퓨팅 디바이스" 및 "모바일 디바이스" 는 셀룰러 전화기들, 스마트폰들, 개인 또는 모바일 멀티-미디어 플레이어들, 개인 휴대 정보단말기들 (PDA's), 랩탑 컴퓨터들, 태블릿 컴퓨터들, 스마트북들, 울트라북들, 팜탑 컴퓨터들, 무선 전자 메일 수신기들, 멀티미디어 인터넷 이용가능한 셀룰러 전화기들, 무선 게이밍 제어기들, 및 메모리, 프로그래밍가능 프로세서를 포함하고 전력 절약 방법들이 도움이 될 수 있는 배터리 전력 하에서 동작하는 유사한 개인 전자 디바이스들 중 임의의 하나 또는 모두를 지칭하기 위해, 본원에서 상호교환가능하게 사용된다. 여러 양태들이 제한된 리소스들을 갖고 배터리 전력 상에서 동작하는, 스마트폰들과 같은, 모바일 컴퓨팅 디바이스들에 특히 유용한 한편, 상기 양태들은 플래시 메모리 디바이스와 함께 사용하기 위해 호환가능한 임의의 전자 디바이스에 유용하다.

용어 "플래시 메모리" 는 본원에서 전기적으로 삭제되고 재프로그래밍될 수 있는, 전자 비-휘발성 컴퓨터 스토리지, 또는 메모리를 지칭한다. 플래시 메모리 디바이스 아키텍처는 일반적으로 NAND 및 NOR 유형들을 포함한다. 본원에서 양태들은 일반적으로 플래시 메모리 디바이스들의 NAND 유형 아키텍처에 관한 것이다. 플래시 메모리는 데이터의 일반적인 저장 및 전송을 위해, 메인 메모리, 메모리 카드들, USB 플래시 드라이브들, 고체-상태 드라이브들, 및 유사한 제품들에 사용될 수도 있다. NAND 플래시 메모리 디바이스들의 예들은 내장 MultiMediaCards (eMMC), 범용 플래시 스토리지 (UFS), eSATA (External Serial Advanced Technology Attachment), 볼 그리드 어레이 (BGA) SATA, 범용 시리얼 버스 (USB) 드라이브, 보안 디지털 (SD) 카드, 범용 가입자 식별 모듈 (USIM) 카드, 및 컴팩트 플래시 카드를 포함한다.

용어들 "플래시 변환 계층" 및 "FTL" 은 본원에서 플래시 메모리 디바이스의 제어기로 하여금 논리 어드레스들에 대한 요청들을 실제 플래시 메모리 칩들에서의 물리 어드레스들로 변환가능하게 하도록 생성된 디렉토리 구조를 지칭한다. 디렉토리 구조는 여러 데이터 구조들 중 임의의 구조를 포함할 수도 있다. 예의 목적들을 위해, 본원에서 FTL 은 테이블들의 유형인 것으로 설명될 것이다.

메모리들에서 변환 성능을 증가시키는 하나의 기법은 전용 동적 랜덤 액세스 메모리 (DRAM) 를 전체 변환 테이블을 캐싱하는데 사용되는 솔리드 스테이트 드라이브 (SSD), 또는 하드 디스크 드라이브 (HDD) 에 추가한다. DRAM 이 NAND 플래시 메모리 또는 하드 디스크 드라이브 메모리 보다 대략 1000 배 더 큰 속도로 액세스될 수 있기 때문에, 이것은 유의미한 성능 상승을 제공할 수 있다. 그러나, 칩에 DRAM 을 추가하는 것은 비용을 증가시키고, 콘텐츠를 유지하기 위해 여분의 DRAM 이 셀프 리프레시 (self refresh) 되어야 하기 때문에, 상당한 대기 전력을 소모한다. 일부 랩탑 컴퓨터 SSD들은, 이러한 컴퓨터들이 일반적으로 전력 제한되지 않고 소비자들이 이러한 디바이스들에 더 많이 지출할 것으로 예상되기 때문에, 이 유형의 메커니즘을 채용하여 변환 테이블을 캐싱한다. 그러나, 내장된 DRAM 메모리에 의한 NAND 플래시 메모리들의 비용들에서의 증가 및 추가된 전력 드레인은 스마트폰들과 같은 모바일 컴퓨팅 디바이스들에 대한 상당한 단점들이다.

여러 양태들은 플래시 메모리에 대한 변환 테이블을 저장하는데 호스트 디바이스의 DRAM 메모리를 이용함으로써, 플래시 메모리 디바이스 동작들의 성능을 향상시킴과 동시에, 그의 비용 및 전력 드레인을 최소화하도록 구성된 방법들, 시스템들, 및 디바이스들을 포함한다. 이것은 플래시 메모리 디바이스와 통신하는 호스트 디바이스를 포함하는 시스템을 통해서 달성될 수도 있으며, 여기서, 호스트 디바이스 및 플래시 메모리는, 논리 및 물리 메모리 어드레스들 사이에 변환시키는데 플래시 메모리 디바이스가 사용하는 변환 테이블들을 캐싱하기 위해 호스트 디바이스의 더 빠른 메모리 리소스들을 플래시 메모리 디바이스가 이용할 수 있도록, 구성된다.

일 양태에서, 호스트 디바이스는 플래시 메모리 디바이스에게 그의 더 빠른 메모리 리소스들에의 직접 메모리 액세스를 승인할 수도 있다. 직접 메모리 액세스는 더 빠른 메모리 리소스들에 대한 판독 및/또는 기록 특권들을 포함할 수도 있다. 플래시 메모리 디바이스는 이러한 직접 액세스 허가들을 이용하여, FTL 테이블들의 복사본을 호스트 디바이스의 더 빠른 메모리 리소스들에 저장할 수도 있다. FTL 테이블들의 복사본의 저장을 허용할 때, 호스트 디바이스는 FTL 테이블들의 복사본을 포함하기에 적합한 사이즈의 특정의 영역을 제공하기 위해, 그의 더 빠른 메모리 리소스들을 재분할할 수도 있다. 따라서, 메모리 재분할 부분의 사이즈는 FTL 테이블들의 사이즈에 기초할 수도 있다.

또 다른 양태에서, 직접 메모리 액세스는 플래시 메모리 디바이스에게 승인된 직접 메모리 액세스 허가들로부터 기인하는 보안 이슈들로부터 호스트 디바이스를 보호하기 위해 제한될 수도 있다. 예를 들어, 직접 메모리 액세스는 FTL 테이블들의 복사본용으로 지정된 더 빠른 메모리 리소스들의 영역에 대해서만 오직 승인될 수도 있다. 키 비교들과 같은, 추가적인 보안 조치가 또한 강구될 수도 있다. 또한, 호스트 디바이스를 보호하기 위해 취해지는 이러한 보안 조치들 및 다른 보안 조치들이 플래시 메모리 디바이스를 보호하기 위해 또한 적용될 수도 있는 것으로 생각된다. 플래시 메모리 디바이스에 대해 보안 조치들을 구현하는 것은 FTL 테이블들을 변경시키는 것으로부터 호스트 디바이스를 방지할 수도 있다.

플래시 메모리 디바이스에 대한 판독 및/또는 기록 동작들이 호스트 디바이스에 의해 요청될 때, 판독 및/또는 기록 동작 요청은 플래시 메모리 디바이스로부터 데이터를 판독하거나 및/또는 플래시 메모리 디바이스에 데이터를 기록할 장소에 대한 논리 어드레스들을 포함할 수도 있다. 판독 및/또는 기록 요청들을 실행하기 위해, 플래시 메모리 디바이스는 FTL 테이블들을 이용하여 논리 어드레스를 그의 자신의 메모리의 물리 어드레스로 변환할 수도 있다. 이를 행하기 위해, 플래시 메모리 디바이스는 대응하는 물리 어드레스로 변환하기 위해, 그의 직접 메모리 액세스 허가들을 이용하여 그 규정된 논리 어드레스들에 관련된 FTL 테이블들의 복사본으로부터 어드레스 맵핑 정보를 취출할 수도 있다.

직접 메모리 액세스는 또한 플래시 메모리 디바이스로 하여금, FTL 테이블들의 복사본에 기록가능하게 할 수도 있다. 호스트 디바이스로부터의 기록 요청을 완료한 후, 플래시 메모리 디바이스는 데이터가 기록된 물리 어드레스들을 포함한, 그의 자신의 메모리 콘텐츠를 변경한다. 그의 메모리에서의 변화들을 반영하기 위해, 플래시 메모리 디바이스는 호스트 디바이스에 저장된 FTL 테이블들을 업데이트하여, 현재의 물리 어드레스들을 반영할 수도 있다. 업데이트들은 메모리에 기록된 정보가 추후 액세스될 수 있도록 하며, 정보가 기록된 공간이 자유 공간 (free space) 이 아니라는 것을 표시한다.

또 다른 양태에서, 플래시 메모리 디바이스는 호스트 디바이스의 빠른 메모리 리소스들에 저장된 FTL 테이블들에 기초하여 그의 자신의 메모리에 저장된 FTL 테이블들을 업데이트하기 위해 직접 메모리 액세스할 수도 있다. FTL 테이블의 복사본이 플래시 메모리 디바이스에서의 변화들을 반영하기 위해 업데이트될 때, 플래시 메모리 디바이스에서의 FTL 테이블들은 유사하게 동시에 업데이트되지 않을 수도 있다. 플래시 메모리에 저장된 FTL 테이블들의 업데이트를 지연시키는 것은 특히, 호스트 디바이스가 빈번한 메모리 기록 동작들을 수행하고 있을 때, 전력 리소스들을 절감하는 것이 가능하게 할 수도 있다. 반드시 플래시 메모리 디바이스에 대한 변화들의 기록들이 플래시 메모리 디바이스에 저장된 FTL 테이블들의 비-휘발성 복사본에 반영되도록 하기 위해서, 그들 FTL 테이블들은 호스트 디바이스의 빠른 메모리 리소스들에 저장된 FTL 테이블들로부터 주기적으로 업데이트될 수도 있다. 이를 행하기 위해, 플래시 메모리 디바이스는 호스트 디바이스의 빠른 메모리 리소스들에 저장된 FTL 테이블들 (또는, 최종 업데이트 이후 FTL 테이블들의 복사본에 대해 이루어진 변화들) 로부터 FTL 테이블들의 복사본을 취출하고, 그 FTL 테이블의 복사본을 플래시 메모리에 저장하여, 그의 자신의 FTL 테이블들 (또는, 그의 변화된 부분들) 을 효과적으로 덮어 쓸 수도 있다. 이러한 프로세스들에서, 플래시 메모리 디바이스는 그의 FTL 테이블들을 FTL 테이블들의 복사본으로 대체하고, FTL 테이블들의 2개의 버전들을 비교하여, 차이들을 결정하고 그 차이들을 그의 FTL 테이블들에 기록하거나, 또는 FTL 테이블들의 복사본에서의 변환들을 그의 FTL 테이블들에 기록할 수도 있다. 업데이트는 또한 메모리 액세스들 또는 배터리 전력과 같은, 시스템 리소스들에 대한 영향을 감소시키거나 또는 최소화시키는 시간에서 및/또는 방법으로 실행될 수도 있다.

일 양태에서, 호스트 디바이스 및 플래시 메모리 디바이스는 디바이스들 사이의 통신이 통신 버스를 통해서 송신되도록 접속될 수도 있다. 호스트 디바이스의 빠른 메모리 리소스들에 직접 액세스하기 위해, 플래시 메모리 디바이스는 더 빠른 메모리 리소스들에 접속하는 통신 버스를 제어하는 버스 마스터로서 기능가능하도록 할 수도 있다. 다시 말해서, 플래시 메모리 디바이스 및 통신 버스는 플래시 메모리 디바이스로 하여금 통신 버스를 통해서 통신 트랜잭션들을 개시하도록 구성될 수도 있다. 여러 양태들은 호스트 디바이스 및 플래시 메모리 디바이스에 버스 마스터링 능력들을 제공하기 위해 상이한 통신 버스 구성들을 가질 수도 있다. 예를 들어, 각각의 디바이스에 대한 전용 통신 버스들은 오직 하나의 디바이스만이 각각의 통신 버스에 대해 버스 마스터로서 기능하도록 할 수도 있다. 또 다른 예로서, 통신 버스 구성은 PCI Express (PCIe) 또는 낮은 레이턴시 인터페이스 (LLI) 와 같은, 다중 디바이스 버스 마스터링을 지원하는 버스 표준들을 따를 수도 있다.

여러 양태들은 도 1 에 예시된 예시적인 FTL 호스트 캐싱 시스템 (10) 과 같은, 다양한 시스템들 내에 구현될 수도 있다. FTL 호스트 캐싱 시스템 (10) 은 프로세서 (24, 52), 메모리 또는 저장 유닛 (28, 30, 38, 58, 64), 통신 제어기 (26, 32, 54), 메모리 인터페이스 (60), 및 통신 링크 (34, 36, 40, 62, 66) 를 포함할 수도 있다. 일 양태에서, 프로세서는 중앙 처리 유닛 (CPU) (24) 또는 마이크로제어기 (μCtrl) (56) 일 수도 있다. 다른 양태들은 CPU (24) 및 마이크로제어기 (56) 를 대안적인 프로세서로 대체할 수도 있거나, 또는 추가적인 프로세서들을 포함할 수도 있다. 이러한 다른 프로세서들은 예를 들어, 하나 이상의 다른 CPU들 또는 마이크로제어기들, 마이크로프로세서, 그래픽 프로세싱 유닛 (GPU), 가속 프로세싱 유닛 (APU), 물리 프로세싱 유닛 (PPU) 을 포함할 수도 있다.

메모리 또는 저장 유닛들 (28, 30, 38, 58, 64) 은 다양한 메모리의 휘발성 및 비-휘발성 유형들 중 임의의 유형을 포함할 수도 있다. 일 양태에서, FTL 호스트 캐싱 시스템 (10) 은 SRAM (28, 58), ROM (30), DRAM (38), 및 플래시 메모리 (64) 를 포함할 수도 있다. 다른 유형들의 메모리는 자기, 광학, 또는 하이브리드 메모리 디바이스들을 포함할 수도 있다. 더욱이, FTL 테이블들 (68) 은 플래시 메모리 (64) 에 저장될 수도 있으며, 생성될 때, FTL 테이블들 (70) 의 복사본은 DRAM (38) 상에 저장될 수도 있다.

통신 제어기들 (26, 32, 54, 60) 은 FTL 호스트 캐싱 시스템 (10) 의 다수의 구성요소들 사이의 통신을 관리하도록 구성될 수도 있다. 각각의 통신 제어기 (26, 32, 54) 는 구체적으로 말하면 특정의 구성요소와 다른 구성요소들 사이의 통신을 관리할 수도 있다. 예를 들어, 직접 메모리 액세스 (DMA) 버스 제어기 (26) 는 CPU (24) 와, DMA 버스 제어기 (26) 의 일 측면 상의 DRAM (38) 및 다른 측면 상의 마이크로제어기 (56) 사이의 통신들을 관리하도록 구성될 수도 있다. 유사하게, DMA 버스 제어기 (54) 는 DMA 버스 제어기 (54) 의 일 측면 상의 마이크로제어기 (56) 와 다른 측면 상의 CPU (24) 사이의 통신을 관리할 수도 있다. CPU (24) 가 플래시 메모리 (64) 에의 직접 메모리 액세스를 승인받았으면, DMA 버스 제어기는 플래시 메모리 (64) 와 CPU (24) 사이의 어드레스 및 데이터 통신들을 관리하도록 구성될 수 있다. DRAM 제어기 (32) 는 일 측면 상의 DRAM (38) 과, CPU (24) 및 다른 측면 상의 마이크로제어기 (54) 사이의 통신을 관리하도록 구성될 수도 있다.

메모리 인터페이스 (60) 는 플래시 메모리 인터페이스 (60) 로서 구성될 수도 있다. 일 양태에서, 플래시 메모리 인터페이스 (60) 는 구체적으로 말하면 NAND 또는 NOR 플래시 메모리 아키텍처용으로 구성될 수도 있다. 일 양태에서, 플래시 메모리 인터페이스 (60) 는 플래시 메모리 인터페이스 (60) 가 페이지 어드레싱 단위로 (on a page addressing basis) 플래시 메모리 (64) 에의 판독 및 기록 액세스를 제공하는 NAND 아키텍처용으로 구성될 수도 있다.

통신 링크들 (34, 36, 40, 62, 66) 은 FTL 호스트 캐싱 시스템 (10) 의 여러 구성요소들 사이의 어드레스 및 데이터 통신들을 위한 경로를 제공할 수도 있다. 여러 양태들에서, 통신 링크들 (34, 36, 40, 62, 66) 은 단일 디바이스의 구성요소들 사이의 내부 통신, 또는 메인 디바이스와 주변장치 디바이스 사이의 외부 통신 용으로 구성될 수도 있다. 호스트 버스는 예를 들어, CPU (24), DMA 버스 제어기 (26), SRAM (28), ROM (30), 및 DRAM 제어기 (32) 사이에 통신 경로를 제공할 수도 있다. DRAM 버스 (36) 는 DRAM (36) 과, DRAM 제어기 (32) 와 같은 다른 구성요소들 사이에 통신 경로를 제공할 수도 있다. 스토리지 버스 (40) 는 DMA 버스 제어기들 (26, 54) 사이에 통신 경로를 제공할 수도 있다. 플래시 메모리 디바이스 버스 (62) 는 DMA 버스 제어기 (54), 마이크로제어기 (56), SRAM (58), 및 플래시 메모리 인터페이스 (60) 사이에 통신 경로를 제공할 수도 있다. 플래시 메모리 버스 (66) 는 플래시 메모리 (64) 와, 플래시 메모리 인터페이스 (60) 와 같은 다른 구성요소들 사이에 통신 경로를 제공할 수도 있다.

일부 양태들에서, 이들 구성요소들의 일부 또는 모두의 조합은 호스트 디바이스 (20) 및 플래시 메모리 디바이스 (50) 를 형성한다. 여러 양태들에서, 호스트 디바이스 (20) 및 플래시 메모리 디바이스 (50) 는 통신 링크 (40) 를 통해서 통신하는 능력을 가진 별개로 하우징된 디바이스들로서 구성될 수도 있다. 제한하는 것으로 의도되지 않는 예를 위해서, 호스트 디바이스 (20) 는 CPU (24), DMA 버스 제어기 (26), SRAM (28), ROM (30), DRAM 제어기 (32), 호스트 버스 (34), DRAM 버스 (36), DRAM (38), 및 스토리지 버스 (40) 의 부분 또는 모두로 이루어질 수도 있다. 이 예에 이어서, 플래시 메모리 디바이스 (50) 는 스토리지 버스 (40) 의 부분 또는 모두, DMA 버스 제어기 (54), 마이크로제어기 (56), SRAM (58), 플래시 메모리 인터페이스 (60), 플래시 메모리 디바이스 버스 (62), 플래시 메모리 (64), 및 플래시 메모리 버스 (66) 로 이루어질 수도 있다.

호스트 디바이스 (20) 의 양태에서, 구성요소들은 시스템 온 칩 (SoC) (22) 과 같은, 집적 회로에 추가로 결합될 수도 있다. SoC (22) 의 구성요소들은 CPU (24), DMA 버스 제어기 (26), SRAM (28), ROM (30), DRAM 제어기 (32), 호스트 버스 (34), 및 DRAM 버스 (36) 및 스토리지 버스 (40) 의 부분 또는 모두를 포함할 수도 있다. 이와 유사하게, 플래시 메모리 디바이스 (50) 는 관리된 플래시 메모리 제어기 (52) 와 같은, 집적 회로에의 구성요소들의 조합을 더 포함할 수도 있다. 관리된 플래시 메모리 제어기 (52) 의 구성요소들은 스토리지 버스 (40) 의 부분 또는 모두 및 플래시 메모리 버스 (66), DMA 버스 제어기 (54), 마이크로제어기 (56), SRAM (58), 플래시 메모리 인터페이스 (60), 및 플래시 메모리 디바이스 버스 (62) 를 포함할 수도 있다.

도 2 는 FTL 호스트 캐싱 시스템 (10) 에서의 사용에 적합한 예시적인 모바일 디바이스 (200) 를 예시한다. 여러 양태들에서, 모바일 디바이스 (200) 는 터치스크린 제어기 (204) 및 내부 메모리 (206) 에 커플링된 프로세서 (202) 를 포함할 수도 있다. 내부 메모리 (206) 는 휘발성 또는 비-휘발성 메모리일 수도 있으며, 또한 보안 및/또는 암호화된 메모리, 또는 비보안 및/또는 비암호화된 메모리, 또는 이들의 임의의 조합일 수도 있다. 터치스크린 제어기 (204) 및 프로세서 (202) 는 또한 저항-감지 터치스크린, 정전용량-감지 터치스크린, 적외선 감지 터치스크린, 등과 같은, 터치스크린 패널 (212) 에 커플링될 수도 있다. 모바일 디바이스 (200) 는 하나 이상의 라디오 신호 송수신기들 (208) (예컨대, Peanut®, Bluetooth®, Zigbee®, Wi-Fi, RF 라디오) 및 전송 및 수신용 안테나들 (210) 을 가질 수도 있다. 송수신기들 (208) 및 안테나들 (210) 은 여러 무선 송신 프로토콜 스택들 및 인터페이스들을 구현하기 위해 위에서 언급된 회로와 함께 사용될 수도 있다. 모바일 디바이스 (200) 는 셀룰러 네트워크를 통해서 통신을 가능하게 하는 셀룰러 네트워크 무선 모뎀 칩 (216) 을 포함할 수도 있다. 모바일 디바이스 (200) 는 프로세서 (202) 에 커플링되어 플래시 메모리 디바이스 (50) 에 접속하도록 구성되는 주변장치 디바이스 접속 포트 (218) 를 포함할 수도 있다. 주변장치 디바이스 접속 포트 (218) 는 하나의 접속 유형을 수용하도록 단일로 (singularly) 구성될 수도 있거나, 또는 USB, FireWire, 썬더볼트 (Thunderbolt), 또는 PCIe 와 같은, 여러 유형들의 물리 및 통신 접속들을 수용하도록 복합적으로 구성될 수도 있다. 모바일 디바이스 (200) 는 또한 오디오 출력들을 제공하기 위한 스피커들 (214) 을 포함할 수도 있다. 모바일 디바이스 (200) 는 또한 본원에서 설명된 구성요소들의 모두 또는 일부를 포함하기 위한, 플라스틱, 금속, 또는 재료들의 조합으로 이루어지는, 하우징 (220) 을 포함할 수도 있다.

호스트 디바이스의 빠른 메모리 리소스들에서 FTL 테이블들을 캐싱하는 여러 양태들은, 도 3 에 양태가 예시된 FTL 호스트 캐시 초기화 방법 (300) 을 FTL 호스트 캐싱 시스템 (10) 에 의해 실행하는 것을 수반할 수도 있다. FTL 호스트 캐시 초기화 방법 (300) 은 호스트 디바이스 (20) 에 의해 개시될 수도 있다. 방법 (300) 을 시작하기 위해, 호스트 디바이스 (20) 는 블록 (302) 에서, 일반적으로 사용되거나 또는 독점적인 프로세스에 의해, 플래시 메모리 디바이스 (50) 를 초기화할 수도 있다. 메모리 디바이스 (50) 의 초기화 동안 또는 완료되자 마자, 호스트 디바이스 (20) 는 결정 블록 (304) 에서 플래시 메모리 디바이스 (50) 에 쿼리하여 플래시 메모리 디바이스 (50) 가 FTL 호스트 캐싱을 지원하는지 여부를 결정할 수도 있다. 플래시 메모리 디바이스 (50) 가 FTL 호스트 캐싱을 지원하지 않을 때 (즉 결정 블록 (304) = "아니오"), 호스트 디바이스 (20) 는 블록 (306) 에서 플래시 메모리 디바이스 (50) 를 일반적인 플래시 메모리 디바이스로서 취급할 것이다.

플래시 메모리 디바이스 (50) 가 FTL 호스트 캐싱을 지원한다고 호스트 디바이스 (20) 가 결정하면 (즉 결정 블록 (304) = "예"), 호스트 디바이스 (22) 는 블록 (308) 에서 플래시 메모리 디바이스 (50) 에게 FTL 테이블들 (68) 의 사이즈에 대해 쿼리할 수도 있다. 일단 호스트 디바이스가 FTL 테이블들 (68) 의 사이즈를 통지 받으면, 블록 (312) 에서, 호스트 디바이스 (20) 는 그의 DRAM (38) 을 재분할하고, FTL 테이블들 (70) 의 복사본을 저장하여 수정하기에 충분한 공간을 확보할 수도 있다. 블록 (314) 에서, 호스트 디바이스 (20) 는 FTL 테이블들 (70) 의 복사본용으로 재분할 및 확보된 DRAM (38) 의 부분에 대한 플래시 메모리 디바이스 (50) 에의, 판독 및/또는 기록 특권들을 포함한, 직접 메모리 액세스를 승인할 수도 있다. 일단 FTL 테이블들 (70) 의 복사본이 DRAM (38) 에 저장되면, 호스트 디바이스 (20) 는 블록 (316) 에서 FTL 테이블들 (68) 의 복사가 완료되었다는 통지를 수신할 수도 있다.

플래시 메모리 디바이스 (50) 가 FTL 호스트 캐싱을 지원한다고 호스트 디바이스 (20) 가 결정하면 (즉 결정 블록 (304) = "예"), 호스트 디바이스 (20) 는 결정 블록 (310) 에서 그의 자신의 DRAM (38) 내에 FTL 테이블들 (68) 의 모두를 저장할 수 있는지 여부를 결정할 수도 있다. 호스트 디바이스 (20) 가 그의 자신의 DRAM (38) 내에 FTL 테이블들 (68) 의 모두를 저장할 수 있으면 (즉 결정 블록 (310) = "예"), 호스트 디바이스 (20) 는 (본원에서 설명된 바와 같이) 블록 (312) 에서 그의 DRAM (38) 을 재분할하고, 블록 (314) 에서 플래시 메모리 디바이스 (50) 에의 직접 메모리 액세스를 승인하고, 그리고 블록 (316) 에서 FTL 테이블들 (68) 의 복사가 완료되었다는 통지를 수신할 수도 있다.

호스트 디바이스 (20) 가 그의 자신의 DRAM (38) 내에 FTL 테이블들 (68) 의 모두를 저장할 수 없으면 (즉 결정 블록 (310) = "아니오"), 호스트 디바이스 (20) 는 블록 (318) 에서 플래시 메모리 디바이스 (50) 에게 DRAM (38) 에서 이용가능한 공간의 양을 통지하고, 블록 (312) 을 참조하여 위에서 설명된 동작들을 속행할 수도 있다. 호스트 디바이스 (20) 가 FTL 테이블들 (68) 의 모두를 저장할 수 없으면 (즉 결정 블록 (310) = "아니오"), 블록 (320) 에서, 호스트 디바이스 (20) 는 플래시 메모리 디바이스 (50) 를 일반적인 플래시 메모리 디바이스, 또는 FTL 호스트 캐싱을 지원하지 않는 플래시 메모리 디바이스로서 취급할 수도 있다.

FTL 호스트 캐시 초기화 방법 (300) 의 대안 양태들은 FTL 호스트 캐싱을 초기화하고 호스트 디바이스 (20) 에게 쿼리하여 호스트 디바이스 (20) 가 FTL 호스트 캐싱을 지원하는지 여부를 결정하는 플래시 메모리 디바이스 (50) 를 포함할 수도 있다. 이러한 양태에서, 부팅 시 및 FTL 호스트 캐시 초기화 방법 (300) 을 실행하기 전에, 호스트 디바이스 (20) 는 FTL 호스트 캐싱을 예상하여 그의 DRAM (38) 의 재분할 부분을 확보할 수도 있다. 플래시 메모리 디바이스 (50) 가 호스트 디바이스 (20) 에 접속될 때, FTL 호스트 캐시 초기화 방법 (300) 이 시작될 수도 있으며, 그 때, 플래시 메모리 디바이스 (50) 는 호스트 디바이스 (20) 에 쿼리하여, 호스트 디바이스 (20) 가 FTL 호스트 캐싱을 지원하는지 여부를 결정할 수도 있다. 호스트 디바이스 (20) 가 FTL 호스트 캐싱을 지원하지 않으면, 플래시 메모리 디바이스 (50) 는 호스트 디바이스 (20) 를 일반적인 호스트 디바이스로서 취급할 수도 있다. 호스트가 FTL 호스트 캐싱을 지원하면, FTL 호스트 캐시 초기화 방법 (300) 의 나머지 동작 (예컨대, 블록들 (308-320)) 이 실행될 수도 있다.

FTL 호스트 캐싱 초기화 방법 (300) 의 여러 양태들은 도 4 에 예시된 추가 동작들을 포함할 수도 있다. 이러한 동작들은 도 3 에 예시된 동작들과 동시에, 적당한 순서로 발생할 수도 있다. 일단 호스트 디바이스 (20) 에 의해 초기화되면, 블록 (400) 에서, 플래시 메모리 디바이스 (50) 가 호스트 디바이스 (20) 로부터의 쿼리에 응답하여, 플래시 메모리 디바이스 (50) 가 FTL 호스트 캐싱을 지원하는지를 결정할 수도 있다. FTL 호스트 캐싱 초기화 방법 (300) 의 양태들은 수동 (passive) 또는 능동 (active) 인 이 쿼리에 대한 응답을 포함할 수도 있다. 예를 들어, 응답이 능동이면, 호스트 디바이스 (20) 는 플래시 메모리 디바이스 (50) 의 특정의 레지스터 또는 메모리 로케이션에서의 값을 판독하여 FTL 호스트 캐싱의 지원을 결정할 수도 있다. 능동 응답은, 예를 들어, 플래시 메모리 디바이스 (50) 가 FTL 호스트 캐싱을 지원하는지 여부를 나타내는 특정의 신호를 호스트 디바이스 (20) 로 플래시 메모리 디바이스 (50) 가 전송하는 것을 포함할 수도 있다. 능동 응답 양태에서, 응답의 부족 (lack) 은 또한 플래시 메모리 디바이스 (20) 가 FTL 호스트 캐싱을 지원하는지 여부의 표시일 수도 있다.

플래시 메모리 디바이스 (50) 가 FTL 호스트 캐싱과 양립가능하면, 블록 (402) 에서, 플래시 메모리 디바이스는 FTL 테이블들 (68) 의 사이즈에 대한 호스트 디바이스 (20) 로부터의 쿼리에 응답할 수도 있다 응답은 전체 FTL 테이블들의 복사본을 저장하는데 필요한 메모리의 양을 나타내는 값을 반환하는 것을 수반할 수도 있다. 블록 (400) 에서 FTL 호스트 캐싱 호환성을 결정하기 위한, 쿼리에 대한 응답과 아주 유사하게, 블록 (402) 에서, 이 응답의 여러 양태들은 능동 및 수동 응답들을 포함할 수도 있다. 호스트 디바이스 (20) 가 플래시 메모리 디바이스 (50) 에게 직접 메모리 액세스 허가들을 승인하였으면, 블록 (404) 에서, 플래시 메모리 디바이스 (50) 가 완전한 FTL 테이블들 (70) 의 복사본을 호스트 디바이스 (20) 의 DRAM (38) 에 기록할 수도 있다. 대안적으로, 호스트 디바이스 (20) 가 FTL 테이블들 (68) 의 모두를 저장할 수 없다고 호스트 디바이스 (20) 가 결정하면, 플래시 메모리 디바이스 (50) 는 플래시 메모리 디바이스 (50) 에게 직접 메모리 액세스 허가들을 승인한 후, 블록 (408) 에서, FTL 테이블들 (70) 의 부분 복사본을 DRAM (38) 에 기록할 수도 있다. 일단 이 동작이 완료되면, 블록 (406) 에서, 플래시 메모리 디바이스 (50) 는 FTL 테이블들 (70) 의 복사본이 호스트 디바이스 (20) 의 DRAM (38) 에 저장되어 있다는 것을 나타내는 통지를 호스트 디바이스 (20) 로 전송할 수도 있다.

플래시 메모리 (64) 로부터 및/또는 플래시 메모리 (64) 로의 판독 및/또는 기록 동작들을 돕기 위해, FTL 호스트 캐싱의 여러 양태들은 플래시 메모리 디바이스 (50) 가 호스트 디바이스 (20) 의 DRAM (38) 에 저장된 FTL 테이블들 (70) 의 복사본으로부터 판독하거나 및/또는 그에 기록하는 것을 포함할 수도 있다. 일 양태에서, 플래시 메모리 디바이스 (50) 로부터의 판독 동작 (500) 은 도 5 에 예시된 바와 같이, 구현될 수도 있다. 블록 (502) 에서, 플래시 메모리 디바이스 (50) 는 플래시 메모리 (64) 의 논리 어드레스와 연관되는, 호스트 디바이스 (20) 로부터의 판독 요청을 수신할 수도 있다. 요청된 동작 및 논리 어드레스를 통지 받았으면, 플래시 메모리 디바이스 (50) 는 기록 동작을 개시할 수도 있다. 블록 (504) 에서, 플래시 메모리 디바이스 (50) 가 호스트 디바이스 (20) 의 DRAM (38) 에 로케이트된 FTL 테이블들 (70) 의 복사본에 직접 액세스할 수도 있다. 판독 동작 (500) 의 양태에서, DRAM (38) 에의 직접 메모리 액세스에 대해 플래시 메모리 디바이스 (50) 에게 승인된 허가들은, 플래시 메모리 디바이스 (50) 로 하여금, 디바이스들 (20, 50) 을 접속하는 스토리지 버스 (40) 를 통해서, 버스 마스터링하거나 또는 지령들을 발하도록 할 수도 있다. 일단 호스트 디바이스 (20) 의 DRAM (38) 에 직접 액세스하면, 블록 (506) 에서, 플래시 메모리 디바이스 (50) 가 논리 어드레스와 연관되는 FTL 테이블들 (70) 의 복사본으로부터 정보를 판독/취출할 수도 있다.

FTL 테이블들 (70) 의 복사본으로부터 필요한 정보를 취출하였으면, 블록 (508) 에서, 플래시 메모리 디바이스 (50) 는 논리 어드레스를 플래시 메모리 (64) 의 물리 어드레스로 변환할 수도 있다. 블록 (510) 에서, 플래시 메모리 디바이스 (50) 가 플래시 메모리 (64) 에 액세스하고, 블록 (512) 에서 물리 어드레스에 로케이트된 데이터를 취출/판독할 수도 있다. 그의 플래시 메모리 (64) 로부터 데이터를 취출한 후, 블록 (514) 에서, 플래시 메모리 디바이스 (50) 가 데이터를 호스트 디바이스 (20) 로 반환하고 판독 요청을 완료할 수도 있다.

또 다른 양태에서, 도 6 은 플래시 메모리 디바이스 (50) 에의 기록 동작 (600) 이 구현될 수도 있음을 예시한다. 블록 (602) 에서, 플래시 메모리 디바이스 (50) 는 플래시 메모리 (64) 의 논리 어드레스와 연관되는, 호스트 디바이스 (20) 로부터의 기록 요청을 수신할 수도 있다. 요청된 동작 및 논리 어드레스를 통지 받으면, 플래시 메모리 디바이스 (50) 는 기록 동작을 개시할 수도 있다. 블록 (604) 에서, 플래시 메모리 디바이스 (50) 가 이제 호스트 디바이스 (20) 의 DRAM (38) 에 로케이트된 FTL 테이블들 (70) 의 복사본에 직접 액세스할 수도 있다. 기록 동작 (500) 의 양태에서, DRAM (38) 에의 직접 메모리 액세스에 대해 플래시 메모리 디바이스 (50) 에게 승인된 허가들은, 플래시 메모리 디바이스 (50) 로 하여금, 디바이스들 (20, 50) 을 접속하는 스토리지 버스 (40) 를 통해서, 버스 마스터링하거나 또는 지령들을 발하도록 할 수도 있다. 일단 호스트 디바이스 (20) 의 DRAM (38) 에 직접 액세스하면, 블록 (606) 에서, 플래시 메모리 디바이스 (50) 가 논리 어드레스와 연관되는 FTL 테이블들 (70) 의 복사본으로부터 정보를 판독/취출할 수도 있다.

FTL 테이블들 (70) 의 복사본으로부터 필요한 정보를 취출하였으면, 블록 (608) 에서, 플래시 메모리 디바이스 (50) 는 논리 어드레스를 플래시 메모리 (64) 의 물리 어드레스로 변환할 수도 있다. 블록 (610) 에서, 플래시 메모리 디바이스 (50) 가 플래시 메모리 (64) 에 액세스하고, 블록 (612) 에서 기록 요청과 연관되는 데이터를 플래시 메모리 (64) 의 물리 어드레스에 기록할 수도 있다. 데이터가 플래시 메모리 (64) 에 저장될 때, 블록 (614) 에서, 플래시 메모리 디바이스 (50) 는 호스트 디바이스 (20) 의 DRAM (38) 에 로케이트된 FTL 테이블들 (70) 의 복사본에 다시 직접 액세스할 수도 있다. 블록 (616) 에서, 플래시 메모리 디바이스 (50) 가 기록 요청의 데이터를 저장하는데 사용되는 물리 어드레스들에서의 변화들을 반영하기 위해 FTL 테이블들 (70) 의 복사본을 업데이트할 수도 있다. 일단 데이터가 플래시 메모리 (64) 에 기록되고 FTL 테이블들 (70) 의 복사본이 업데이트되었으면, 블록 (618) 에서, 플래시 메모리 디바이스 (50) 는 플래시 메모리 디바이스 (50) 에의 기록 동작 (600) 이 완료되었다는 통지를 전송할 수도 있다.

플래시 메모리 디바이스 (50) 에의 기록 동작 (600) 의 대안 양태에서는, 특정의 논리 및 물리 어드레스들에 기록하는 것이 불필요할 수도 있다. 대신, 데이터를 기록할 빈 공간이 존재하는 장소를, 그리고 어쩌면 그 공간이 데이터를 저장하는데 좋은 상태에 있는지를 파악하는 것만으로도 충분할 수도 있다. 따라서, 다양한 양태들에서 논리 어드레스를 제공하거나 또는 제공하지 않을 수도 있는 블록 (602) 에서 호스트 디바이스 (20) 로부터 기록 요청을 수신한 후, 블록 (620) 에서, 플래시 저장 디바이스 (50) 가 그의 SRAM (58) 에 저장된 테이블들에 액세스할 수도 있다. SRAM (58) 에서의 이들 테이블들은 플래시 메모리 (64) 에서, 자유 저장 공간의 로케이션, 또는 블록들의 로케이션을 나타낼 수도 있는 정보 및 플래시 메모리 (64) 에 대한 웨어 레벨링 정보 (wear leveling information) 를 포함할 수도 있다. 블록 (622) 에서, 플래시 저장 디바이스 (50) 는 SRAM (58) 에서의 테이블들로부터 데이터를 저장하기에 적합한 공간에 대한 플래시 메모리 (64) 에 관련된 자유 저장 공간 및/또는 웨어 레벨링 정보를 취출할 수도 있다. 이 정보에 의해, 블록 (624) 에서, 플래시 저장 디바이스 (50) 는 데이터를 메모리에 기록할 장소의 물리 어드레스를 결정하고, 블록 (610) 에서 플래시 메모리 (64) 에 액세스하고, 본원에서 설명하는 바와 같이 플래시 메모리 디바이스 (50) 에의 기록 동작 (600) 의 나머지를 속행할 수도 있다.

다른 양태들은 FTL 테이블들 (70) 의 복사본에게 이루어진 변화들을 반영하기 위해 FTL 테이블들 (68) 을 업데이트하는 것을 포함할 수도 있다. 하나의 이러한 양태는 플래시 메모리 디바이스 (50) 에의 기록 동작 (600) 의 일부로서 또는 그 이후에 FTL 테이블들 (68) 을 업데이트하는 것을 포함할 수도 있다. 예를 들어, 블록 (616) 에서, FTL 테이블들 (68) 이 FTL 테이블들 (70) 의 복사본을 업데이트한 후 임의의 지점에서 업데이트될 수도 있다. 이러한 업데이트는 FTL 테이블들 (70) 의 복사본을 복사하거나 또는 단지 FTL 테이블들 (70) 의 복사본에 대한 업데이트들을 플래시 메모리 (64) 에 복사하는 것을 포함할 수도 있다. 또한, FTL 테이블들 (68) 에 대한 업데이트들이 FTL 테이블들의 복사본에 대한 업데이트들 이전에 또는 동시에 일어날 수도 있는 것으로 생각된다. 추가 양태들은 가용 리소스들에 기초하여, 미리 정의된 규칙에 의해 또는 동적으로 FTL 테이블들 (68) 을 업데이트하는 것을 포함할 수도 있다. 예를 들어, 미리 정의된 규칙은 FTL 테이블들 (68) 의 업데이트를 주기적으로, 스케쥴, 가용 리소스들에 기초하여, 지령에 응답하여, 또는 파라미터들의 세트에 기초하여, 실행할 수도 있다. 예를 들어, FTL 테이블들 (68) 을 동적으로 업데이트하는 것은, 디바이스들 (20, 50) 중 어느 하나 또는 양자에 의한, FTL 호스트 캐싱 시스템 (10) 의 성능에 대한 최저 비용으로 업데이트를 실행하는데 요구되는 가용 리소스들, 전력, 및/또는 시간의 결정에 기초하여 일어날 수도 있다. 이러한 시간들은 FTL 호스트 캐싱 시스템 (10) 이 휴지 중이거나 또는 최소의 프로세스들이 동작 중일 때 일 수도 있다.

도 7 은 호스트 디바이스 (20) 의 부트 시퀀스 동안 FTL 호스트 캐싱 초기화 방법 (300) 의 프로세스 흐름의 양태를 예시한다. 양태들은 FTL 호스트 캐싱 초기화 방법 (300) 이 호스트 디바이스 (20) 의 부트 시퀀스 동안 이외의 시간들에서 실행되는 것으로 생각된다. 예를 들어, 플래시 메모리 디바이스 (50) 의 접속 시, 한편 호스트 디바이스 (20) 는 동작중이다. 도 7 에서, 호스트 디바이스 (50) 의 CPU (24) 는 신호 (700) 를 전송하여, BIOS 및 드라이버들과 같은, 호스트 디바이스 (50) 의 ROM (30) 내 부트 정보에 액세스하여, 초기화 방법 (300) 의 코드 프로세스들을 실행한다. CPU (24) 는 ROM (30) 으로부터 반환 신호 (702) 를 통해서 정보 및 코드 프로세스들을 수신할 수도 있다. CPU (24) 는 플래시 메모리 디바이스 (50) 와 같은, 접속된 주변장치 디바이스들을 체크하여 초기화하고, FTL 호스트 캐싱 호환성, 및 FTL 테이블들 (58) 의 사이즈에 대해 쿼리할 수도 있다. 이를 행하기 위해, CPU (24) 는 신호 (704) 를 호스트 디바이스 (50) 의 DMA 버스 제어기 (26) 로 전송하고, 그 신호는 신호 (706) 로서 플래시 메모리 디바이스 (50) 의 DMA 버스 제어기 (54) 로 포워딩될 수도 있다. 신호 (706) 는 플래시 메모리 디바이스 (50) 의 마이크로제어기 (56) 로 신호 (708) 로서 포워딩될 수도 있다. 일부 양태들에서, 마이크로제어기 (56) 는 응답 신호 (710) 를 CPU (24) 로 DMA 버스 제어기 (54) 를 통해서 되전송하고 신호 (710) 를 신호 (712) 로서 DMA 버스 제어기로 그리고, 신호 (714) 로서 CPU (24) 로 포워딩함으로써, CPU (24) 의 쿼리에 응답할 수도 있다.

FTL 테이블들 (58) 의 사이즈를 통지 받으면, CPU (24) 는 신호 (716) 를 전송하여 호스트 디바이스 (20) 의 DRAM (38) 을 체크하여 FTL 테이블들 (58) 의 모두를 저장하는 것이 가능한지 여부를 결정할 수도 있으며, CPU (24) 는 FTL 테이블들 (58) 에 대한 DRAM (38) 의 부분을 재분할하여 확보할 수도 있다. 신호 (716) 가 DRAM 제어기 (32) 에 의해 수신되고, DRAM (38) 으로 전송되는 신호 (718) 로 해석될 수도 있다. DRAM 제어기 (32) 는 DRAM (38) 으로부터 반환 신호 (720) 를 수신하고, 반환 신호 (722) 를 CPU (24) 로 전송하여, 이들 동작의 부분들을 완료할 수도 있다.

CPU (24) 는 신호 (724) 를 DMA 버스 제어기 (26) 로 전송함으로써, 마이크로제어기 (56) 에게 DRAM (38) 에의 직접 메모리 액세스를 제공하고 FTL 테이블들 (70) 의 복사본을 요청할 수도 있다. 신호 (724) 는 DMA 버스 제어기 (54) 로 신호 (726) 로서, 그리고, 마이크로제어기 (56) 로 신호 (728) 로서 포워딩될 수도 있다. 마이크로제어기 (56) 는 신호 (730) 를 전송하여, 플래시 메모리 (64) 내 FTL 테이블들 (58) 에 액세스하여 FTL 테이블들 (70) 의 복사본을 취출할 수도 있다. 메모리 인터페이스 (60) 는 신호 (730) 를 수신하고 그 신호를 플래시 메모리 (64) 로 전송되는 신호 (732) 로 해석한다. 메모리 인터페이스 (60) 는 FTL 테이블들 (70) 의 복사본을 나타내는 반환 신호 (734) 를 메모리 (64) 로부터 수신하고, 그 신호 (734) 를 신호 (736) 로서 마이크로제어기 (56) 로 포워딩한다.

DRAM (38) 에의 직접 메모리 액세스를 승인받았으면, 마이크로제어기 (56) 는 그것을 DRAM (38) 에 접속하는 버스들 (34, 40) 을 버스 마스터링할 수도 있다. 마이크로제어기 (56) 는 신호 (738) 을 전송하여, FTL 테이블들 (70) 의 복사본을 DRAM (38) 에 기록할 수도 있다. 신호 (738) 는 DMA 제어기 (54) 에 의해, 신호 (740) 로서, DMA 제어기 (26) 로 포워딩되며, 그 DMA 제어기 (26) 는 신호 (742) 를 DRAM 제어기 (32) 로 포워딩한다. 신호 (742) 는 신호 (744) 로서 해석되어 DRAM (38) 으로 전송된다. DRAM 제어기 (32) 는 신호 (746) 를 수신함으로써 FTL 테이블들 (70) 의 복사본이 DRAM (38) 에 저장되는 때를 식별하고, 신호 (748) 를 마이크로제어기 (56) 로 전송하여 기록이 완료되었다는 것을 표시할 수도 있다. DMA 버스 제어기 (26) 는 신호 (748) 을 수신하여 그것을 신호 (750) 로서 포워딩할 수도 있으며, 그 신호 (750) 는 DMA 버스 제어기 (54) 에 의해 수신되어 마이크로제어기 (56) 로 신호 (752) 로서 포워딩될 수도 있다.

일단 FTL 테이블들 (70) 의 복사본이 DRAM (38) 에 기록되면, 마이크로제어기 (56) 는 신호 (754) 를 전송함으로써 FTL 호스트 캐싱 초기화 방법 (300) 이 완료되었다는 것을 CPU (24) 로 시그널링할 수도 있다. DMA 버스 제어기 (54) 는 신호 (754) 를 수신하여 그것을 신호 (756) 로서 DMA 버스 제어기 (16) 로 포워딩할 수도 있으며, 그 DMA 버스 제어기 (16) 는 신호 (758) 를 CPU (24) 로 포워딩할 수도 있다.

CPU (24) 는 신호 (760) 를 전송함으로써, FTL 호스트 캐싱 초기화 방법 (300) 의 완료를 수신응답하고, 판독 및 기록 동작들을 위해 DRAM (38) 내 FTL 테이블들 (70) 의 복사본을 이용하기 시작하라는 허가를 마이크로제어기에게 명령하거나 또는 부여할 수도 있다. DMA 버스 제어기 (26) 는 신호 (760) 를 수신하여 그것을 DMA 버스 제어기 (54) 로 신호 (762) 로서 포워딩할 수도 있으며, 그 신호 (762) 는 DMA 버스 제어기 (54) 로부터 마이크로제어기 (56) 로 신호 (764) 로서 중계될 수도 있다. 마이크로제어기 (56) 는 CPU (24) 로부터 허가의 수신응답을 신호 (766) 로서 반환할 수도 있다. DMA 버스 제어기 (54) 는 신호 (766) 를 수신하고 그것을 DMA 버스 제어기 (26) 로 신호 (768) 로서, 그리고 DMA 버스 제어기 (26) 로부터 CPU (24) 로 신호 (780) 로 포워딩할 수도 있다. 도 8 은 플래시 메모리 디바이스 (50) 로부터의 판독 동작 (500) 의 프로세스 흐름의 양태를 예시한다. CPU (24) 는 논리 어드레스에 대한 판독 요청을 마이크로제어기 (56) 로 발하여, 그 요청을 운반하는 신호 (800) 를 DMA 버스 제어기 (26) 를 통해서 신호 (802) 로서 전송할 수도 있다. DMA 제어기 (54) 는 신호 (802) 를 수신하고 그것을 마이크로제어기 (56) 로 신호 (804) 로서 포워딩할 수도 있다.

FTL 호스트 캐싱 초기화 동안 DRAM (38) 에의 직접 메모리 액세스를 승인 받았으면, 마이크로제어기 (56) 는 그것을 DRAM (38) 에 접속하는 버스들 (34, 40) 을 버스 마스터링할 수도 있다. 마이크로제어기는 신호 (806) 를 전송하여, FTL 테이블들 (70) 의 복사본에서의 논리 어드레스와 연관되는 정보를 DRAM (38) 으로부터 취출/판독할 수도 있다. DMA 버스 제어기 (54) 는 신호 (806) 를 DMA 버스 제어기 (26) 로 신호 (808) 로서 포워딩할 수도 있으며, 그 신호 (808) 는 DRAM 제어기 (32) 로 신호 (810) 로서 포워딩될 수도 있다. DRAM 제어기 (32) 는 신호 (810) 를 해석하고 신호 (812) 를 DRAM (38) 으로 전송할 수도 있다. DRAM 제어기 (32) 는 DRAM (38) 으로부터 반환 신호 (814) 를 수신할 수도 있으며, 그 반환 신호 (814) 는 DMA 버스 제어기 (26) 로 신호 (816) 로서 전송되고, DMA 버스 제어기 (54) 로 신호 (818) 로서 포워딩되고, 마지막으로 마이크로제어기 (56) 에 의해 신호 (820) 로서 수신될 수도 있다. FTL 테이블들 (70) 의 복사본으로부터 취출된 정보에 의해, 마이크로제어기 (56) 는 이제 논리 어드레스를 플래시 메모리 (64) 의 물리 어드레스로 변환할 수도 있다.

물리 어드레스를 결정하였으면, 마이크로제어기 (56) 는 신호 (822) 를 전송함으로써 메모리 (64) 에 액세스하고 물리 어드레스에 로케이트된 데이터를 취출/판독할 수도 있다. 메모리 인터페이스 (60) 는 신호 (822) 를 해석하고 신호 (824) 를 메모리 (64) 로 전송할 수도 있다. 물리 어드레스에서의 정보를 나타내는, 메모리 (64) 로부터의 반환 신호 (826) 는 메모리 인터페이스 (60) 에 의해 수신되어 마이크로제어기 (56) 로 신호 (828) 로서 전송될 수도 있다. 마이크로제어기 (56) 는 신호 (830) 를 전송함으로써 CPU (24) 에 의한 사용을 위해 그 취출된 데이터를 DRAM (38) 으로 포워딩할 수도 있다. DMA 버스 제어기 (54) 는 신호 (830) 를 수신하고 그것을 DMA 버스 제어기 (26) 로 신호 (832) 로서 포워딩할 수도 있으며, 그 신호 (832) 는 DRAM 제어기 (32) 로 신호 (834) 로서 포워딩될 수도 있다. DRAM 제어기 (32) 는 신호 (834) 를 해석하고 신호 (836) 를 전송하여 메모리 (64) 의 물리 어드레스로부터 판독된 데이터를 DRAM (38) 에 기록할 수도 있다. DRAM (38) 에의 기록의 완료를 나타내는 반환 신호 (838) 는 DRAM 제어기 (32) 에 의해 수신되고, DMA 버스 제어기 (26) 로 신호 (840) 로서 포워딩될 수도 있으며, 그 DMA 버스 제어기 (26) 는 그 신호를 DMA 버스 제어기 (54) 로 신호 (842) 로서 중계할 수도 있으며, 그 DMA 버스 제어기 (54) 는 그 신호를 마이크로제어기 (56) 로 신호 (844) 로서 중계할 수도 있다.

일단 메모리 (64) 의 물리 어드레스로부터의 데이터 판독이 DRAM (38) 에 기록되면, 마이크로제어기 (56) 는 신호 (846) 를 전송함으로써, 요청된 판독 동작이 완료되었으며 데이터가 DRAM (38) 에서 이용가능하다는 통지를 CPU (24) 로 전송할 수도 있다. DMA 버스 제어기 (54) 는 통지 신호 (846) 를 수신하고 그것을 DMA 버스 제어기 (26) 로 신호 (848) 로서 포워딩할 수도 있으며, 그 신호 (848) 은 CPU (24) 로 신호 (850) 로서 포워딩될 수도 있다.

도 9 는 플래시 메모리 디바이스 (50) 에의 기록 동작 (600) 의 프로세스 흐름의 양태를 예시한다. CPU (24) 는 논리 어드레스에 대한 기록 요청을 마이크로제어기 (56) 로 발하여, 그 요청을 운반하는 신호 (900) 를 DMA 버스 제어기 (26) 를 통해서 신호 (902) 로서 전송할 수도 있다. DMA 제어기 (54) 는 신호 (902) 를 수신하고 그것을 마이크로제어기 (56) 로 신호 (904) 로서 포워딩할 수도 있다.

FTL 호스트 캐싱 초기화 동안 DRAM (38) 에의 직접 메모리 액세스를 승인 받았으면, 마이크로제어기 (56) 는 그것을 DRAM (38) 에 접속하는 버스들 (34, 40) 을 버스 마스터링할 수도 있다. 마이크로제어기는 신호 (906) 를 전송하여, FTL 테이블들 (70) 의 복사본에서의 논리 어드레스와 연관되는 정보를 DRAM (38) 으로부터 취출/판독할 수도 있다. DMA 버스 제어기 (54) 는 신호 (906) 를 DMA 버스 제어기 (26) 로 신호 (908) 로서 포워딩할 수도 있으며, 그 신호 (908) 는 DRAM 제어기 (32) 로 신호 (910) 로서 포워딩될 수도 있다. DRAM 제어기 (32) 는 신호 (910) 를 해석하고 신호 (912) 를 DRAM (38) 으로 전송할 수도 있다. DRAM 제어기 (32) 는 DRAM (38) 으로부터 반환 신호 (914) 를 수신할 수도 있으며, 그 반환 신호 (814) 는 DMA 버스 제어기 (26) 로 신호 (916) 로서 전송되고, DMA 버스 제어기 (54) 로 신호 (918) 로서 포워딩되고, 마지막으로 마이크로제어기 (56) 에 의해 신호 (920) 로서 수신될 수도 있다. FTL 테이블들 (70) 의 복사본으로부터 취출된 정보에 의해, 마이크로제어기 (56) 는 이제 논리 어드레스를 플래시 메모리 (64) 의 물리 어드레스로 변환할 수도 있다.

기록 데이터를 저장할 장소에 관한 정보를 수신하였으면, 마이크로제어기 (56) 는 신호 (922) 를 전송함으로써 DRAM (38) 으로부터 기록 데이터를 취출할 수도 있다. DMA 버스 제어기 (54) 는 신호 (922) 를 수신하여 그것을 신호 (924) 로서 DMA 버스 제어기 (26) 로 포워딩할 수도 있다. DRAM 제어기 (32) 는 DMA 버스 제어기 (26) 로부터 신호 (926) 를 수신하고 그것을 신호 (928) 로서 해석하여 신호 (928) 를 DRAM (38) 으로 전송할 수도 있다. DRAM 제어기 (32) 는 DRAM (38) 으로부터 판독된 기록 데이터를 신호 (930) 로서 수신하고 그 기록 데이터를 마이크로제어기 (56) 로 신호 (932) 로서 포워딩할 수도 있다. DMA 버스 제어기 (26) 는 신호 (932) 를 수신하고 그것을 신호 (934) 로서 DMA 버스 제어기 (54) 로 포워딩할 수도 있으며, 그 신호 (934) 는 마이크로제어기 (56) 로 신호 (936) 로서 포워딩될 수도 있다.

물리 어드레스를 결정하고 기록 데이터를 취출하였으면, 마이크로제어기 (56) 는 신호 (938) 를 전송함으로써 그 물리 어드레스에서의 메모리 (64) 에 액세스하여 데이터를 기록할 수도 있다. 메모리 인터페이스 (60) 는 신호 (938) 를 해석하고 신호 (940) 를 메모리 (64) 로 전송할 수도 있다. 메모리 인터페이스 (60) 는 메모리 (64) 로부터 반환 신호 (942) 를 수신함으로써 메모리 (64) 에 기록하는 것이 완료되는 때를 식별하고, 신호 (944) 를 마이크로제어기 (56) 로 전송하여, 그 기록이 완료되었다는 것을 표시할 수도 있다.

FTL 호스트 캐싱 초기화 동안 DRAM (38) 에의 직접 메모리 액세스를 승인 받았으면, 마이크로제어기 (56) 는 그것을 DRAM (38) 에 접속하는 버스들 (34, 40) 을 버스 마스터링함으로써 FTL 테이블들 (70) 의 복사본을 업데이트할 수도 있다. 마이크로제어기는 신호 (946) 를 전송하여 DRAM (38) 에 직접 기록할 수도 있다. DMA 버스 제어기 (54) 는 신호 (946) 를 DMA 버스 제어기 (26) 로 신호 (948) 로서 포워딩할 수도 있으며, 그 신호 (908) 는 DRAM 제어기 (32) 로 신호 (950) 로서 포워딩될 수도 있다. DRAM 제어기 (32) 는 신호 (950) 를 해석하고 신호 (952) 를 DRAM (38) 으로 전송할 수도 있다. DRAM 제어기 (32) 는 DRAM (38) 으로부터 반환 신호 (954) 를 수신함으로써 FTL 테이블들 (70) 의 복사본의 업데이트가 완료된 때를 식별할 수도 있다. 신호 (954) 는 DMA 버스 제어기 (26) 로 신호 (956) 로서 전송되고, DMA 버스 제어기 (54) 로 신호 (958) 로서 포워딩되고, 마지막으로 마이크로제어기 (56) 에 의해 신호 (960) 로서 수신될 수도 있다.

FTL 테이블들 (70) 의 복사본의 업데이트를 완료한 후, 마이크로제어기 (56) 는 신호 (962) 를 전송함으로써 동작 (600) 이 완료되었다는 것을 CPU (24) 에게 통지할 수도 있다. DMA 버스 제어기들 (54) 은 신호 (962) 를 수신하고 그것을 DMA 버스 제어기 (26) 로 신호 (964) 로서 포워딩할 수도 있으며, 그 신호 (964) 는 CPU (24) 로 신호 (966) 로서 포워딩될 수도 있다.

도 10 은 플래시 메모리 디바이스 (50) 에의 기록 동작 (600) 의 프로세스 흐름의 양태를 예시한다. CPU (24) 는 기록 요청을 마이크로제어기 (56) 로 발하여, 그 요청을 운반하는 신호 (1000) 를 DMA 버스 제어기 (26) 를 통해서 신호 (1002) 로서 전송할 수도 있다. DMA 제어기 (54) 는 신호 (1002) 를 수신하고 그것을 마이크로제어기 (56) 로 신호 (1004) 로서 포워딩할 수도 있다.

기록 요청을 수신하였으면, 마이크로제어기 (56) 는 신호 (1006) 를 전송함으로써, 플래시 메모리 디바이스 (50) 의 SRAM (58) 에 액세스하고, 기록 요청의 대상 데이터를 저장하기에 적합한 공간에 관한 플래시 메모리 (64) 에 관련된 정보를 취출/판독할 수도 있다. 이 정보는 플래시 메모리 (64) 에 대한 자유 저장 공간 및/또는 웨어 레벨링 정보를 포함할 수도 있다. 마이크로제어기 (56) 는 원하는 정보를 나타내는, SRAM (58) 으로부터의 반환 신호 (1008) 를 수신할 수도 있다. 이 정보에 의해, 마이크로제어기 (56) 는 데이터를 기록하기 위한 플래시 메모리 (64) 의 물리 어드레스를 결정할 수도 있다.

기록 데이터를 기록할 장소를 결정하였으면, 마이크로제어기 (56) 는 신호 (1010) 를 전송함으로써 DRAM (38) 으로부터 기록 데이터를 취출할 수도 있다. DMA 버스 제어기 (54) 는 신호 (1010) 를 수신하여 그것을 신호 (1012) 로서 DMA 버스 제어기 (26) 로 포워딩할 수도 있다. DRAM 제어기 (32) 는 DMA 버스 제어기 (26) 로부터 신호 (1014) 를 수신하고 그것을 신호 (1016) 로서 해석하여 그 신호 (1016) 를 DRAM (38) 으로 전송할 수도 있다. DRAM 제어기 (32) 는 DRAM (38) 으로부터 판독된 기록 데이터를 신호 (1018) 로서 수신하고 그 기록 데이터를 마이크로제어기 (56) 로 신호 (1012) 로서 포워딩할 수도 있다. DMA 버스 제어기 (26) 는 신호 (1020) 를 수신하고 그것을 신호 (1022) 로서 DMA 버스 제어기 (54) 로 포워딩할 수도 있으며, 그 신호 (934) 는 마이크로제어기 (56) 로 신호 (1024) 로서 포워딩될 수도 있다.

물리 어드레스를 결정하여 기록 데이터를 취출하였으면, 마이크로제어기 (56) 는 신호 (1026) 를 전송함으로써 메모리 (64) 에 액세스하여, 데이터를 물리 어드레스에서의 메모리 (64) 에 기록할 수도 있다. 메모리 인터페이스 (60) 는 신호 (1026) 를 해석하고 신호 (1028) 를 메모리 (64) 로 전송할 수도 있다. 메모리 인터페이스 (60) 는 메모리 (64) 로부터 반환 신호 (1030) 를 수신함으로써 메모리 (64) 에 기록하는 것이 완료되는 때를 식별하고, 신호 (1032) 를 마이크로제어기 (56) 로 전송하여, 그 기록이 완료되었다는 것을 표시할 수도 있다.

FTL 호스트 캐싱 초기화 동안 DRAM (38) 에의 직접 메모리 액세스를 승인 받았으면, 마이크로제어기 (56) 는 그것을 DRAM (38) 에 접속하는 버스들 (34, 40) 을 버스 마스터링함으로써 FTL 테이블들 (70) 의 복사본을 업데이트할 수도 있다. 마이크로제어기는 신호 (1034) 를 전송하여 DRAM (38) 에 직접 기록할 수도 있다. DMA 버스 제어기 (54) 는 신호 (1034) 를 DMA 버스 제어기 (26) 로 신호 (1036) 로서 포워딩할 수도 있으며, 그 신호 (908) 는 DRAM 제어기 (32) 로 신호 (1038) 로서 포워딩될 수도 있다. DRAM 제어기 (32) 는 신호 (1038) 를 해석하고 신호 (1040) 를 DRAM (38) 으로 전송할 수도 있다. DRAM 제어기 (32) 는 DRAM (38) 으로부터 반환 신호 (1042) 를 수신함으로써 FTL 테이블들 (70) 의 복사본의 업데이트가 완료된 때를 식별할 수도 있다. 신호 (1042) 는 DMA 버스 제어기 (26) 로 신호 (1044) 로서 전송되고, DMA 버스 제어기 (54) 로 신호 (1046) 로서 포워딩되고, 마지막으로 마이크로제어기 (56) 에 의해 신호 (1048) 로서 수신될 수도 있다.

FTL 테이블들 (70) 의 복사본의 업데이트를 완료한 후, 마이크로제어기 (56) 는 신호 (1050) 를 전송함으로써 동작 (600) 이 완료되었다는 것을 CPU (24) 에게 통지할 수도 있다. DMA 버스 제어기들 (54) 은 신호 (1050) 를 수신하고 그것을 DMA 버스 제어기 (26) 로 신호 (1052) 로서 포워딩할 수도 있으며, 그 신호 (964) 는 CPU (24) 로 신호 (1054) 로서 포워딩될 수도 있다.

일부 양태들에서, 구성요소들 중 임의의 구성요소 사이의 프로세스 흐름의 임의의 부분은 본원에서 설명되는 프로세스들 중 하나 이상에 대해 도 7 내지 도 10 에 나타낸 것보다 더 많이 반복될 수도 있다. 예를 들어, FTL 테이블들 (68) 을 플래시 메모리 디바이스 (50) 로부터 호스트 디바이스에 복사하는 것을 나타내는 신호들 (734-758) 은 그 복사 (copying) 의 트랜잭션들로서 수차례 발생할 수도 있다. 트랜잭션들은 그 복사의 실행들일 수도 있으며, 여기서, 각각의 트랜잭션은 FTL 테이블들 (68) 의 부분을 복사하는 장소를 복사하는 것의 실행들일 수도 있으며, 트랜잭션들은 복사가 완료될 때까지 계속한다. 32MB 의 FTL 테이블 데이터의 예를 취하면, 트랜잭션 당 단지 32, 64, 또는 128 바이트들의 FTL 테이블 데이터가 호스트 디바이스 (20) 로 복사될 수도 있다. 동일한 것이 도 7 내지 도 10 에 도시된 임의의 판독 또는 기록 동작에 대해 유효하다.

상기 방법 설명들 및 프로세스 흐름도들은 단지 예시적인 예들로서 제공되며 여러 양태들의 동작들이 제시된 순서로 수행되어야 한다는 것을 요구하거나 또는 암시하려고 의도된 것이 아니다. 당업자가 주지하고 있는 바와 같이 전술한 양태들에서 동작들의 순서는 임의의 순서로 수행될 수도 있다. "그후", "따라서", "다음" 등과 같은 단어들은 동작들의 순서를 제한하려고 의도되지 않으며; 이들 단어들은 방법들의 설명을 통해서 독자를 안내하기 위해서 단지 사용된다. 또, 단수형으로, 예를 들어, 한정사 "한", "하나" 또는 "그" 를 이용한, 청구항 엘리먼트들에 대한 임의의 언급은, 그 엘리먼트를 단수에 한정하는 것으로 해석되어서는 안된다.

본원에서 개시한 양태들과 관련하여 설명한 여러가지 예시적인 로직 블록들, 모듈들, 회로들, 및 알고리즘 동작들은 전자적 하드웨어, 컴퓨터 소프트웨어, 또는 양쪽의 조합들로서 구현될 수도 있다. 이러한 하드웨어와 소프트웨어의 상호 교환가능성을 명확히 예시하기 위하여, 여러가지 예시적인 구성요소들, 블록들, 모듈들, 회로들, 및 동작들 일반적으로 그들의 기능의 관점에서 위에서 설명되었다. 이런 기능이 하드웨어 또는 소프트웨어로 구현되는지 여부는 특정의 애플리케이션 및 전체 시스템에 부과되는 설계 제한 사항들에 의존한다. 숙련자들은 각각의 특정의 애플리케이션 마다 설명한 기능을 여러가지 방법으로 구현할 수도 있으며, 그러나 이런 구현 결정들이 본 발명의 범위로부터 일탈을 초래하는 것으로 해석되어서는 안된다.

본원에서 개시한 양태들과 관련하여 설명한 여러 예시적인 로직들, 로직 블록들, 모듈들, 및 회로들을 구현하기 위해 사용되는 하드웨어는 범용 프로세서, 디지털 신호 프로세서 (DSP), 주문형 집적회로 (ASIC), 필드 프로그래밍가능 게이트 어레이 (FPGA) 또는 다른 프로그래밍가능 로직 디바이스, 이산 게이트 또는 트랜지스터 로직, 이산 하드웨어 구성요소들, 또는 본원에서 설명한 기능들을 수행하도록 설계된 이들의 임의의 조합으로 구현되거나 또는 수행될 수도 있다. 범용 프로세서는 마이크로프로세서일 수도 있으며, 그러나, 대안적으로는, 프로세서는 임의의 종래의 프로세서, 제어기, 마이크로제어기, 또는 상태 머신일 수도 있다. 프로세서는 또한 컴퓨팅 디바이스들의 조합, 예컨대, DSP 와 마이크로프로세서의 조합, 복수의 마이크로프로세서들, DSP 코어와 결합된 하나 이상의 마이크로프로세서들, 또는 임의의 다른 이러한 구성으로서 구현될 수도 있다. 대안적으로, 일부 동작들 또는 방법들은 주어진 기능에 특유한 회로에 의해 수행될 수도 있다.

하나 이상의 예시적인 양태들에서, 설명된 기능들은 하드웨어, 소프트웨어, 펌웨어, 또는 이들의 임의의 조합으로 구현될 수도 있다. 소프트웨어로 구현되는 경우, 이 기능들은 비일시적 컴퓨터-판독가능 매체 또는 비일시적 프로세서-판독가능 매체에 하나 이상의 명령들 또는 코드로서 저장될 수도 있다. 본원에서 개시한 방법 또는 알고리즘의 동작들은 비일시적 컴퓨터-판독가능 또는 프로세서-판독가능 저장 매체 상에 상주할 수도 있는 프로세서-실행가능한 소프트웨어 모듈에 내장될 수도 있다. 비일시적 컴퓨터-판독가능 또는 프로세서-판독가능 저장 매체들은 컴퓨터 또는 프로세서에 의해 액세스될 수도 있는 임의의 저장 매체들일 수도 있다. 비제한적인 예로서, 이런 비일시적 컴퓨터-판독가능 또는 프로세서-판독가능 매체들은 RAM, ROM, EEPROM, 플래시 메모리, CD-ROM 또는 다른 광디스크 스토리지, 자기디스크 스토리지 또는 다른 자기 저장 디바이스들, 또는 원하는 프로그램 코드를 명령들 또는 데이터 구조들의 형태로 저장하는데 사용될 수도 있고 컴퓨터에 의해 액세스될 수도 있는 임의의 다른 매체를 포함할 수 있다. 디스크 (disk) 및 디스크 (disc) 는, 본원에서 사용할 때, 컴팩트 디스크 (CD), 레이저 디스크, 광 디스크, 디지털 다기능 디스크 (DVD), 플로피 디스크 및 Blu-ray 디스크를 포함하며, 디스크들 (disks) 은 데이터를 자기적으로 보통 재생하지만, 디스크들 (discs) 은 레이저로 데이터를 광학적으로 재생한다. 앞에서 언급한 것들의 조합들이 또한 비일시적 컴퓨터-판독가능 및 프로세서-판독가능 매체들의 범위 내에 포함된다. 게다가, 방법 또는 알고리즘의 동작들은 컴퓨터 프로그램 제품에 포함될 수도 있는 비일시적 프로세서-판독가능 매체 및/또는 컴퓨터-판독가능 매체 상에, 코드들 및/또는 명령들 중 하나 또는 임의의 조합 또는 세트로 상주할 수도 있다.

개시된 양태들의 선행하는 설명은 임의의 당업자가 본 발명을 실시하고 이용할 수 있도록 제공된다. 이들 양태들에 대한 여러 변경들은 당업자들에게 쉽게 알 수 있을 것이며, 본원에서 정의하는 일반 원리들은 본 발명의 정신 또는 범위로부터 일탈함이 없이, 다른 양태들에 적용될 수도 있다. 따라서, 본 발명은 본원에서 나타낸 양태들에 한정시키려는 것이 아니라, 다음 청구범위에 부합하는 최광의의 범위 및 본원에서 개시된 원리들 및 신규한 특징들을 부여받게 하려는 것이다.

Claims (60)

- 플래시 메모리 디바이스의 플래시 변환 계층 (FTL) 의 성능을 증가시키는 방법으로서,

상기 플래시 메모리 디바이스에 의해 상기 플래시 메모리 디바이스의 FTL 테이블의 복사본을 호스트 디바이스의 휘발성 메모리 상에 저장하는 단계;

상기 플래시 메모리 디바이스에 의해, 상기 호스트 디바이스의 상기 휘발성 메모리에 저장된 상기 FTL 테이블의 상기 복사본에의 액세스를 수신하는 단계; 및

상기 플래시 메모리 디바이스에 의해, 판독 동작 및 기록 동작 중 적어도 하나의 부분으로서, 상기 호스트 디바이스의 상기 휘발성 메모리에 저장된 상기 플래시 메모리 디바이스의 상기 FTL 테이블의 상기 복사본에 액세스하는 단계를 포함하는, 플래시 메모리 디바이스의 플래시 변환 계층 (FTL) 의 성능을 증가시키는 방법. - 제 1 항에 있어서,

상기 플래시 메모리 디바이스에서 상기 호스트 디바이스로부터 상기 FTL 테이블의 사이즈에 대한 쿼리를 수신하는 단계;

상기 FTL 테이블의 상기 사이즈를 상기 플래시 메모리 디바이스로부터 상기 호스트 디바이스로 반환 (return) 하는 단계;

상기 호스트 디바이스에서 상기 플래시 메모리 디바이스로부터 상기 FTL 테이블의 상기 사이즈를 수신하는 단계; 및

상기 호스트 디바이스에 의해, 상기 호스트 디바이스의 상기 휘발성 메모리가 상기 FTL 테이블의 모두를 저장할 수 있는지 여부를 결정하는 단계를 더 포함하는, 플래시 메모리 디바이스의 플래시 변환 계층 (FTL) 의 성능을 증가시키는 방법. - 제 2 항에 있어서,

상기 호스트 디바이스에 의해, 상기 호스트 디바이스의 상기 휘발성 메모리를 재분할하는 단계로서, 재분할 부분 (subdivision) 의 사이즈는 상기 FTL 테이블의 사이즈에 기초하는, 상기 재분할하는 단계;

상기 플래시 메모리 디바이스에 의해, 상기 FTL 테이블의 상기 복사본이 저장된 상기 호스트 디바이스의 상기 휘발성 메모리의 상기 재분할 부분에 대한 직접 메모리 액세스 판독 특권들을 수신하는 단계; 및

상기 플래시 메모리 디바이스에 의해, 상기 FTL 테이블의 상기 복사본이 저장된 상기 호스트 디바이스의 상기 휘발성 메모리의 상기 재분할 부분에 대한 직접 메모리 액세스 기록 특권들을 수신하는 단계를 더 포함하며,

상기 FTL 테이블의 복사본을 저장하는 단계는, 상기 플래시 메모리 디바이스에 의해, 상기 FTL 테이블의 상기 복사본을 상기 호스트 디바이스의 상기 휘발성 메모리의 상기 재분할 부분에 저장하는 단계를 포함하는, 플래시 메모리 디바이스의 플래시 변환 계층 (FTL) 의 성능을 증가시키는 방법. - 제 1 항에 있어서,

상기 FTL 테이블의 상기 복사본에 액세스하는 단계는, 상기 플래시 메모리 디바이스에 의해, 상기 플래시 메모리 디바이스와 상기 호스트 디바이스의 상기 휘발성 메모리를 통신가능하게 접속하는 통신 버스를 버스 마스터링하는 단계를 포함하는, 플래시 메모리 디바이스의 플래시 변환 계층 (FTL) 의 성능을 증가시키는 방법. - 제 1 항에 있어서,

상기 FTL 테이블의 상기 복사본에 액세스하는 단계는,

상기 플래시 메모리 디바이스에서 상기 호스트 디바이스로부터 논리 어드레스에 대한 판독 동작 요청을 수신하는 단계;

상기 플래시 메모리 디바이스에 의해 판독 동작을 개시하는 단계;

상기 플래시 메모리 디바이스에 의해 상기 FTL 테이블의 상기 복사본 중 적어도 일부분을 판독하는 단계;

상기 플래시 메모리 디바이스에 의해 상기 논리 어드레스에 대응하는 물리 어드레스를 결정하는 단계;

상기 플래시 메모리 디바이스에 의해, 상기 플래시 메모리 디바이스의 메모리의 상기 물리 어드레스에 로케이트된 데이터를 취출하는 단계; 및

상기 플래시 메모리 디바이스에 의해 상기 데이터를 상기 호스트 디바이스로 반환하는 단계를 포함하는, 플래시 메모리 디바이스의 플래시 변환 계층 (FTL) 의 성능을 증가시키는 방법. - 제 1 항에 있어서,

상기 FTL 테이블의 상기 복사본에 액세스하는 단계는,

상기 플래시 메모리 디바이스에 의해 상기 호스트 디바이스로부터 논리 어드레스에 대한 기록 동작 요청을 수신하는 단계;

상기 플래시 메모리 디바이스에 의해 기록 동작을 개시하는 단계;

상기 플래시 메모리 디바이스에 의해 상기 플래시 메모리 디바이스의 메모리의 물리 어드레스에 데이터를 기록하는 단계;

상기 데이터가 기록되었을 때 상기 플래시 메모리 디바이스의 상기 메모리에 대해 이루어진 변화들과 일치하도록 상기 FTL 테이블의 상기 복사본을 업데이트하기 위해, 상기 플래시 메모리 디바이스에 의해, 상기 FTL 테이블의 상기 복사본에 기록하는 단계; 및

상기 플래시 메모리 디바이스에 의해 상기 기록 동작의 완료의 통지를 상기 호스트 디바이스로 전송하는 단계를 포함하는, 플래시 메모리 디바이스의 플래시 변환 계층 (FTL) 의 성능을 증가시키는 방법. - 제 6 항에 있어서,

상기 플래시 메모리 디바이스에 의해 상기 FTL 테이블의 상기 복사본 중 적어도 일부분을 판독하는 단계; 및

상기 플래시 메모리 디바이스에 의해 상기 논리 어드레스에 대응하는 상기 물리 어드레스를 결정하는 단계를 더 포함하는, 플래시 메모리 디바이스의 플래시 변환 계층 (FTL) 의 성능을 증가시키는 방법. - 제 6 항에 있어서,

상기 플래시 메모리 디바이스에 의해 상기 플래시 메모리 디바이스의 SRAM 을 판독하는 단계; 및

상기 플래시 메모리 디바이스에 의해, 상기 플래시 메모리 디바이스의 상기 메모리에서의 자유 저장 공간의 로케이션을 나타내는 상기 물리 어드레스를 결정하는 단계를 더 포함하는, 플래시 메모리 디바이스의 플래시 변환 계층 (FTL) 의 성능을 증가시키는 방법. - 제 1 항에 있어서,

상기 플래시 메모리 디바이스에 의해, 상기 FTL 테이블의 상기 복사본을 상기 호스트 디바이스의 상기 휘발성 메모리에 저장하는 것의 완료를 나타내는 통지를 상기 호스트 디바이스로 전송하는 단계를 더 포함하는, 플래시 메모리 디바이스의 플래시 변환 계층 (FTL) 의 성능을 증가시키는 방법. - 제 1 항에 있어서,

상기 플래시 메모리 디바이스에 의해, 기록 동작의 완료, 가용 리소스들, 및 스케쥴로 이루어진 그룹으로부터 선택된 파라미터에 기초하여, 상기 플래시 메모리 디바이스의 상기 FTL 테이블을 상기 FTL 의 상기 복사본으로 업데이트하는 단계를 더 포함하는, 플래시 메모리 디바이스의 플래시 변환 계층 (FTL) 의 성능을 증가시키는 방법. - 제 1 항에 있어서,

상기 호스트 디바이스에 의해, 상기 플래시 메모리 디바이스가 상기 호스트 디바이스의 상기 휘발성 메모리에서의 상기 FTL 테이블의 복사본의 호스트 캐싱을 지원하는지 여부를 결정하는 단계를 더 포함하는, 플래시 메모리 디바이스의 플래시 변환 계층 (FTL) 의 성능을 증가시키는 방법. - 제 1 항에 있어서,

상기 호스트 디바이스에서, 상기 플래시 메모리 디바이스로부터 상기 FTL 테이블의 상기 복사본을 저장하는 것의 완료의 통지를 수신하는 단계를 더 포함하는, 플래시 메모리 디바이스의 플래시 변환 계층 (FTL) 의 성능을 증가시키는 방법. - 시스템으로 하여금, 상기 시스템의 플래시 메모리 디바이스의 플래시 변환 계층 (FTL) 의 성능을 증가시키도록 구성된 프로세서-실행가능한 소프트웨어 명령들을 저장하고 있는 비일시적 프로세서-판독가능 매체로서,

동작들은,

상기 플래시 메모리 디바이스에 의해 상기 플래시 메모리 디바이스의 FTL 테이블의 복사본을 호스트 디바이스의 휘발성 메모리 상에 저장하는 것;

상기 플래시 메모리 디바이스에 의해, 상기 호스트 디바이스의 상기 휘발성 메모리에 저장된 상기 FTL 테이블의 상기 복사본에의 액세스를 수신하는 것; 및

상기 플래시 메모리 디바이스에 의해, 판독 동작 및 기록 동작 중 적어도 하나의 부분으로서, 상기 호스트 디바이스의 상기 휘발성 메모리에 저장된 상기 플래시 메모리 디바이스의 상기 FTL 테이블의 상기 복사본에 액세스하는 것을 포함하는, 비일시적 프로세서-판독가능 매체. - 제 13 항에 있어서,

상기 저장된 프로세서-실행가능한 소프트웨어 명령들은, 상기 시스템으로 하여금,

상기 플래시 메모리 디바이스에서 상기 호스트 디바이스로부터 상기 FTL 테이블의 사이즈에 대한 쿼리를 수신하는 것;

상기 FTL 테이블의 상기 사이즈를 상기 플래시 메모리 디바이스로부터 상기 호스트 디바이스로 반환하는 것;

상기 호스트 디바이스에서 상기 플래시 메모리 디바이스로부터 상기 FTL 테이블의 상기 사이즈를 수신하는 것; 및

상기 호스트 디바이스에 의해, 상기 호스트 디바이스의 상기 휘발성 메모리가 상기 FTL 테이블의 모두를 저장할 수 있는지 여부를 결정하는 것을 더 포함하는 동작들을 수행하게 하도록 구성되는, 비일시적 프로세서-판독가능 매체. - 제 14 항에 있어서,

상기 저장된 프로세서-실행가능한 소프트웨어 명령들은, 상기 시스템으로 하여금,

상기 호스트 디바이스에 의해, 상기 호스트 디바이스의 상기 휘발성 메모리를 재분할하는 것으로서, 재분할 부분의 사이즈는 상기 FTL 테이블의 사이즈에 기초하는, 상기 재분할하는 것;

상기 플래시 메모리 디바이스에 의해, 상기 FTL 테이블의 상기 복사본이 저장된 상기 호스트 디바이스의 상기 휘발성 메모리의 상기 재분할 부분에 대한 직접 메모리 액세스 판독 특권들을 수신하는 것; 및

상기 플래시 메모리 디바이스에 의해, 상기 FTL 테이블의 상기 복사본이 저장된 상기 호스트 디바이스의 상기 휘발성 메모리의 상기 재분할 부분에 대한 직접 메모리 액세스 기록 특권들을 수신하는 것을 더 포함하는 동작들을 수행하게 하도록 구성되며,

상기 FTL 테이블의 복사본을 저장하는 것은 상기 플래시 메모리 디바이스에 의해, 상기 FTL 테이블의 상기 복사본을 상기 호스트 디바이스의 상기 휘발성 메모리의 상기 재분할 부분에 저장하는 것을 포함하는, 비일시적 프로세서-판독가능 매체. - 제 13 항에 있어서,

상기 저장된 프로세서-실행가능한 소프트웨어 명령들은, 상기 시스템으로 하여금,

상기 FTL 테이블의 상기 복사본에 액세스하는 것이, 상기 플래시 메모리 디바이스에 의해, 상기 플래시 메모리 디바이스와 상기 호스트 디바이스의 상기 휘발성 메모리를 통신가능하게 접속하는 통신 버스를 버스 마스터링하는 것을 포함하도록,

동작들을 수행하게 하도록 구성되는, 비일시적 프로세서-판독가능 매체. - 제 13 항에 있어서,

상기 저장된 프로세서-실행가능한 소프트웨어 명령들은, 상기 시스템으로 하여금,

상기 FTL 테이블의 상기 복사본에 액세스하는 것이,

상기 플래시 메모리 디바이스에서 상기 호스트 디바이스로부터 논리 어드레스에 대한 판독 동작 요청을 수신하는 것;

상기 플래시 메모리 디바이스에 의해 판독 동작을 개시하는 것;

상기 플래시 메모리 디바이스에 의해 상기 FTL 테이블의 상기 복사본 중 적어도 일부분을 판독하는 것;

상기 플래시 메모리 디바이스에 의해 상기 논리 어드레스에 대응하는 물리 어드레스를 결정하는 것;

상기 플래시 메모리 디바이스에 의해, 상기 플래시 메모리 디바이스의 메모리의 상기 물리 어드레스에 로케이트된 데이터를 취출하는 것; 및

상기 플래시 메모리 디바이스에 의해 상기 데이터를 상기 호스트 디바이스로 반환하는 것을 포함하도록,

동작들을 수행하게 하도록 구성되는, 비일시적 프로세서-판독가능 매체. - 제 13 항에 있어서,

상기 저장된 프로세서-실행가능한 소프트웨어 명령들은, 상기 시스템으로 하여금,

상기 FTL 테이블의 상기 복사본에 액세스하는 것이,

상기 플래시 메모리 디바이스에 의해 상기 호스트 디바이스로부터 논리 어드레스에 대한 기록 동작 요청을 수신하는 것;

상기 플래시 메모리 디바이스에 의해 기록 동작을 개시하는 것;

상기 플래시 메모리 디바이스에 의해 상기 플래시 메모리 디바이스의 메모리의 물리 어드레스에 데이터를 기록하는 것;

상기 데이터가 기록되었을 때 상기 플래시 메모리 디바이스의 상기 메모리에 대해 이루어진 변화들과 일치하도록 상기 FTL 테이블의 상기 복사본을 업데이트하기 위해, 상기 플래시 메모리 디바이스에 의해, 상기 FTL 테이블의 상기 복사본에 기록하는 것; 및

상기 플래시 메모리 디바이스에 의해 상기 기록 동작의 완료의 통지를 상기 호스트 디바이스로 전송하는 것을 포함하도록,

동작들을 수행하게 하도록 구성되는, 비일시적 프로세서-판독가능 매체. - 제 18 항에 있어서,

상기 저장된 프로세서-실행가능한 소프트웨어 명령들은, 상기 시스템으로 하여금,

상기 플래시 메모리 디바이스에 의해 상기 FTL 테이블의 상기 복사본 중 적어도 일부분을 판독하는 것; 및

상기 플래시 메모리 디바이스에 의해 상기 논리 어드레스에 대응하는 상기 물리 어드레스를 결정하는 것을 더 포함하는 동작들을 수행하게 하도록 구성되는, 비일시적 프로세서-판독가능 매체. - 제 18 항에 있어서,

상기 저장된 프로세서-실행가능한 소프트웨어 명령들은, 상기 시스템으로 하여금,

상기 플래시 메모리 디바이스에 의해 상기 플래시 메모리 디바이스의 SRAM 을 판독하는 것; 및

상기 플래시 메모리 디바이스에 의해, 상기 플래시 메모리 디바이스의 상기 메모리에서의 자유 저장 공간의 로케이션을 나타내는 상기 물리 어드레스를 결정하는 것을 더 포함하는 동작들을 수행하게 하도록 구성되는, 비일시적 프로세서-판독가능 매체. - 제 13 항에 있어서,

상기 저장된 프로세서-실행가능한 소프트웨어 명령들은, 상기 시스템으로 하여금,

상기 플래시 메모리 디바이스에 의해, 상기 FTL 테이블의 상기 복사본을 상기 호스트 디바이스의 상기 휘발성 메모리에 저장하는 것의 완료를 나타내는 통지를 상기 호스트 디바이스로 전송하는 것을 더 포함하는 동작들을 수행하게 하도록 구성되는, 비일시적 프로세서-판독가능 매체. - 제 13 항에 있어서,

상기 저장된 프로세서-실행가능한 소프트웨어 명령들은, 상기 시스템으로 하여금,

상기 플래시 메모리 디바이스에 의해, 상기 기록 동작의 완료, 가용 리소스들, 및 스케쥴로 이루어진 그룹으로부터 선택된 파라미터에 기초하여, 상기 플래시 메모리 디바이스의 상기 FTL 테이블을 상기 FTL 의 상기 복사본으로 업데이트하는 것을 더 포함하는 동작들을 수행하게 하도록 구성되는, 비일시적 프로세서-판독가능 매체. - 제 13 항에 있어서,

상기 저장된 프로세서-실행가능한 소프트웨어 명령들은, 상기 시스템으로 하여금,

상기 호스트 디바이스에 의해, 상기 플래시 메모리 디바이스가 상기 호스트 디바이스의 상기 휘발성 메모리에서의 상기 FTL 테이블의 복사본의 호스트 캐싱을 지원하는지 여부를 결정하는 것을 더 포함하는 동작들을 수행하게 하도록 구성되는, 비일시적 프로세서-판독가능 매체. - 제 13 항에 있어서,

상기 저장된 프로세서-실행가능한 소프트웨어 명령들은, 상기 시스템으로 하여금,

상기 호스트 디바이스에서, 상기 플래시 메모리 디바이스로부터 상기 FTL 테이블의 상기 복사본을 저장하는 것의 상기 완료의 통지를 수신하는 것을 더 포함하는 동작들을 수행하게 하도록 구성되는, 비일시적 프로세서-판독가능 매체. - 시스템으로서,

호스트 디바이스; 및

상기 호스트 디바이스에 커플링된 플래시 메모리 디바이스를 포함하며,

상기 호스트 디바이스는,

휘발성 메모리; 및

상기 휘발성 메모리에 커플링된 제 1 프로세서를 포함하며,

상기 플래시 메모리 디바이스는,

논리 어드레스와 물리 어드레스 사이에서 변환할 때에 사용을 위한 플래시 변환 계층 (FTL) 테이블을 저장하도록 구성된 플래시 메모리; 및

상기 플래시 메모리에 커플링된 제 2 프로세서를 포함하며,

상기 제 2 프로세서는,

상기 플래시 메모리 디바이스의 상기 FTL 테이블의 복사본을 상기 호스트 디바이스의 상기 휘발성 메모리에 저장하는 것;

상기 호스트 디바이스의 상기 휘발성 메모리에 저장된 상기 FTL 테이블의 상기 복사본에의 액세스를 수신하는 것; 및

판독 동작 및 기록 동작 중 적어도 하나의 부분으로서 상기 호스트 디바이스의 상기 휘발성 메모리에 저장된 상기 플래시 메모리 디바이스의 상기 FTL 테이블의 상기 복사본에 액세스하는 것을 포함하는 동작들을 수행하는 프로세서-실행가능한 명령들로 구성되는, 시스템. - 제 25 항에 있어서,

상기 제 2 프로세서는,

상기 플래시 메모리 디바이스에서 상기 호스트 디바이스로부터 상기 FTL 테이블의 사이즈에 대한 쿼리를 수신하는 것; 및

상기 FTL 테이블의 상기 사이즈를 상기 플래시 메모리 디바이스로부터 상기 호스트 디바이스로 반환하는 것을 더 포함하는 동작들을 수행하는 프로세서-실행가능한 명령들로 구성되며,

상기 제 1 프로세서는,

상기 호스트 디바이스에서 상기 플래시 메모리 디바이스로부터 상기 FTL 테이블의 상기 사이즈를 수신하는 것; 및

상기 호스트 디바이스에 의해, 상기 호스트 디바이스의 상기 휘발성 메모리가 상기 FTL 테이블의 모두를 저장할 수 있는지 여부를 결정하는 것을 더 포함하는 동작들을 수행하는 프로세서-실행가능한 명령들로 구성되는, 시스템. - 제 26 항에 있어서,

상기 제 1 프로세서는,

상기 호스트 디바이스에 의해, 상기 호스트 디바이스의 상기 휘발성 메모리를 재분할하는 것을 더 포함하는 동작들을 수행하는 프로세서-실행가능한 명령들로 구성되며, 재분할 부분의 사이즈는 상기 FTL 테이블의 사이즈에 기초하며,

상기 FTL 테이블의 상기 복사본을 저장하는 것은 상기 플래시 메모리 디바이스에 의해, 상기 FTL 테이블의 상기 복사본을 상기 호스트 디바이스의 상기 휘발성 메모리의 상기 재분할 부분에 저장하는 것을 포함하며,

상기 제 2 프로세서는,

상기 플래시 메모리 디바이스에 의해, 상기 FTL 테이블의 상기 복사본이 저장된 상기 호스트 디바이스의 상기 휘발성 메모리의 상기 재분할 부분에 대한 직접 메모리 액세스 판독 특권들을 수신하는 것; 및

상기 플래시 메모리 디바이스에 의해, 상기 FTL 테이블의 상기 복사본이 저장된 상기 호스트 디바이스의 상기 휘발성 메모리의 상기 재분할 부분에 대한 직접 메모리 액세스 기록 특권들을 수신하는 것을 더 포함하는 동작들을 수행하기 위한 프로세서-실행가능한 명령들로 구성되는, 시스템. - 제 25 항에 있어서,

상기 플래시 메모리 디바이스와 상기 호스트 디바이스의 상기 휘발성 메모리를 통신가능하게 접속하는 통신 버스를 더 포함하며,

상기 제 2 프로세서는, 상기 FTL 테이블의 상기 복사본에 액세스하는 것이 상기 통신 버스를 버스 마스터링하는 것을 포함하도록 동작들을 수행하는 프로세서-실행가능한 명령들로 구성되는, 시스템. - 제 25 항에 있어서,

상기 제 2 프로세서는,

상기 FTL 테이블의 상기 복사본에 액세스하는 것이,

상기 플래시 메모리 디바이스에서 상기 호스트 디바이스로부터 상기 논리 어드레스에 대한 판독 동작 요청을 수신하는 것;

상기 플래시 메모리 디바이스에 의해 판독 동작을 개시하는 것;

상기 플래시 메모리 디바이스에 의해 상기 FTL 테이블의 상기 복사본 중 적어도 일부분을 판독하는 것;

상기 플래시 메모리 디바이스에 의해 상기 논리 어드레스에 대응하는 상기 물리 어드레스를 결정하는 것;

상기 플래시 메모리 디바이스에 의해, 상기 플래시 메모리 디바이스의 상기 플래시 메모리의 상기 물리 어드레스에 로케이트된 데이터를 취출하는 것; 및

상기 플래시 메모리 디바이스에 의해 상기 데이터를 상기 호스트 디바이스로 반환하는 것을 포함하도록, 프로세서-실행가능한 명령들로 구성되는, 시스템. - 제 25 항에 있어서,

상기 제 2 프로세서는,

상기 FTL 테이블의 상기 복사본에 액세스하는 것이,

상기 플래시 메모리 디바이스에 의해 상기 호스트 디바이스로부터 상기 논리 어드레스에 대한 기록 동작 요청을 수신하는 것;

상기 플래시 메모리 디바이스에 의해 기록 동작을 개시하는 것;

상기 플래시 메모리 디바이스에 의해 상기 플래시 메모리 디바이스의 상기 플래시 메모리의 상기 물리 어드레스에 데이터를 기록하는 것;

상기 데이터가 기록되었을 때 상기 플래시 메모리 디바이스의 상기 플래시 메모리에 대해 이루어진 변환들에 일치하도록 상기 FTL 테이블의 상기 복사본을 업데이트하기 위해, 상기 플래시 메모리 디바이스에 의해, 상기 FTL 테이블의 상기 복사본에 기록하는 것; 및

상기 플래시 메모리 디바이스에 의해 상기 기록 동작의 완료의 통지를 상기 호스트 디바이스로 전송하는 것을 포함하도록, 프로세서-실행가능한 명령들로 구성되는, 시스템. - 제 30 항에 있어서,

상기 제 2 프로세서는,

상기 플래시 메모리 디바이스에 의해 상기 FTL 테이블의 상기 복사본 중 적어도 일부분을 판독하는 것; 및

상기 플래시 메모리 디바이스에 의해 상기 논리 어드레스에 대응하는 상기 물리 어드레스를 결정하는 것을 더 포함하는 동작들을 수행하는 프로세서-실행가능한 명령들로 구성되는, 시스템. - 제 30 항에 있어서,

상기 플래시 메모리 디바이스는 상기 제 2 프로세서에 커플링된 SRAM 을 더 포함하며, 그리고

상기 제 2 프로세서는,

상기 플래시 메모리 디바이스에 의해 상기 플래시 메모리 디바이스의 상기 SRAM 을 판독하는 것; 및

상기 플래시 메모리 디바이스에 의해, 상기 플래시 메모리 디바이스의 상기 플래시 메모리에서의 자유 저장 공간의 로케이션을 나타내는 상기 물리 어드레스를 결정하는 것을 더 포함하는 동작들을 수행하는 프로세서-실행가능한 명령들로 구성되는, 시스템. - 제 25 항에 있어서,

상기 제 2 프로세서는,

상기 플래시 메모리 디바이스에 의해, 상기 FTL 테이블의 상기 복사본을 상기 호스트 디바이스의 상기 휘발성 메모리에 저장하는 것의 완료를 나타내는 통지를 상기 호스트 디바이스로 전송하는 것을 더 포함하는 동작들을 수행하는 프로세서-실행가능한 명령들로 구성되는, 시스템. - 제 25 항에 있어서,

상기 제 2 프로세서는,

상기 플래시 메모리 디바이스에 의해, 상기 기록 동작의 완료, 가용 리소스들, 및 스케쥴로 이루어진 그룹으로부터 선택된 파라미터에 기초하여, 상기 플래시 메모리 디바이스의 상기 FTL 테이블을 상기 FTL 의 상기 복사본으로 업데이트하는 것을 더 포함하는 동작들을 수행하는 프로세서-실행가능한 명령들로 구성되는, 시스템. - 제 25 항에 있어서,

상기 제 1 프로세서는,

상기 호스트 디바이스에 의해, 상기 플래시 메모리 디바이스가 상기 호스트 디바이스의 상기 휘발성 메모리에서의 상기 FTL 테이블의 복사본의 호스트 캐싱을 지원하는지 여부를 결정하는 것을 더 포함하는 동작들을 수행하는 프로세서-실행가능한 명령들로 구성되는, 시스템. - 제 25 항에 있어서,

상기 제 1 프로세서는,

상기 호스트 디바이스에서, 상기 플래시 메모리 디바이스로부터 상기 FTL 테이블의 상기 복사본을 저장하는 것의 상기 완료의 통지를 수신하는 것을 더 포함하는 동작들을 수행하는 프로세서-실행가능한 명령들로 구성되는, 시스템. - 플래시 메모리 디바이스;

상기 플래시 메모리 디바이스에 의해 호스트 디바이스의 휘발성 메모리 상에 상기 플래시 메모리 디바이스의 플래시 변환 계층 (FTL) 테이블의 복사본을 저장하는 수단;

상기 플래시 메모리 디바이스에 의해 상기 호스트 디바이스의 상기 휘발성 메모리에 저장된 상기 FTL 테이블의 상기 복사본에의 액세스를 수신하는 수단; 및

상기 플래시 메모리 디바이스에 의해, 판독 동작 및 기록 동작 중 적어도 하나의 부분으로서, 상기 호스트 디바이스의 상기 휘발성 메모리에 저장된 상기 플래시 메모리 디바이스의 상기 FTL 테이블의 상기 복사본에 액세스하는 수단을 포함하는, 시스템. - 제 37 항에 있어서,

상기 플래시 메모리 디바이스에서 상기 호스트 디바이스로부터 상기 FTL 테이블의 사이즈에 대한 쿼리를 수신하는 수단;

상기 FTL 테이블의 상기 사이즈를 상기 플래시 메모리 디바이스로부터 상기 호스트 디바이스로 반환하는 수단;

상기 호스트 디바이스에서 상기 플래시 메모리 디바이스로부터 상기 FTL 테이블의 상기 사이즈를 수신하는 수단; 및

상기 호스트 디바이스에 의해, 상기 호스트 디바이스의 상기 휘발성 메모리가 상기 FTL 테이블의 모두를 저장할 수 있는지 여부를 결정하는 수단을 더 포함하는, 시스템. - 제 38 항에 있어서,

상기 호스트 디바이스에 의해, 상기 호스트 디바이스의 상기 휘발성 메모리를 재분할하는 수단으로서, 재분할 부분의 사이즈는 상기 FTL 테이블의 사이즈에 기초하는, 상기 재분할하는 수단;

상기 플래시 메모리 디바이스에 의해, 상기 FTL 테이블의 상기 복사본이 저장된 상기 호스트 디바이스의 상기 휘발성 메모리의 상기 재분할 부분에 대한 직접 메모리 액세스 판독 특권들을 수신하는 수단; 및

상기 플래시 메모리 디바이스에 의해, 상기 FTL 테이블의 상기 복사본이 저장된 상기 호스트 디바이스의 상기 휘발성 메모리의 상기 재분할 부분에 대한 직접 메모리 액세스 기록 특권들을 수신하는 수단을 더 포함하며,

상기 FTL 테이블의 복사본을 저장하는 수단은 상기 플래시 메모리 디바이스에 의해, 상기 FTL 테이블의 상기 복사본을 상기 호스트 디바이스의 상기 휘발성 메모리의 상기 재분할 부분에 저장하는 수단을 포함하는, 시스템. - 제 37 항에 있어서,

상기 FTL 테이블의 상기 복사본에 액세스하는 수단은,

상기 플래시 메모리 디바이스에 의해, 상기 호스트 디바이스의 상기 휘발성 메모리와 상기 플래시 메모리 디바이스를 통신가능하게 접속하는 통신 버스를 버스 마스터링하는 수단을 더 포함하는, 시스템. - 제 37 항에 있어서,

상기 FTL 테이블의 상기 복사본에 액세스하는 수단은,

상기 플래시 메모리 디바이스에서 상기 호스트 디바이스로부터 논리 어드레스에 대한 판독 동작 요청을 수신하는 수단;

상기 플래시 메모리 디바이스에 의해 판독 동작을 개시하는 수단;

상기 플래시 메모리 디바이스에 의해 상기 FTL 테이블의 상기 복사본 중 적어도 일부분을 판독하는 수단;

상기 플래시 메모리 디바이스에 의해 상기 논리 어드레스에 대응하는 물리 어드레스를 결정하는 수단;

상기 플래시 메모리 디바이스에 의해, 상기 플래시 메모리 디바이스의 메모리의 상기 물리 어드레스에 로케이트된 데이터를 취출하는 수단; 및

상기 플래시 메모리 디바이스에 의해 상기 데이터를 상기 호스트 디바이스로 반환하는 수단을 포함하는, 시스템. - 제 37 항에 있어서,

상기 FTL 테이블의 상기 복사본에 액세스하는 수단은,

상기 플래시 메모리 디바이스에 의해 상기 호스트 디바이스로부터 논리 어드레스에 대한 기록 동작 요청을 수신하는 수단;

상기 플래시 메모리 디바이스에 의해 기록 동작을 개시하는 수단;

상기 플래시 메모리 디바이스에 의해 상기 플래시 메모리 디바이스의 메모리의 물리 어드레스에 데이터를 기록하는 수단;

상기 데이터가 기록되었을 때 상기 플래시 메모리 디바이스의 상기 메모리에 대해 이루어진 변화들과 일치하도록 상기 FTL 테이블의 상기 복사본을 업데이트하기 위해, 상기 플래시 메모리 디바이스에 의해, 상기 FTL 테이블의 상기 복사본에 기록하는 수단; 및

상기 플래시 메모리 디바이스에 의해 상기 기록 동작의 완료의 통지를 상기 호스트 디바이스로 전송하는 수단을 더 포함하는, 시스템. - 제 42 항에 있어서,

상기 플래시 메모리 디바이스에 의해 상기 FTL 테이블의 상기 복사본 중 적어도 일부분을 판독하는 수단; 및

상기 플래시 메모리 디바이스에 의해 상기 논리 어드레스에 대응하는 상기 물리 어드레스를 결정하는 수단을 더 포함하는, 시스템. - 제 42 항에 있어서,

상기 플래시 메모리 디바이스에 의해 상기 플래시 메모리 디바이스의 SRAM 을 판독하는 수단; 및

상기 플래시 메모리 디바이스에 의해, 상기 플래시 메모리 디바이스의 상기 메모리에서의 자유 저장 공간의 로케이션을 나타내는 상기 물리 어드레스를 결정하는 수단을 더 포함하는, 시스템. - 제 37 항에 있어서,

상기 플래시 메모리 디바이스에 의해, 상기 FTL 테이블의 상기 복사본을 상기 호스트 디바이스의 상기 휘발성 메모리에 저장하는 것의 완료를 나타내는 통지를 상기 호스트 디바이스로 전송하는 수단을 더 포함하는, 시스템. - 제 37 항에 있어서,

상기 플래시 메모리 디바이스에 의해, 기록 동작의 완료, 가용 리소스들, 및 스케쥴로 이루어진 그룹으로부터 선택된 파라미터에 기초하여, 상기 플래시 메모리 디바이스의 상기 FTL 테이블을 상기 FTL 의 상기 복사본으로 업데이트하는 수단을 더 포함하는, 시스템. - 제 37 항에 있어서,

상기 호스트 디바이스에 의해, 상기 플래시 메모리 디바이스가 상기 호스트 디바이스의 상기 휘발성 메모리에서의 상기 FTL 테이블의 복사본의 호스트 캐싱을 지원하는지 여부를 결정하는 수단을 더 포함하는, 시스템. - 제 37 항에 있어서,

상기 호스트 디바이스에서, 상기 플래시 메모리 디바이스로부터 상기 FTL 테이블의 상기 복사본을 저장하는 것의 완료의 통지를 수신하는 수단을 더 포함하는, 시스템. - 호스트 디바이스에 커플링하도록 구성된 플래시 메모리 디바이스로서,

상기 플래시 메모리 디바이스는,

논리 어드레스와 물리 어드레스 사이에 변환할 때에 사용을 위한 플래시 변환 계층 (FTL) 테이블을 포함하는 데이터를 저장하도록 구성된 플래시 메모리; 및

상기 플래시 메모리에 커플링된 프로세서를 포함하며,

상기 프로세서는,

상기 플래시 메모리 디바이스의 플래시 변환 계층 (FTL) 테이블의 복사본을 상기 호스트 디바이스의 휘발성 메모리에 저장하는 것;

상기 호스트 디바이스의 상기 휘발성 메모리에 저장된 상기 FTL 테이블의 상기 복사본에의 액세스를 수신하는 것; 및

판독 동작 및 기록 동작 중 적어도 하나의 부분으로서 상기 호스트 디바이스의 상기 휘발성 메모리에 저장된 상기 플래시 메모리 디바이스의 상기 FTL 테이블의 상기 복사본에 액세스하는 것을 포함하는 동작들을 수행하는 프로세서-실행가능한 명령들로 구성되는, 플래시 메모리 디바이스. - 제 49 항에 있어서,

상기 프로세서는,

상기 호스트 디바이스로부터 상기 FTL 테이블의 사이즈에 대한 쿼리를 수신하는 것; 및

상기 FTL 테이블의 상기 사이즈를 상기 호스트 디바이스로 반환하는 것을 더 포함하는 동작들을 수행하는 프로세서-실행가능한 명령들로 구성되며,

상기 프로세서는,

상기 플래시 메모리 디바이스의 상기 FTL 테이블의 상기 복사본을 상기 호스트 디바이스의 휘발성 메모리에 저장하는 것이 상기 호스트 디바이스에 의해 상기 프로세서에 식별되는 상기 호스트 디바이스의 상기 휘발성 메모리의 재분할 부분에 상기 FTL 테이블의 상기 복사본을 저장하는 것을 포함하도록 동작들을 수행하는 프로세서-실행가능한 명령들로 구성되는, 플래시 메모리 디바이스. - 제 50 항에 있어서,

상기 호스트 디바이스의 상기 휘발성 메모리와 상기 플래시 메모리 디바이스를 통신가능하게 접속하는 통신 버스;

상기 프로세서는,

상기 호스트 디바이스로부터, 상기 FTL 테이블의 상기 복사본이 저장된 상기 호스트 디바이스의 상기 휘발성 메모리의 상기 재분할 부분에 대한 직접 메모리 액세스 판독 특권들을 수신하는 것; 및

상기 호스트 디바이스로부터, 상기 FTL 테이블의 상기 복사본이 저장된 상기 호스트 디바이스의 상기 휘발성 메모리의 상기 재분할 부분에 대한 직접 메모리 액세스 기록 특권들을 수신하는 것을 더 포함하는 동작들을 수행하는 프로세서-실행가능한 명령들로 구성되며,

상기 FTL 테이블의 상기 복사본에 액세스하는 것은 상기 통신 버스를 버스 마스터링하는 것을 포함하는, 플래시 메모리 디바이스. - 제 49 항에 있어서,

상기 프로세서는,

상기 FTL 테이블의 상기 복사본에 액세스하는 것이,

상기 호스트 디바이스로부터의, 상기 논리 어드레스에 대한 판독 및 기록 동작 요청 중 하나에 응답하여, 상기 호스트 디바이스의 상기 휘발성 메모리로부터 상기 FTL 테이블의 상기 복사본 중 적어도 일부분을 판독하는 것;

판독 동작 요청에 응답하여, 상기 호스트 디바이스로, 상기 논리 어드레스에 대응하는 상기 플래시 메모리의 상기 물리 어드레스에 로케이트된 데이터를 반환하는 것;

기록 동작 요청에 응답하여 데이터가 상기 논리 어드레스에 대응하는 상기 플래시 메모리 디바이스의 상기 물리 어드레스에 기록될 때 상기 플래시 메모리에 대해 이루어진 변화들에 일치하도록 상기 FTL 테이블의 상기 복사본을 업데이트하기 위해, 상기 호스트 디바이스의 상기 휘발성 메모리에 저장된 상기 FTL 테이블의 상기 복사본에 기록하는 것; 및

상기 기록 동작 요청에 응답하여, 상기 호스트 디바이스로, 상기 기록 동작의 완료의 통지를 전송하는 것을 포함하도록, 프로세서-실행가능한 명령들로 구성되는, 플래시 메모리 디바이스. - 호스트 디바이스에 커플링하도록 구성된 플래시 메모리 디바이스로서,

상기 플래시 메모리 디바이스는,

상기 플래시 메모리 디바이스의 플래시 변환 계층 (FTL) 테이블의 복사본을 상기 호스트 디바이스의 휘발성 메모리에 저장하는 수단;

상기 호스트 디바이스의 상기 휘발성 메모리에 저장된 상기 FTL 테이블의 상기 복사본에의 액세스를 수신하는 수단; 및

판독 동작 및 기록 동작 중 적어도 하나의 부분으로서 상기 호스트 디바이스의 상기 휘발성 메모리에 저장된 상기 플래시 메모리 디바이스의 상기 FTL 테이블의 상기 복사본에 액세스하는 수단을 포함하는, 플래시 메모리 디바이스. - 제 53 항에 있어서,

상기 호스트 디바이스로부터 상기 FTL 테이블의 사이즈에 대한 쿼리를 수신하는 수단; 및

상기 FTL 테이블의 상기 사이즈를 상기 호스트 디바이스로 반환하는 수단을 더 포함하며,

상기 플래시 메모리 디바이스의 상기 FTL 테이블의 상기 복사본을 상기 호스트 디바이스의 휘발성 메모리에 저장하는 수단은, 상기 FTL 테이블의 상기 복사본을 상기 호스트 디바이스의 상기 휘발성 메모리의 재분할 부분에 저장하는 수단을 포함하는, 플래시 메모리 디바이스. - 제 54 항에 있어서,

상기 호스트 디바이스로부터, 상기 FTL 테이블의 상기 복사본이 저장된 상기 호스트 디바이스의 상기 휘발성 메모리의 상기 재분할 부분에 대한 직접 메모리 액세스 판독 특권들을 수신하는 수단; 및

상기 호스트 디바이스로부터, 상기 FTL 테이블의 상기 복사본이 저장된 상기 호스트 디바이스의 상기 휘발성 메모리의 상기 재분할 부분에 대한 직접 메모리 액세스 기록 특권들을 수신하는 수단을 더 포함하며,

상기 FTL 테이블의 상기 복사본에 액세스하는 수단은 상기 호스트 디바이스의 상기 휘발성 메모리와 상기 플래시 메모리 디바이스를 통신가능하게 접속하는 통신 버스를 버스 마스터링하는 수단을 포함하는, 플래시 메모리 디바이스. - 제 53 항에 있어서,

상기 FTL 테이블의 상기 복사본에 액세스하는 수단은,

상기 호스트 디바이스로부터의, 논리 어드레스에 대한 판독 및 기록 동작 요청 중 하나에 응답하여, 상기 호스트 디바이스의 상기 휘발성 메모리로부터, 상기 FTL 테이블의 상기 복사본 중 적어도 일부분을 판독하는 수단;

판독 동작 요청에 응답하여, 상기 호스트 디바이스로, 상기 논리 어드레스에 대응하는 플래시 메모리의 물리 어드레스에 로케이트된 데이터를 반환하는 수단;

기록 동작 요청에 응답하여 데이터가 상기 논리 어드레스에 대응하는 상기 플래시 메모리 디바이스의 상기 물리 어드레스에 기록될 때 상기 플래시 메모리에 대해 이루어진 변화들에 일치하도록 상기 FTL 테이블의 상기 복사본을 업데이트하기 위해, 상기 호스트 디바이스의 상기 휘발성 메모리에 저장된 상기 FTL 테이블의 상기 복사본에 기록하는 수단; 및

상기 기록 동작 요청에 응답하여, 상기 호스트 디바이스로, 상기 기록 동작의 완료의 통지를 전송하는 수단을 포함하는, 플래시 메모리 디바이스. - 플래시 메모리 디바이스에 커플링하도록 구성된 호스트 디바이스로서,

상기 호스트 디바이스는,

휘발성 메모리;

상기 호스트 디바이스의 상기 휘발성 메모리와 통신가능하게 접속하며 상기 호스트 디바이스에 커플링될 때 상기 플래시 메모리 디바이스와 통신하도록 구성되는 통신 버스; 및

상기 휘발성 메모리 및 상기 통신 버스에 커플링된 프로세서를 포함하며,

상기 프로세서는,

상기 플래시 메모리 디바이스가 상기 휘발성 메모리에서의 상기 플래시 메모리 디바이스의 플래시 변환 계층 (FTL) 테이블의 복사본의 호스트 캐싱을 지원하는지 여부를 결정하는 것;

상기 FTL 테이블의 상기 복사본을 저장하기 위해 상기 휘발성 메모리의 부분을 할당하는 것; 및

상기 통신 버스를 통해서 상기 휘발성 메모리의 상기 부분에 대한 상기 플래시 메모리 디바이스에게 직접 메모리 액세스 판독 및 기록 특권들을 승인하는 것을 포함하는 동작들을 수행하는 프로세서-실행가능한 명령들로 구성되는, 플래시 메모리 디바이스. - 제 57 항에 있어서,

상기 프로세서는,

상기 플래시 메모리 디바이스에 저장된 상기 FTL 테이블의 사이즈에 대해 상기 플래시 메모리 디바이스에 쿼리하는 것; 및

상기 휘발성 메모리가 상기 FTL 테이블의 모두를 저장할 수 있는지 여부를 결정하는 것을 더 포함하는 동작들을 수행하는 프로세서-실행가능한 명령들로 구성되며,

상기 휘발성 메모리의 상기 부분을 할당하는 것은 상기 FTL 테이블의 상기 사이즈에 기초하여 상기 휘발성 메모리의 부분의 사이즈를 결정하는 것을 포함하는, 플래시 메모리 디바이스. - 플래시 메모리 디바이스에 커플링하도록 구성된 호스트 디바이스로서,

상기 호스트 디바이스는,

상기 플래시 메모리 디바이스가 상기 호스트 디바이스의 휘발성 메모리에서의 상기 플래시 메모리 디바이스의 플래시 변환 계층 (FTL) 테이블의 복사본의 호스트 캐싱을 지원하는지 여부를 결정하는 수단;

상기 FTL 테이블의 상기 복사본을 저장하기 위해 상기 휘발성 메모리의 부분을 할당하는 수단; 및

상기 휘발성 메모리의 상기 부분에 대한 상기 플래시 메모리 디바이스에게 직접 메모리 액세스 판독 및 기록 특권들을 승인하는 수단을 포함하는, 호스트 디바이스. - 제 59 항에 있어서,

상기 플래시 메모리 디바이스에 저장된 상기 FTL 테이블의 사이즈에 대해 상기 플래시 메모리 디바이스에 쿼리하는 수단; 및

상기 휘발성 메모리가 상기 FTL 테이블의 모두를 저장할 수 있는지 여부를 결정하는 수단을 더 포함하며,

상기 휘발성 메모리의 부분을 할당하는 수단은 상기 FTL 테이블의 상기 사이즈에 기초하여 상기 휘발성 메모리의 상기 부분의 사이즈를 결정하는 수단을 포함하는, 호스트 디바이스.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US13/892,433 | 2013-05-13 | ||

| US13/892,433 US9575884B2 (en) | 2013-05-13 | 2013-05-13 | System and method for high performance and low cost flash translation layer |

| PCT/US2014/037531 WO2014186232A1 (en) | 2013-05-13 | 2014-05-09 | System and method for high performance and low cost flash translation layer |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20160006709A true KR20160006709A (ko) | 2016-01-19 |

Family

ID=50942864

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020157033238A KR20160006709A (ko) | 2013-05-13 | 2014-05-09 | 고성능 및 저비용 플래시 변환 계층을 위한 시스템 및 방법 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US9575884B2 (ko) |

| EP (1) | EP2997459B1 (ko) |

| JP (1) | JP6190045B2 (ko) |

| KR (1) | KR20160006709A (ko) |

| CN (1) | CN105378642A (ko) |

| BR (1) | BR112015028634A2 (ko) |

| TW (1) | TWI556099B (ko) |

| WO (1) | WO2014186232A1 (ko) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20170132652A (ko) * | 2016-05-24 | 2017-12-04 | 삼성전자주식회사 | 저장 장치 레이턴시/대역폭 자가 모니터링을 위한 방법 및 장치 |

Families Citing this family (56)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20150139718A (ko) * | 2014-06-03 | 2015-12-14 | 에스케이하이닉스 주식회사 | 불휘발성 메모리를 제어하는 컨트롤러 및 그것을 포함하는 반도체 장치 |

| US9563382B2 (en) | 2014-06-05 | 2017-02-07 | Sandisk Technologies Llc | Methods, systems, and computer readable media for providing flexible host memory buffer |

| US9507722B2 (en) * | 2014-06-05 | 2016-11-29 | Sandisk Technologies Llc | Methods, systems, and computer readable media for solid state drive caching across a host bus |

| US10228854B2 (en) | 2014-08-20 | 2019-03-12 | Sandisk Technologies Llc | Storage devices and methods for optimizing use of storage devices based on storage device parsing of file system metadata in host write operations |

| US10268584B2 (en) * | 2014-08-20 | 2019-04-23 | Sandisk Technologies Llc | Adaptive host memory buffer (HMB) caching using unassisted hinting |

| US10007442B2 (en) | 2014-08-20 | 2018-06-26 | Sandisk Technologies Llc | Methods, systems, and computer readable media for automatically deriving hints from accesses to a storage device and from file system metadata and for optimizing utilization of the storage device based on the hints |

| US9851901B2 (en) * | 2014-09-26 | 2017-12-26 | Western Digital Technologies, Inc. | Transfer of object memory references in a data storage device |

| US10007433B2 (en) * | 2015-01-21 | 2018-06-26 | Sandisk Technologies Llc | Systems and methods for performing adaptive host memory buffer caching of transition layer tables |

| US10101918B2 (en) | 2015-01-21 | 2018-10-16 | Sandisk Technologies Llc | Systems and methods for generating hint information associated with a host command |

| KR20160120004A (ko) * | 2015-04-07 | 2016-10-17 | 삼성전자주식회사 | 시스템 온-칩 및 이를 포함하는 전자 기기 |

| CN106155579A (zh) * | 2015-04-27 | 2016-11-23 | 广明光电股份有限公司 | 固态硬盘动态储存转换层数据的方法 |

| CN106293493A (zh) * | 2015-05-18 | 2017-01-04 | 广明光电股份有限公司 | 固态硬盘模块动态储存转换层的方法 |

| US10055236B2 (en) * | 2015-07-02 | 2018-08-21 | Sandisk Technologies Llc | Runtime data storage and/or retrieval |

| US10452556B2 (en) | 2015-09-11 | 2019-10-22 | Toshiba Memory Corporation | Memory device and information processing device |

| TWI553478B (zh) * | 2015-09-23 | 2016-10-11 | 瑞昱半導體股份有限公司 | 能夠使用外部揮發性記憶體的裝置以及能夠釋放內部揮發性記憶體的裝置 |

| CN106557271B (zh) * | 2015-09-30 | 2019-08-20 | 合肥沛睿微电子股份有限公司 | 能够使用外部挥发性记忆体的装置以及能够释放内部挥发性记忆体的装置 |

| US10452594B2 (en) | 2015-10-20 | 2019-10-22 | Texas Instruments Incorporated | Nonvolatile logic memory for computing module reconfiguration |

| TWI556100B (zh) * | 2015-10-26 | 2016-11-01 | 點序科技股份有限公司 | 快閃記憶體裝置及其交錯存取方法 |

| CN105353989B (zh) | 2015-11-19 | 2018-12-28 | 华为技术有限公司 | 存储数据访问方法及相关的控制器、设备、主机和系统 |

| US20170177497A1 (en) * | 2015-12-21 | 2017-06-22 | Qualcomm Incorporated | Compressed caching of a logical-to-physical address table for nand-type flash memory |

| US9927997B2 (en) | 2015-12-21 | 2018-03-27 | Sandisk Technologies Llc | Methods, systems, and computer readable media for automatically and selectively enabling burst mode operation in a storage device |

| US10331203B2 (en) | 2015-12-29 | 2019-06-25 | Texas Instruments Incorporated | Compute through power loss hardware approach for processing device having nonvolatile logic memory |

| US10114743B2 (en) * | 2016-04-06 | 2018-10-30 | Sandisk Technologies Inc. | Memory erase management |

| US10157004B2 (en) * | 2016-04-14 | 2018-12-18 | Sandisk Technologies Llc | Storage system and method for recovering data corrupted in a host memory buffer |

| CN109074318B (zh) * | 2016-05-31 | 2023-07-04 | 桑迪士克科技有限责任公司 | 用于执行转换层表的自适应主机存储器缓冲区高速缓存的系统和方法 |

| US10521118B2 (en) | 2016-07-13 | 2019-12-31 | Sandisk Technologies Llc | Methods, systems, and computer readable media for write classification and aggregation using host memory buffer (HMB) |

| US10503635B2 (en) * | 2016-09-22 | 2019-12-10 | Dell Products, Lp | System and method for adaptive optimization for performance in solid state drives based on segment access frequency |

| CN107870870B (zh) * | 2016-09-28 | 2021-12-14 | 北京忆芯科技有限公司 | 访问超过地址总线宽度的内存空间 |

| CN107870867B (zh) * | 2016-09-28 | 2021-12-14 | 北京忆芯科技有限公司 | 32位cpu访问大于4gb内存空间的方法与装置 |

| US10853233B2 (en) | 2016-10-18 | 2020-12-01 | Toshiba Memory Corporation | Reconstruction of address mapping in a host of a storage system |

| CN108121664A (zh) * | 2016-11-28 | 2018-06-05 | 慧荣科技股份有限公司 | 数据储存装置以及其操作方法 |

| TWI627531B (zh) * | 2016-11-28 | 2018-06-21 | 慧榮科技股份有限公司 | 資料儲存裝置以及其操作方法 |

| US11256431B1 (en) | 2017-01-13 | 2022-02-22 | Lightbits Labs Ltd. | Storage system having a field programmable gate array |

| KR20180121733A (ko) * | 2017-04-28 | 2018-11-08 | 에스케이하이닉스 주식회사 | 데이터 저장 장치 및 그것의 동작 방법 |

| US10558393B2 (en) * | 2017-10-20 | 2020-02-11 | Qualcomm Incorporated | Controller hardware automation for host-aware performance booster |

| JP2019079464A (ja) * | 2017-10-27 | 2019-05-23 | 東芝メモリ株式会社 | メモリシステムおよび制御方法 |

| US10409726B2 (en) * | 2017-10-30 | 2019-09-10 | Micron Technology, Inc. | Dynamic L2P cache |

| KR102384759B1 (ko) | 2017-11-13 | 2022-04-11 | 삼성전자주식회사 | 호스트 메모리 버퍼를 사용하기 위해 호스트 장치와 속성 정보를 공유하는 스토리지 장치 및 그것을 포함하는 전자 장치 |

| WO2019099018A1 (en) | 2017-11-17 | 2019-05-23 | Hewlett-Packard Development Company, L.P. | Peripheral device configurations by host systems |

| US10459844B2 (en) * | 2017-12-21 | 2019-10-29 | Western Digital Technologies, Inc. | Managing flash memory read operations |

| US10725983B2 (en) | 2017-12-29 | 2020-07-28 | Huawei Technologies Co., Ltd. | Systems and methods for database management using append-only storage devices |

| TWI679538B (zh) * | 2018-03-31 | 2019-12-11 | 慧榮科技股份有限公司 | 資料儲存系統之控制單元以及邏輯至物理映射表更新方法 |

| WO2019209707A1 (en) | 2018-04-23 | 2019-10-31 | Micron Technology, Inc. | Host logical-to-physical information refresh |

| US10884920B2 (en) | 2018-08-14 | 2021-01-05 | Western Digital Technologies, Inc. | Metadata-based operations for use with solid state devices |

| US11249664B2 (en) * | 2018-10-09 | 2022-02-15 | Western Digital Technologies, Inc. | File system metadata decoding for optimizing flash translation layer operations |

| US11340810B2 (en) | 2018-10-09 | 2022-05-24 | Western Digital Technologies, Inc. | Optimizing data storage device operation by grouping logical block addresses and/or physical block addresses using hints |

| KR20200046264A (ko) | 2018-10-24 | 2020-05-07 | 삼성전자주식회사 | 호스트 메모리 버퍼를 이용하는 데이터 스토리지 장치 및 그 동작 방법 |

| KR102599176B1 (ko) | 2018-11-14 | 2023-11-08 | 삼성전자주식회사 | 호스트 메모리 버퍼를 사용하는 스토리지 장치 및 그것의 메모리 관리 방법 |

| CN111367830B (zh) * | 2018-12-06 | 2023-11-14 | 北京忆恒创源科技股份有限公司 | 主机参与的重建ftl表的方法及其存储设备 |

| KR20200069889A (ko) * | 2018-12-07 | 2020-06-17 | 에스케이하이닉스 주식회사 | 컨트롤러, 이를 포함하는 메모리 시스템 및 이의 동작 방법 |

| KR20200088635A (ko) * | 2019-01-15 | 2020-07-23 | 에스케이하이닉스 주식회사 | 메모리 시스템 및 메모리 시스템의 동작방법 |

| KR20210118453A (ko) * | 2019-04-30 | 2021-09-30 | 양쯔 메모리 테크놀로지스 씨오., 엘티디. | 플래시 메모리의 판독 레벨을 관리하는 전자 장치 및 방법 |

| KR20200143871A (ko) | 2019-06-17 | 2020-12-28 | 삼성전자주식회사 | 스토리지를 포함하는 전자 장치 및 그의 스토리지 이용 방법 |

| KR20210068699A (ko) | 2019-12-02 | 2021-06-10 | 삼성전자주식회사 | 스토리지 장치, 스토리지 시스템 및 스토리지 장치의 동작 방법 |

| CN111177033A (zh) * | 2019-12-24 | 2020-05-19 | 河南文正电子数据处理有限公司 | 一种固态硬盘的使用方法 |

| KR20220080254A (ko) * | 2020-12-07 | 2022-06-14 | 에스케이하이닉스 주식회사 | 메모리 시스템 및 메모리 시스템의 컨트롤러 |

Family Cites Families (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6014724A (en) * | 1995-10-27 | 2000-01-11 | Scm Microsystems (U.S.) Inc. | Flash translation layer block indication map revision system and method |

| US6484218B1 (en) * | 1998-10-08 | 2002-11-19 | Texas Instruments Incorporated | Method for improving direct memory access performance |

| JP2001243110A (ja) * | 1999-12-20 | 2001-09-07 | Tdk Corp | メモリコントローラ、フラッシュメモリシステム及びフラッシュメモリへのアクセス方法 |

| JP4199519B2 (ja) * | 2002-11-05 | 2008-12-17 | パナソニック株式会社 | メモリ管理装置及びメモリ管理方法 |

| US8041878B2 (en) | 2003-03-19 | 2011-10-18 | Samsung Electronics Co., Ltd. | Flash file system |

| US6981123B2 (en) * | 2003-05-22 | 2005-12-27 | Seagate Technology Llc | Device-managed host buffer |

| US20050138464A1 (en) * | 2003-11-21 | 2005-06-23 | Chong Pohsoon | Scratch fill using scratch tracking table |

| TW200832440A (en) | 2007-01-25 | 2008-08-01 | Genesys Logic Inc | Flash memory translation layer system |

| KR101663667B1 (ko) | 2009-02-03 | 2016-10-07 | 삼성전자주식회사 | 플래시 메모리의 주소 매핑에 의한 데이터 관리 방법 및 장치 |

| US8219776B2 (en) | 2009-09-23 | 2012-07-10 | Lsi Corporation | Logical-to-physical address translation for solid state disks |

| US8874824B2 (en) * | 2009-06-04 | 2014-10-28 | Memory Technologies, LLC | Apparatus and method to share host system RAM with mass storage memory RAM |

| EP2264602A1 (en) | 2009-06-17 | 2010-12-22 | Gemalto SA | Memory device for managing the recovery of a non volatile memory |

| CN102201259A (zh) * | 2010-03-24 | 2011-09-28 | 建兴电子科技股份有限公司 | 非易失性存储器的平均抹写方法 |

| KR20110121897A (ko) | 2010-05-03 | 2011-11-09 | 삼성전자주식회사 | 사용자 장치 및 그것의 프로그램 페일 처리 방법 |

| US8966176B2 (en) * | 2010-05-27 | 2015-02-24 | Sandisk Il Ltd. | Memory management storage to a host device |

| KR20120081351A (ko) | 2011-01-11 | 2012-07-19 | 에스케이하이닉스 주식회사 | Ftl을 수행하는 비휘발성 메모리 장치 및 그의 제어 방법 |

| JP5405513B2 (ja) * | 2011-03-22 | 2014-02-05 | 株式会社東芝 | メモリシステム、不揮発性記憶装置、不揮発性記憶装置の制御方法、及びプログラム |

| JP2012243287A (ja) * | 2011-05-24 | 2012-12-10 | Sony Corp | 情報処理装置および情報処理方法 |

| US8806112B2 (en) | 2011-07-14 | 2014-08-12 | Lsi Corporation | Meta data handling within a flash media controller |

| KR101856506B1 (ko) | 2011-09-22 | 2018-05-11 | 삼성전자주식회사 | 데이터 저장 장치 및 그것의 데이터 쓰기 방법 |

| CN102541760B (zh) * | 2012-01-04 | 2015-05-20 | 记忆科技(深圳)有限公司 | 基于固态硬盘的计算机系统 |

| US9213632B1 (en) * | 2012-02-29 | 2015-12-15 | Marvell International Ltd. | Systems and methods for data storage devices to use external resources |

| US9116820B2 (en) * | 2012-08-28 | 2015-08-25 | Memory Technologies Llc | Dynamic central cache memory |

| KR102015906B1 (ko) * | 2012-11-12 | 2019-08-29 | 삼성전자주식회사 | 불휘발성 메모리 장치를 포함하는 메모리 시스템 및 그것의 읽기 방법 |

| US9329991B2 (en) * | 2013-01-22 | 2016-05-03 | Seagate Technology Llc | Translation layer partitioned between host and controller |

| US9122588B1 (en) * | 2013-03-15 | 2015-09-01 | Virident Systems Inc. | Managing asymmetric memory system as a cache device |

-

2013

- 2013-05-13 US US13/892,433 patent/US9575884B2/en active Active

-

2014

- 2014-05-09 WO PCT/US2014/037531 patent/WO2014186232A1/en active Application Filing

- 2014-05-09 JP JP2016513995A patent/JP6190045B2/ja active Active

- 2014-05-09 BR BR112015028634A patent/BR112015028634A2/pt not_active Application Discontinuation

- 2014-05-09 EP EP14730327.5A patent/EP2997459B1/en not_active Not-in-force

- 2014-05-09 CN CN201480026743.4A patent/CN105378642A/zh active Pending

- 2014-05-09 KR KR1020157033238A patent/KR20160006709A/ko active IP Right Grant

- 2014-05-13 TW TW103116876A patent/TWI556099B/zh not_active IP Right Cessation

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20170132652A (ko) * | 2016-05-24 | 2017-12-04 | 삼성전자주식회사 | 저장 장치 레이턴시/대역폭 자가 모니터링을 위한 방법 및 장치 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP2997459B1 (en) | 2018-03-07 |

| JP6190045B2 (ja) | 2017-08-30 |

| WO2014186232A1 (en) | 2014-11-20 |

| CN105378642A (zh) | 2016-03-02 |

| BR112015028634A2 (pt) | 2017-07-25 |

| JP2016522942A (ja) | 2016-08-04 |

| TWI556099B (zh) | 2016-11-01 |

| TW201506619A (zh) | 2015-02-16 |

| EP2997459A1 (en) | 2016-03-23 |

| US9575884B2 (en) | 2017-02-21 |

| US20140337560A1 (en) | 2014-11-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP2997459B1 (en) | System and method for high performance and low cost flash translation layer | |

| CN107967221B (zh) | 具有非易失性存储器的计算系统及其操作方法 | |

| KR101673280B1 (ko) | 영구 저장소로의 라이트백을 요구하는 비 트랜잭션 코드 영역의 시작과 끝을 마킹하는 명령어들 | |

| TWI752620B (zh) | 與記憶體類型相關的頁表 | |

| TWI610172B (zh) | 用於經由集合和通道來靈活地將快取記憶體劃分成分量快取記憶體的方法和裝置 | |

| US20170255561A1 (en) | Technologies for increasing associativity of a direct-mapped cache using compression | |

| KR20190066466A (ko) | 기입 레이턴시를 줄일 수 있는 저장 장치의 동작 방법 | |

| US20220405015A1 (en) | Storage controller, computational storage device, and operational method of computational storage device | |

| US11775188B2 (en) | Communications to reclaim storage space occupied by proof of space plots in solid state drives | |

| US11960756B2 (en) | Management of storage space in solid state drives to support proof of space activities | |

| KR102595233B1 (ko) | 데이터 처리 시스템 및 그것의 동작 방법 | |

| KR20190022933A (ko) | 하이브리드 메모리 드라이브, 컴퓨터 시스템, 및 멀티 모드 하이브리드 드라이브를 동작시키기 위한 관련 방법 | |

| KR20200139433A (ko) | 컨트롤러의 동작 방법 및 메모리 시스템 | |

| CN110597742A (zh) | 用于具有持久系统存储器的计算机系统的改进存储模型 | |

| US20230229357A1 (en) | Storage controller, computational storage device, and operational method of computational storage device | |

| US20150106573A1 (en) | Data processing system | |

| KR20200114086A (ko) | 컨트롤러, 메모리 시스템 및 그것의 동작 방법 | |

| US11526454B2 (en) | Data storage device with an exclusive channel for flag checking of read data, and non-volatile memory control method | |

| US11768625B2 (en) | Storage device managing a multi-tier cache memory and operating method thereof | |

| US12014080B2 (en) | Memory system using host memory buffer and operation method thereof | |

| US20240329884A1 (en) | Method and a memory controller for managing memory operations in a storage device | |

| Khalifa et al. | A novel memory controller architecture | |

| CN111367830B (zh) | 主机参与的重建ftl表的方法及其存储设备 | |

| KR20240010310A (ko) | 컴퓨팅 시스템 및 그 동작 방법 | |

| KR20230151602A (ko) | 메모리 컨트롤러 및 그것을 포함하는 메모리 시스템 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| NORF | Unpaid initial registration fee |