KR20120124527A - 표시 장치 및 표시 장치의 제조 방법 - Google Patents

표시 장치 및 표시 장치의 제조 방법 Download PDFInfo

- Publication number

- KR20120124527A KR20120124527A KR1020110042220A KR20110042220A KR20120124527A KR 20120124527 A KR20120124527 A KR 20120124527A KR 1020110042220 A KR1020110042220 A KR 1020110042220A KR 20110042220 A KR20110042220 A KR 20110042220A KR 20120124527 A KR20120124527 A KR 20120124527A

- Authority

- KR

- South Korea

- Prior art keywords

- pixel

- display device

- organic layer

- electrode

- pixel electrode

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

- G02F1/134309—Electrodes characterised by their geometrical arrangement

- G02F1/134363—Electrodes characterised by their geometrical arrangement for applying an electric field parallel to the substrate, i.e. in-plane switching [IPS]

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

Abstract

표시 장치는 하부 기판, 유기막 패턴, 제1 화소 전극, 유전막 및 제2 화소 전극을 포함한다. 하부 기판은 스위칭 소자를 구비한다. 유기막 패턴은 상기 하부 기판 상에 배치되며, 화소 영역에 단차부를 포함한다. 제1 화소 전극은 화소 영역의 유기막 패턴 상에 배치된다. 유전막은 제1 화소 전극 상에 배치된다. 제2 화소 전극들은 유전막 상에서 제1 화소 전극과 부분적으로 중첩된다. 제1 화소 전극의 모폴로지에 의해 불균일한 수직 전계 발생이 억제되어 표시 장치 특히 화소 전극과 공통 전극 사이에 유기된 프린지 필드를 사용하는 PLS 모드 방식의 액정 표시 장치의 휘도 분포를 개선할 수 있다.

Description

본 발명은 표시 장치 및 이의 제조 방법에 관한 것이다. 보다 상세하게는, 본 발명은 액정 표시 장치 및 액정 표시 장치의 제조 방법에 관한 것이다.

일반적으로 액정 표시 장치는 하부 기판, 하부 기판과 마주하는 상부 기판, 상기 하부 기판과 상부 기판 사이에 게재되는 액정층 등으로 이루어진다.

상기 하부 기판 상에는 종횡으로 배열되어 복수의 화소 영역들을 정의하는 복수의 데이터 라인들 및 게이트 라인들이 배치된다. 상기 데이터 라인들과 게이트 라인들이 교차하는 영역들에는 박막 트랜지스터(thin film transistor: TFT)와 같은 스위칭 소자들이 배치되고, 상기 화소 영역들에는 화소 전극들이 각기 위치한다.

종래에는 액정 표시 장치의 구동 방식으로 네마틱 상의 액정 분자를 기판에 대해 수직 방향으로 구동시키는 TN(twisted nematic) 모드를 주로 사용하였으나, 최근에는 광 시야각 확보를 위해 PLS(plane to line switching) 모드가 이용되고 있다.

상기 PLS 모드를 사용하는 액정 표시 장치에 있어서, 박막트랜지스터(TFT)들이 배열된 하부 기판 상에 전계를 생성하기 위한 화소 전극 및 공통 전극을 서로 절연시켜 배치시키고, 상기 화소 전극과 공통 전극 사이에 유기된 프린지 필드(fringe field)에 의해 수평 배향된 액정 입자들로 액정층의 광투과율을 조절함으로써 화상을 표시하게 된다.

그러나, 상술한 PLS 모드를 갖는 액정 표시 장치에서 있어서, 화소 및 공통 전극들의 중앙부에서 불균일한 수직 전계가 발생하는 문제가 있다. 이를 완화하기 위해, 상기 화소 및 공통 전극들 사이에 두꺼운 절연막을 배치하거나, 상기 전극들을 슬릿(slit) 패턴으로 형성하는 방법들이 제안되고 있으나, 상기 전극들 사이의 불균일한 수직 전계를 최소화하기 위한 보다 근본적인 대안이 요구된다.

본 발명의 일 목적은 휘도 분포 및 투과율을 향상시킬 수 있는 표시 장치를 제공하는 것이다.

본 발명의 다른 목적은 휘도 분포 및 투과율을 향상시킬 수 있는 표시 장치의 제조 방법을 제공하는 것이다.

다만, 본 발명이 해결하고자 하는 과제는 전술한 과제들에 의해 한정되는 것은 아니며, 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위에서 다양하게 확장될 수 있을 것이다.

상술한 본 발명의 일 목적을 달성하기 위한 표시 장치는, 하부 기판, 유기막 패턴, 제1 화소 전극, 유전막 및 제2 화소 전극을 포함한다. 상기 하부 기판은 스위칭 소자를 구비한다. 상기 유기막 패턴은 상기 하부 기판 상에 배치되며, 화소 영역에 단차부를 포함한다. 상기 제1 화소 전극은 상기 화소 영역의 유기막 패턴 상에 배치된다. 상기 유전막은 상기 제1 화소 전극 상에 배치된다. 제2 화소 전극은 상기 유전막 상에서 상기 제1 화소 전극과 부분적으로 중첩한다.

예시적인 실시예들에 따르면, 상기 화소 영역의 유기막 패턴은 파동의 구조 또는 톱니 구조를 가질 수 있다.

예시적인 실시예들에 따르면, 상기 화소 영역의 유기막 패턴은 리세스들 또는 덴트들을 포함할 수 있다.

예시적인 실시예들에 따르면, 상기 리세스들 또는 덴트들은 각기 라운드 형상 또는 경사진 측벽을 포함할 수 있다.

예시적인 실시예들에 따르면, 상기 제1 화소 전극 및 상기 유전막은 각기 리세스들 또는 덴트들을 포함할 수 있다.

예시적인 실시예들에 따르면, 상기 제2 화소 전극들은 각기 상기 유전막의 리세스들 또는 덴트들에 배치될 수 있다.

예시적인 실시예들에 따르면, 상기 제2 화소 전극들의 상면들은 각기 상기 제1 화소 전극의 최상부의 상면보다 낮게 배치될 수 있다.

예시적인 실시예들에 따르면, 상기 제2 화소 전극은 제1 서브 전극 및 제2 서브 전극들을 포함할 수 있다. 상기 제1 서브 전극은 상기 스위칭 소자에 전기적으로 연결되며, 상기 제2 서브 전극들은 상기 제1 화소 전극과 부분적으로 중첩될 수 있다.

예시적인 실시예들에 따르면, 상기 제1 서브 전극은 상기 유전막 및 상기 유기막 패턴을 관통하는 콘택 홀을 통해 상기 스위칭 소자에 접촉될 수 있다.

예시적인 실시예들에 따르면, 상기 제1 화소 전극은 상기 스위칭 소자와 전기적으로 연결될 수 있다.

예시적인 실시예들에 따르면, 상기 스위칭 소자는 상기 하부 기판 상에 형성된 게이트 전극, 게이트 절연막, 활성층, 소스 전극 및 드레인 전극을 포함할 수 있다.

예시적인 실시예들에 따르면, 상기 표시 장치는 상기 제2 화소 전극들 상에 배치되는 액정층, 상기 액정층 상에 상기 하부 기판에 대향하여 배치되는 상부 기판을 더 포함할 수 있다.

예시적인 실시예들에 따르면, 상기 하부 기판은 데이터 라인을 포함하며 상기 제1 화소 전극은 상기 데이터 라인과 중첩될 수 있다.

예시적인 실시예들에 따르면, 상기 제1 화소 전극과 이에 인접하는 상기 제2 화소 전극들 사이에는 상기 하부 기판에 대해 수평한 전계가 생성될 수 있다.

상술한 본 발명의 다른 목적을 달성하기 위한 표시 장치의 제조 방법에 있어서, 하부 기판 상에 스위칭 소자를 형성한다. 상기 하부 기판 상에, 소자 영역에서 상기 스위칭 소자를 덮으며 화소 영역에서 단차부를 갖는 유기막 패턴을 형성한다. 상기 화소 영역의 상기 유기막 패턴 상에 제1 화소 전극을 형성한다. 상기 유기막 패턴 상에 상기 제1 화소 전극을 덮는 유전막을 형성한다. 상기 유전막 상에, 상기 제1 화소 전극과 부분적으로 중첩되는 제2 화소 전극들을 포함하는 제2 화소 전극을 형성한다.

예시적인 실시예들에 따르면, 상기 화소 영역의 유기막 패턴은 파동의 구조 또는 톱니 구조로 형성될 수 있다.

예시적인 실시예들에 따르면, 상기 화소 영역의 유기막 패턴에는 라운드 형상의 리세스들, 라운드 형상의 덴트들, 경사진 측벽을 갖는 리세스들, 또는 경사진 측벽을 갖는 덴트들이 형성될 수 있다.

예시적인 실시예들에 따르면, 상기 제2 화소 전극들은 라운드 형상의 리세스들, 라운드 형상의 덴트들, 경사진 측벽을 갖는 리세스들, 또는 경사진 측벽을 갖는 덴트들에 형성될 수 있다.

예시적인 실시예들에 따르면, 상기 유기막 패턴을 형성함에 있어서, 상기 하부 기판 상에 상기 스위칭 소자를 덮는 유기막을 형성한다. 상기 유기막을 투과 영역 및 반투과 영역을 갖는 마스크를 사용하여 노광한다. 상기 유기막의 노광된 부분을 부분적으로 제거한다.

예시적인 실시예들에 따르면, 상기 유기막 패턴을 형성함에 있어서, 상기 하부 기판 상에 상기 스위칭 소자를 덮는 유기막을 형성한다. 건식 식각 공정을 통해 상기 화소 영역의 유기막을 부분적으로 식각한다.

상술한 바와 같이, 본 발명에 따른 표시 장치는 물결 모양 혹은 톱니 모양의 단면 프로파일을 갖는 화소 전극들을 포함한다. 상기 화소 전극의 모폴로지 혹은 기하적인 형태에 기인하여 전극들 사이의 불균일한 수직 전계가 상쇄되고 수평 전계가 강화될 수 있다. 이에 따라, 표시 기판 전체에 걸쳐 휘도 분포가 개선되고 투과율을 향상시킬 수 있다. 부가적으로 상기 화소 전극의 모폴로지를 조절하여 데이터 라인과의 기생 커패시턴스(parasitic capacitance)를 최소화하고 광시야각을 증가시킬 수 있다.

도 1은 본 발명의 예시적인 실시예들에 따른 표시 장치를 나타내는 평면도이다.

도 2는 도 1의 "A" 부분을 확대한 평면도이다.

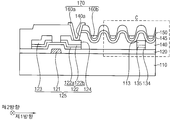

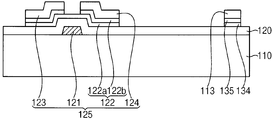

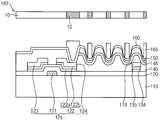

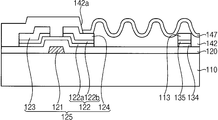

도 3은 도 2의 A-A' 라인을 따라 절단한 단면도이다.

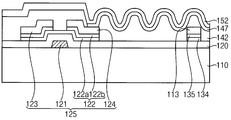

도 4는 본 발명의 다른 예시적인 실시예들에 따른 표시 장치를 나타내는 단면도이다.

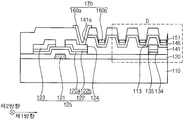

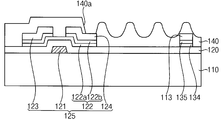

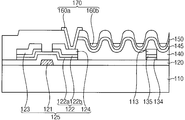

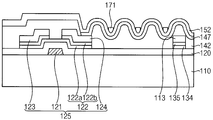

도 5는 본 발명의 또 다른 예시적인 실시예들에 따른 표시 장치를 나타내는 단면도이다.

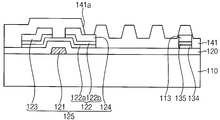

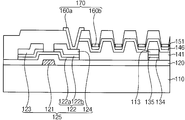

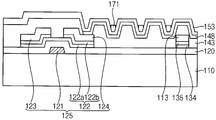

도 6은 본 발명의 또 다른 예시적인 실시예들에 따른 표시 장치를 나타내는 단면도이다.

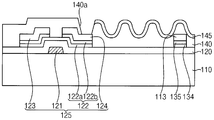

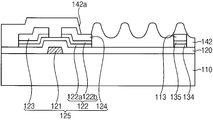

도 7은 종래의 PLS 모드를 갖는 액정 표시 장치에서 형성되는 프린지 필드를 나타내기 위한 단면도이다.

도 8은 도 3의 "C" 부분을 확대한 단면도이다.

도 9는 도 4의 "D" 부분을 확대한 단면도이다.

도 10 내지 도 23은 본 발명의 예시적인 실시예들에 따른 표시 장치의 제조 방법을 설명하기 위한 단면도들이다.

도 24 내지 도 31은 본 발명의 다른 예시적인 실시예들에 따른 표시 장치의 제조 방법을 설명하기 위한 단면도들이다.

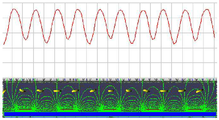

도 32는 종래의 PLS 모드로 구동하는 표시 장치에서 화소 전극 및 공통 전극 사이에 발생하는 전계를 설명하기 위한 그래프이다.

도 33 내지 도 35는 본 발명의 예시적인 실시예들에 따른 표시 장치들의 제1 화소 전극들 및 제2 화소 전극들 사이에서 발생하는 전계들을 설명하기 위한 그래프이다.

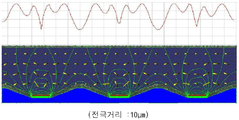

도 36은 도 32 내지 도 35을 참조하여 설명한 표시 장치들 각각에 대한 투과율들을 나타내는 그래프이다.

도 2는 도 1의 "A" 부분을 확대한 평면도이다.

도 3은 도 2의 A-A' 라인을 따라 절단한 단면도이다.

도 4는 본 발명의 다른 예시적인 실시예들에 따른 표시 장치를 나타내는 단면도이다.

도 5는 본 발명의 또 다른 예시적인 실시예들에 따른 표시 장치를 나타내는 단면도이다.

도 6은 본 발명의 또 다른 예시적인 실시예들에 따른 표시 장치를 나타내는 단면도이다.

도 7은 종래의 PLS 모드를 갖는 액정 표시 장치에서 형성되는 프린지 필드를 나타내기 위한 단면도이다.

도 8은 도 3의 "C" 부분을 확대한 단면도이다.

도 9는 도 4의 "D" 부분을 확대한 단면도이다.

도 10 내지 도 23은 본 발명의 예시적인 실시예들에 따른 표시 장치의 제조 방법을 설명하기 위한 단면도들이다.

도 24 내지 도 31은 본 발명의 다른 예시적인 실시예들에 따른 표시 장치의 제조 방법을 설명하기 위한 단면도들이다.

도 32는 종래의 PLS 모드로 구동하는 표시 장치에서 화소 전극 및 공통 전극 사이에 발생하는 전계를 설명하기 위한 그래프이다.

도 33 내지 도 35는 본 발명의 예시적인 실시예들에 따른 표시 장치들의 제1 화소 전극들 및 제2 화소 전극들 사이에서 발생하는 전계들을 설명하기 위한 그래프이다.

도 36은 도 32 내지 도 35을 참조하여 설명한 표시 장치들 각각에 대한 투과율들을 나타내는 그래프이다.

이하, 본 발명의 예시적인 실시예들에 따른 표시 장치들 및 표시 장치의 제조 방법들에 대하여 첨부된 도면들을 참조하여 상세하게 설명하지만, 본 발명이 하기 실시예들에 의해 제한되는 것은 아니며, 해당 분야에서 통상의 지식을 가진 자라면 본 발명의 기술적 사상을 벗어나지 않는 범위 내에서 본 발명을 다양한 다른 형태로 구현할 수 있을 것이다.

본 명세서에 있어서, 특정한 구조적 내지 기능적 설명들은 단지 본 발명의 실시예들을 설명하기 위한 목적으로 예시된 것이고, 본 발명의 실시예들은 다양한 형태로 실시될 수 있으며, 본 명세서에 설명된 실시예들에 한정되는 것으로 해석되지 않으며, 본 발명의 사상 및 기술 범위에 포함되는 모든 변경, 균등물 내지 대체물을 포함하는 것으로 이해되어야 한다. 어떤 구성 요소가 다른 구성 요소에 "연결되어" 있다거나 "접촉되어"있다고 기재된 경우, 다른 구성 요소에 직접적으로 연결되어 있거나 또는 접촉되어 있을 수도 있지만, 중간에 또 다른 구성 요소가 존재할 수도 있다고 이해되어야 할 것이다. 또한, 어떤 구성 요소가 다른 구성 요소에 "직접 연결되어" 있다거나 "직접 접촉되어"있다고 기재된 경우에는, 중간에 또 다른 구성 요소가 존재하지 않는 것으로 이해될 수 있다. 구성 요소들 간의 관계를 설명하는 다른 표현들, 예를 들면, "~사이에"와 "직접 ~사이에" 또는 "~에 인접하는"과 "~에 직접 인접하는" 등도 마찬가지로 해석될 수 있다.

본 명세서에서 사용되는 용어는 단지 예시적인 실시예들을 설명하기 위해 사용된 것으로, 본 발명을 한정하려는 의도는 아니다. 단수의 표현은 문맥상 명백하게 다르게 뜻하지 않는 한, 복수의 표현을 포함한다. 본 명세서에서, "포함하다", "구비하다" 또는 "가지다" 등의 용어는 실시된 특징, 숫자, 단계, 동작, 구성 요소, 부품 또는 이들을 조합한 것이 존재함을 지정하려는 것이지, 하나 또는 그 이상의 다른 특징들이나 숫자, 단계, 동작, 구성 요소, 부품 또는 이들을 조합한 것들의 존재 또는 부가 가능성을 미리 배제하지 않는 것으로 이해되어야 한다. 다르게 정의되지 않는 한, 기술적이거나 과학적인 용어를 포함해서 여기서 사용되는 모든 용어들은 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자에 의해 일반적으로 이해되는 것과 동일한 의미를 가지고 있다. 일반적으로 사용되는 사전에 정의되어 있는 것과 같은 용어들은 관련 기술의 문맥 상 가지는 의미와 일치하는 의미를 가지는 것으로 해석되어야 하며, 본 출원에서 명백하게 정의하지 않는 한, 이상적이거나 과도하게 형식적인 의미로 해석되지는 않는다.

제1, 제2 및 제3 등의 용어는 다양한 구성 요소들을 설명하는데 사용될 수 있지만, 이러한 구성 요소들은 상기 용어들에 의해 한정되는 것은 아니다. 상기 용어들은 하나의 구성 요소를 다른 구성 요소로부터 구별하는 목적으로 사용된다. 예를 들어, 본 발명의 권리 범위로부터 벗어나지 않고, 제1 구성 요소가 제2 또는 제3 구성 요소 등으로 명명될 수 있으며, 유사하게 제2 또는 제3 구성 요소도 교호적으로 명명될 수 있다.

도 1은 본 발명의 예시적인 실시예들에 따른 표시 장치를 나타내는 평면도이다.

도 1을 참조하면, 표시 장치(100)는 하부 기판(110)을 포함한다. 예시적인 실시예들에 있어서, 하부 기판(110)은 표시 영역(DA), 제1 주변 영역(PA1), 제2 주변 영역(PA2), 제3 주변 영역(PA3) 및 제4 주변 영역(PA4)을 포함할 수 있다. 이 경우, 표시 영역(DA)은 하부 기판(110)의 중앙부에 위치할 수 있으며, 제1 내지 제4 주변 영역(PA1, PA2, PA3, PA4)은 각기 표시 영역(DA)을 둘러싸는 하부 기판(110)의 주변부들에 배치될 수 있다.

본 발명의 예시적인 실시예들에 따르면, 표시 장치(100)의 표시 영역(DA)에는 복수의 게이트 라인들(112) 및 복수의 데이터 라인들(113)이 배치될 수 있다. 게이트 라인들(112)은 하부 기판(110) 상에서 제1 방향으로 연장될 수 있으며, 데이터 라인들(113)은 하부 기판(110)의 상부에서 제2 방향을 따라 연장될 수 있다. 이 때, 상기 제1 방향은 상기 제2 방향에 대해 실질적으로 직교할 수 있다. 즉, 데이터 라인들(113)은 각기 게이트 라인들(112)에 대하여 실질적으로 직교하는 방향을 따라 배열될 수 있다.

표시 장치(100)의 제1 주변 영역(PA1)에는 게이트 라인들(112)의 일측 단부들과 연결되어 게이트 신호를 제공하는 복수의 게이트 패드들(114)이 배치될 수 있다. 또한, 표시 장치(100)의 제2 주변 영역(PA2)에는 데이터 라인들(113)의 일측 단부들에 연결되어 데이터 라인들(113)에 제공되는 영상 신호를 전달하는 복수의 데이터 패드들(115)이 위치할 수 있다.

전술한 바와 같이, 게이트 라인들(112) 및 데이터 라인들(113)의 교차에 따라 표시 장치(100)의 화소(pixel)들이 정의될 수 있다. 표시 장치(100)의 화소들 가운데 임의의 화소(A)를 확대하여 도 2에 도시한다.

도 2는 도 1의 "A" 부분을 확대한 평면도이다.

도 2에 도시한 바와 같이, 각 게이트 라인(112) 및 데이터 라인(113)의 교차 영역에는 스위칭 소자(125)가 배치된다. 표시 장치(100)의 각 화소에는 프린지 필드(fringe field)를 발생시키기 위한 제1 화소 전극(145) 및 제2 화소 전극(170)이 배치된다. 제2 화소 전극(170)은 제2 서브 전극(160b)들을 포함하며, 제2 서브 전극(160b)들은 슬릿(slit) 구조 또는 그리드(grid) 구조를 가질 수 있다. 예를 들면, 표시 장치(100)는 소정의 간격으로 이격되는 라인(line) 형상 또는 바(bar)의 형상으로 배열되는 복수의 제2 서브 전극(160b)들을 포함할 수 있다.

이하, 스위칭 소자(125)가 배치되는 영역을 "소자 영역"이라 지칭하고, 이러한 소자 영역을 제외한 상기 화소 내의 나머지 영역을 "화소 영역"이라 지칭한다.

도 3은 도 2의 A-A' 라인을 따라 절단한 단면도이다. 구체적으로 도 3에 도시된 표시 장치는 제1 화소 전극(145)이 공통 전극으로 제공되는 Middle-Com PLS 구조에 해당할 수 있다.

도 1 및 도 3을 참조하면, 표시 장치(100)는 하부 기판(110), 하부 기판(110) 상에 배치된 스위칭 소자(125), 제1 화소 전극(145) 및 제2 화소 전극(170)을 포함한다. 또한, 표시 장치(100)는 실질적으로 서로 교차하여 화소 영역을 정의하는 게이트 라인(112) 및 데이터 라인(113)을 포함한다. 게이트 라인(112)은 하부 기판(110) 상에서 제1 방향으로 연장될 수 있으며, 데이터 라인(113)은 하부 기판(110)의 상부에서 상기 제1 방향에 대해 실질적으로 직교하는 제2 방향을 따라 연장될 수 있다.

스위칭 소자(125)는 하부 기판(110) 상에 순차적으로 배치된 게이트 전극(121), 게이트 절연막(120), 활성층(active layer)(122), 소스 전극 (123) 및 드레인 전극(124)을 포함한다.

게이트 전극(121)은 게이트 라인(112)과 연결된다. 예시적인 실시예들에 있어서, 게이트 전극(121)은 라인 형상 또는 바의 형상을 갖는 게이트 라인(112)으로부터 돌출될 수 있다. 예를 들면, 게이트 전극(121)은 크롬(Cr), 알루미늄(Al), 탄탈륨(Ta), 몰리브덴(Mo), 티타늄(Ti), 텅스텐(W), 구리(Cu), 은(Ag), 이들의 합금 등을 포함할 수 있다. 이들은 단독으로 또는 서로 조합되어 사용될 수 있다.

게이트 절연막(120)은 게이트 라인(112) 및 게이트 전극(121)을 덮으면서 하부 기판(110) 상에 구비된다. 예를 들면, 게이트 절연막(120)은 실리콘 산화물(SiOx), 실리콘 질화물(SiNx), 실리콘 산질화물(SiOxNy) 등의 실리콘 화합물을 포함할 수 있다. 예시적인 실시예들에 있어서, 게이트 절연막(120)은 단층 구조 또는 다층 구조를 가질 수 있다.

활성층(122)은 게이트 절연막(120) 상에 구비된다. 예시적인 실시예들에 따르면, 활성층(122)은 비정질 실리콘을 함유하는 반도체층(122a) 및 n+ 타입으로 도핑된 비정질 실리콘을 포함하는 저항성 접촉층(122b)을 포함하는 다층 구조를 가질 수 있다. 다른 예시적인 실시예에 따르면, 활성층(122)은 불순물이 도핑된 실리콘으로 이루어진 단층 구조를 가질 수도 있다.

이와는 달리, 활성층(122)은 저온 폴리실리콘(low temperature poly silicon : LTPS) 박막 구조를 가질 수도 있다. 상기 LTPS 박막은 전자 이동도가 빨라 고집적화가 가능하므로 화소의 크기가 작은 경우 특히 유용하다. 상기 LTPS 박막은 비정질 실리콘 층을 증착한 후, 이를 레이저 어닐링(laser annealing) 공정 등을 통해 결정화 함으로써 형성할 수 있다.

이하에서는, 활성층(122)이 비정질 실리콘을 함유하는 반도체층(122a) 및 n+ 타입으로 도핑된 비정질 실리콘을 포함하는 저항성 접촉층(122b)을 구비하는 경우를 예로 들어 설명하고자 한다.

활성층(122) 상에는 소스 전극(123) 및 드레인 전극(124)이 배치된다. 소스 전극(123)은 데이터 라인(113)과 연결된다. 예를 들면, 소스 전극(123)은 라인 형상 또는 바의 형상을 가지는 데이터 라인(113)으로부터 돌출될 수 있다. 드레인 전극(124)은 소스 전극(123)으로부터 상기 제1 방향을 따라 이격될 수 있다. 예시적인 실시예들에 따르면, 드레인 전극(124)은 제1 서브 전극(160a)과 전기적으로 연결된다. 소스 및 드레인 전극(123, 124)은 각기 크롬, 알루미늄, 탄탈륨, 몰리브덴, 티타늄, 텅스텐, 구리, 은, 이들의 합금을 포함할 수 있다. 이들은 단독으로 또는 서로 조합되어 사용될 수 있다.

하부 기판(110) 상부에는 게이트 절연막(120), 스위칭 소자(125) 일부 및 데이터 라인(113)을 커버하며, 상기 화소 영역에 단차부들을 포함하는 유기막 패턴(140)이 배치된다. 예시적인 실시예들에 있어서, 유기막 패턴(140) 가운데 표시 장치(100)의 화소 영역에 위치하는 단차부를 포함하는 부분은, 도 3에 도시된 바와 같이, 실질적으로 파동(wave)의 형상을 가질 수 있다. 즉, 상기 화소 영역에 위치하는 유기막 패턴(140)에는 실질적으로 라운드 형상의 리세스(recess)들 또는 덴트(dent)들이 형성될 수 있다. 이러한 유기막 패턴(140)은 엠보싱 공정 등을 통해 형성될 수 있다. 유기막 패턴(140)은 아크릴계(acryl based) 수지, 폴리이미드계(polyimide based) 수지, 벤조사이클로부텐(benzocyclobutene; BCB) 등의 투명 절연 물질을 포함할 수 있다. 한편, 유기막 패턴(140)은 소자 영역에서 드레인 전극의 일부를 노출시키는 콘택 홀(140a)을 정의한다. 예시적인 실시예들에 따르면, 콘택 홀(140a)은 하부 기판(110)에 대해 실질적으로 수직한 측벽을 가질 수도 있으며, 하부 기판(110)에 대해 소정의 각도로 경사진 측벽을 가질 수도 있다.

다시 도 1 및 도 3을 참조하면, 제1 화소 전극(145)은 표시 장치(100)의 화소 영역에 위치하는 부분의 유기막 패턴(140) 상에 구비된다. 예시적인 실시예들에 있어서, 제1 화소 전극(145)은 유기막 패턴(140)의 표면 프로파일(profile)을 따라 배치될 수 있기 때문에, 유기막 패턴(140)의 형상과 실질적으로 동일하거나 실질적으로 유사한 파동의 형상을 가질 수 있다. 즉, 제1 화소 전극(145)도 복수의 실질적으로 라운드 형상의 리세스들 또는 덴트들을 포함하는 구조를 가질 수 있다. 예를 들면, 제1 화소 전극(145)은 인듐 주석 산화물(indium tin oxide: ITO), 아연 주석 산화물(zinc tin oxide; ZTO), 인듐 아연 산화물(indium zinc oxide: IZO), 아연 산화물(ZnOx) 등의 투명 도전성 물질을 포함할 수 있다. 예시적인 실시예들에 따르면, 제1 화소 전극(145)은 전술한 투명 도전성 물질로 구성된 단층 구조 또는 다층 구조를 가질 수 있다.

제1 화소 전극(145)을 덮는 유전막(150)이 화소 영역에 위치하는 유기막 패턴(140) 상에 구비된다. 유전막(150)은 상기 화소 영역에서 제1 화소 전극(145)의 표면 프로파일을 따라 배치될 수 있기 때문에, 유전막(150)도 유기막 패턴(140)의 단차 구조로부터 유래되는 실질적으로 파동의 형상을 가질 수 있다. 즉, 유전막(150)도 복수의 라운드 형상의 리세스들 또는 덴트들을 포함할 수 있다. 유전막(150)은 투명 절연성 물질로 구성될 수 있다. 예를 들면, 유전막(150)은 투명 수지, 투명 플라스틱 등을 포함할 수 있다.

제2 화소 전극(170)은 콘택 홀(140a)의 내벽 및 유전막(150) 상에 배치된다. 제2 화소 전극(170)은 콘택 홀(140a) 내벽 상에 위치하여 드레인 전극(124)에 접촉하는 제1 서브 전극(160a) 및 상기 화소 영역에서 제1 화소 전극(145)의 일부와 중첩되게 배치되는 제2 서브 전극(160b)들을 포함한다.

본 발명의 예시적인 실시예들에 따르면, 제2 화소 전극(170)은 복수의 제2 서브 전극(160b)들을 포함할 수 있다. 이 경우, 제2 서브 전극(160b)들은 파동의 형상을 갖는 유전막(150)의 골 부분들(즉, 오목한 부분들, 리세스들 또는 덴트들)에 각각 배치될 수 있다. 제2 서브 전극(160b)들은 유전막(150) 상에서 상기 제2 방향을 따라 연장될 수 있으며, 예를 들면, 슬릿 구조 또는 그리드 구조를 가질 수 있다. 제2 화소 전극(170)은 인듐 주석 산화물(ITO), 인듐 아연 산화물(IZO), 아연 주석 산화물(ZTO), 아연 산화물 등과 같은 투명 도전성 물질을 포함할 수 있다. 또한, 제2 화소 전극(170)은 이러한 투명 도전성 물질로 이루어진 단층 구조 또는 다층 구조를 가질 수 있다.

일 실시예에 있어서, 도 3에 도시된 바와 같이, 제2 화소 전극(170)의 제2 서브 전극들(160b)의 상면은 제1 화소 전극(145)의 최상부 상면보다 실질적으로 낮게 위치할 수 있다.

도시하지는 않았으나, 예시적인 실시예들에 따른 표시 장치(100)는 제2 화소 전극(170)과 유기막 패턴(140) 상에 배치되는 액정 분자들, 제1 및 제2 화소 전극(145, 170) 상부에 배치되는 상부 기판을 구비할 수 있다. 이 경우, 상기 상부 기판의 저면 또는 상면 상에 특정한 색광들을 구현하기 위한 컬러 필터들이 추가적으로 배치될 수 있다.

도 4는 본 발명의 다른 예시적인 실시예들에 따른 표시 장치를 나타내는 단면도이다.

도 1 및 도 4를 참조하면, 하부 기판(110) 상부에 배치되는 유기막 패턴(141) 중에서 표시 장치(100)의 화소 영역에 위치하는 부분은 실질적으로 톱니 구조와 같은 단차부를 포함할 수 있다. 예를 들면, 상기 화소 영역에 위치하는 유기막 패턴(141)은 실질적으로 경사진 측벽을 갖는 복수의 리세스들 또는 덴트들을 포함하는 구조를 가질 수 있다. 이에 따라, 제1 화소 전극(146) 및 유전막(151)도 각기 유기막 패턴(141)의 표면 프로파일을 따라 실질적으로 경사진 측벽을 갖는 리세스들 또는 덴트들을 포함하는 톱니 구조를 가질 수 있다.

일 실시예에 있어서, 도 4에 도시된 바와 같이, 제2 화소 전극(170)의 제2 서브 전극(160b)의 상면은 제1 화소 전극(146)의 최상부 상면보다 실질적으로 낮게 위치할 수 있다.

도 5는 본 발명의 또 다른 예시적인 실시예들에 따른 표시 장치를 나타내는 단면도이다. 구체적으로, 도 5에 도시된 표시 장치는 제2 화소 전극(171)이 공통 전극으로 제공되는 Top-Com PLS 구조에 해당할 수 있다.

도 1 및 도 5를 참조하면, 유기막 패턴(142)은 표시 장치(100)의 화소 영역에서 실질적으로 라운드 형상의 리세스들 또는 덴트들을 포함하는 파동 형상을 가지며, 소자 영역에서는 드레인 전극(124)의 일부를 노출시키는 콘택 홀(142a)을 정의한다.

제1 화소 전극(147)은 화소 영역의 유기막 패턴(142) 및 소자 영역의 콘택 홀(142a)의 저면 상에 형성되어 드레인 전극(124)과 접촉한다. 제1 화소 전극(147)을 덮는 유전막(152)이 유기막 패턴(142) 상에 구비된다. 상기 화소 영역 위치에서 제1 화소 전극(147) 및 유전막(152)은 유기막 패턴(142)의 표면 프로파일을 따라 형성되므로 유기막 패턴(142)의 단차 구조로부터 유래되는 실질적으로 파동의 구조를 가질 수 있다.

제2 화소 전극(171)은 화소 영역 위치에서 실질적으로 파동의 형상을 갖는 유전막(152)의 골 부분들(즉, 리세스들 또는 덴트들)에 배치될 수 있다. 일 실시예에 있어서, 제2 화소 전극(171)의 상면은 제1 화소 전극(147)의 최상부 상면보다 실질적으로 낮게 위치할 수 있다.

도 6은 본 발명의 또 다른 예시적인 실시예들에 따른 표시 장치를 나타내는 단면도이다.

도 1 및 도 6을 참조하면, 유기막 패턴(143)은 표시 장치(100)의 화소 영역에서 실질적으로 경사진 측벽을 갖는 리세스들 또는 덴트들을 포함하는 톱니 형상을 가지며, 소자 영역에서는 드레인 전극(124)의 일부를 노출시키는 콘택 홀(143a)을 정의한다.

제1 화소 전극(148)은 화소 영역의 유기막 패턴(143) 및 소자 영역의 콘택 홀(143a)의 저면 상에 형성되어 드레인 전극(124)과 접촉한다. 상기 화소 영역 위치에서 제1 화소 전극(148) 및 유전막(153)은 유기막 패턴(143)의 표면 프로파일을 따라 형성되므로 유기막 패턴(143)의 단차 구조로부터 유래되는 실질적으로 톱니 구조를 가질 수 있다. 일 실시예에 있어서, 제2 화소 전극(171)의 상면은 제1 화소 전극(148)의 최상부 상면보다 실질적으로 낮게 위치할 수 있다.

도 7은 종래의 PLS 모드를 갖는 표시 장치에 발생되는 프린지 필드를 설명하기 위한 단면도이다. 도 8 및 도 9는 본 발명의 예시적인 실시예들에 따라 각기 도 3의 "C" 부분 및 도 4의 "D" 부분에서 발생되는 프린지 필드들을 설명하기 위한 확대 단면도들이다.

도 7에 도시한 바와 같이, 종래의 PLS 모드의 표시 장치에서는, 평탄한 표면을 갖는 유기막(240) 상에 제1 화소 전극(245) 및 유전막(250)이 순차적으로 배치되고, 유전막(250) 상에 슬릿 패턴 형태의 제2 화소 전극(270)이 구비된다. 도 7을 참조하면, 제1 화소 전극(245)과 제2 화소 전극(270) 사이에서 프린지 필드들이 형성되며, 점선으로 나타낸 바와 같이 인접하는 제2 화소 전극(270)들 사이에서 수직 전계들이 불균일하게 집중될 수 있다. 이와 같은 불균일한 수직 전계 집중 현상에 의해 제2 화소 전극(270) 상에 배치되는 액정 분자들(도시되지 않음)의 배향의 제어가 어려워지며, 결국 종래의 표시 장치에 의해 표시되는 화상 전체에 걸쳐 휘도 분포의 분산이 커지는 문제가 발생한다.

도 8 및 도 9를 참조하면, 본 발명의 예시적인 실시예들에 따른 표시 장치는 유기막 패턴(140, 141). 제1 화소 전극(145, 146) 및 유전막(150, 151)이 리세스들 또는 덴트들을 포함하는 실질적으로 파동의 형상 또는 실질적으로 톱니의 형상 등과 같은 구조를 가질 수 있다. 여기서, 상기 표시 장치의 제2 화소 전극(170)의 제2 서브 전극(160b)들은 각기 유전막(150, 151)의 골 부분들(리세스들 또는 덴트들)에 배치될 수 있다. 제2 서브 전극(160b)들과 부분적으로 중첩되는 제1 화소 전극(145, 146)의 모폴로지(morphology) 혹은 기하학적 형태에 기인하여, 점선으로 도시된 바와 같이 인접하는 제2 서브 전극(160b)들 사이에 하부 기판에 대해 부분적인 수평 전계들이 발생하며, 이에 따라 불균일한 수직 전계들이 상쇄되는 효과를 얻을 수 있다

도 8 및 도 9에 도시된 바와 같이, 본 발명의 일 실시예에 따르면, 제2 화소 전극의(170)의 제2 서브 전극(160b)의 상면들이 각기 제1 화소 전극들(145, 146)의 최상부 상면들보다 실질적으로 낮게 위치할 수 있다. 이 경우, PLS 모드 및 화소 전극과 공통 전극이 하부 기판에 대해 나란히 배치되는 IPS(In Plane Switch) 모드의 효과를 동시에 가질 수 있다.

구체적으로, 점선으로 도시된 바와 같이, 제2 서브 전극(160b)의 양 측부들에 제1 화소 전극(145, 146)이 부분적으로 중첩됨에 따라, 제2 서브 전극(160b)과 제1 화소 전극(145, 146) 사이에 발생되는 수평 전계들이 더욱 강화될 수 있다. 따라서, 제1 화소 전극(145, 146)과 제2 화소 전극(170) 사이에 불균일하게 발생하는 수직 전계들에 대한 상쇄 효과가 보다 커질 수 있다. 이에 따라, 액정 텍스처의 제어를 보다 용이하게 할 수 있으므로, 상기 표시 장치가 표시하는 영상의 잔상 문제를 방지할 수 있다.

더욱이, 유기막 패턴들(140, 141)의 단차와 리세스들 또는 덴트들의 경사 각도를 조정함에 따라 유기막 패턴들(140, 141)이 실질적으로 렌즈의 기능을 수행할 수 있으므로, 이러한 유기막 패턴들(140, 141)을 통해 액정 분자들의 광학적 굴절 및 회절을 조절하여 상기 표시 장치의 시야각 특성을 개선할 수 있으며, 영상의 색감을 원하는 수준으로 제어할 수 있다.

한편, 본 발명의 예시적인 실시예들에 따르면, 유기막 패턴(140, 141)의 단차를 조절함으로써, 데이터 라인(113)과 제1 화소 전극(145, 146) 및/또는 데이터 라인(113)과 제2 서브 전극(160b) 사이의 거리를 조정할 수 있다. 이에 따라 데이터 라인(113)과 제1 화소 전극(145, 146) 및/또는 데이터 라인(113)과 제2 화소 전극(170) 사이의 기생 커패시턴스를 최소함으로써 제2 화소 전극(170) 상에 인가되는 전압을 최소화 할 수 있고, 상기 표시 장치의 소비 전력을 감소시킬 수 있다.

또한, 도 8 및 도 9를 참조하면 제1 화소 전극(145, 146)은 데이터 라인(113)의 상부에도 위치할 수 있다. 즉, 제1 화소 전극(145, 146)이 상기 표시 장치의 화소 영역의 최외곽부까지 확장됨으로써, 상기 표시 장치의 개구율 및 투과율을 보다 향상시킬 수 있다.

도 10 내지 도 23은 본 발명의 예시적인 실시예들에 따른 표시 장치들의 제조 방법들을 설명하기 위한 단면도들이다.

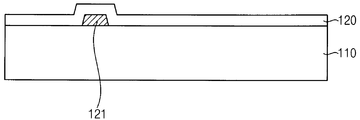

도 10을 참조하면, 하부 기판(110) 상에 게이트 전극(121) 및 게이트 라인(도시되지 않음)을 형성한다. 하부 기판(110)은 투명 절연 기판을 포함할 수 있다. 예를 들면, 하부 기판(110)은 유리 기판, 투명 플라스틱 기판, 투명 세라믹 기판 등으로 구성될 수 있다. 예시적인 실시예들에 있어서, 하부 기판(110) 상에 제1 도전막(도시되지 않음)을 형성한 후, 식각 공정을 통해 상기 제1 도전막을 패터닝하여 하부 기판(110) 상에 게이트 전극(121)과 상기 게이트 라인을 형성할 수 있다. 상기 제1 도전막은 크롬, 알루미늄, 탄탈륨, 몰리브덴, 티타늄, 텅스텐, 구리, 은, 이들의 합금 등을 사용하는 스퍼터링 공정, 화학 기상 증착(CVD) 공정, 프린팅(printing) 공정 등을 통해 형성될 수 있다. 이 경우, 상기 제1 도전막은 두 가지 이상의 도전성 물질을 포함하는 다층 구조로 형성될 수도 있다.

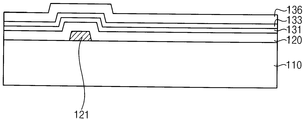

도 11을 참조하면, 게이트 전극(121) 및 상기 게이트 라인을 커버하면서 하부 기판(110) 상에 게이트 절연막(120)을 형성한다. 예를 들면, 게이트 절연막(120)은 실리콘 질화물(SiNx), 실리콘 산화물(SiOx), 실리콘 산질화물(SiOxNy) 등을 사용하는 화학 기상 증착(CVD) 공정, 플라즈마 증대 화학 기상 증착 공정(PECVD) 등을 통해 형성될 수 있다. 또한, 게이트 절연막(120)은 서로 다른 물질을 포함하는 다층 구조로 형성될 수도 있다.

도 12를 참조하면, 게이트 절연막(120) 상에 비정질(amorphous) 실리콘막(131), n+ 타입으로 도핑된 비정질 실리콘막(133) 및 제2 도전막(136)을 순차적으로 형성한다. 예시적인 실시예들에 있어서, 비정질(amorphous) 실리콘막(131)과 n+ 타입의 비정질 실리콘막(133)은 각기 화학 기상 증착 공정, 플라즈마 증대 화학 기상 증착 공정 등을 통해 형성될 수 있다. 제2 도전막(136)은 크롬, 알루미늄, 탄탈륨, 몰리브덴, 티타늄, 텅스텐, 구리, 은, 이들의 합금 등을 사용하는 스퍼터링 공정, 화학 기상 증착 공정, 프린팅 공정 등을 통해 형성될 수 있다. 또한, 제2 도전막(136)은 두 가지 이상의 도전성 물질로 이루어진 다층 구조로 형성될 수도 있다.

도 13을 참조하면, 비정질 실리콘막(131), n+ 타입의 비정질 실리콘막(133) 및 제2 도전막(136)을 식각하여 게이트 절연막(120) 상에 활성층(122), 소스 전극(123), 드레인 전극(124) 및 데이터 라인(113)을 형성한다. 예시적인 실시예들에 있어서, 제2 도전막(136)을 식각하여 소스 전극(123), 드레인 전극(124) 및 데이터 라인(113)을 형성한 다음, 비정질(amorphous) 실리콘막(131) 및 n+ 타입의 비정질 실리콘막(133)을 부분적으로 식각함으로써, 상기 표시 장치의 소자 영역에 활성층(122)을 형성하고, 상기 표시 장치의 화소 영역에 제1 및 제2 패턴(134, 135)을 형성할 수 있다. 상기 소자 영역의 활성층(122)은 비정질 실리콘을 포함하는 반도체층(122a) 및 n+ 타입의 비정질 실리콘을 포함하는 저항성 접촉층(122b)으로 구성된다. 상기 화소 영역의 제1 및 제2 패턴(134, 135)은 데이터 라인(113)과 하부 기판(110) 사이에 형성된다.

본 발명의 예시적인 실시예들에 따르면, 제2 도전막(136), n+ 타입의 비정질 실리콘막(133) 및 비정질 실리콘막(131)은 2회 이상의 식각 공정을 수행하여 순차적으로 식각될 수 있다. 이와는 다르게, 제2 도전막(136), n+ 비정질 실리콘막(133) 및 비정질 실리콘막(131)은 하프톤(halftone) 마스크를 사용하여 동시에 식각될 수 도 있다.

하부 기판(110) 상에서 데이터 라인(113) 및 상기 게이트 라인이 교차하는 영역들 가운데 상기 소자 영역에 게이트 전극(121), 게이트 절연막(120), 활성층(122), 소스 전극(123) 및 드레인 전극(124)을 포함하는 스위칭 소자(125)가 형성된다.

한편, 도시되지는 않았으나, 활성층은(122) 비정질 실리콘 층을 증착한 후, 이를 레이저 어닐링(laser annealing) 공정 등을 통해 결정화 함으로써 LTPS 박막 구조를 갖도록 형성할 수도 있다.

도 14를 참조하면, 게이트 절연막(120) 상에 스위칭 소자(125)의 일부와 데이터 라인(113)을 커버하는 유기막 패턴(140)을 형성한다. 예시적인 실시예들에 따르면, 아크릴계 수지, 폴리이미드계 수지, 벤조사이클로부텐(BCB) 등의 투명 절연성 물질을 스핀 코팅(spin coating) 공정, 슬릿 코팅(slit coating) 공정 등을 통해 하부 기판(110)의 전면 상에 결과물을 커버하는 유기막(도시되지 않음)을 형성한다. 데이터 라인(113)과 상기 게이트 라인이 교차하는 영역들 중에서 상기 화소 영역에 위치하는 상기 유기막의 일부에 대해 엠보싱 공정을 수행하여 유기막 패턴(140)을 형성한다. 예를 들면, 상기 유기막 상부에 차광 영역, 반투과 영역, 투과 영역 등을 포함하는 하프톤 마스크(도시되지 않음) 또는 하프톤 슬릿 마스크(도시되지 않음)를 위치시킨 후, 상기 하프톤 마스크 또는 하프톤 슬릿 마스크를 이용하여 상기 유기막을 노광시킨다. 상기 유기막의 노광된 부분을 현상액으로 제거함에 따라 하부 기판(110)의 상부에 유기막 패턴(140)을 형성한다. 유기막 패턴(140)이 형성되면서, 소자 영역 위치에서는 드레인 전극(124)의 일부를 노출시키는 콘택 홀(140a)이 동시에 형성된다. 콘택 홀(140a)은 각기 하부 기판(110)에 대하여 실질적으로 수직한 측벽을 가질 수도 있지만, 하부 기판(110)에 대해 소정의 각도로 경사지게 형성될 수도 있다

이 경우, 유기막 패턴(140)은 상기 화소 영역에서 도 14에 도시된 바와 같이 실질적으로 파동의 구조로 형성될 수 있다. 즉, 유기막 패턴(140) 중에서 상기 화소 영역에 위치하는 부분에 라운드 형상의 리세스들, 라운드 형상의 덴트들이 형성될 수 있다.

본 발명의 다른 예시적인 실시예들에 따르면, 상기 유기막 공정의 공정 조건을 조절하여 도 15에 도시된 바와 같이 유기막 패턴(141)이 실질적으로 톱니 구조로 형성될 수도 있다. 이 때, 상기 화소 영역에 위치하는 유기막 패턴(141)의 일부에 경사진 측벽을 갖는 리세스들, 경사진 측벽을 갖는 덴트들 등이 형성될 수 있다. 예를 들면, 건식 식각 공정을 이용하여 상기 화소 영역의 유기막을 부분적으로 식각함으로써, 경사진 측벽을 갖는 리세스들, 경사진 측벽을 덴트들 등을 포함하는 유기막 패턴(141)을 형성할 수 있다. 한편, 소자 영역의 유기막을 부분적으로 식각함으로써, 드레인 전극(124)의 일부를 노출시키는 콘택 홀(141a)을 동시에 형성할 수 있다. 콘택 홀(141a)은 각기 하부 기판(110)에 대하여 실질적으로 수직한 측벽을 가질 수도 있지만, 하부 기판(110)에 대해 소정의 각도로 경사지게 형성될 수도 있다.

도 16을 참조하면, 유기막 패턴(140) 상에 제1 투명 전극층(도시되지 않음)을 형성한 다음, 상기 제1 투명 전극층 중에서 상기 소자 영역에 위치하는 부분을 식각하여 유기막 패턴(140) 상에 제1 화소 전극(145)을 형성한다. 상기 제1 투명 전극층은 인듐 주석 산화물, 인듐 아연 산화물, 아연 산화물, 아연 주석 산화물 등과 같은 투명 도전성 물질로 사용하는 스퍼터링 공정, 화학 기상 증착 공정, 프린팅 공정 등을 통해 형성할 수 있다.

제1 화소 전극(145)은 유기막 패턴(140)의 구조와 실질적으로 동일하거나 실질적으로 유사한 구조로 형성될 수 있다. 예를 들면, 제1 화소 전극(145)은 라운드 형상의 리세스들, 라운드 형상의 덴트들을 포함하는 실질적으로 파동의 구조로 형성될 수 있다.

본 발명의 다른 예시적인 실시예들에 따르면, 도 17에 도시한 바와 같이, 유기막 패턴(141)이 실질적으로 톱니 구조를 가질 경우, 제1 화소 전극(146)도 실질적으로 톱니 구조로 형성될 수 있다. 예를 들면, 제1 화소 전극(146)은 경사진 측벽을 갖는 리세스들, 경사진 측벽을 갖는 덴트들 등을 포함할 수 있다.

본 발명의 예시적인 실시예들에 따르면, 제1 화소 전극(145, 146)은 데이터 라인(113)의 상부, 즉 데이터 라인(113)과 중첩되도록 형성될 수 있으며, 이에 따라 상기 표시 장치의 개구율 및 투과율을 보다 향상시킬 수 있다.

도 18을 참조하면, 제1 화소 전극(145) 상에 유전막(150)을 형성한다. 유전막(150)은 광을 투과시킬 수 있는 절연 물질을 사용하여 형성될 수 있으며, 화학 기상 증착 공정, 플라즈마 증대 화학 기상 증착 공정 등을 통해 제1 화소 전극(145) 상에 형성될 수 있다. 여기서, 유전막(150)은 제1 화소 전극(145)의 프로파일을 따라 형성되므로, 유기막 패턴(140)의 구조에 기인하는 실질적으로 파동의 구조로 형성될 수 있다.

본 발명의 다른 예시적인 실시예들에 있어서, 도 19에 도시한 바와 같이, 유기막 패턴(141)이 실질적으로 톱니 구조를 가질 경우에는, 상기 화소 영역에 위치하는 제1 화소 전극(146) 상에서 유전막(151)도 실질적으로 톱니 구조로 형성될 수 있다.

이하, 실질적으로 파동의 구조를 갖는 유전막(150)과 실질적으로 톱니 구조를 갖는 유전막(151) 상에 후속 부재들을 형성하는 공정들에 대하여 함께 설명한다.

도 20 및 도 21을 참조하면, 유전막들(150, 151) 및 콘택 홀들(140a, 141a)의 내벽 상에 형성되고 소자 영역을 커버하는 제2 투명 전극층들(160, 161)을 형성한 다음, 제2 투명 전극층들(160, 161) 상에 포토레지스트 패턴들(165)을 형성한다.

본 발명의 예시적인 실시예들에 있어서, 제2 투명 전극층들(160, 161)은 인듐 주석 산화물, 인듐 아연 산화물, 아연 산화물, 아연 주석 산화물 등의 투명 도전성 물질을 사용하여 스퍼터링 공정, 화학 기상 증착 공정, 프린팅 공정 등을 통해 형성될 수 있다. 제2 투명 전극층들(160, 161) 상에 각기 포토레지스트막을 형성한 후, 상기 포토레지스트막들을 각기 투과 영역(10)과 차광 영역(12)을 갖는 마스크들(167)을 이용하여 노광시킨다. 이와 같이 노광된 포토레지스트막들에 대해 현상 공정을 수행하여 유전막들(150, 151) 상에 각기 포토레지스트 패턴들(165)을 형성한다. 예를 들면, 마스크들(167)은 복수의 차광부(12)들을 포함하며, 차광부(12)들 아래에 위치하는 상기 포토레지스트막의 부분들은 현상 공정 후에 제거되지 않고 제2 투명 전극들(160, 161) 상에 포토레지스트 패턴들(165)을 형성하게 된다.

도 22 및 도 23을 참조하면, 포토레지스트 패턴들(165)을 식각 마스크들로 사용하여, 제2 투명 전극층들(160, 161)을 부분적으로 식각함으로써, 유전막들(150, 151) 상에 각기 제2 화소 전극들(170)을 형성한다. 제2 화소 전극들(170)의 형성 후, 포토레지스트 패턴들(165)은 애싱(ashing) 공정 및/또는 스트립(strip) 공정을 통해 제거될 수 있다.

본 발명의 예시적인 실시예들에 있어서, 제2 화소 전극들(170)은 각기 콘택 홀들(155)의 내벽 상에 형성되어 드레인 전극들(124)과 접촉하는 제1 서브 전극들(160a)과 상기 화소 영역에서 제1 화소 전극들(145, 146)과 대향하는 제2 서브 전극들(160b)을 포함할 수 있다. 예를 들면, 도 22 및 도 23에 도시된 바와 같이, 제2 서브 전극들(160b) 은 실질적으로 파동의 구조 및 실질적으로 톱니 구조로 형성된 유전막들(150, 151)의 골 부분들(리세스들 또는 덴트들)에 형성될 수 있다. 이에 따라, 전술한 바와 같이, 서로 대향하는 제2 화소 전극들(170)의 제2 서브 전극들(160b)과 제1 화소 전극들(145, 146) 사이에서 하부 기판(110)에 대해 실질적으로 평행한 방향으로 프린지 필드들이 생성될 수 있으며, 인접하는 제2 화소 전극들(170)사이에 생성되는 불균일한 수직 전계를 최소화 할 수 있다.

일 실시예에 있어서, 도 8 및 도 9를 참조하여 설명한 바와 같이, 제2 화소 전극(170)의 제2 서브 전극들(160b)의 상면들이 각기 제1 화소 전극들(145, 146)의 최상부들의 상면들보다 낮게 위치하도록 형성될 수도 있다.

도시하지는 않았으나, 하부 기판(110)의 주변부에 실런트(sealant)를 배치한 다음, 하부 기판(110)과 제1 및 제2 화소 전극들(145, 146, 170)에 대향하는 상부 기판을 결합하여 표시 장치를 제조할 수 있다. 이 경우, 액정 분자들은 하부 기판(110)과 상기 상부 기판의 결합 전후에 하부 기판(110)과 상기 상부 기판 사이의 공간에 주입될 수 있다. 또한, 상기 상부 기판 및/또는 하부 기판(110)에 스위칭 소자(125)에 대응하는 블랙 매트릭스, 컬러 영상을 구현하기 위한 컬러 필터 등이 배치될 수 있다.

본 발명의 예시적인 실시예들에 따른 표시 기판의 제조 방법들에 있어서, 전술한 공정들과 다른 순서의 공정들을 포함할 수도 있다. 또한, 상술한 바와 같이, 유기막 패턴, 제1 화소 전극, 유전막 등이 실질적으로 파동의 구조, 실질적으로 톱니 구조를 갖는 것으로 설명하였으나, 이들 부재들이 이러한 구조에 한정되는 것은 아니다. 예를 들면, 인접하는 화소 전극들 사이에서 수평 전계를 강화하고 수직 전계를 상쇄시키기 위해 적절한 구조로 형성될 수 있다.

도 24 및 도 는 본 발명의 다른 예시적인 실시예들에 따른 표시 장치들의 제조 방법들을 설명하기 위한 단면도들이다. 도 10 및 도 23을 참조로 설명한 공정들과 중복되는 부분들에 대한 자세한 설명은 생략한다.

도 24를 참조하면, 도 10 내지 도 14를 참조로 설명한 공정들과 실질적으로 동일하거나 유사한 공정들을 수행하여, 하부 기판(110) 상에 게이트 절연막, 스위칭 소자(125) 및 데이터 라인(113)을 형성한다. 이후, 게이트 절연막(120) 상에 데이터 라인(113)을 커버하는 유기막 패턴(142)을 형성한다.

유기막 패턴(142)은 도 24에 도시된 바와 같이, 화소 영역 위치에서는 라운드 형상의 리세스들 또는 덴트들을 포함하는 실질적으로 파동의 구조로 형성될 수 있으며, 소자 영역에서는 드레인 전극(124)의 일부를 노출시키는 콘택 홀(142a)이 형성될 수 있다.

다른 실시예들에 있어서, 도 25에 도시된 바와 같이, 유기막 패턴(143)은 화소 영역에서 실질적으로 톱니 구조를 갖도록 형성될 수도 있다. 한편, 소자 영역에서는 드레인 전극(124)의 일부를 노출시키는 콘택 홀(143a)이 유기막 패턴(143)과 함께 형성될 수 있다.

도 26을 참조하면, 화소 영역 위치에서 유기막 패턴(142) 상에 형성되고, 콘택 홀(142a)의 저면 상에서 드레인 전극(124) 일부와 접촉하는 제1 화소 전극(147)을 형성한다. 예시적인 실시예들에 따르면, 유기막 패턴(142) 및 콘택 홀(142a)의 내벽 상에 제1 투명 전극층을 형성한다. 상기 제1 투명 전극층을 포토레지스트 패턴 등을 사용한 사진 식각 공정을 통해 부분적으로 식각하여, 상기 화소 영역 위치의 유기막 패턴(142) 상에 구비되며 드레인 전극(124) 일부와 접촉하는 제1 화소 전극(147)을 형성한다. 제1 화소 전극(147)은 유기막 패턴(142)의 형상에 따라, 라운드 형상의 리세스들 혹은 덴트들을 포함하는 실질적으로 파동의 구조로 형성될 수 있다.

다른 예시적인 실시예들에 있어서, 도 27에 도시된 바와 같이, 유기막 패턴(143)이 실질적으로 톱니 구조를 갖는 경우, 제1 화소 전극(148)도 실질적으로 톱니 구조로 형성될 수 있다. 제1 화소 전극(148)은 콘택 홀(143a)의 저면 상에서 드레인 전극(124)의 일부와 접촉하도록 형성될 수 있다.

도 28을 참조하면, 유기막 패턴(142) 및 제1 화소 전극(147) 상에 유전막(152)을 형성한다. 유전막(152)은 화소 영역에서는 제1 화소 전극(147)의 프로파일을 따라 형성되므로, 유기막 패턴(142)의 구조에 따라 실질적으로 파동의 구조로 형성될 수 있다.

다른 예시적인 실시예들에 있어서, 도 29에 도시된 바와 같이, 유기막 패턴(143)이 실질적으로 톱니 구조를 갖는 경우, 유전막(153) 역시 화소 영역에 위치하는 제1 화소 전극(148) 상에 실질적으로 톱니 구조로 형성될 수 있다.

도 30 및 도 31을 참조하면, 도 20 내지 도 23을 참조로 설명한 공정들과 실질적으로 유사한 공정을 수행하여, 유전막들(152, 153) 상에 제2 화소 전극들(171)을 형성한다. 본 발명의 예시적인 실시예들에 있어서, 도 30 및 도 31에 도시된 바와 같이 제2 화소 전극들(171)은 실질적으로 파동의 구조 및 톱니 구조로 형성된 유전막들(152, 153)의 골 부분들(리세스들 혹은 덴트틀) 상에 형성될 수 있다.

이에 따라, 제1 화소 전극들(147, 148) 및 제2 화소 전극들(171) 사이에서 하부 기판(110)에 대해 실질적으로 평행한 프린지 필드들이 생성될 수 있으며, 인접하는 제2 화소 전극들(171) 사이에 생성되는 불균일한 수직 전계를 최소화 할 수 있다.

일 실시예에 있어서, 유기막 패턴(142, 143)의 단차를 조절하여 제2 화소 전극들(171)의 상면이 제1 화소 전극들(147, 148)의 최상부의 상면들보다 낮게 위치하도록 형성될 수도 있다.

도시하지는 않았으나, 하부 기판(110)의 주변부에 실런트(sealant)를 배치한 다음, 하부 기판(110)과 제1 및 제2 화소 전극들(147, 148, 171)에 대향하는 상부 기판을 결합하여 표시 장치를 제조할 수 있다. 이 경우, 액정 분자들은 하부 기판(110)과 상기 상부 기판 사이의 공간에 주입될 수 있다. 상기 상부 기판 및/또는 하부 기판(110)에 스위칭 소자(125)에 대응하는 블랙 매트릭스, 컬러 영상을 구현하기 위한 컬러 필터 등이 배치될 수 있다.

도 32는 종래의 PLS 모드의 액정 표시 장치에서 화소 전극 및 공통 전극 사이에 발생하는 전계를 설명하기 위한 그래프이다. 도 33 내지 도 35는 본 발명의 예시적인 실시예들에 따른 표시 장치들의 제1 화소 전극들과 제2 화소 전극들 사이에서 발생하는 전계들을 설명하기 위한 그래프들이다.

도 32에 도시된 바와 같이, 종래의 액정 표시 장치에 있어서, 서로 수평 하게 배치된 화소 전극 및 공통 전극 사이에서는 상대적으로 강한 수직 전계가 관찰된다. 반면, 도 33 내지 도 35에 도시한 바와 같이, 본 발명의 예시적인 실시예들에 따른 표시 장치들에 있어서는, 인접하는 화소 전극들 사이에서 발생되는 수직 전계들이 현저히 약화되는 반면, 수평 전계들이 상대적으로 강화되는 것을 알 수 있다. 특히, 상기 표시 장치들의 제1 화소 전극들과 제2 화소 전극들 사이의 거리가 감소할수록 수평 전계들이 증대되는 경향을 관찰할 수 있다.

도 36은 도 32 내지 도 35을 참조하여 설명한 표시 장치들 각각에 대한 투과율들을 나타내는 그래프이다.

도 36에 도시된 바와 같이, 전압이 약 4V를 넘어서면서 본 발명의 예시적인 실시예들에 따른 도 33 내지 도 35의 표시 장치의 경우 종래의 PLS 모드의 액정 표시 장치(도 32) 보다 투과율이 향상되는 점을 알 수 있다.

상술한 바와 같이, 본 발명의 예시적인 실시예들을 설명하였지만, 본 발명은 이에 한정되지 않으며 해당 기술 분야에서 통상의 지식을 가진 자라면 다음에 기재하는 특허 청구 범위의 개념과 범위를 벗어나지 않는 범위 내에서 다양한 변경 및 변형이 가능하다는 것을 이해할 수 있을 것이다.

본 발명의 실시예들에 따른 표시 장치는, 화소 전극과 공통 전극 사이에 유기된 프린지 필드를 사용하는 PLS 모드 방식의 액정 표시 장치로 활용될 수 있다. 예를 들면, 상기 표시 장치는 실질적으로 파동의 구조 혹은 실질적으로 톱니 구조의 모폴로지를 갖는 화소 전극들을 구비함으로써, 인접하는 화소 전극들 사이에서 불균일한 수직 전계를 최소화하여 표시 장치의 휘도 분포 및 투과율을 형상시킬 수 있다.

10: 마스크 12: 차광부

100: 표시기판 110: 하부기판

112: 게이트 라인 113: 데이터 라인

114: 게이트 패드 115: 데이터 패드

120: 게이트 절연막 121: 게이트 전극

122: 활성층 122a: 반도체 층

122b: 저항성 접촉층 123: 소스 전극

124: 드레인 전극 125: 스위칭 소자

131: 비정질 실리콘 막 133: n+ 비정질 실리콘 막

140, 141, 142, 143: 유기막 패턴

140a, 141a, 142a, 143a : 콘택 홀

145, 146, 147, 148: 제1 화소 전극

150, 151, 152, 153: 유전막

160: 제2 투명 전극층 160a: 제1 서브 전극

160b: 제2 서브 전극

165: 포토레지스트 패턴 170, 171: 제2 화소 전극

100: 표시기판 110: 하부기판

112: 게이트 라인 113: 데이터 라인

114: 게이트 패드 115: 데이터 패드

120: 게이트 절연막 121: 게이트 전극

122: 활성층 122a: 반도체 층

122b: 저항성 접촉층 123: 소스 전극

124: 드레인 전극 125: 스위칭 소자

131: 비정질 실리콘 막 133: n+ 비정질 실리콘 막

140, 141, 142, 143: 유기막 패턴

140a, 141a, 142a, 143a : 콘택 홀

145, 146, 147, 148: 제1 화소 전극

150, 151, 152, 153: 유전막

160: 제2 투명 전극층 160a: 제1 서브 전극

160b: 제2 서브 전극

165: 포토레지스트 패턴 170, 171: 제2 화소 전극

Claims (20)

- 스위칭 소자를 갖는 하부 기판;

상기 하부 기판 상에 배치되며, 화소 영역에 단차부를 포함하는 유기막 패턴;

상기 화소 영역의 유기막 패턴 상에 배치되는 제1 화소 전극;

상기 제1 화소 전극 상에 배치되는 유전막; 및

상기 유전막 상에서 상기 제1 화소 전극과 부분적으로 중첩되는 제2 화소 전극들을 구비하는 표시 장치. - 제1항에 있어서, 상기 화소 영역의 유기막 패턴은 파동의 구조 또는 톱니 구조를 가지는 것을 특징으로 하는 표시 장치.

- 제2항에 있어서, 상기 화소 영역의 유기막 패턴은 리세스들 또는 덴트들을 포함하는 것을 특징으로 하는 표시 장치.

- 제3항에 있어서, 상기 리세스들 또는 덴트들은 각기 라운드 형상 또는 경사진 측벽을 포함하는 것을 특징으로 하는 표시 장치.

- 제3항에 있어서, 상기 제1 화소 전극 및 상기 유전막은 각기 리세스들 또는 덴트들을 포함하는 것을 특징으로 하는 표시 장치.

- 제5항에 있어서, 상기 제2 화소 전극들은 각기 상기 유전막의 리세스들 또는 덴트들에 배치되는 것을 특징으로 하는 표시 장치.

- 제6항에 있어서, 상기 제2 화소 전극들의 상면들은 각기 상기 제1 화소 전극의 최상부의 상면보다 낮게 배치되는 것을 특징으로 하는 표시 장치.

- 제1항에 있어서, 상기 제2 화소 전극은 제1 서브 전극 및 제2 서브 전극들을 포함하며,

상기 제1 서브 전극은 상기 스위칭 소자에 전기적으로 연결되며, 상기 제2 서브 전극들은 상기 제1 화소 전극과 부분적으로 중첩되는 것을 특징으로 하는 표시 장치. - 제8항에 있어서, 상기 제1 서브 전극은 상기 유전막 및 상기 유기막 패턴을 관통하는 콘택 홀을 통해 상기 스위칭 소자에 접촉하는 것을 특징으로 하는 표시 장치.

- 제1항에 있어서, 상기 제1 화소 전극은 상기 스위칭 소자와 전기적으로 연결되는 것을 특징으로 하는 표시 장치.

- 제1항에 있어서, 상기 스위칭 소자는 상기 하부 기판 상에 형성된 게이트 전극, 게이트 절연막, 활성층, 소스 전극 및 드레인 전극을 포함하는 것을 특징으로 하는 표시 장치.

- 제1항에 있어서, 상기 제2 화소 전극들 상에 배치되는 액정층; 및

상기 액정층 상에 상기 하부 기판에 대향하여 배치되는 상부 기판을 더 포함하는 것을 특징으로 하는 표시 장치. - 제1항에 있어서, 상기 하부 기판은 데이터 라인을 포함하며, 상기 제1 화소 전극은 상기 데이터 라인과 중첩되는 것을 특징으로 하는 표시 장치.

- 제1항에 있어서, 상기 제1 화소 전극과 이에 인접하는 상기 제2 화소 전극들 사이에는 상기 하부 기판에 대해 수평한 전계가 생성되는 것을 특징으로 하는 표시 장치.

- 하부 기판 상에 스위칭 소자를 형성하는 단계;

상기 하부 기판 상에, 소자 영역에서 상기 스위칭 소자를 덮으며 화소 영역에서 단차부를 갖는 유기막 패턴을 형성하는 단계;

상기 화소 영역의 상기 유기막 패턴 상에 제1 화소 전극을 형성하는 단계;

상기 유기막 패턴 상에 상기 제1 화소 전극을 덮는 유전막을 형성하는 단계; 및

상기 유전막 상에 상기 제1 화소 전극과 부분적으로 중첩되는 제2 화소 전극을 형성하는 단계를 포함하는 표시 장치의 제조 방법. - 제15항에 있어서, 상기 화소 영역의 유기막 패턴은 파동의 구조 또는 톱니 구조로 형성되는 것을 특징으로 하는 표시 장치의 제조 방법.

- 제15항에 있어서, 상기 화소 영역의 유기막 패턴에는 라운드 형상의 리세스들, 라운드 형상의 덴트들, 경사진 측벽을 갖는 리세스들, 또는 경사진 측벽을 갖는 덴트들이 형성되는 것을 특징으로 하는 표시 장치의 제조 방법.

- 제17항에 있어서, 상기 제2 화소 전극들은 상기 라운드 형상의 리세스들, 라운드 형상의 덴트들, 경사진 측벽을 갖는 리세스들, 또는 경사진 측벽을 갖는 덴트들에 형성되는 것을 특징으로 하는 표시 장치의 제조 방법.

- 제16항에 있어서, 상기 유기막 패턴을 형성하는 단계는,

상기 하부 기판 상에 상기 스위칭 소자를 덮는 유기막을 형성하는 단계;

상기 유기막을 투과 영역 및 반투과 영역을 갖는 마스크를 사용하여 노광하는 단계; 및

상기 유기막의 노광된 부분을 부분적으로 제거하는 단계를 포함하는 것을 특징으로 하는 표시 장치의 제조 방법. - 제16항에 있어서, 상기 유기막 패턴을 형성하는 단계는,

상기 하부 기판 상에 상기 스위칭 소자를 덮는 유기막을 형성하는 단계; 및

건식 식각 공정을 통해 상기 화소 영역의 유기막을 부분적으로 식각하는 단계를 포함하는 것을 특징으로 하는 표시 장치의 제조 방법.

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020110042220A KR20120124527A (ko) | 2011-05-04 | 2011-05-04 | 표시 장치 및 표시 장치의 제조 방법 |

| US13/208,296 US8604484B2 (en) | 2011-05-04 | 2011-08-11 | Display devices and methods of manufacturing the display devices |

| JP2011177676A JP5791076B2 (ja) | 2011-05-04 | 2011-08-15 | 表示装置及び表示装置の製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020110042220A KR20120124527A (ko) | 2011-05-04 | 2011-05-04 | 표시 장치 및 표시 장치의 제조 방법 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20120124527A true KR20120124527A (ko) | 2012-11-14 |

Family

ID=47089648

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020110042220A KR20120124527A (ko) | 2011-05-04 | 2011-05-04 | 표시 장치 및 표시 장치의 제조 방법 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8604484B2 (ko) |

| JP (1) | JP5791076B2 (ko) |

| KR (1) | KR20120124527A (ko) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20160108660A (ko) * | 2015-03-04 | 2016-09-20 | 삼성디스플레이 주식회사 | 박막 트랜지스터 기판 및 그 제조 방법 |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102067122B1 (ko) * | 2012-01-10 | 2020-01-17 | 삼성디스플레이 주식회사 | 박막 트랜지스터 및 이의 제조 방법 |

| US9214533B2 (en) * | 2012-01-31 | 2015-12-15 | Sharp Kabushiki Kaisha | Semiconductor device having transparent electrodes |

| CN102709237B (zh) * | 2012-03-05 | 2014-06-25 | 京东方科技集团股份有限公司 | 薄膜场效应晶体管阵列基板及其制造方法、电子器件 |

| JP6051986B2 (ja) * | 2013-03-19 | 2016-12-27 | 三菱電機株式会社 | 液晶表示装置及びその製造方法 |

| CN103197480B (zh) * | 2013-03-22 | 2015-07-01 | 京东方科技集团股份有限公司 | 阵列基板及其制作方法、显示面板 |

| KR102081827B1 (ko) | 2013-07-02 | 2020-04-16 | 삼성디스플레이 주식회사 | 액정 표시 장치 |

| TWI559062B (zh) * | 2013-12-09 | 2016-11-21 | 友達光電股份有限公司 | 主動元件陣列基板 |

| TWI566020B (zh) * | 2014-07-08 | 2017-01-11 | 群創光電股份有限公司 | 顯示面板與顯示裝置 |

| KR102231630B1 (ko) * | 2014-10-07 | 2021-03-24 | 삼성디스플레이 주식회사 | 액정 표시 장치 |

| CN105068351B (zh) * | 2015-08-28 | 2018-01-09 | 武汉华星光电技术有限公司 | 蓝相液晶显示模组、蓝相液晶显示器及其制作方法 |

| CN105068325A (zh) * | 2015-08-31 | 2015-11-18 | 深圳市华星光电技术有限公司 | Psva型液晶显示面板 |

| US20170229554A1 (en) * | 2016-02-05 | 2017-08-10 | Applied Materials, Inc. | High-k dielectric materials utilized in display devices |

| US20180026055A1 (en) | 2016-07-19 | 2018-01-25 | Applied Materials, Inc. | Hybrid high-k dielectric material film stacks comprising zirconium oxide utilized in display devices |

| US11239258B2 (en) | 2016-07-19 | 2022-02-01 | Applied Materials, Inc. | High-k dielectric materials comprising zirconium oxide utilized in display devices |

| KR102328085B1 (ko) * | 2017-11-30 | 2021-11-17 | 엘지디스플레이 주식회사 | 전계발광 표시장치 |

| KR20200113079A (ko) | 2019-03-21 | 2020-10-06 | 삼성디스플레이 주식회사 | 표시 장치 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100260359B1 (ko) * | 1997-04-18 | 2000-07-01 | 김영환 | 액정 표시 장치 및 그 제조방법 |

| JP3892715B2 (ja) * | 2000-12-26 | 2007-03-14 | 株式会社東芝 | 液晶表示装置 |

| KR100798540B1 (ko) | 2001-12-31 | 2008-01-28 | 비오이 하이디스 테크놀로지 주식회사 | 프린지 필드 스위칭 액정표시장치의 제조방법 |

| KR100827856B1 (ko) | 2006-07-07 | 2008-05-07 | 비오이 하이디스 테크놀로지 주식회사 | 반투과형 프린지 필드 스위칭 모드 액정표시장치의어레이기판 및 그 제조방법 |

| JP4349461B2 (ja) * | 2007-04-17 | 2009-10-21 | エプソンイメージングデバイス株式会社 | 液晶表示装置 |

| JP5215617B2 (ja) * | 2007-09-04 | 2013-06-19 | 株式会社ジャパンディスプレイイースト | 液晶表示装置 |

-

2011

- 2011-05-04 KR KR1020110042220A patent/KR20120124527A/ko not_active Application Discontinuation

- 2011-08-11 US US13/208,296 patent/US8604484B2/en active Active

- 2011-08-15 JP JP2011177676A patent/JP5791076B2/ja active Active

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20160108660A (ko) * | 2015-03-04 | 2016-09-20 | 삼성디스플레이 주식회사 | 박막 트랜지스터 기판 및 그 제조 방법 |

| US10128278B2 (en) | 2015-03-04 | 2018-11-13 | Samsung Display Co., Ltd. | Thin film transistor substrate and method of manufacturing the same |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2012234140A (ja) | 2012-11-29 |

| US20120280236A1 (en) | 2012-11-08 |

| US8604484B2 (en) | 2013-12-10 |

| JP5791076B2 (ja) | 2015-10-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5791076B2 (ja) | 表示装置及び表示装置の製造方法 | |

| US8790941B2 (en) | Array substrate for fringe field switching mode liquid crystal display device and method of manufacturing the same | |

| TWI579624B (zh) | 邊緣電場切換型液晶顯示裝置用陣列基板及其製造方法 | |

| JP4916770B2 (ja) | 液晶表示装置、及びその製造方法 | |

| US7436474B2 (en) | Thin film transistor array panel and liquid crystal display including the panel | |

| US8450744B2 (en) | High light transmittance in-plane switching liquid crystal display device and method for manufacturing the same | |

| KR101981279B1 (ko) | 액정표시장치 및 그 제조방법 | |

| US9274388B2 (en) | Array substrate having common electrode driving interface pattern with slits, and manufacturing method thereof, and liquid crystal display | |

| US7652738B2 (en) | Array substrate for in-plane switching mode liquid crystal display device and method of manufacturing the same | |

| KR101423909B1 (ko) | 표시 기판 및 이를 구비하는 액정 표시 장치 | |

| KR20120075207A (ko) | 터치 패널 인 셀 방식의 액정표시장치용 어레이기판 및 그 제조방법 | |

| JP2004198845A (ja) | 液晶表示セルおよび液晶ディスプレイ | |

| KR100679100B1 (ko) | 수평 전계 인가형 액정 표시 패널 및 그 제조방법 | |

| KR20080048261A (ko) | 수평 전계 인가형 액정표시패널 및 그 제조방법 | |

| JP4916522B2 (ja) | 液晶表示装置 | |

| KR102218945B1 (ko) | 박막 트랜지스터 기판의 제조 방법 | |

| US20190187528A1 (en) | Liquid crystal display device | |

| KR101260666B1 (ko) | 박막 트랜지스터 기판과 그 제조방법 및 액정 표시장치와 그 제조방법 | |

| KR101668993B1 (ko) | 횡전계 방식 액정표시장치 | |

| KR101055201B1 (ko) | Cot형 액정표시소자의 제조방법 | |

| KR101915223B1 (ko) | 에이에이치-아이피에스 방식 액정표시장치용 어레이기판 및 그 제조방법 | |

| JP4928646B2 (ja) | 液晶表示装置、及びその製造方法 | |

| JP5318269B2 (ja) | 液晶表示装置 | |

| JP5507738B2 (ja) | 液晶表示装置 | |

| KR101374107B1 (ko) | 반사투과형 액정표시장치 및 그 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| N231 | Notification of change of applicant | ||

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E601 | Decision to refuse application |