KR20080098680A - 반도체 장치 및 그 제조 방법 - Google Patents

반도체 장치 및 그 제조 방법 Download PDFInfo

- Publication number

- KR20080098680A KR20080098680A KR1020087023778A KR20087023778A KR20080098680A KR 20080098680 A KR20080098680 A KR 20080098680A KR 1020087023778 A KR1020087023778 A KR 1020087023778A KR 20087023778 A KR20087023778 A KR 20087023778A KR 20080098680 A KR20080098680 A KR 20080098680A

- Authority

- KR

- South Korea

- Prior art keywords

- film

- dielectric film

- electrode layer

- ferroelectric

- semiconductor device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D1/00—Resistors, capacitors or inductors

- H10D1/60—Capacitors

- H10D1/68—Capacitors having no potential barriers

- H10D1/692—Electrodes

- H10D1/694—Electrodes comprising noble metals or noble metal oxides

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B53/00—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory capacitors

- H10B53/30—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory capacitors characterised by the memory core region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B53/00—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory capacitors

- H10B53/40—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory capacitors characterised by the peripheral circuit region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D1/00—Resistors, capacitors or inductors

- H10D1/60—Capacitors

- H10D1/68—Capacitors having no potential barriers

- H10D1/682—Capacitors having no potential barriers having dielectrics comprising perovskite structures

- H10D1/684—Capacitors having no potential barriers having dielectrics comprising perovskite structures the dielectrics comprising multiple layers, e.g. comprising buffer layers, seed layers or gradient layers

Landscapes

- Semiconductor Memories (AREA)

- Semiconductor Integrated Circuits (AREA)

Abstract

Description

Claims (27)

- 반도체 기판과,상기 반도체 기판의 상방에 형성되어 있으며, 유전체 재료로 이루어지는 커패시터막을 하부 전극과 상부 전극에 의해 협지하여 이루어지는 커패시터 구조를 포함하고,상기 커패시터막은 그 내부에 이리듐을 함유하고 있으며, 상층 영역에서 하층 영역으로 향할수록 이리듐 농도가 낮아지는 이리듐 농도 분포를 갖는 것을 특징으로 하는 반도체 장치.

- 제1항에 있어서, 상기 커패시터막에서 상기 상층 영역은 균일한 높은 이리듐 농도이며, 상기 하층 영역은 하방으로 향할수록 이리듐 농도가 낮아지는 것을 특징으로 하는 반도체 장치.

- 제2항에 있어서, 상기 상층 영역의 이리듐 함유량은 0.01 ㏖% 이상 3.00 ㏖% 이하의 범위의 값인 것을 특징으로 하는 반도체 장치.

- 제1항에 있어서, 상기 커패시터막은 강유전체 재료로 이루어지는 것을 특징으로 하는 반도체 장치.

- 제4항에 있어서, 상기 상층 영역은 A사이트 및 B사이트 중 적어도 한쪽에 Ir 원소를 포함하는 ABO3형 페로브스카이트 구조(A=Bi, Pb, Ba, Sr, Ca, Na, K 및 희토류 원소에서 선택된 적어도 1종, B=Ti, Zr, Nb, Ta, W, Mn, Fe, Co, Cr에서 선택된 적어도 1종)의 강유전체 재료로 이루어지는 것을 특징으로 하는 반도체 장치.

- 제5항에 있어서, 상기 상층 영역은 PZT, La, Ca, Sr 및 Si에서 선택된 적어도 1종이 도핑된 PZT, PLZT, BLT, SBT 및 Bi 층형 구조에서 선택된 1종으로 이루어지는 것을 특징으로 하는 반도체 장치.

- 제5항에 있어서, 상기 하층 영역은 A사이트 및 B사이트 중 적어도 한쪽에 Ir 원소를 포함하는 ABO3형 페로브스카이트 구조(A=Bi, Pb, Ba, Sr, Ca, Na, K 및 희토류 원소에서 선택된 적어도 1종, B=Ti, Zr, Nb, Ta, W, Mn, Fe, Co, Cr에서 선택된 적어도 1종)의 강유전체 재료로 이루어지는 것을 특징으로 하는 반도체 장치.

- 제7항에 있어서, 상기 하층 영역은 PZT, La, Ca, Sr 및 Si에서 선택된 적어도 1종이 도핑된 PZT, PLZT, BLT, SBT 및 Bi 층형 구조에서 선택된 1종으로 이루어지는 것을 특징으로 하는 반도체 장치.

- 제1항에 있어서, 상기 상부 전극은 복수층 구조로 되어 있으며, 최하층의 조 성이 IrOx(0<x<2)인 것을 특징으로 하는 반도체 장치.

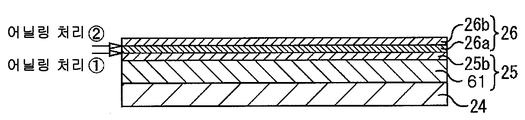

- 반도체 기판의 상방에, 유전체 재료로 이루어지는 커패시터막을 하부 전극과 상부 전극에 의해 협지하여 이루어지는 커패시터 구조를 구비한 반도체 장치의 제조 방법으로서,상기 커패시터 구조를 형성하는데 있어서,하부 전극층을 형성하는 공정과,상기 하부 전극층 상에 제1 유전체막을 형성하는 공정과,상기 제1 유전체막 상에, 내부에 이리듐을 함유하는 아몰퍼스형의 제2 유전체막을 형성하는 공정과,산화성 분위기에서 상기 제2 유전체막을 열처리하여, 상기 제2 유전체막을 결정화하고, 상기 제2 유전체막 내의 이리듐을 상기 제1 유전체막의 내부에 확산시키는 공정과,상기 제2 유전체막 상에 상부 전극층을 형성하는 공정과,상기 상부 전극층, 상기 제2 유전체막, 상기 제1 유전체막 및 상기 하부 전극층을 각각 가공하여, 상기 커패시터 구조를 형성하는 공정을 포함하는 것을 특징으로 하는 반도체 장치의 제조 방법.

- 제10항에 있어서, 상기 제1 유전체막을 아몰퍼스형으로 형성하며, 상기 제2 유전체막의 열처리에 의해, 상기 제2 유전체막과 함께 상기 제1 유전체막을 결정화시키는 것을 특징으로 하는 반도체 장치의 제조 방법.

- 제10항에 있어서, 상기 제1 유전체막을 아몰퍼스형으로 형성하며,상기 제2 유전체막을 형성하기 전에, 산화성 분위기에서 상기 제1 유전체막을 열처리하여 상기 제1 유전체막을 결정화시키는 공정을 더 포함하는 것을 특징으로 하는 반도체 장치의 제조 방법.

- 제10항에 있어서, 상기 제2 유전체막을 형성한 후에, 상기 상부 전극층을 형성하며, 상기 상부 전극층이 형성된 상태에서 상기 제2 유전체막의 열처리를 수행하는 것을 특징으로 하는 반도체 장치의 제조 방법.

- 제13항에 있어서, 상기 제1 유전체막을 아몰퍼스형으로 형성하며, 상기 제2 유전체막의 열처리에 의해, 상기 제2 유전체막과 함께 상기 제1 유전체막을 결정화시키는 것을 특징으로 하는 반도체 장치의 제조 방법.

- 제10항에 있어서, 상기 상부 전극층을 형성한 후, 상기 상부 전극층이 형성된 상태에서, 재차 상기 제2 유전체막의 열처리를 수행하는 것을 특징으로 하는 반도체 장치의 제조 방법.

- 제10항에 있어서, 상기 제2 유전체막의 이리듐 함유량은 0.01 ㏖% 이상 3.00 ㏖% 이하의 범위의 값인 것을 특징으로 하는 반도체 장치의 제조 방법.

- 제10항에 있어서, 상기 커패시터막은 강유전체 재료로 이루어지는 것을 특징으로 하는 반도체 장치의 제조 방법.

- 제17항에 있어서, 상기 제2 유전체막은 A사이트 및 B사이트 중 적어도 한쪽에 Ir 원소를 포함하는 ABO3형 페로브스카이트 구조(A=Bi, Pb, Ba, Sr, Ca, Na, K 및 희토류 원소에서 선택된 적어도 1종, B=Ti, Zr, Nb, Ta, W, Mn, Fe, Co, Cr에서 선택된 적어도 1종)의 강유전체 재료로 이루어지는 것을 특징으로 하는 반도체 장치의 제조 방법.

- 제18항에 있어서, 상기 제2 유전체막은 PZT, La, Ca, Sr 및 Si에서 선택된 적어도 1종이 도핑된 PZT, PLZT, BLT, SBT 및 Bi 층형 구조에서 선택된 1종으로 이루어지는 것을 특징으로 하는 반도체 장치의 제조 방법.

- 제18항에 있어서, 상기 제1 유전체막은 ABO3형 페로브스카이트 구조(A=Bi, Pb, Ba, Sr, Ca, Na, K 및 희토류 원소에서 선택된 적어도 1종, B=Ti, Zr, Nb, Ta, W, Mn, Fe, Co, Cr에서 선택된 적어도 1종)의 강유전체 재료로 이루어지는 것을 특 징으로 하는 반도체 장치의 제조 방법.

- 제20항에 있어서, 상기 제1 유전체막은 PZT, La, Ca, Sr 및 Si에서 선택된 적어도 1종이 도핑된 PZT, PLZT, BLT, SBT 및 Bi 층형 구조에서 선택된 1종으로 이루어지는 것을 특징으로 하는 반도체 장치의 제조 방법.

- 반도체 기판의 상방에, 유전체 재료로 이루어지는 커패시터막을 하부 전극과 상부 전극에 의해 협지하여 이루어지는 커패시터 구조를 구비한 반도체 장치의 제조 방법으로서,상기 커패시터 구조를 형성하는데 있어서,하부 전극층을 형성하는 공정과,상기 하부 전극층 상에 아몰퍼스형의 유전체막을 형성하는 공정과,산화성 분위기에서 상기 유전체막에 제1 열처리를 시행하여, 상기 유전체막을 결정화하는 공정과,상기 유전체막 상에, 내부에 이리듐을 함유하는 상부 전극층을 형성하는 공정과,산화성 분위기에서 상기 상부 전극층에 제2 열처리를 시행하여, 상기 상부 전극층 내의 이리듐을 상기 유전체막의 내부에 확산시키는 공정과,상기 상부 전극층, 상기 유전체막 및 상기 하부 전극층을 각각 가공하여, 상기 커패시터 구조를 형성하는 공정을 포함하는 것을 특징으로 하는 반도체 장치의 제조 방법.

- 제22항에 있어서, 상기 상부 전극층을 복수층 구조로 하며,상기 유전체막 상에, IrOx(0<x<2)의 조성으로 상기 상부 전극층의 최하층을 형성하고,상기 최하층에 상기 제2 열처리를 시행하여, 상기 최하층 내의 이리듐을 상기 유전체막의 내부에 확산시킨 후,상기 최하층 상에 상기 상부 전극층의 나머지 층을 형성하여, 상기 상부 전극층을 완성시키는 것을 특징으로 하는 반도체 장치의 제조 방법.

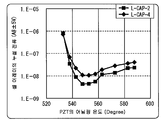

- 제22항에 있어서, 상기 제2 열처리를 548℃ 이상 558℃의 범위 내의 처리 온도에서 행하는 것을 특징으로 하는 반도체 장치의 제조 방법.

- 제22항에 있어서, 상기 유전체막은 강유전체 재료로 이루어지는 것을 특징으로 하는 반도체 장치의 제조 방법.

- 제25항에 있어서, 상기 유전체막은 ABO3형 페로브스카이트 구조(A=Bi, Pb, Ba, Sr, Ca, Na, K 및 희토류 원소에서 선택된 적어도 1종, B=Ti, Zr, Nb, Ta, W, Mn, Fe, Co, Cr에서 선택된 적어도 1종)의 강유전체 재료로 이루어지는 것을 특징 으로 하는 반도체 장치의 제조 방법.

- 제26항에 있어서, 상기 유전체막은 PZT, La, Ca, Sr 및 Si에서 선택된 적어도 1종이 도핑된 PZT, PLZT, BLT, SBT 및 Bi 층형 구조에서 선택된 1종으로 이루어지는 것을 특징으로 하는 반도체 장치의 제조 방법.

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| PCT/JP2006/306654 WO2007116442A1 (ja) | 2006-03-30 | 2006-03-30 | 半導体装置及びその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20080098680A true KR20080098680A (ko) | 2008-11-11 |

| KR101101566B1 KR101101566B1 (ko) | 2012-01-02 |

Family

ID=38580751

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020087023778A Expired - Fee Related KR101101566B1 (ko) | 2006-03-30 | 2006-03-30 | 반도체 장치 및 그 제조 방법 |

Country Status (4)

| Country | Link |

|---|---|

| US (3) | US7964904B2 (ko) |

| JP (1) | JP4998461B2 (ko) |

| KR (1) | KR101101566B1 (ko) |

| WO (1) | WO2007116442A1 (ko) |

Families Citing this family (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4601896B2 (ja) * | 2002-10-30 | 2010-12-22 | 富士通セミコンダクター株式会社 | 半導体装置及びその製造方法 |

| JP5196106B2 (ja) * | 2007-03-28 | 2013-05-15 | セイコーエプソン株式会社 | 圧電素子の製造方法 |

| JP5119058B2 (ja) * | 2008-06-19 | 2013-01-16 | 太陽誘電株式会社 | 薄膜キャパシタ |

| JP5600916B2 (ja) * | 2009-09-30 | 2014-10-08 | 富士通セミコンダクター株式会社 | 強誘電体キャパシタの製造方法 |

| JP5610134B2 (ja) * | 2010-05-07 | 2014-10-22 | セイコーエプソン株式会社 | 液体噴射ヘッド、液体噴射装置、及び圧電素子 |

| US8450168B2 (en) * | 2010-06-25 | 2013-05-28 | International Business Machines Corporation | Ferro-electric capacitor modules, methods of manufacture and design structures |

| JP2012074479A (ja) * | 2010-09-28 | 2012-04-12 | Fujitsu Semiconductor Ltd | 半導体装置の製造方法 |

| WO2012063642A1 (ja) * | 2010-11-10 | 2012-05-18 | コニカミノルタホールディングス株式会社 | 強誘電体薄膜、強誘電体薄膜の製造方法、圧電体素子の製造方法 |

| JP2013012681A (ja) * | 2011-06-30 | 2013-01-17 | Toshiba Corp | 磁気抵抗効果素子及びその製造方法 |

| JP5489009B2 (ja) * | 2011-11-18 | 2014-05-14 | 独立行政法人科学技術振興機構 | 積層構造体、強誘電体ゲート薄膜トランジスター及び強誘電体薄膜キャパシター |

| JP5747849B2 (ja) | 2012-03-26 | 2015-07-15 | 東レ株式会社 | ゲートバルブおよびゲートバルブの製造方法 |

| JP5994466B2 (ja) * | 2012-08-06 | 2016-09-21 | 富士通セミコンダクター株式会社 | 半導体装置とその製造方法 |

| KR102125746B1 (ko) * | 2013-07-25 | 2020-06-23 | 고쿠리츠켄큐카이하츠호진 상교기쥬츠 소고켄큐쇼 | 강유전체 디바이스 및 그 제조방법 |

| US9219225B2 (en) * | 2013-10-31 | 2015-12-22 | Micron Technology, Inc. | Multi-bit ferroelectric memory device and methods of forming the same |

| CN104474571A (zh) * | 2014-11-19 | 2015-04-01 | 重庆联佰博超医疗器械有限公司 | 一种淀粉复合多糖止血粉及其制备方法 |

| US10093586B2 (en) | 2015-02-26 | 2018-10-09 | General Electric Company | Ceramic matrix composite articles and methods for forming same |

| JP2015213197A (ja) * | 2015-08-10 | 2015-11-26 | 富士通セミコンダクター株式会社 | 半導体装置の製造方法 |

| JP6751866B2 (ja) | 2016-04-22 | 2020-09-09 | 国立研究開発法人産業技術総合研究所 | 半導体強誘電体記憶素子の製造方法及び半導体強誘電体記憶トランジスタ |

| US11121139B2 (en) * | 2017-11-16 | 2021-09-14 | International Business Machines Corporation | Hafnium oxide and zirconium oxide based ferroelectric devices with textured iridium bottom electrodes |

| KR101948481B1 (ko) | 2018-04-04 | 2019-02-14 | 한국과학기술원 | 단일 사건 현상과 누적 이온화 현상에 강인한 내방사선 입체 단위 모스펫 |

| US12382640B2 (en) | 2020-10-30 | 2025-08-05 | Taiwan Semiconductor Manufacturing Company, Ltd. | Memory device and method for fabricating the same |

| US11706928B2 (en) | 2020-10-30 | 2023-07-18 | Taiwan Semiconductor Manufacturing Company, Ltd. | Memory device and method for fabricating the same |

| US11706927B2 (en) | 2021-03-02 | 2023-07-18 | Micron Technology, Inc. | Memory devices and methods of forming memory devices |

| US12557307B2 (en) * | 2021-07-09 | 2026-02-17 | Taiwan Semiconductor Manufacturing Company, Ltd. | Metal-insulator-metal (MIM) capacitor with a top electrode having an oxygen-enriched portion |

| US11695072B2 (en) | 2021-07-09 | 2023-07-04 | Micron Technology, Inc. | Integrated assemblies and methods of forming integrated assemblies |

| US12035536B2 (en) | 2021-07-19 | 2024-07-09 | Micron Technology, Inc. | Integrated assemblies and methods of forming integrated assemblies |

| US11917834B2 (en) * | 2021-07-20 | 2024-02-27 | Micron Technology, Inc. | Integrated assemblies and methods of forming integrated assemblies |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3517876B2 (ja) * | 1998-10-14 | 2004-04-12 | セイコーエプソン株式会社 | 強誘電体薄膜素子の製造方法、インクジェット式記録ヘッド及びインクジェットプリンタ |

| EP1153424A1 (de) * | 1998-12-23 | 2001-11-14 | Infineon Technologies AG | Kondensatorelektrodenanordnung |

| US6316797B1 (en) * | 1999-02-19 | 2001-11-13 | Advanced Technology Materials, Inc. | Scalable lead zirconium titanate(PZT) thin film material and deposition method, and ferroelectric memory device structures comprising such thin film material |

| US6660631B1 (en) * | 2000-08-31 | 2003-12-09 | Micron Technology, Inc. | Devices containing platinum-iridium films and methods of preparing such films and devices |

| US20020117700A1 (en) * | 2001-02-28 | 2002-08-29 | Glex Fox | Amorphous iridium oxide barrier layer and electrodes in ferroelectric capacitors |

| TW564550B (en) * | 2001-06-05 | 2003-12-01 | Hitachi Ltd | Semiconductor device |

| JP2003068991A (ja) * | 2001-08-23 | 2003-03-07 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| JP2003128419A (ja) * | 2001-10-22 | 2003-05-08 | Jsr Corp | 強誘電体薄膜形成用塗布液および強誘電体薄膜 |

| US6635497B2 (en) * | 2001-12-21 | 2003-10-21 | Texas Instruments Incorporated | Methods of preventing reduction of IrOx during PZT formation by metalorganic chemical vapor deposition or other processing |

| JP2004079675A (ja) * | 2002-08-13 | 2004-03-11 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| US7473949B2 (en) * | 2002-12-10 | 2009-01-06 | Fujitsu Limited | Ferroelectric capacitor and method of manufacturing the same |

| WO2004053991A1 (ja) * | 2002-12-10 | 2004-06-24 | Fujitsu Limited | 強誘電体キャパシタ及びその製造方法 |

| JP2005183841A (ja) * | 2003-12-22 | 2005-07-07 | Fujitsu Ltd | 半導体装置の製造方法 |

| JP2006313833A (ja) * | 2005-05-09 | 2006-11-16 | Seiko Epson Corp | 強誘電体キャパシタの形成方法、強誘電体キャパシタおよび電子デバイス |

| JP2006344684A (ja) * | 2005-06-07 | 2006-12-21 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| JP2006344783A (ja) * | 2005-06-09 | 2006-12-21 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| KR20090017758A (ko) * | 2007-08-16 | 2009-02-19 | 삼성전자주식회사 | 강유전체 커패시터의 형성 방법 및 이를 이용한 반도체장치의 제조 방법 |

| US7709359B2 (en) * | 2007-09-05 | 2010-05-04 | Qimonda Ag | Integrated circuit with dielectric layer |

| JP4479770B2 (ja) * | 2007-09-14 | 2010-06-09 | セイコーエプソン株式会社 | 強誘電体メモリの製造方法 |

-

2006

- 2006-03-30 JP JP2008509594A patent/JP4998461B2/ja not_active Expired - Fee Related

- 2006-03-30 KR KR1020087023778A patent/KR101101566B1/ko not_active Expired - Fee Related

- 2006-03-30 WO PCT/JP2006/306654 patent/WO2007116442A1/ja not_active Ceased

-

2008

- 2008-09-26 US US12/239,332 patent/US7964904B2/en not_active Expired - Fee Related

-

2011

- 2011-05-16 US US13/108,230 patent/US8357585B2/en not_active Expired - Fee Related

-

2012

- 2012-12-16 US US13/716,177 patent/US8497181B1/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US7964904B2 (en) | 2011-06-21 |

| US20110217792A1 (en) | 2011-09-08 |

| US20090020797A1 (en) | 2009-01-22 |

| WO2007116442A1 (ja) | 2007-10-18 |

| US8497181B1 (en) | 2013-07-30 |

| JPWO2007116442A1 (ja) | 2009-08-20 |

| US8357585B2 (en) | 2013-01-22 |

| KR101101566B1 (ko) | 2012-01-02 |

| US20130178038A1 (en) | 2013-07-11 |

| JP4998461B2 (ja) | 2012-08-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101101566B1 (ko) | 반도체 장치 및 그 제조 방법 | |

| US7405121B2 (en) | Semiconductor device with capacitors and its manufacture method | |

| JP5668303B2 (ja) | 半導体装置及びその製造方法 | |

| US8236643B2 (en) | Method of manufacturing semiconductor device including ferroelectric capacitor | |

| US8278181B2 (en) | Semiconductor device and method of manufacturing the same | |

| US7927890B2 (en) | Method of manufacturing a semiconductor device | |

| US20070275484A1 (en) | Ferroelectric memory and method for manufacturing the same | |

| JP2009117768A (ja) | 半導体記憶装置およびその製造方法 | |

| JP5347381B2 (ja) | 半導体装置の製造方法 | |

| US8962347B2 (en) | Semiconductor device and method of manufacturing the same | |

| US7407862B2 (en) | Method for manufacturing ferroelectric memory device | |

| US20070228431A1 (en) | Semiconductor device and its manufacturing method | |

| JP5561300B2 (ja) | 半導体装置の製造方法 | |

| JP5412754B2 (ja) | 半導体装置及び半導体装置の製造方法 | |

| JP2004153006A (ja) | 容量素子の製造方法 | |

| US7419837B2 (en) | Method of manufacturing semiconductor device | |

| US20070158715A1 (en) | Ferroelectric capacitor and method for fabricating the same | |

| JP5338800B2 (ja) | 半導体装置の製造方法 | |

| JPH10200072A (ja) | 半導体メモリセルのキャパシタ構造及びその作製方法 | |

| KR20070007073A (ko) | 반도체 장치의 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0105 | International application |

St.27 status event code: A-0-1-A10-A15-nap-PA0105 |

|

| A201 | Request for examination | ||

| E13-X000 | Pre-grant limitation requested |

St.27 status event code: A-2-3-E10-E13-lim-X000 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| PA0201 | Request for examination |

St.27 status event code: A-1-2-D10-D11-exm-PA0201 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| N231 | Notification of change of applicant | ||

| PN2301 | Change of applicant |

St.27 status event code: A-3-3-R10-R13-asn-PN2301 St.27 status event code: A-3-3-R10-R11-asn-PN2301 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-3-3-R10-R18-oth-X000 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-3-3-R10-R13-asn-PN2301 St.27 status event code: A-3-3-R10-R11-asn-PN2301 |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

St.27 status event code: A-1-2-D10-D21-exm-PE0902 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

St.27 status event code: A-1-2-D10-D21-exm-PE0902 |

|

| T11-X000 | Administrative time limit extension requested |

St.27 status event code: U-3-3-T10-T11-oth-X000 |

|

| E13-X000 | Pre-grant limitation requested |

St.27 status event code: A-2-3-E10-E13-lim-X000 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

St.27 status event code: A-1-2-D10-D22-exm-PE0701 |

|

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment |

St.27 status event code: A-2-4-F10-F11-exm-PR0701 |

|

| PR1002 | Payment of registration fee |

St.27 status event code: A-2-2-U10-U12-oth-PR1002 Fee payment year number: 1 |

|

| PG1601 | Publication of registration |

St.27 status event code: A-4-4-Q10-Q13-nap-PG1601 |

|

| FPAY | Annual fee payment |

Payment date: 20141205 Year of fee payment: 4 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 4 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-5-5-R10-R18-oth-X000 |

|

| FPAY | Annual fee payment |

Payment date: 20151201 Year of fee payment: 5 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 5 |

|

| FPAY | Annual fee payment |

Payment date: 20161129 Year of fee payment: 6 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 6 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 7 |

|

| FPAY | Annual fee payment |

Payment date: 20181129 Year of fee payment: 8 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 8 |

|

| FPAY | Annual fee payment |

Payment date: 20191127 Year of fee payment: 9 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 9 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R11-asn-PN2301 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R14-asn-PN2301 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 10 |

|

| PC1903 | Unpaid annual fee |

St.27 status event code: A-4-4-U10-U13-oth-PC1903 Not in force date: 20211227 Payment event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE |

|

| PC1903 | Unpaid annual fee |

St.27 status event code: N-4-6-H10-H13-oth-PC1903 Ip right cessation event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE Not in force date: 20211227 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |