KR101447176B1 - 선택적으로 증착된 가역 저항-스위칭 소자를 사용하는 메모리 셀과 상기 메모리 셀을 형성하는 방법 - Google Patents

선택적으로 증착된 가역 저항-스위칭 소자를 사용하는 메모리 셀과 상기 메모리 셀을 형성하는 방법 Download PDFInfo

- Publication number

- KR101447176B1 KR101447176B1 KR1020097027303A KR20097027303A KR101447176B1 KR 101447176 B1 KR101447176 B1 KR 101447176B1 KR 1020097027303 A KR1020097027303 A KR 1020097027303A KR 20097027303 A KR20097027303 A KR 20097027303A KR 101447176 B1 KR101447176 B1 KR 101447176B1

- Authority

- KR

- South Korea

- Prior art keywords

- forming

- delete delete

- memory cell

- switching element

- diode

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body

- H01L27/10—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including a plurality of individual components in a repetitive configuration

- H01L27/101—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including a plurality of individual components in a repetitive configuration including resistors or capacitors only

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B53/00—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory capacitors

- H10B53/20—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory capacitors characterised by the three-dimensional arrangements, e.g. with cells on different height levels

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B63/00—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices

- H10B63/20—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices comprising selection components having two electrodes, e.g. diodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B63/00—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices

- H10B63/30—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices comprising selection components having three or more electrodes, e.g. transistors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B63/00—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices

- H10B63/80—Arrangements comprising multiple bistable or multi-stable switching components of the same type on a plane parallel to the substrate, e.g. cross-point arrays

- H10B63/84—Arrangements comprising multiple bistable or multi-stable switching components of the same type on a plane parallel to the substrate, e.g. cross-point arrays arranged in a direction perpendicular to the substrate, e.g. 3D cell arrays

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices without a potential-jump barrier or surface barrier, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/011—Manufacture or treatment of multistable switching devices

- H10N70/021—Formation of the switching material, e.g. layer deposition

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices without a potential-jump barrier or surface barrier, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/20—Multistable switching devices, e.g. memristors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices without a potential-jump barrier or surface barrier, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/821—Device geometry

- H10N70/826—Device geometry adapted for essentially vertical current flow, e.g. sandwich or pillar type devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices without a potential-jump barrier or surface barrier, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/881—Switching materials

- H10N70/883—Oxides or nitrides

- H10N70/8833—Binary metal oxides, e.g. TaOx

Abstract

몇몇 실시예에서, (1) 기판 위에 제 1 전도체를 형성하는 단계; (2) 상기 제 1 전도체 위에 다이오드를 형성하는 단계; (3) 선택적인 증착 프로세스를 이용해 상기 제 1 전도체 위에 가역 저항-스위칭 소자를 형성하는 단계; 그리고 (4) 상기 다이오드와 상기 가역 저항 스위칭 소자 위에 제 2 전도체를 형성하는 단계를 포함하는 메모리 셀을 형성하는 방법이 제공된다. 수많은 다른 실시예가 제공된다.

Description

본 출원은, "MEMORY CELL THAT EMPLOYS A SELECTIVELY GROWN REVERSIBLE RESISTANCE-SWITCHING ELEMENT AND METHODS OF FORMING THE SAME"이란 제목의 2007년 6월 29일 출원된 미합중국 특허출원 일련번호 제 11/772,090호(Docket No. MXD-333X)의 우선권을 주장하고, "MEMORY CELL THAT EMPLOYS A SELECTIVELY DEPOSITED REVERSIBLE RESISTANCE-SWITCHING ELEMENT AND METHODS OF FORMING THE SAME"이란 제목의 2007년 6월 29일 출원된 미합중국 특허출원 일련번호 제 11/772,084호(Docket No. MXD-333Y)의 우선권을 주장하며, 이들 모두는 본 명세서에 그 전체 기재 내용이 참조로 포함되어 있다.

관련 출원에 대한 상호 참조

본 출원은 다음의 특허 출원에 관련되며, 이들 각각은 그대로 본 명세서에 참조로서 인용된다:.

"METHOD TO FORM A REWRITEABLE MEMORY CELL COMPRISING A DIODE AND A RESISTIVITY -SWITCHING GROWN OXIDE"이란 제목의 2007년 6월 29일 출원된 미합중국 특허출원 일련번호 제 11/772,081호(Docket No. MD-304X).

"MEMORY CELL THAT EMPLOYS A SELECTIVELY GROWN REVERSIBLE RESISTANCE-SWITCHING ELEMENT AND METHODS OF FORMING THE SAME"이란 제목의 2007년 6월 29일 출원된 미합중국 특허출원 일련번호 제 11/772,082호(Attorney Docket No. SD-MXD-0335X).

"MEMORY CELL THAT EMPLOYS A SELECTIVELY GROWN REVERSIBLE RESISTANCE-SWITCHING ELEMENT AND METHODS OF FORMING THE SAME"이란 제목의 2007년 6월 29일 출원된 미합중국 특허출원 일련번호 제 11/772,088호(Attorney Docket No. SD-MXD-0335Y).

본 발명은, 비휘발성 메모리(non-volatile memory)에 관한 것이고, 보다 구체적으로는 선택적으로 성장한 가역 저항-스위칭 소자(slectively grown reversible resistance-switching element)를 사용하는 메모리 셀(memory cell)과 상기 메모리 셀을 형성하는 방법에 관한 것이다.

가역 저항-스위칭 소자(reversible resistance-switching element)로부터 형성된 비휘발성 메모리가 알려져 있다. 예를 들어, 본 명세서에 그대로 참조로서 인용된 "REWRITEABLE MEMORY CELL COMPRISING A DIODE AND A RESISTANCE -SWITCHING MATERIAL"이란 제목의 2005년 5월 9일 출원된 미합중국 출원 일련번호 제 11/125,939호(이하, '939 출원)는 메탈 산화물 또는 메탈 질화물과 같은 가역 저항률-스위칭 재료에 의해 직렬로 결합한 다이오드를 포함하는 재기록 가능한 비휘발성 메모리 셀을 기술한다.

그러나, 재기록 가능한 저항률-스위칭 재료(rewriteable resistivity-switching element)로 메모리 디바이스를 제조하는 것은 어려우며, 가역 저항률-스위칭 재료를 사용하는 메모리 디바이스를 형성하는 개선된 방법이 바람직하다.

본 발명의 제 1 양상에서, (1) 기판 위에 스티어링 소자(steering element)를 형성하는 단계; 그리고 (2) 선택 성장 공정을 이용하여 상기 스티어링 소자에 결합된 가역 저항-스위칭 소자를 형성하는 단계를 포함하는 메모리 셀을 형성하는 방법이 제공된다.

본 발명의 제 2 양상에서, (1) 기판 위에 제 1 전도체(first conductor)를 형성하는 단계; (2) 선택 성장 공정을 이용하여 상기 제 1 전도체 위에 가역 저항-스위칭 소자를 형성하는 단계; (3) 상기 제 1 전도체 위에 다이오드를 형성하는 단계; 그리고 (4) 상기 다이오드 및 상기 가역 저항-스위칭 소자 위에 제 2 전도체를 형성하는 단계를 포함하는 메모리 셀을 형성하는 방법이 제공된다.

본 발명의 제 3 양상에서, (1) 기판 위에 제 1 전도체(first conductor)를 형성하는 단계; (2) 상기 제 1 전도체 위에 티타늄 질화물 층(titanium nitride layer)을 형성하는 단계; (3) 상기 티타늄 질화물 층을 산화시킴으로써 가역 저항-스위칭 소자를 선택적으로 형성하는 단계; (4) 상기 가역 저항-스위칭 소자 위에 수직 다결정 다이오드(vertical polycrystalline diode)를 형성하는 단계; 그리고 (5) 상기 수직 다결정 다이오드 위에 제 2 전도체를 형성하는 단계를 포함하는 메모리 셀을 형성하는 방법이 제공된다.

본 발명의 제 4 양상에서, (1) 소스 영역(source region)과 드레인 영역(drain region)을 갖는 박막 트랜지스터(thin film transistor)를 형성하는 단계; (2) 상기 트랜지스터의 상기 소스 영역 또는 상기 드레인 영역에 결합된 제 1 전도체를 형성하는 단계; (3) 상기 제 1 전도체 위에 티타늄 질화물 층을 형성하는 단계; (4) 상기 티타늄 질화물 층을 산화시킴으로써 가역 저항-스위칭 소자를 선택적으로 형성하는 단계; 그리고 (5) 상기 가역 저항-스위칭 소자 위에 제 2 전도체를 형성하는 단계를 포함하는 메모리 셀을 형성하는 방법이 제공된다.

본 발명의 제 5 양상에서, (1) 스티어링 소자; 그리고 (2)상기 스티어링 소자에 결합되고 선택 성장 공정을 이용해 형성된 가역 저항-스위칭 소자를 포함하는 메모리 셀이 제공된다.

본 발명의 제 6 양상에서, (1) 제 1 전도체; (2)상기 제 1 전도체 위에 형성된 제 2 전도체; (3) 상기 제 1 및 제 2 전도체 사이에 형성된 다이오드; 그리고 (4) 선택 성장 공정을 이용해 상기 제 1 및 제 2 전도체 사이에 형성된 가역 저항-스위칭 소자를 포함하는 메모리 셀이 제공된다.

본 발명의 제 7 양상에서, (1) 제 1 전도체; (2)상기 제 1 전도체 위에 형성된 수직 다결정 다이오드; (3) 상기 수직 다결정 다이오드 위에 선택적으로 형성된 니켈 산화물 층을 포함한 가역 저항-스위칭 소자; 그리고 (4) 상기 수직 다결정 다이오드 위에 형성된 제 2 전도체를 포함하는 메모리 셀이 제공된다.

본 발명의 제 8 양상에서, (1) 소스 영역 및 드레인 영역을 갖는 박막 트랜지스터; (2) 상기 소스 영역 또는 상기 드레인 영역에 결합된 제 1 전도체; (3) 상기 제 1 전도체 위에 선택적으로 형성된 니켈 산화물 층을 포함한 가역 저항-스위칭 소자; 그리고 (5) 상기 가역 저항-스위칭 소자 위에 형성된 제 2 전도체를 포함하는 메모리 셀이 제공된다.

본 발명의 제 9 양상에서, (1) 제 1 방향으로 연장된 실질적으로 평행이고, 실질적으로 동일 평면인 복수의 제 1 전도체; (2) 복수의 다이오드; (3) 복수의 가역 저항-스위칭 소자; 그리고 (4) 상기 제 1 방향과 다른 제 2 방향으로 연장된 실질적으로 평행이고, 실질적으로 동일 평면인 복수의 제 2 전도체를 포함하는 복수의 비휘발성 메모리 셀이 제공된다. 각각의 메모리 셀에서, 다이오드 중 하나와 가역 저항-스위칭 소자 중 하나가 직렬로 배치되고, 상기 제 1 전도체중 하나와 상기 제 2 전도체 중 하나 사이에 배치된다. 각각의 가역 저항-스위칭 소자가 선택 성장 공정을 이용해 형성된다. 더욱이, 각각의 가역 저항-스위칭 소자는 선택적인 증착 프로세스를 이용해 형성된다.

본 발명의 제 10 양상에서, 기판 위에 형성되고 복수의 메모리 셀을 갖는 제 1 메모리 레벨을 포함하는 단결정 3차원 메모리 어레이가 제공된다. 제 1 메모리 레벨의 각각의 메모리 셀은 (1) 스티어링 소자; 그리고 (2) 상기 스티어링 소자에 결합되고 선택적인 증착 프로세스를 이용해 형성된 가역 저항-스위칭 소자를 포함한다. 단결정 3차원 메모리 어레이는 또한 상기 제 1 메모리 레벨 위에 단결정적으로 형성된 적어도 제 2 메모리 레벨을 포함한다. 수많은 다른 실시예가 본 발명의 이들 및 다른 실시예에 따라서 제공된다.

본 발명의 다른 특징 및 실시예가 다음의 상세한 설명, 첨부된 청구항 및 첨부 도면으로부터 보다 분명해질 것이다.

도 1은, 본 발명에 따라서 제공된 예시적인 메모리 셀의 개략적인 예시도.

도 2a는, 본 발명에 따라서 제공된 메모리 셀의 제 1 실시예의 단순 투시도.

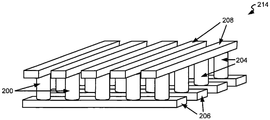

도 2b는, 도 2a의 복수의 메모리 셀로부터 형성된 제 1 메모리 레벨의 일부의 단순 투시도.

도 2c는, 본 발명에 따라서 제공된 제 1 예시적인 3차원 메모리 어레이의 일부의 단순 투시도.

도 2d는, 본 발명에 따라서 제공된 제 2 예시적인 3차원 메모리 어레이의 일부의 단순 투시도.

도 3은, 도 2a의 메모리 셀의 예시적인 실시예의 단면도.

도 4a~d는, 본 발명에 따라서 싱글 메모리 레벨의 제조 동안 기판의 일부의 단면도.

도 5는, 본 발명에 따라서 제공된 대안적인 메모리 셀의 단면도.

도 6은, 본 발명에 따라서 제공된 제 2 대안적인 메모리 셀의 단면도.

전술한 바와 같이, 재기록 가능한 저항률-스위칭 재료로 메모리 디바이스를 제조하는 것은 어렵다. 예를 들어, 많은 재기록 가능한 저항률-스위칭 재료는 화학적으로 에칭하기가 어렵고, 집적 회로에서 이들의 사용과 연관된 제조 비용 및 복잡도가 증가한다.

본 발명에 따라서, 화학적으로 에칭하기 어려운 재기록 가능한 저항률-스위칭 재료가 에칭됨이 없이 메모리 셀 내에서 사용될 수 있다. 예를 들어, 적어도 하나의 실시예에서, 가역 저항률-스위칭 재료가 에칭됨이 없이 메모리 셀내에서 사용될 수 있도록 선택 성장 공정을 이용해 형성된 재기록 가능한 저항률-스위칭 재료를 포함하는 메모리 셀이 제공된다.

하나 이상의 예시적인 실시예에서, 가역 저항-스위칭 소자가 가역 저항률-스위칭 재료로서 니켈 산화물을 이용해 형성될 수 있다. 니켈 산화물 막은 기술된 바와 같이 앞서 인용된 '939 출원에서 메모리 셀에서 사용하기에 적합하도록 도시되었다.

Ni, NixPy, NiO, NiOx, NiOxPy 등과 같은 니켈 함유 막은 화학적으로 에칭하기에 어렵다. 적어도 하나의 실시예에서, 증착 성장 프로세스의 이용을 통해, 니켈산화물 층은 니켈 산화물 층이 에칭됨이 없이 메모리 셀의 가역 저항-스위칭 소자에서 사용될 수 있다. 예를 들어, 가역 저항-스위칭 소자는 니켈 산화물보다 패턴 및 에칭이 용이한 니켈 질화물과 같은 니켈 함유 층을 산화시킴으로써 형성될 수 있다. 이러한 방법에서, 단지 기본적인 니켈 함유 층(예를 들어, 니켈 함유 층의 증착에 앞서)이 니켈 함유 층 및 니켈 산화 층이 아닌 산화에 앞서 패턴화되고/되거나 에칭된다.

몇몇 실시예에서, 니켈 산화물은 O2, 오존, 동일 또는 임의의 다른 적절한 산화 종의 조합과 같은 산소 환경에서 니켈 함유 층의 급속한 열적 산화에 의해 선 택적으로 형성될 수 있다. 임의의 경우에 있어서, 니켈 및/또는 니켈 산화물 층의 에칭을 위한 필요가 제거될 수 있으며 메모리 셀 제조가 상당히 단순해진다.

다른 재료가 메모리 셀에서 사용하기 위해 가역 또는 원-타임-프로그램가능한 저항률-스위칭 재료를 형성하기 위해 본 발명에 따라서 선택적으로 산화될 수 있다. 예를 들어, 가역 저항률-스위칭 재료를 형성하기 위해 전기도금, 그리고 산화됨에 따라서 Ta, TaN, Nb, NbN, Al, AlN, Hf, HfN, V, VN 등은 선택적으로 증착될 수 있다.

예시적인 발명의 메모리 셀

도 1은 본 발명에 따라서 제공된 예시적인 메모리 셀(100)의 개략적인 예이다. 메모리 셀(100)은 스티어링 소자(104)에 결합된 가역 저항-스위칭 소자(102)를 포함한다.

가역 저항-스위칭 소자(102)는 둘 이상의 상태간에 가역적으로 스위칭될 수 있는 저항을 갖는 (개별적으로 도시되지 않은) 가역 저항률-스위칭 재료를 포함한다. 예를 들어, 상기 소자(102)의 가역 저항률-스위칭 재료는 제 1 전압 및/또는 전류를 가할때 고-저항률 상태로 스위칭 가능한 제조때 초기, 낮은-저항률 상태일 수 있다. 제 2 전압 및/또는 전류의 인가는 낮은-저항률 상태로 가역 저항률-스위칭 재료를 리턴할 수 있다. 대안으로, 가역 저항-스위칭 소자(102)는 적절한 전압(들) 및/또는 전류(들)를 가할 때 낮은-저항 상태로 가역적으로 스위칭 가능한 제조시 초기, 고-저항 상태일 수 있다. 메모리 셀에서 사용될 때, 비록 둘 이상의 데이터/저항 상태가 사용될 수 있다고 하더라도, 하나의 저항 상태는 2진 "0"을 나타낼 수 있는 반면에 다른 저항 상태는 2진 "1"을 나타낼 수 있다. 수많은 가역 저항률-스위칭 재료 및 가역 저항-스위칭 소자를 사용한 메모리 셀의 동작이, 예를 들어, 앞서 인용된 '939 출원에 기술되어 있다, .

본 발명의 적어도 하나의 실시예에서, 가역 저항-스위칭 소자(102)가 선택 성장 공정을 이용해 형성된다. 이하 더 기술되는 바와 같이, 선택 성장 공정의 이용은 가역 저항률-스위칭 재료가 에칭될 가역 저항률-스위칭 재료없이 가역 저항-스위칭 소자(102)에서 제공될 수 있도록 한다. 이에 의해 가역 저항-스위칭 소자(102)의 제조가 단순해진다.

스티어링 소자(104)는 가역 저항-스위칭 소자(102)를 통해 전압 및/또는 전류를 선택적으로 제한함으로써 비저항 전도를 나타내는 박막 트랜지스터, 다이오드, 또는 다른 적절한 스티어링 소자를 포함할 수 있다. 이러한 방법에 있어서, 메모리 셀(100)은 2차 또는 3차원 메모리 어레이의 일부로서 사용될 수 있으며 데이터는 어레이내 다른 메모리 셀의 상태에 영향을 끼치지 않고 메모리 셀(100)에 기록하고/하거나 메모리 셀(100)로부터 판독할 수 있다.

메모리 셀(100), 가역 저항-스위칭 소자(102) 및 스티어링 소자(104)의 예시적인 실시예가 도 2a-도 6을 참조하여 이하 기술된다.

메모리 셀의 예시적인 제 1

실시예

도 2A는 본 발명에 따라서 제공된 메모리 셀(200)의 제 1 실시예의 단순 투시도이다. 도 2A를 참조하면, 메모리 셀(200)은 제 1 전도체(206)와 제 2 전도체(208) 사이의 다이오드(204)에 직렬로 결합된 (착시적으로 도시된) 가역 저항-스 위칭 소자(202)를 포함한다. 몇몇 실시예에서, 니켈 질화물, 탄탈륨 질화물, 텅스텐 질화물 등과 같은 배리어 층(210)이 가역 저항-스위칭 소자(202)와 다이오드(204) 사이에 제공될 수 있다. 예를 들어, 배리어 층(210)은 티타늄 질화물, 탄탈륨 질화물, 텅스텐 질화물 등을 포함할 수 있으며, 그리고 전도 층(212)은 텅스텐 또는 다른 적절한 금속 층을 포함할 수 있다. 이하 더 기술될 바와 같이, 배리어 층(210) 및/또는 전도 층(212)은 다이오드(204)의 형성 동안 하드 마스크로서 제공될 수 있다. 이러한 하드 마스크는 본 명세서에 참조로서 인용된 "CONDUCTIVE HARD MASK TO PROTECT PATTERNED FEATURES DURING TRENCH ETCH"란 제목의 2006년 5월 13일 출원된 미합중국 일련 출원번호 제 11/444,936호에 기술된다. 티타늄 질화물, 탄탈륨 질화물, 텅스텐 질화물 등과 같은 추가적인 배리어 층(213)이 또한 다이오드(204)와 제 1 전도체(206) 사이에 형성될 수 있다.

이하 더 기술될 바와 같이, 가역 저항-스위칭 소자(202)는 메모리 셀(200)의 제조를 단순히 하기 위해 선택적으로 형성된다. 적어도 일 실시예에서, 가역 저항-스위칭 소자(202)는 니켈 질화물과 같은 니켈 함유 층을 산화시킴으로써 형성된 니켈 산화물 층의 일부를 포함한다. 예를 들어, 니켈 질화물 층 또는 니켈의 다른 유사한 형태가 다이오드(204) 위 또는 아래에 증착되고, 패턴화되며 에칭될 수 있다(예를 들어, 제 1 전도체(206)를 갖는 것과 같은). 그 다음, 니켈 질화물(또는 다른) 층이 니켈 산화물을 형성하기 위해 산화될 수 있다(예를 들어, 급속한 열적 산화 또는 다른 산화 프로세스 사용). 다른 실시예에서, 니켈 산화물 자체가 선택적으로 증착될 수 있다. 예를 들어, NiO-, NiOx- 또는 NiOxPy 함유 층이 선택적인 증착 프로세스를 이용해 다이오드(204) 위에 선택적으로 증착될 수 있으며 (필요시) 어닐링되고/되거나 산화될 수 있다. 이들 및 다른 실시예가 도 3을 참조하여 이하 더 기술된다. 비록 가역 저항-스위칭 소자(202)가 도 2A에서 다이오드(204) 위에 위치되는 것으로 도시되지만, 가역 저항-스위칭 소자(202)는 다이오드(204) 아래에 위치될 수 있다(아래 기술된 바와 같이, 예를 들어, 도 6을 참조). 몇몇 실시예에서, 가역 저항-스위칭 소자(202)의 하나 이상의 필라멘트와 같은 부분만이 스위치될 수 있고/있거나 스위치 가능하다.

다이오드(204)는 다이오드의 p-영역 위에 n-영역을 갖는 윗방향 포인팅 또는 다이오드의 n-영역 위에 p-영역을 갖는 아래 방향 포인팅인지 어떤지 수직 다결정 p-n 또는 p-i-n 다이오드와 같은 임의의 적절한 다이오드를 포함할 수 있다. 상기 다이오드(204)의 예시적인 실시예는 도 3을 참조하여 아래 기술되어 있다.

제 1 및/또는 제 2 전도체(206, 208)는, 텅스텐, 임의의 적절한 금속, 크게 도핑된 반도체 재료, 전도성 규소화합물, 전도성 규소화합물-게르마늄화합물(germanide), 전도성 게르마늄화합물 등과 같은 임의의 적절한 전도성 재료를 포함할 수 있다. 도 2A의 실시예에서, 제 1 및 제 2 전도체(206, 208)는 레일형이며 상이한 방향(예를 들어, 서로 실질적으로 수직)으로 연장된다. 다른 전도체 형상 및/또는 구성이 사용될 수 있다. 몇몇 실시예에서, (도시되지 않은) 배리어 층, 응착 층, 반사방지 코팅 등이 디바이스 성능을 향상시키고/향상시키거나 디바이스 제 조에 도움을 주기 위해 제 1 및/또는 제 2 전도체(206, 208)가 사용될 수 있다.

전술한 바와 같이, 다른 재료가 가역 저항-스위칭 소자(202)를 형성하기 위해 사용될 수 있다. 예를 들어, Ta, TaN, Nb, NbN, Al, AlN, Hf, HfN, V, VN 등과 같은 재료가 제 1 전도체(206) 위에 증착(및/또는 패턴화되고 에칭됨)된 다음에 가역 저항-스위칭 소자(202)를 포함하는 층(212)을 형성하기 위해 산화된다.

도 2B는 도 2A의 복수의 메모리 셀(200)로부터 형성된 제 1 메모리 레벨(214)의 일부의 단순 투시도이다. 단순히 하기 위해, 티타늄 함유 층(210) 및 티타늄 산화물 층(212)만이 아래 전도체(206) 중 하나에 도시된다. 메모리 어레이(214)는 복수 비트 라인(제 2 전도체(208)) 및 (도시된 바와 같이) 다중 메모리 셀이 결합되는 워드 라인(제 1 전도체(206))을 포함하는 "크로스-포인트" 어레이이다. 다른 메모리 어레이 구성이 사용될 수 있으며, 마찬가지로 다중 레벨의 메모리가 사용될 수 있다. 예를 들어, 도 2C는 제 2 메모리 레벨(220) 아래에 위치된 제 1 메모리 레벨(218)을 포함하는 모놀리식 3차원 어레이(216)의 일부의 단순 투시도이다. 도 2C의 실시예에서, 각각의 메모리 레벨(218, 220)은 크로스-포인트 어레이내 복수의 메모리 셀(200)을 포함한다. 하나 이상의 추가적인 층(예를 들어, 인터레벨 유전체)이 제 1 및 제 2 메모리 레벨(218 및 220) 사이에 존재할 수 있지만, 단순화하기 위해 도 2C에 도시되지 않는다.다른 메모리 어레이 구성이 사용될 수 있으며, 마찬가지로 추가적인 레벨의 메모리가 사용될 수 있다. 도 2C의 실시예에서, 모든 다이오드는 다이오드의 하부 또는 상부에 p-도핑 영역을 갖는 p-i-n 다이오드가 사용되는지에 따라서 위 또는 아래와 같은 동일한 방향의 "포인트"일 수 있 으며, 다이오드 제조를 단순화한다.

몇몇 실시예에서, 메모리 레벨은 예를 들어 본 명세서에 참조로서 인용된 "High-density three-dimensional memory cell"이란 제목의 미합중국 특허 제 6,952,030호에 기술된 바와 같이 형성될 수 있다. 예를 들어, 제 1 메모리 레벨의 상부 전도체는 도 2D에 도시된 바와 같이 제 1 메모리 레벨 위에 위치되는 제 2 메모리 레벨의 하부 전도체로 사용될 수 있다. 이러한 실시예에서, 인접한 메모리 레벨상의 다이오드는 바람직하게 본 명세서에 참조로서 인용된 "LARGE ARRAY OF UPWARD POINTING P-I-N DIODES HAVING LARGE AND UNIFORM CURRENT"란 제목의 2007년 3월 27일 출원된 미합중국 출원 일련번호 제 11/692,151호(이후 '151 출원)에 기술된 바와 같이 반대 방향 포인트이다. 예를 들어, 제 1 메모리 레벨(218)의 다이오드는 화살표 A1으로 표시된 바와 같이(예를 들어, 다이오드의 아래에 p-영역을 갖는) 업워드 포인팅 다이오드인 반면에, 제 2 메모리 레벨(220)의 다이오드는 화살표 A2로 표시된 바와 같이(예를 들어, 다이오드의 아래에 n-영역을 갖는) 다운워드 포인팅 다이오드이거나, 그 반대이다.

모놀리식 3차원 메모리 어레이는 다중 메모리 레벨이 방해하는 기판이 없는 웨이퍼와 같은 단일 기판 위에 형성된다. 하나의 메모리 레벨을 형성하는 층이 기존의 레벨 또는 레벨의 층 위에 직접적으로 증착되거나 성장된다. 대조적으로, 적층 메모리는 "Three dimensional structure memory"란 제목의 Leedy의 미합중국 특허 제5,915,167호에서와 같이 분리 기판에 메모리 레벨을 형성하고 서로 상부에 메 모리 레벨을 부착함으로써 구성되었다. 기판은 박막화되거나 접착에 앞서 메모리 레벨로부터 제거될 수 있지만, 메모리 레벨이 분리 기판 위에 초기에 형성되기 때문에, 이러한 메모리들은 진정한 모놀리식 3차원 메모리 어레이가 아니다.

도 3은 도 2A의 메모리 셀(200)의 예시적인 실시예의 단면도이다. 도 3을 참조하면, 메모리 셀(200)은 가역 저항-스위칭 소자(202), 다이오드(204) 및 제 1 및 제 2 전도체(206, 208)를 포함한다.

전술한 바와 같이, 다이오드(204)는 수직 p-n 또는 p-i-n 다이오드일 수 있으며, 이것은 포인트 업워드 또는 다운워드일 수 있다. 인접한 메모리 레벨이 전도체를 공유하는 도 2D의 실시예에서, 인접한 메모리 레벨은 바람직하게 제 1 메모리 레벨에 대해 다운워드-포인팅 p-i-n 다이오드 및 인접한, 제 2 메모리 레벨에 대해 업워드-포인팅 p-i-n 다이오드와 같은 반대 방향의 포인트인 다이오드를 갖는다(또는 반대).

몇몇 실시예에서, 다이오드(204)는 폴리실리콘, 다결정 실리콘-게르마늄 합금, 폴리게르마늄 또는 임의의 다른 적절한 재료와 같은 다결정 반도체 재료로 형성될 수 있다. 예를 들어, 다이오드(204)는 고농도 n+ 폴리실리콘 영역(302), n+ 폴리실리콘 영역(302) 위에 저농도 또는 진성(비의도적으로 도핑된) 폴리실리콘 영역(304) 및 진성 영역(304) 위에 고농도 도핑된, p+ 폴리실리콘 영역(306)을 포함할 수 있다. 몇몇 실시예에서, 박막(예를 들어, 수백 옹스트롬 이하) 게르마늄 및/또는 실리콘-게르마늄 합금 층을 이용할 때 약 10% 이하의 게르마늄을 갖는 (도시되지 않은) 실리콘-게르마늄 합금 층이 n+ 폴리실리콘 영역(302)에 형성되어 전술 한 바와 같이, 예를 들어, "DEPOSITED SEMICONDUCTOR STRUCTURE TO MINIMIZE N-TYPE DOPANT DIFFUSION AND METHOD OF MAKING"이란 제목의 2005년 12월 9일 출원된 미합중국 특허출원 일련번호 제 11/298,331호(이후 '331 출원)(본 명세서에 그 전체 기재 내용이 참조로 포함되어 있음)에서 n+ 폴리실리콘 영역(302)으로부터 진성 영역(304)으로의 도펀트 이동을 방지 및/또는 감소시킬 수 있다. n+ 및 p+ 영역의 위치가 역전될 수 있다는 것이 이해될 것이다.

몇몇 실시예에서, 티타늄 질화물, 탄탈륨 질화물, 텅스텐 질화물 등과 같은 배리어 층(308)은 티타늄 산화물 층(212)과 n+ 영역(302)에 형성될 수 있다(예를 들어, 폴리실리콘 영역으로의 금속 원자의 이동을 방지 및/또는 감소시키기 위해). 이러한 금속 배리어 층의 이용은 배리어 층(308)과 티타늄 산화물 층(212) 간의 원하지 않는 정류 접점을 형성할 수 있다. 따라서, 몇몇 실시예에서, 티타늄, 니켈, 기타 전도성 재료 등과 같은 (도시되지 않은) 박막 전도성 층이 티타늄 산화물 층(212)와 배리어 층(308) 사이에 형성될 수 있다(예를 들어, 작업 기능 튜닝을 위해, 정류 접점의 형성을 감소시키거나 방지하기 위해).

다이오드(204)가 증착된 실리콘으로부터 형성될 때(예를 들어, 비정질 또는 다결정), 규소화합물 층(310)은 제조시 낮은 저항률 상태로 증착된 실리콘을 위치시키기 위해 다이오드(204)상에 형성될 수 있다. 이러한 낮은 저항률 상태는 큰전압이 증착된 실리콘을 낮은 저항률 상태로 스위칭하기 위해 요구되지 않기 때문에 메모리 셀(200)의 프로그래밍을 보다 쉽게 한다. 예를 들어, 티타늄 또는 코발트와 같은 규소화합물-형성 금속 층(312)은 p+ 폴리실리콘 영역(306)상에 증착될 수 있 다. (이하 기술된) 다이오드(204)를 형성하는 증착된 실리콘을 결정화하기 위해 사용된 후속적인 어닐 단계 동안, 규소화합물-형성 금속 층(312) 및 다이오드(204)의 증착된 실리콘은 규소화합물 층(310)을 형성하기 위해 상호작용하며, 규소화합물-형성 금속 층(312)의 전체 또는 일부를 소모한다.

본 명세서에 참조로서 인용된 "Memory Cell Comprising a Semiconductor Junction Diode Crystallized Adjacent to a Silicide"란 제목의 미합중국 특허 제 7,176,064호에 기술된 바와 같이, 티타늄 및 코발트와 같은 규소화합물-형성 재료는 규소화합물 층을 형성하기 위해 어닐링 동안 증착된 실리콘과 반응한다. 티타늄 규소화합물과 코발트 규소화합물의 격자 공간은 실리콘의 것과 가까우면, 이러한 규소화합물 층은 증착된 실리콘이 결정화됨에 따라서 인접한 증착된 실리콘을 위한 "결정화 템플릿" 또는 "시드"로서 제공될 수 있다(예를 들어, 규소화합물 층(310)은 어닐링 동안 실리콘 다이오드(204)의 크리스털 구조를 향상시킨다). 이에 의해, 보다 낮은 저항률 실리콘이 제공된다. 유사한 결과가 실리콘-게르마늄 합금 및/또는 게르마늄 다이오드에 대해 달성될 수 있다.

도 3의 실시예에서, 가역 저항-스위칭 소자(202)가 선택적인 증착 프로세스에 의해 형성된다. 몇몇 실시예에서, 가역 저항-스위칭 소자(202)는 전도성 규소화합물-형성 금속 층(312) 위에 형성될 수 있다(또는 규소화합물-형성 금속 층(312) 위에 형성된 전도성 배리어 층위에). (이러한 층은 도 4A-4D를 참조하여 이하 기술된 바와 같이 다이오드(204)의 형성 동안 패턴화될 수 있다.) 그러나, 다른 실시예에서, 금속 하드 마스크는 저항-스위칭 소자(202)의 형성에 앞서 규소화합물-형성 금속 층(312) 위에 형성될 수 있다. 예를 들어, 배리어 층(314) 및/또는 전도 층(316)은 규소화합물-형성 금속 층(312) 위에 형성될 수 있다. 배리어 층(314)은 티타늄 질화물, 탄탈륨 질화물, 텅스텐 질화물 등을 포함할 수 있으며, 전도 층(316)은 텅스텐 또는 다른 적절한 금속 층을 포함할 수 있다.

이하 기술될 바와 같이, 배리어 층(314) 및/또는 전도 층(316)은 다이오드(204)의 형성 동안 하드 마스크로서 제공될 수 있으며 (앞서 인용된 '936 출원에 기술된 바와 같이) 상부 전도체(208)의 형성 동안 발생할 수 있는 임의의 오버에칭을 완화할 수 있다. 예를 들어, 배리어 층(314) 및 전도 층(316)은 패턴화되고 에칭될 수 있으며, 그 다음 다이오드(204)의 에칭 동안 마스크로서 제공될 수 있다. 전도 층(316), 배리어 층(314), 규소화합물-형성 금속 층(312), 다이오드(204)(p+폴리실리콘 층(306), 진성 층(304), n+폴리실리콘 층(302)) 및 배리어 층(308)의 에칭은 필러 구조(318)를 생성한다. 유전체 재료(320)가 필러 구조(318)의 상부 및 주변에 증착되어 메모리 셀(200)을 포함하는 메모리 셀상에 제조된 (도시되지 않은) 다른 메모리 셀의 다른 유사한 필러 구조로부터 필러 구조(318)를 격리한다. 그 다음, P 또는 유전체 에치백 단계가 수행되어 유전체 재료(320)를 평탄화하고 전도 층(316)의 상부로부터 유전체 재료를 제거한다.

유전체 재료(320)의 평탄화 후, 가역 저항-스위칭 소자(202)가 선택적인 증착 프로세스에 의해 패턴화되고 에칭된 전도 층(316) 위에 형성될 수 있다. 예를 들어, 니켈 산화물 층은 (1)NiO, NiOx 및 NiOxPy와 같은 니켈 산화물을 선택적으로 증착시키고, 필요시 니켈 산화물을 어닐링 및/또는 산화시키며; 그리고/또는 (2)니켈을 선택적으로 증착한 후 니켈을 산화시킴으로써 패턴화되고 에칭된 전도 층(316) 위에 선택적으로 형성될 수 있다. 임의의 경우에 있어서, 니켈 산화물이 오직 전도 층(316)의 패턴화되고 에칭된 상면에 증착되기 때문에, 니켈 및/또는 니켈 산화물 층의 에칭을 위한 필요가 제거될 수 있으며 메모리 셀 제조가 상당히 간단해 진다. 더욱이, 니켈 산화물의 임의의 원하는 두께가 형성될 수 있다. 몇몇 실시예에서, 약 1000 옹스트롬 이하, 보다 바람직하게 약 500 옹스트롬 이하의 니켈 산화물 층 두께가 가역 저항-스위칭 소자(202)를 위해 사용된다(비록 다른 두께 범위가 사용될 수 있다고 하더라도).

일 실시예에서, 형성 후, 전도 층(316)의 패턴화 및 에칭, 비전해 증착 프로세스가 전도 층(316)에 니켈 또는 니켈 산화물을 선택적으로 증착하기 위해 사용된다. 예를 들어, 수용액에 전도 층(316)을 담금으로써 전도 층(316)에 니켈 또는 니켈 산화물을 선택적으로 형성하기 위해 수용액이 사용될 수 있다. 예를 들어, 수용액은 하나 이상의 용해된 솔트/프리커서, 복잡한 시약 및/또는 용액의 pH를 조절하기 위한 버퍼를 포함할 수 있다. 몇몇 실시예에서, 수용액은 니켈 솔트 및/또는 니켈 황산염, 니켈 아황산염, 니켈 인산염, 니켈 아인산염, 니켈 수산화물, 암모니아 인산염, 또는 이들의 혼합물과 같은 니켈 솔트 수산화물을 포함할 수 있다. 더욱이, 예시적인 성분은 NiSO4, NaH2PO2, 구연산 나트륨, (NH4)2SO4 등을 포함할 수 있다. 니켈 또는 니켈 산화물(또는 둘다)이 수용액 및/또는 다른 프로세스 조건을 형 성하기 위해 사용된 정확한 성분에 따라서 전도 층(316)에 증착될 수 있다.

예시적인 프로세스 조건은 약 20 내지 85℃ 사이의 온도로 수용액이 유지되는 동안 약 1초 내지 약 5분 동안 수용 니켈 함유 용액에 전도 층(316)을 담그는 단계를 포함한다. 추가적인 예시적인 수용액 및/또는 니켈 또는 니켈 산화물 층을 선택적으로 형성하기 위해 사용될 수 있는 프로세스 조건이 본 명세에 그대로 참조로서 인용된 N. Takano 등에 의한 "Mechanism of the Chemical Deposition of Nickel on Silicon Wafers in Aqueous Solutions"란 제목의 Electrochemical Society의 저널, 146(4) pp.1407-1411에 기술된다. 전술한 바와 같이, 증착된 니켈 또는 니켈 산화물은 Ni, NixSOp, NiO, NiOx, NiOxPp 또는 다른 유사한 재료를 포함할 수 있다.

니켈 또는 니켈 산화물의 형성에 이어, 열적 산화 프로세스가 선택적으로 증착된 니켈로부터 니켈 산화물을 형성하거나 선택적으로 증착된 니켈 산화물의 조직 및/또는 전기적 특성을 개선하기 위해 사용될 수 있다. 예시적인 산화 조건은 약 400 내지 800℃의 온도로 약 20초 내지 10분 동안 O2와 같은 산소 환경에서 급속한 열적 산화를 포함한다. 다른 산화 또는 어닐링 프로세스, 산소 종, 시간 및/또는 온도가 사용될 수 있다.

패턴화되고 에칭된 전도 층(316)에 니켈 함유 층을 형성하기 위해 사용될 수 있는 임의의 다른 적절한 선택적인 증착 프로세스는 종래의 니켈 전기도금을 포함한다. 임의의 적절한 전기도금 프로세스는 전도 층(316)에 니켈을 선택적으로 증착 하기 위해 사용될 수 있다. 이후, 전기도금 니켈이 전술한 바와 같이 니켈 산화물을 형성하기 위해 산화될 수 있다.

전술한 바와 같이, 다른 재료가 가역 저항-스위칭 소자(202)를 형성하기 위해 사용될 수 있다. 예를 들어, Nb, Ta, V, Al, Ti, Co, 코발트-니켈 합금 등과 같은 재료가 다이오드(204) 위에 유사하게 선택적으로 증착될 수 있으며(도 2A에도시된 바와 같이 배리어 층(210) 및/또는 전도 층(212) 위) 필요시 어닐링 및/또는 산화될 수 있다.

가역 저항-스위칭 소자(202)의 형성에 이어, 상부 전도체(208)가 형성된다. 몇몇 실시예에서, 하나 이상의 배리어 층 및/또는 부착층(322)이 전도 층(324)의 증착에 앞서 가역 저항-스위칭 소자(202) 위에 형성될 수 있다. 전도 층(324) 및 배리어 층(322)은 상부 전도체(208)를 형성하기 위해 함께 패턴화되고/되거나 에칭될 수 있다. 몇몇 실시예에서, 상부 전도체(208)는 도 4A-4D를 참조하여 이하 기술된 바와 같이 다마신 프로세스(damascene process)를 이용해 형성될 수 있다.

상부 전도체(208)의 형성에 이어, 메모리 셀(200)이 어닐링되어 다이오드(204)의 증착된 반도체 재료를 크리스탈화(및/또는 규소화합물 층(310)을 형성하기 위해)한다. 적어도 하나의 실시예에서, 어닐은 약 600℃ 내지 800℃, 보다 바람직하게는 약 650℃ 내지 750℃ 사이의 온도로 질소에서 약 10초 내지 약 2분 동안 수행될 수 있다. 다른 어닐링 시간, 온도 및/또는 환경이 사용될 수 있다. 전술한 바와 같이, 규소화합물 층(310)이 다이오드(204)를 형성하는 기본 증착 반도체 재료를 위한 어닐링 동안 "크리스탈화 템플릿" 또는 "시드"로서 제공될 수 있다. 이 에 의해 보다 낮은 저항률 다이오드 재료가 제공된다.

본 발명에 따라서 메모리 셀을 제조하기 위한 예시적인 프로세스가 도 4A-D를 참조하여 이하 기술된다.

메모리 셀에 대한 예시적인 제조 공정

도 4A-D는 본 발명에 따라서 제 1 메모리 레벨의 제조 동안 기판(400)의 일부의 단면도를 예시한다. 이하 기술될 바와 같이, 싱글 메모리 레벨은 선택 성장 공정을 이용해 형성된 가역 저항-스위칭 소자를 각각 포함하는 복수의 메모리 셀을 포함한다. 추가적인 메모리 레벨은 (도 2C-2D를 참조하여 전술한 바와 같이)제 1 메모리 레벨 위에 제조될 수 있다.

도 4A를 참조하면, 기판(400)은 이미 진행된 여러 프로세싱 단계를 갖는 것으로 도시된다. 기판(400)은 추가적인 회로를 갖거나 갖지 않는 실리콘, 게르마늄, 실리콘-게르마늄, 도핑되지 않은, 도핑된, 벌크, 실리콘-온-절연체(SOI) 또는 다른 기판과 같은 임의의 적절한 기판일 수 있다. 예를 들어, 기판(400)은 (도시되지 않은)하나 이상의 n-well 또는 p-well 영역을 포함할 수 있다.

절연층(402)은 기판(400) 위에 형성된다. 몇몇 실시예에서, 절연층(402)은 실리콘 산화물, 실리콘 질화물, 실리콘 산화질화물의 층 또는 임의의 다른 적절한 절연 층일 수 있다. 다른 실시예에서, 절연 층(402)은 기판(400)에서 트렌치를 에칭하고, 트렌치를 채우기 위해 기판(400) 위에 실리콘 이산화물, 실리콘 질화물 도는 다른 유전체와 같은 유전체를 증착시키며 기판(400)의 상면(403)을 재노출하기 위해 기판(400)을 평탄화함으로써 형성된 얕은 트렌치 격리(STI) 영역일 수 있다. 주목해야 할 것은 하나 이상의 실시예에서, 실리콘 질화물 또는 (도시되지 않은)유사한 보호층이 격리 영역 형성에 앞서 (예를 들어, 활성 영역을 보호하기 위해)기판(400)의 (도시되지 않은) 활성 영역 위에 형성될 수 있다. 대안으로서, 실리콘의 국부 산화(LOCOS) 프로세스 또는 임의의 다른 적절한 프로세스가 격리 층(402)을 정의하기 위해 사용될 수 있다.

격리 층(402)의 형성에 이어, 부착 층(404)이 격리 층(402) 위에 형성된다(예를 들어, 물리적 증착 또는 다른 방법에 의해). 예를 들어, 부착 층(404)은 티타늄 질화물 또는 탄탈륨 질화물, 텅스텐 질화물, 하나 이상의 부착층의 조합 등과 같은 다른 적절한 부착 층의 약 20 내지 약 500 옹스트롬, 바람직하게는 약 100 옹스트롬일 수 있다. 다른 부착 층 재료 및/또는 두께가 사용될 수 있다. 몇몇 실시예에서, 부착 층(404)은 선택적일 수 있다.

부착 층(404)의 형성 후, 전도 층(406)이 부착 층(404) 위에 증착된다. 전도 층(406)은 텅스텐 또는 다른 적절한 금속, 고농도 반도체 재료, 전도성 규소화합물, 전도성 규소화합물-게르마늄, 전도성 게르마늄, 또는 임의의 적절한 방법(예를 들어, 화학 증착, 물리적 증착 등)에 의해 증착된 것과 같은 임의의 적절한 전도성 재료를 포함할 수 있다. 적어도 하나의 실시예에서, 전도성 층(406)은 약 200 내지 2500 옹스트롬의 텅스텐을 포함할 수 있다. 다른 전도 층 재료 및/또는 두께가 사용될 수 있다.

전도 층(406)의 형성 후, 티타늄 질화물과 같은 티타늄 함유 층(407)이 (예를 들어, 물리적 증착 또는 다른 방법을 이용해) 전도 층(406) 위에 형성된다. 몇 몇 실시예에서, 티타늄 함유 층(407)은 약 20 내지 약 1200 옹스트롬의 티타늄 질화물을 포함한다. 티타늄, 티타늄 합금, TiSi2, TiW 등과 같은 다른 티타늄 함유 층 재료 및/또는 두께가 사용될 수 있다.

전도 층(406)의 형성에 이어, 부착 층(404), 전도 층(406)이 패턴화되고 에칭된다. 예를 들어, 부착 층(404), 전도 층(406)이 소프트 또는 하드 마스크를 갖는 종래의 리소그래피 기법 및 습식 또는 건식 에칭 프로세싱을 이용해 패턴화되고 에칭될 수 있다. 적어도 하나의 실시예에서, 부착 층(404), 전도 층(406)이 패턴화되고 에칭되어 (도 4A에 도시된 바와 같이) 실질적으로 평행하고, 실질적으로 공면 전도체(408)를 형성한다. 비록 다른 전도체 폭 및/또는 공간이 사용될 수 있다고 하더라도, 전도체(408)에 대한 예시적인 폭 및/또는 전도체(408) 간의 공간은 약 200 내지 약 2500 옹스트롬의 범위이다.

전도체(408)가 형성된 후, 유전체 층(410)이 기판(400)위에 증착되어 전도체(408) 사이의 빈공간을 채우도록 한다. 예를 들어, 대략 3000-7000 옹스트롬의 실리콘 이산화물이 기판(400)에 증착될 수 있으며 평탄면(412)을 형성하기 위해 화학적 기계적 폴리싱 또는 에치백 프로세스를 이용하여 평탄화될 수 있다. 평탄 면(412)은 도시된 바와 같이 유전체 재료(410)에 의해 분리된 티타늄 함유 층 재료(407)의 노출된, 이산 영역(407a-f)을 포함한다. 이산 티타늄 함유 층 영역(407a-f)은 (이하 보다 더 기술되는 바와 같이) 기판(400) 위에 형성되는 각각의 메모리 셀을 위한 티타늄 산화물 가역 저항-스위칭 소자를 선택적으로 형성하기 위 해 사용될 수 있다.

본 발명의 다른 실시예에서, 전도체(408)는 전도체(408)를 위한 오프닝 또는 빈공간을 생성하기 위해 유전체 층(410)이 형성되고 패턴화되는 다마신 프로세스를 이용해 형성될 수 있다. 그 다음, 오프닝 또는 빈공간 부착 층(404) 및 전도 층(406)으로 채워질 수 있다(및/또는 전도 시드, 전도 채움 및/또는 배리어 층). 그 다음 부착 층(404) 및 전도 층(406)이 평탄면(412)을 형성하기 위해 평탄화될 수 있다. 이러한 실시예에서, 부착 층(404)은 각각의 오프닝 또는 빈공간의 하부 및 벽면 라인일 수 있다.

평탄화에 이어, 각각의 메모리 셀의 다이오드 구조가 형성된다. 도 4B를 참조하면, 배리어 층(414)이 기판(400)의 평탄화된 상면(412) 위에 형성된다. 배리어 층(414)은 약 20 내지 약 500 옹스트롬, 보다 바람직하게는 약 100옹스트롬의 티타늄 질화물, 또는 탄탈륨 질화물, 텅스텐 질화물, 하나 이상의 배리어 층의 조합, 티나늄/탄탈륨 질화물과 같은 다른 층과의 조합인 배리어 층 또는 텅스텐/텅스텐 질화물 스택 등일 수 있다. 다른 배리어 층 재료 및/또는 두께가 사용될 수 있다.

배리어 층(414)의 증착 후, 각각의 메모리 셀의 다이오드를 형성하기 위해 사용된 반도체 재료의 증착이 시작된다(예를 들어, 도 2A-3의 다이오드(204)). 각각의 다이오드는 전술한 바와 같이 수직 p-n 또는 p-i-n 다이오드일 수 있다. 몇몇 실시예에서, 각각의 다이오드는 폴리실리콘, 다결정 실리콘-게르마늄 합금, 폴리게르마늄과 같은 다결정 반도체 재료 또는 임의의 다른 적절한 재료로 형성된다. 편의를 위해, 폴리실리콘, 다운워드-포인팅 다이오드의 형성이 본 명세서에 기술된 다. 다른 재료 및/또는 다이오드 구성이 사용될 수 있다는 것이 이해될 것이다.

도 4B를 참조하면, 배리어 층(414)의 형성에 이어, 고농도 n+ 실리콘 층(416)이 배리어 층(414)에 증착된다. 몇몇 실시예에서, n+ 실리콘 층(416)은 증착때 비정질 상태로 존재한다. 다른 실시예에서, n+ 실리콘 층(416)은 증착때 다결정 상태로 존재한다. 착화학 기상 증 또는 다른 적절한 프로세스가 n+ 실리콘 층(416)을 증착하기 위해 사용될 수 있다. 적어도 하나의 실시예에서, n+ 실리콘 층(416)이 형성될 수 있으며, 예를 들어, 약 100 내지 1000 옹스트롬, 바람직하게는 약 100옹스트롬의 약 1021cm-3의 도핑 농도를 갖는 인(phosphorus) 또는 비소(arsenic) 도핑 실리콘으로 형성될 수 있다. 다른 층 두께, 도펀트 및/또는 도핑 농도가 사용될 수 있다. 예를 들어, n+ 실리콘 층(416)이 증착 동안 도너 가스(donor gas)를 흘림으로써 원위치에 도핑될 수 있다. 다른 도핑 방법이 사용될 수 있다(예를 들어, 이온주입).

n+ 실리콘 층(416)의 증착 후, 저농도, 진성 및/또는 비의도적으로 도핑된 실리콘 층(418)이 n+ 실리콘 층(416) 위에 형성된다. 몇몇 실시예에서, 진성 실리콘 층(418)이 증착때 비정절 상태로 존재한다. 다른 실시예에서, 진성 실리콘 층(418)이 증착때 다결정 상태로 존재한다. 착화학 기상 증 또는 다른 적절한 증착 방법이 진성 실리콘 층(418)을 증착하기 위해 사용될 수 있다. 적어도 하나의 실시예에서, 진성 실리콘 층(418)은 약 500 내지 4800옹스트롬, 바람직하게는 약 2500 옹스트롬의 두께일 수 있다. 다른 진성 층 두께가 사용될 수 있다.

박막(예를 들어, 수백 옹스트롬 이하) 게르마늄 및/또는 (도시되지 않은)실리콘-게르마늄 합금 층이 n+ 실리콘 층(416)에서 진성 실리콘 층(418)으로의 도펀트 이동을 방지 및/또는 감소시키기 위해 진성 실리콘 층(418)의 증착에 앞서 n+ 실리콘 층(416)에 형성될 수 있다(앞서 인용된 '331 출원에 기술된 바와 같이).

n+ 실리콘 층(416) 및 진성 실리콘 층(418)의 형성에 이어, n+ 실리콘 층(416), 진성 실리콘 층(418), 배리어 층(414) 및/또는 임의의 전도성 층(사용된다면)이 패턴화 및 에칭되어 (도시된 바와 같이)전도체(408)를 오버라잉하는 실리콘 필러(silicon pillar)(420)를 형성하도록 한다. 소프트 또는 하드 마스크, 그리고 습식 또는 건식 에칭 프로세싱을 갖는 종래의 리소그래피 기법이 실리콘 필러(420)를 형성하기 위해 사용될 수 있다.

실리콘 필러(420)가 형성된 후, 유전체 층(422)이 증착되어 실리콘 필러(420) 사이의 빈공간을 채운다. 예를 들어, 약 200-7000옹스트롬의 실리콘 이산화물이 증착될 수 있으며 평탄면(424)을 형성하기 위해 화학적 기계적 폴리싱 또는 에치백 프로세스를 이용해 평탄해질 수 있다. 도시된 바와 같이, 평탄면(424)은 유전체 재료(422)에 의해 분리된 실리콘 필러(420)의 노출된 상면을 포함한다. 실리콘 질화물, 실리콘 산화질화물, 로우 K 유전체 등과 같은 다른 유전체 재료 및/또는 다른 유전체 층 두께가 사용될 수 있다. 예시적인 로우 K 유전체는 탄소 도핑 산화물, 실리콘 탄소 층 등을 포함한다.

실리콘 필러(420)의 형성 후, p+ 실리콘 영역(426)이 각각의 실리콘 필러(420), 실리콘 필러(420)의 상면 근처에 형성된다. 예를 들어, 블랭킷 p+ 임플란 트가 실리콘 필러(420)내 사전결정된 깊이로 붕소(boron)를 주입하기 위해 사용될 수 있다. 예시적인 주입가능한 분자 이온은 BF2, BF3, B 등을 포함한다. 몇몇 실시예에서, 약 1-5×10 ions/㎠ 의 임플란트 도스가 사용될 수 있다. 다른 임플란트 종 및/또는 도스가 사용될 수 있다. 더욱이, 몇몇 실시예에서, 확산 프로세스가 실리콘 필러(420)의 상부를 도핑하기 위해 사용될 수 있다. 적어도 하나의 실시예에서, 비록 다른 p+ 실리콘 영역 사이즈가 사용될 수 있다고 하더라도, p+ 실리콘 영역(426)은 약 100-700옹스트롬의 깊이를 갖는다. (주목해야 할 것은 형성될 다이오드가 업워드 포인팅 p-n 또는 p-i-n 다이오드이면, 실리콘 필러(420)의 상부는 n-타입으로 도핑될 것이다). 이에 의해, 각각의 실리콘 필러(420)는 다운워드-포인팅, p-i-n 다이오드(428)를 포함한다.

도 4D를 참조하면, p-i-n 다이오드(428)의 완료 후, 규소화합물-형성 금속 층(430)이 기판(400) 위에 증착된다. 예시적인 규소화합물-형성 금속은 스퍼터 또는 기타 증착된 티타늄 또는 코발트를 포함한다. 몇몇 실시예에서, 규소화합물-형성 금속 층(430)은 약 10 내지 약 200 옹스트롬, 바람직하게는 약 20 내지 약 50 옹스트롬 그리고 보다 바람직하게는 약 20 옹스트롬의 두께를 갖는다. 다른 규소화합물-형성 금속 층 재료 및/또는 두께가 사용될 수 있다. 이하 더 기술될 바와 같이, 구조의 어닐링은 규소화합물-형성 금속 층(430)으로 부터의 금속 및 p+ 실리콘 영역(426)으로부터의 실리콘이 각각의 p+ 실리콘 영역(426)에 인접한 규소화합물 영역(432)을 형성하도록 반응한다.

규소화합물-형성 금속 층(430)의 형성에 이어, 전도체(436)의 제 2 세트가 전도체(408)의 하부 세트의 형성과 유사한 방식으로 다이오드(428) 위에 형성될 수 있다. 몇몇 실시예에서, 하나 이상의 배리어 층 및/또는 부착 층(438)이 전도체(436)의 상부, 제 2 세트를 형성하기 위해 사용된 전도층(440)의 증착에 앞서 규소화합물-형성 금속 층(430) 위에 배치될 수 있다.

전도 층(440)은 임의의 적절한 방법(예를 들어, 화학 증착, 물리적 증착 등)에 의해 증착된 텅스텐, 다른 적절한 금속, 고농도 반도체 재료, 전도성 규소화합물, 전도성 규소화합물-게르마늄, 전도성 게르마늄 등과 같은 임의의 적절한 전도성 재료로 형성될 수 있다. 다른 전도 층 재료가 사용될 수 있다. 배리어 층 및/또는 부착 층(438)은 탄탈륨 질화물, 텅스텐 질화물, 하나 이상의 층의 조합, 또는 임의의 다른 적절한 재료(들)과 같은 티타늄 질화물 또는 다른 적절한 층을 포함할 수 있다. 증착된 전도 층(440), 배리어 및/또는 부착 층(438), 및/또는 규소화합물-형성 금속 층(430)이 전도체(436)의 제 2 세트를 형성하기 위해 패턴화 및/또는 에칭될 수 있다. 적어도 하나의 실시예에서, 상부 전도체(436)는 실질적으로 평행이고, 보다 낮은 전도체(408)와 다른 방향으로 연장되는 실질적으로 공면인 전도체이다.

상부 전도체(436)의 형성에 이어, 구조는 다이오드(430)의 증착된 반도체 재료를 결정화(및/또는 p+ 영역(420)을 갖는 규소화합물-형성 금속 층(422)의 반응에 의해 규소화합물 영역을 형성하기 위해)하기 위해 어닐닝될 수 있다. 적어도 하나의 실시예에서, 어닐링은 약 600 내지 800℃, 보다 바람직하게는 약 650과 750℃ 사이의 온도로 질소에서 약 10초 내지 약 2분 동안 수행될 수 있다. 다른 어닐링 시간, 온도 및/또는 환경이 사용될 수 있다. 각각의 규소화합물-형성 금속 층 영역(422) 및 영역(420)이 반응할 때 형성된 규소화합물 영역은 다이오드(430)를 형성하는 기본 증착 반도체 재료를 위한 어닐링 동안 "크리스탈화 템플릿" 또는 "시드"로서 제공될 수 있다(예를 들어, 임의의 비정질 반도체 재료를 다결정 반도체 재료로 변화시키고/거나 다이오드(430)의 전반적인 크리스털 속성을 개선함으로써). 이에 의해 보다 낮은 저항률 다이오드 재료가 제공된다.

대안적인 예시적인 메모리 셀

도 5는 본 발명에 따라서 제공된 예시적인 메모리 셀(500)의 단면도이다. 메모리 셀(500)은 박막, 기판(505) 위에 형성된 가변 저항-스위칭 소자(504)에 결합된 금속 산화물 반도체 전계 효과 트랜지스터(MOSFET)(502)와 같은 박막 트랜지스터(TFT)를 포함한다. 예를 들어, MOSFET(502)은 임의의 적절한 기판에 형성된 n-채널 또는 p-채널 박막 MOSFET일 수 있다. 도시된 실시예에서, 실리콘 이산화물, 실리콘 질화물, 산소질화물 등과 같은 절연 영역(506)이 기판(505) 위에 형성되고 증착된 실리콘, 게르마늄, 실리콘-게르마늄 등과 같은 증착된 반도체 영역(507)이 절연 영역(506) 위에 형성된다. 박막 MOSFET(502)은 증착된 반도체 영역(507) 내에 형성되고 절연 영역(506)에 의해 기판(505)으로부터 절연된다.

MOSFET(502)은 게이트 유전체 층(514)과 마찬가지로 소스/드레인 영역(508, 510) 및 채널 영역(512), 게이트 전극(516) 및 스페이서(518a-b)를 포함한다. 적어도 하나의 실시예에서, 소스/드레인 영역(508, 510)은 도핑된 p-타입일 수 있으며 채널 영역(512)은 도핑된 n-타입일 수 있는 반면에, 다른 실시예에서 소스/드레인 영역(508, 510)은 도핑된 n-타입이고 채널 영역(512)은 도핑된 p-타입일 수 있다. 임의의 다른 MOSFET 구성 또는 임의의 적절한 제조 기법이 박막 MOSFET(502)을 위해 사용될 수 있다. 몇몇 실시예에서, MOSFET(502)은 기판(506)에 형성된(예를 들어, STI, LOCOS 또는 다른 유사한 프로세스를 이용해 형성된) (도시되지 않은) 격리 영역에 의해 전기적으로 격리될 수 있다. 대안으로, MOSFET(502)의 게이트, 소스 및/또는 드레인 영역은 기판(506)에 형성된 (도시되지 않은) 다른 트랜지스터와 공유될 수 있다.

가역 저항-스위칭 소자(504)는 전도성 플러스(526) 위에 형성된 가역 저항률-스위칭 재료(522)를 포함한다. 적어도 한 실시예에서, 가역 저항률-스위칭 재료(522)는 도 1-4D의 실시예를 참조하여 사전 기술된 바와 같이 선택적 증착 프로세스를 이용해 형성된다. 예를 들어, 니켈 산화물 층은 (1) 니켈 산화물; 그리고/또는 (2) 선택적으로 증착된 니켈을 선택적으로 증착시킨 다음에 니켈을 산화시킴으로써 전도성 플러그(526) 위에 선택적으로 형성될 수 있다. 예시적인 선택적 증착 프로세스는 비전해 증착, 전기도금 등을 포함한다. 다른 재료가 선택적으로 증착될 수 있으며, 메모리 셀(500)에서 사용하기 위한 가역 저항률-스위칭 재료를 형성하기 위해 본 발명에 따라서 선택적으로 증착되고, 산화되며/되거나 어닐링될 수 있다(예를 들어, Nb, Ta, V, Al, Ti, Co, 코발트-니켈 합금 등).

도 5에 도시된 바와 같이, 가역 저항-스위칭 소자(504)는 제 1 전도성 플러스(526)에 의해 MOSFET(502)의 소스/드레인 영역(510)에 결합되고 제 2 전도성 플 러그(530)에 의해 제 1 금속 레벨(M1) 라인(528)에 결합된다(이것은 유전체 층(532)을 통해 연장된다). 마찬가지로, 제 3 전도성 플러그(534)는 MOSFET(502)의 소스/드레인 영역(508)을 M1 라인(536)에 결합한다. 전도성 플러그 및/또는 라인은 텅스텐, 다른 금속, 고농도 반도체 재료, 전도성 규소화합물, 전도성 규소화합물-게르마늄, 전도성 게르마늄 등과 같은 (배리어 층을 갖거나 갖지 않는)임의의 적절한 재료로 형성될 수 있다. 주목해야 할 것은 MOSFET(502)이 n-채널 디바이스일 때, 영역(508)은 드레인으로서 제공되고 영역(510)은 MOSFET(502)을 위한 소스로서 제공되며; 그리고 MOSFET(502)이 p-채널 디바이스일 때, 영역(508)은 소스로서 제공되며 영역(510)은 MOSFET(502)을 위한 드레인으로서 제공된다. 유전체 층(532)은 실리콘 규소화합물, 실리콘 질화물, 실리콘 산소질화물, 로우 K 유전체 등과 같은 임의의 적절한 유전체를 포함할 수 있다.

메모리 셀(500)에서, 박막 MOSFET(502)은 도 2A-4D의 메모리 셀에서 사용된 다이오드의 것과 유사한 방식으로 스티어링 소자로서 동작하며, 가역 저항-스위칭 소자(504)를 통해 인가된 전압 및/또는 전류를 선택적으로 제한한다.

적어도 하나의 실시예에서, 가역 저항-스위칭 소자(504)는 약 500 옹스트롬 이하의 두께, 보다 바람직하게는 약 300옹스트롬 이하의 두께를 갖는 티타늄 산화물 층을 포함한다. 다른 티타늄 산화물 두께가 사용될 수 있다.

제 2 대안 메모리 셀

도 6은 본 발명에 따라서 제공된 예시적인 메모리 셀(600)의 단면도이다. 메모리 셀(600)은 가역 저항-스위칭 소자(202)가 다이오드(204) 아래에 형성되는 것 을 제외하고는 도 3의 메모리 셀(200)과 유사하다. 특히, 도 6에 도시된 바와 같이, 가역 저항-스위칭 소자(202)는 패턴화되고 에칭된 하부 전도체(206)상에 전도성 재료(602)를 선택적으로 증착시킴으로써 형성된다. 그 다음 전도성 재료(602)는 메모리 셀(600)에서 사용하기 위한 가역 저항-스위칭 재료(604)를 형성하기 위해 본 발명에 따라서 필요시 어닐링 및/또는 산화될 수 있다. 예를 들어, 전도성 재료(602)는 전기도금 등과 같은 선택적인 증착 및 가역 저항률-스위칭 재료 층(604)을 형성하기 위해 산화되는 Ni, NixPy, NiO, NiOx, NiOxPy, Nb, Ta, V, Al, Ti, Co, 코발트-니켈 합금 등을 포함할 수 있다. 다이오드(204)와 수직적으로 오버랩되고/되거나 정렬되는 가역 저항률-스위칭 재료 층(604)의 일부가 다이오드(204)와 메모리 셀(600)의 제 1 전도체(206) 사이의 가역 저항-스위칭 소자(202)로서 제공될 수 있다. 몇몇 실시예에서, 가역 저항-스위칭 소자(202)의 하나 이상의 필라멘트와 같은 일부만이 스위치 및/또는 스위치가능할 수 있다. 층(604)이 이미 패턴화되고 에칭된 하부 전도체(206) 위에 선택적으로 증착될 수 있기 때문에, 가역 저항률-스위칭 재료 층(604)은 에칭을 필요로 하지 않는다.

전술한 설명은 단지 본 발명의 예시적인 실시예를 개시한다. 본 발명의 범주내의 상기 개시된 장치 및 방법의 변경이 당업자에게 분명할 것이다. 예를 들어, 비록 본 발명이 티타늄 질화물의 선택적인 산화에 대해 주로 기술하였지만, 예를 들어, Ta2O5, Nb2O5, Al2O3, V2O5, CoO, (CoxNiy)Oz, 그리고 TiO2를 형성하는 Ta, Nb, Al, V, Co, 코발트-니켈 합금, Ti 등과 같은 메모리 셀에서 사용하기 위한 가역 저 항률-스위칭 재료를 형성하기 위해 다른 재료가 선택적으로 산화될 수 있다.

따라서, 비록 본 발명이 본 발명의 예시적인 실시예와 관련하여 개시되었지만, 이어지는 청구항에 의해 정의된 바와 같이 다른 실시예가 본 발명의 사상 및 범주내에 포함될 것이라는 것이 이해될 것이다.

상술한 바와 같이, 본 발명은, 선택적으로 성장한 가역 저항-스위칭 소자를 사용하는 메모리 셀과 상기 메모리 셀을 형성하는 방법을 제공하는데 사용된다.

Claims (78)

- 메모리 셀을 형성하는 방법으로서,기판(substrate) 위에 스티어링 소자(steering element)를 형성하는 단계와,선택 증착 공정(selective deposition process)을 사용하여 상기 스티어링 소자에 결합된 가역 저항-스위칭 소자를 형성하는 단계를포함하는, 메모리 셀 형성 방법.

- 제 1항에 있어서, 상기 스티어링 소자를 형성하는 단계는 다이오드를 형성하는 단계를 포함하는, 메모리 셀 형성 방법.

- 제 1항에 있어서, 상기 스티어링 소자를 형성하는 단계는 다결정 다이오드를 형성하는 단계를 포함하는, 메모리 셀 형성 방법.

- 제 1항에 있어서, 상기 스티어링 소자를 형성하는 단계는 수직 다결정 다이오드를 형성하는 단계를 포함하는, 메모리 셀 형성 방법.

- 제 1항에 있어서, 상기 스티어링 소자를 형성하는 단계는, 다결정 재료가 낮은-저항률 상태로 존재하는 수직 다결정 다이오드를 형성하는 단계를 포함하는, 메모리 셀 형성 방법.

- 제 1항에 있어서, 상기 스티어링 소자를 형성하는 단계는 p-n 다이오드 또는 p-i-n 다이오드를 형성하는 단계를 포함하는, 메모리 셀 형성 방법.

- 제 1항에 있어서, 상기 스티어링 소자를 형성하는 단계는 박막 트랜지스터를 형성하는 단계를 포함하는, 메모리 셀 형성 방법.

- 제 1항에 있어서, 상기 스티어링 소자를 형성하는 단계는, 박막, 금속 산화물 반도체 전계 효과 트랜지스터(MOSFET)를 형성하는 단계를 포함하는, 메모리 셀 형성 방법.

- 제 1항에 있어서, 상기 가역 저항-스위칭 소자를 형성하는 단계는 NiO, NiOx 및 NiOxPy 중 적어도 하나를 형성하는 단계를 포함하는, 메모리 셀 형성 방법.

- 제 9항에 있어서, 상기 가역 저항-스위칭 소자를 형성하는 단계는 1000 옹스트롬 이하의 산화물 두께를 갖는 가역 저항-스위칭 소자를 형성하는 단계를 포함하는, 메모리 셀 형성 방법.

- 제 10항에 있어서, 상기 가역 저항-스위칭 소자를 형성하는 단계는 500 옹스트롬 이하의 산화물 두께를 갖는 가역 저항-스위칭 소자를 형성하는 단계를 포함하는, 메모리 셀 형성 방법.

- 제 1항에 있어서, 상기 가역 저항-스위칭 소자를 형성하는 단계는 니켈 함유 층을 선택적으로 형성하는 단계를 포함하는, 메모리 셀 형성 방법.

- 제 12항에 있어서, 상기 니켈 함유 층을 형성하는 단계는, NiO-, NiOx- 및 NiOxPy 함유 층을 선택적으로 형성하는 단계를 포함하는, 메모리 셀 형성 방법.

- 제 13항에 있어서, 상기 NiO-, NiOx- 및 NiOxPy 함유 층을 어닐링 또는 산화시키는 단계를 더 포함하는, 메모리 셀 형성 방법.

- 제 12항에 있어서, 상기 니켈 함유 층을 형성하는 단계는, Ni 또는 NixPy 층을 선택적으로 형성하는 단계와, 상기 Ni 또는 NixPy 층을 산화시키는 단계를 더 포함하는, 메모리 셀 형성 방법.

- 제 13항에 있어서, 상기 니켈 함유 층을 형성하는 단계는 상기 니켈 함유 층을 비전해적으로 증착하는 단계를 포함하는, 메모리 셀 형성 방법.

- 제 13항에 있어서, 상기 니켈 함유 층을 형성하는 단계는 전기도금을 이용하여 상기 니켈 함유 층을 형성하는 단계를 포함하는, 메모리 셀 형성 방법.

- 제 1항에 있어서, 상기 스티어링 소자와 가역 저항-스위칭 소자를 직렬로 결합하는 단계를 더 포함하는, 메모리 셀 형성 방법.

- 제 1항의 방법을 사용하여 형성된 메모리 셀.

- 제 9항의 방법을 사용하여 형성된 메모리 셀.

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 제 1항에 있어서, 상기 가역 저항-스위칭 소자를 형성하는 단계는, Ta2O5, Nb2O5, Al2O3, V2O5, CoO, (CoxNiy)Oz, 및 TiO2 중 적어도 하나를 형성하는 단계를 포함하는, 메모리 셀 형성 방법.

- 메모리 셀로서,스티어링 소자(steering element)와,상기 스티어링 소자에 결합되고 선택 성장 공정(selective growth process)을 이용하여 형성된 가역 저항-스위칭 소자를포함하는, 메모리 셀.

- 제 40항에 있어서, 상기 스티어링 소자는 다이오드를 포함하는, 메모리 셀.

- 제 41항에 있어서, 상기 다이오드는 수직 다결정 다이오드(polycrystalline diode)를 포함하는, 메모리 셀.

- 제 42항에 있어서, 상기 수직 다결정 다이오드는 낮은-저항률 상태로 존재하는 다결정 재료를 포함하는, 메모리 셀.

- 제 41항에 있어서, 상기 다이오드는 p-n 다이오드 또는 p-i-n 다이오드를 포함하는, 메모리 셀.

- 제 40항에 있어서, 상기 스티어링 소자는 박막 트랜지스터(thin film transistor)를 포함하는, 메모리 셀.

- 제 45항에 있어서, 상기 트랜지스터는 금속 산화물 반도체 전계 효과 트랜지스터(MOSFET)를 포함하는, 메모리 셀.

- 제 40항에 있어서, 상기 가역 저항-스위칭 소자는, NiO, NiOx, 및 NiOxPy 중 적어도 하나를 포함하는, 메모리 셀.

- 제 47항에 있어서, 상기 가역 저항-스위칭 소자는 1000 옹스트롬 이하의 산화물 두께를 갖는, 메모리 셀.

- 제 47항에 있어서, 상기 가역 저항-스위칭 소자는 500 옹스트롬 이하의 산화물 두께를 갖는, 메모리 셀.

- 제 40항에 있어서, 니켈 함유 층을 더 포함하고, 상기 가역 저항-스위칭 소자는 상기 니켈 함유 층을 산화시키거나 어닐링하여 형성되는, 메모리 셀.

- 제 50항에 있어서, 상기 니켈 함유 층은 비전해 증착 또는 전기도금 공정을 사용하여 선택적으로 증착되는, 메모리 셀.

- 제 40항에 있어서, 상기 스티어링 소자와 가역 저항-스위칭 소자는 직렬로 결합되는, 메모리 셀.

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 제 40항에 있어서, 상기 가역 저항-스위칭 소자는, Ta2O5, Nb2O5, Al2O3, V2O5, CoO, (CoxNiy)Oz 및 TiO2 중 적어도 하나를 형성하는 단계를 포함하는, 메모리 셀.

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/772,084 US8233308B2 (en) | 2007-06-29 | 2007-06-29 | Memory cell that employs a selectively deposited reversible resistance-switching element and methods of forming the same |

| US11/772,084 | 2007-06-29 | ||

| US11/772,090 US7846785B2 (en) | 2007-06-29 | 2007-06-29 | Memory cell that employs a selectively deposited reversible resistance-switching element and methods of forming the same |

| US11/772,090 | 2007-06-29 | ||

| PCT/US2008/007986 WO2009005700A2 (en) | 2007-06-29 | 2008-06-27 | Memory cell that employs a selectively deposited reversible resistance-switching element and methods of forming the same |

Related Child Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020147008191A Division KR20140061468A (ko) | 2007-06-29 | 2008-06-27 | 선택적으로 증착된 가역 저항-스위칭 소자를 사용하는 메모리 셀과 상기 메모리 셀을 형성하는 방법 |

| KR1020147008185A Division KR101494335B1 (ko) | 2007-06-29 | 2008-06-27 | 선택적으로 증착된 가역 저항-스위칭 소자를 사용하는 메모리 셀과 상기 메모리 셀을 형성하는 방법 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20100038317A KR20100038317A (ko) | 2010-04-14 |

| KR101447176B1 true KR101447176B1 (ko) | 2014-10-08 |

Family

ID=39791399

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020147008185A KR101494335B1 (ko) | 2007-06-29 | 2008-06-27 | 선택적으로 증착된 가역 저항-스위칭 소자를 사용하는 메모리 셀과 상기 메모리 셀을 형성하는 방법 |

| KR1020097027303A KR101447176B1 (ko) | 2007-06-29 | 2008-06-27 | 선택적으로 증착된 가역 저항-스위칭 소자를 사용하는 메모리 셀과 상기 메모리 셀을 형성하는 방법 |

| KR1020147008191A KR20140061468A (ko) | 2007-06-29 | 2008-06-27 | 선택적으로 증착된 가역 저항-스위칭 소자를 사용하는 메모리 셀과 상기 메모리 셀을 형성하는 방법 |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020147008185A KR101494335B1 (ko) | 2007-06-29 | 2008-06-27 | 선택적으로 증착된 가역 저항-스위칭 소자를 사용하는 메모리 셀과 상기 메모리 셀을 형성하는 방법 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020147008191A KR20140061468A (ko) | 2007-06-29 | 2008-06-27 | 선택적으로 증착된 가역 저항-스위칭 소자를 사용하는 메모리 셀과 상기 메모리 셀을 형성하는 방법 |

Country Status (6)

| Country | Link |

|---|---|

| EP (2) | EP2162916B1 (ko) |

| JP (1) | JP5624463B2 (ko) |

| KR (3) | KR101494335B1 (ko) |

| CN (1) | CN101720506B (ko) |

| TW (1) | TWI433276B (ko) |

| WO (1) | WO2009005700A2 (ko) |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4829320B2 (ja) * | 2009-03-17 | 2011-12-07 | 株式会社東芝 | 不揮発性半導体記憶装置の製造方法 |

| JP2010225741A (ja) | 2009-03-23 | 2010-10-07 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP4875118B2 (ja) * | 2009-03-24 | 2012-02-15 | 株式会社東芝 | 不揮発性記憶装置の製造方法 |

| US7927977B2 (en) * | 2009-07-15 | 2011-04-19 | Sandisk 3D Llc | Method of making damascene diodes using sacrificial material |

| JP5161911B2 (ja) | 2010-03-25 | 2013-03-13 | 株式会社東芝 | 抵抗変化メモリ |

| CN102314940B (zh) * | 2010-07-07 | 2014-04-23 | 旺宏电子股份有限公司 | 具有晶体管与电阻值切换装置并联的非挥发性存储器装置 |

| JP5611903B2 (ja) * | 2011-08-09 | 2014-10-22 | 株式会社東芝 | 抵抗変化メモリ |

| JP5279879B2 (ja) * | 2011-08-09 | 2013-09-04 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| JP2013069922A (ja) | 2011-09-22 | 2013-04-18 | Toshiba Corp | 不揮発性半導体記憶装置の製造方法及び不揮発性半導体記憶装置 |

| JP5818679B2 (ja) | 2011-12-27 | 2015-11-18 | 株式会社東芝 | 半導体装置の製造方法 |

| JP5606478B2 (ja) * | 2012-03-22 | 2014-10-15 | 株式会社東芝 | 半導体記憶装置 |

| WO2015072958A1 (en) * | 2013-11-12 | 2015-05-21 | Hewlett-Packard Development Company, L.P. | Nonlinear memristor devices with three-layer selectors |

| CN111106238B (zh) * | 2019-11-19 | 2023-08-29 | 中山大学 | 一种基于金属掺杂的双向阈值选通器及其制备方法 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20040104967A (ko) * | 2003-06-03 | 2004-12-14 | 삼성전자주식회사 | 한 개의 스위칭 소자와 한 개의 저항체를 포함하는비휘발성 메모리 장치 및 그 제조 방법 |

| KR100717286B1 (ko) | 2006-04-21 | 2007-05-15 | 삼성전자주식회사 | 상변화 물질층의 형성 방법과, 그 방법을 이용한 상변화기억 소자의 형성 방법 및 상변화 기억 소자 |

| KR20070062435A (ko) * | 2005-12-12 | 2007-06-15 | 히다치 글로벌 스토리지 테크놀로지스 네덜란드 비.브이. | 단극 저항 램 장치 및 수직 스택 구조 |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5915167A (en) | 1997-04-04 | 1999-06-22 | Elm Technology Corporation | Three dimensional structure memory |

| US6034882A (en) * | 1998-11-16 | 2000-03-07 | Matrix Semiconductor, Inc. | Vertically stacked field programmable nonvolatile memory and method of fabrication |

| US7102150B2 (en) * | 2001-05-11 | 2006-09-05 | Harshfield Steven T | PCRAM memory cell and method of making same |

| US6545287B2 (en) * | 2001-09-07 | 2003-04-08 | Intel Corporation | Using selective deposition to form phase-change memory cells |

| US7109056B2 (en) * | 2001-09-20 | 2006-09-19 | Micron Technology, Inc. | Electro-and electroless plating of metal in the manufacture of PCRAM devices |

| US7176064B2 (en) | 2003-12-03 | 2007-02-13 | Sandisk 3D Llc | Memory cell comprising a semiconductor junction diode crystallized adjacent to a silicide |

| AU2003296988A1 (en) | 2002-12-19 | 2004-07-29 | Matrix Semiconductor, Inc | An improved method for making high-density nonvolatile memory |

| US7189626B2 (en) * | 2004-11-03 | 2007-03-13 | Micron Technology, Inc. | Electroless plating of metal caps for chalcogenide-based memory devices |

| JP2008060091A (ja) * | 2005-01-14 | 2008-03-13 | Matsushita Electric Ind Co Ltd | 抵抗変化素子 |

| US7812404B2 (en) * | 2005-05-09 | 2010-10-12 | Sandisk 3D Llc | Nonvolatile memory cell comprising a diode and a resistance-switching material |

| JP4364180B2 (ja) * | 2005-08-17 | 2009-11-11 | 株式会社東芝 | 集積回路装置の製造方法 |

| ATE480873T1 (de) * | 2005-12-20 | 2010-09-15 | Nxp Bv | Vertikale phasenwechsel-speicherzelle und herstellungsverfahren dafür |

| WO2008097742A1 (en) * | 2007-02-05 | 2008-08-14 | Interolecular, Inc. | Methods for forming resistive switching memory elements |

| CN102709471B (zh) * | 2007-06-29 | 2014-12-24 | 桑迪士克3D公司 | 利用选择性生长的可逆电阻切换元件的存储器单元以及形成该存储器单元的方法 |

-

2008

- 2008-06-27 WO PCT/US2008/007986 patent/WO2009005700A2/en active Application Filing

- 2008-06-27 EP EP08779800A patent/EP2162916B1/en active Active

- 2008-06-27 CN CN200880022647.7A patent/CN101720506B/zh active Active

- 2008-06-27 KR KR1020147008185A patent/KR101494335B1/ko not_active IP Right Cessation

- 2008-06-27 KR KR1020097027303A patent/KR101447176B1/ko active IP Right Grant

- 2008-06-27 KR KR1020147008191A patent/KR20140061468A/ko not_active Application Discontinuation

- 2008-06-27 JP JP2010514824A patent/JP5624463B2/ja not_active Expired - Fee Related

- 2008-06-27 TW TW097124473A patent/TWI433276B/zh not_active IP Right Cessation

- 2008-06-27 EP EP12166461.9A patent/EP2485258B1/en active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20040104967A (ko) * | 2003-06-03 | 2004-12-14 | 삼성전자주식회사 | 한 개의 스위칭 소자와 한 개의 저항체를 포함하는비휘발성 메모리 장치 및 그 제조 방법 |

| KR20070062435A (ko) * | 2005-12-12 | 2007-06-15 | 히다치 글로벌 스토리지 테크놀로지스 네덜란드 비.브이. | 단극 저항 램 장치 및 수직 스택 구조 |

| KR100717286B1 (ko) | 2006-04-21 | 2007-05-15 | 삼성전자주식회사 | 상변화 물질층의 형성 방법과, 그 방법을 이용한 상변화기억 소자의 형성 방법 및 상변화 기억 소자 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5624463B2 (ja) | 2014-11-12 |

| EP2485258B1 (en) | 2014-03-26 |

| EP2162916B1 (en) | 2013-03-20 |

| WO2009005700A2 (en) | 2009-01-08 |

| EP2485258A2 (en) | 2012-08-08 |

| WO2009005700A3 (en) | 2009-02-26 |

| KR20140061467A (ko) | 2014-05-21 |

| CN101720506A (zh) | 2010-06-02 |

| KR20140061468A (ko) | 2014-05-21 |

| JP2010532569A (ja) | 2010-10-07 |

| EP2162916A2 (en) | 2010-03-17 |

| KR20100038317A (ko) | 2010-04-14 |

| EP2485258A3 (en) | 2012-08-22 |

| TWI433276B (zh) | 2014-04-01 |

| TW200913171A (en) | 2009-03-16 |

| KR101494335B1 (ko) | 2015-02-23 |

| CN101720506B (zh) | 2012-05-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7846785B2 (en) | Memory cell that employs a selectively deposited reversible resistance-switching element and methods of forming the same | |

| US8233308B2 (en) | Memory cell that employs a selectively deposited reversible resistance-switching element and methods of forming the same | |

| KR101447176B1 (ko) | 선택적으로 증착된 가역 저항-스위칭 소자를 사용하는 메모리 셀과 상기 메모리 셀을 형성하는 방법 | |

| US8507315B2 (en) | Memory cell that employs a selectively grown reversible resistance-switching element and methods of forming the same | |

| US7902537B2 (en) | Memory cell that employs a selectively grown reversible resistance-switching element and methods of forming the same | |

| KR101494746B1 (ko) | 선택적으로 제조된 탄소 나노 튜브 가역 저항 전환 소자를 사용하는 메모리 셀과 이를 형성하는 방법 | |

| US8981347B2 (en) | Memory cell that includes a sidewall collar for pillar isolation and methods of forming the same | |

| KR20100031698A (ko) | 선택적으로 성장한 가역 저항-스위칭 소자를 사용하는 메모리 셀과 상기 메모리 셀을 형성하는 방법 | |

| US20140252298A1 (en) | Methods and apparatus for metal oxide reversible resistance-switching memory devices |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| A107 | Divisional application of patent | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20180903 Year of fee payment: 5 |