以下に、本開示の実施の形態について、図面を参照して詳細に説明する。なお、以下では、図中の同一又は相当部分には同一符号を付して、その説明は原則的に繰返さないものとする。

以下に、本開示の実施の形態について、図面を参照して詳細に説明する。なお、以下では、図中の同一又は相当部分には同一符号を付して、その説明は原則的に繰返さないものとする。

実施の形態1.

図1には、実施の形態1に係るアナログ電圧出力回路を備える半導体装置の構成例を説明する回路図が示される。

図1に示される様に、実施の形態1に係る半導体装置10Aは、アナログ電圧を出力するアナログ回路100と、アナログ回路100の出力電圧VOUT(アナログ電圧)を、半導体装置10Aの外部から測定するためのアナログ電圧出力回路200とを備える。

(アナログ回路について)

まず、アナログ回路100について説明する。アナログ回路100は、半導体装置10Aの試験時に、半導体装置10Aの外部からの測定対象となるアナログ電圧を出力電圧とする回路を総称するものであり、本実施の形態では、一定電圧を出力するバンドギャップリファレンスが、アナログ回路100の一例として記載される。

具体的には、アナログ回路100は、P型のトランジスタMP1~MP3と、N型のトランジスタMN1,MN2と、抵抗素子R1,Roと、ダイオードD1~D3とを含む。

トランジスタMP1は、電源電圧AVDD1を供給する電源ノードNP1と、ノードNs1との間に接続され、トランジスタMP2は、電源ノードNP1と、ノードNs2との間に接続される。トランジスタMP1及びMP2のゲートは、ノードNs1と接続される。これにより、トランジスタMP1は、ダイオード接続される。以下、本明細書では、各抵抗素子の電気抵抗値についても同じ符号を用いて表記する。例えば、抵抗素子R0の電気抵抗値もR0と表記される。

トランジスタMN1、抵抗素子R1、及び、ダイオードD1は、ノードNs1と、基準電圧AVSSを供給する基準電圧ノードNGとの間に接続される。基準電圧AVSSは、代表的には、接地電圧(GND)であり、AGND<AVDD1である。トランジスタMN2及びダイオードD2は、ノードNs2及び基準電圧ノードNGの間に直列に接続される。ダイオードD1及びD2のカソードは、基準電圧ノードNGと電気的に接続される。トランジスタMN1及びMN2のゲートは、ノードNs2と接続される。これにより、トランジスタMN2はダイオード接続される。

トランジスタMP3は、電源ノードNP1及び出力ノードNoの間に接続される。抵抗素子Ro及びダイオードD3は、出力ノードNo及び基準電圧ノードNGの間に直列に接続される。ダイオードD3のカソードは、基準電圧ノードNGと電気的に接続される。直列接続された、トランジスタMP3、抵抗素子Ro、及び、ダイオードD3によって、アナログ回路100の「出力段」が構成される。

トランジスタMP1~MP3のゲートは、ノードNs1と共通に接続される。従って、トランジスタMP1~MP3の電流は、ダイオード接続されたトランジスタMP1の電流を基準として、互いに比例する。又、トランジスタMN1及びMN2は同じトランジスタサイズで構成される。

ダイオードD1は、ダイオードD2のM倍(M>1)のカソード面積を有する様に構成される。或いは、ダイオードD1は、ダイオードD2と同一サイズのダイオードをM個並列接続する様に構成してもよい。この場合には、Mは2以上の整数である。

次に、図1のアナログ回路100の動作を説明する。

一般的に、十分に順バイアスされて順方向電圧Vdが発生している状態でのダイオードの電流Idは、逆方向飽和電流Is、ボルツマン定数k、温度T[K]、電荷素量q、及び、結合係数nを用いて、下記の式(1)で近似できることが知られている。

Id=Is・exp(q・Vd/(n・k・T)) …(1)

結合係数nは、理論的には1.0であるので、熱電圧VT=k・T/qを用いて、式(1)を変形すると、導通時のダイオードの順方向電圧Vdとして、下記の式(2)が得られる。

Vd≒VT・ln(Id/Is) …(2)

従って、図1のアナログ回路100において、トランジスタMN1を流れる電流をI1、トランジスタMN2を流れる電流をI2とすると、ダイオードD2に生じる順方向電圧Vd2=VT・ln(I2/Is)、ダイオードD1に生じる順方向電圧Vd1=VT・ln(I1/(M・Is))と示すことができる。

図1のアナログ回路において、トランジスタMN1のゲート電圧Vg1は、ゲート・ソース間電圧Vgs1、及び、電流I1を用いると、下記の式(3)で示される。

Vg1=Vd1+I1・R1+Vgs1 …(3)

同様に、トランジスタMN2のゲート電圧Vg2は、ゲート・ソース間電圧Vgs2、及び、電流I2を用いると、下記の式(4)で示される。

Vg2=Vd2+Vgs2 …(4)

トランジスタMN1及びMN2のトランジスタサイズが同じであるため、I1=I2(=Ic)が成立し、I1=I2から、更にトランジスタMN1及びMN2の間でVgs1=Vgs2も成立する。更に、トランジスタMN1及びMN2のゲート同士が接続されているため、Vg1=Vg2である。

Vg1=Vg2、Vgs1=Vgs2、かつ、I1=I2=Icの条件にて、式(3),(4)を整理すると、下記の式(5)が得られる。

Ic・R1+VT・ln(Ic/(M・Is))=VT・ln(Ic/Is)…(5)

式(5)の左辺第2項を右辺に移項して、Ic(Ic=I1=I2)を求めると、下記の式(6)が得られる。

Ic=(VT/R1)・ln(M) …(6)

更に、トランジスタMP1~MP3のトランジスタサイズを同等に設計すると、トランジスタMP3を流れる電流Ioは、Io=I1となる。従って、ダイオードD3の順方向電圧をVd3とすると、出力ノードNoの出力電圧VOUT=Vd3+Ic・Roは、下記の式(7)で示すことができる。

VOUT=Vd3+VT・(Ro/R1)・ln(M) …(7)

順方向電圧Vd3が、負の温度係数(例えば、-2[mV/deg])を有する一方で、熱電圧VTは、正の温度係数(例えば、0.085[mV/deg])を有することが知られている。従って、抵抗素子R0,Ro及び電流比Mの適切な選定によって、出力電圧VOUTの温度特性をキャンセルすることが可能である。この結果、アナログ回路100は、温度変動に対して不変の一定電圧を出力する、バンドギャップリファレンスとして動作することができる。例えば、アナログ回路100の出力電圧VOUTは、半導体装置10Aの内部の図示しない他の回路に対して、バイアス電圧として供給される。

ここで、出力電圧VOUTを半導体装置10Aの外部から試験のために測定する構成を考察する。

比較例として、半導体装置10Aの外部から電気的にコンタクト可能な測定端子11(パッド)と、出力ノードNoとを直接接続し、測定端子11の電圧をテスタによって測定する試験モードを考える。通常、テスタによる測定時には、測定端子11と接続されるプローブ、及び、測定端子11の寄生容量が、合計で数[pF]程度付加される。

従来のバッドギャップリファレンス回路では、出力段の抵抗素子Roは100[kΩ]オーダで設計される。このため、テスタ測定時のCR時定数は数百[ns]のオーダである。一般的には、テスタによる測定電圧が安定するまでには、上記時定数の3~5倍のセトリング時間を要するため、テスタ接続から電圧測定までの待ち時間が発生する。この場合には、待ち時間は、1~2[μs]となるが、近年の複雑なICの試験時間にはトータルで10[ms]程度を要する傾向にあることを考慮すると、試験全体の所要時間に当たれる影響は小さい。

一方で、出力段の抵抗素子Roが100[kΩ]オーダで構成されたバンドギャップリファレンスは、消費電流がμAオーダであるのに対して、近年のIoTの下では、低消費電力化に対応するために、バイアス用回路には、消費電流をnAオーダに(即ち、3桁)抑制することが求められる。

この様な要求に応えるためには、図1中の抵抗素子R1,Roの電気抵抗値を3桁大きくして、100[MΩ]オーダとすることが必要になる。しかしながら、出力段の抵抗素子Roが100[MΩ]オーダと高インピーダンス化されることで、テスタ測定時のCR時定数も1000倍となり、上記待ち時間も1~2[ms]まで増加する。この結果、アナログ回路100の出力電圧VOUT(アナログ電圧)の測定時間が、半導体装置の試験の全体所要時間に影響を及ぼすことが懸念される。

従って、本実施の形態では、半導体装置10Aの外部から、極低消費電力化のために高出力インピーダンスとされたアナログ回路100の出力電圧VOUTを、高精度かつ高速に測定するためのアナログ電圧出力回路200が、アナログ回路100に対して設けられる。

(アナログ電圧出力回路の説明)

アナログ電圧出力回路200は、半導体装置10Aの外部から電気的にコンタクト可能な端子12,13と、アナログ回路100との間に配置される。以下の説明で明らかになる様に、本実施の形態では、端子12には、アナログ電圧出力回路200によって、アナログ回路100の出力電圧VOUTと同等の出力電圧VOUTtsが、半導体装置10Aの外部からの測定用に出力される。以下では、端子12については、出力端子12とも称する。即ち、出力端子12に図示しないテスタを接続することで、半導体装置10Aの外部から、アナログ回路100の出力電圧VOUTを測定する試験モードを設けることができる。

一方で、端子13に対しては、半導体装置10Aの外部から、アナログ電圧出力回路200の動作に用いられる信号又は電圧が入力される。従って、以下では、端子13は、入力端子13とも称する。実施の形態1では、入力端子13には、クロック信号TCLKが入力される。

アナログ電圧出力回路200は、スイッチSW0~SW2と、キャパシタ201と、駆動トランジスタ202Aとを備える。駆動トランジスタ202Aは、電源ノードNP2と接続されるドレインと、出力端子12と接続されるノードN4に接続されたソースと、ノードN2に接続されるゲートとを有する。電源ノードNP2は、電源電圧AVDD2を供給する。好ましくは、AVDD2(電源ノードNP2)は、AVDD1(電源ノードNP1)よりも高く設定されるが、電源ノードNP1及びNP2を共通化(即ち、AVDD1=AVDD2)とすることも可能である。

駆動トランジスタ202Aは、ネイティブNMOSトランジスタによって構成される。公知の通り、ネイティブNMOSトランジスタのしきい値電圧Vtは、0[V]近傍であり、理想的には、Vt=0である。

キャパシタ201は、ノードN2(即ち、駆動トランジスタ202Aのゲート)及びノードN3の間に接続される。スイッチSW0は、アナログ回路100の出力ノードNoと接続されたノードN1と、ノードN2(駆動トランジスタ202Aのゲート)との間に接続される。スイッチSW1は、ノードN1及びノードN3の間に接続される。スイッチSW2は、ノードN3及びN4の間に接続される。

スイッチSW0~SW2は、クロック信号TCLKに従ってスイッチ制御回路208が生成する制御信号φa,φbに応答してオンオフされる。具体的には、スイッチSW0,SW2が制御信号φaにオンオフされる一方で、スイッチSW1は、制御信号φaと逆相の制御信号φbに応答してオンオフされる。

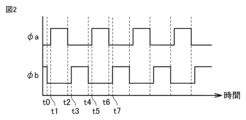

図2には、アナログ電圧出力回路200内のスイッチSW0~SW2の動作を説明するためのタイミングチャートが示される。

図2に示される様に、制御信号φa及びφbは、入力端子13に入力されるクロック信号TCLKに基づく、ノンオーバラッピングクロックとして生成される。即ち、制御信号φa及びφbは、クロック信号TCLKの周波数に従って、交互に論理ハイレベル(以下、単に「Hレベル」と表記)及び論理ローレベル(以下、単に「Lレベル」と表記)の間の遷移を繰り返す。

更に、制御信号φa及びφbには、両方がLレベルに設定されるノンオーバラップ期間(図2中の時刻t0~t1、時刻t2~t3、時刻t4~t5、及び、時刻t6~t7等)が設けられる。

図3には、クロック信号TCLKから制御信号φa,φbを生成するスイッチ制御回路208の構成例が示される。

図3に示される様に、スイッチ制御回路208は、NORゲート211a,211bと、インバータ段212a,212bとを有する。インバータ段212a,212bの各々は、直列接続された偶数個のインバータによって構成される。インバータ段212aは、制御信号φaを出力し、インバータ段212bは、制御信号φbを出力する。

NORゲート211aには、クロック信号TCLKと、インバータ段212bの出力信号とが入力される。NORゲート211aの出力信号は、インバータ段212aに入力される。NORゲート211bには、クロック信号TCLKの反転信号と、インバータ段212aの出力信号とが入力される。NORゲート211bの出力信号は、インバータ段212bに入力される。

この結果、図2に示される様に、制御信号φa及びφbは、ノンオーバラップ期間が設けられた上で、クロック信号TCLKと同じ周期で、交互にLレベル及びHレベルに設定される。ノンオーバラップ期間の長さは、インバータ段212a,212bによる伝送遅延時間に相当するので、インバータの個数(偶数)によって調整することができる。

尚、アナログ電圧出力回路200にスイッチ制御回路208を内蔵する構成に代えて、入力端子13を2個設けて、半導体装置10Aの外部からノンオーバラッピングクロックを入力することで、アナログ電圧出力回路200に制御信号φa,φbを直接供給してもよい。

制御信号φa,φbを用いてスイッチSW0~SW3のオンオフを制御することにより、クロック信号TCLKの周期に応じて、スイッチSW0,SW2がオン(スイッチSW1はオフ)される「第1の状態」と、スイッチSW1がオン(スイッチSW0,SW2はオフ)される「第2の状態」とが交互に設けられ、かつ、「第1の状態」及び「第2の状態」の間には、SW0~SW2の各々がオフされるノンオーバラップ期間が設けられることが理解される。当該ノンオーバラップ期間は「第3の状態」に対応する。

再び図1を参照して、スイッチSW0,SW2がオン(スイッチSW1はオフ)される第1の状態では、アナログ回路100の出力電圧VOUTが、ノードN1及びN2を経由して、駆動トランジスタ202Aのゲートに伝達される。従って、駆動トランジスタ202Aのソースと接続された出力端子12の出力電圧VOUTtsは、駆動トランジスタ202Aのしきい値電圧Vtを用いて、VOUTts=VOUT-Vtと示される。理想的なネイティブNMOSトランジスタではVt=0であるので、このとき、VOUTts=VOUTとすることができる。

しかしながら、しきい値電圧に製造ばらつき(ΔVt)が生じると、Vt=0+ΔVt≠0となるので、VOUTts=VOUT-Vt(Vt=ΔV)となって、しきい値電圧の影響による測定誤差が生じてしまう。一方で、第1の状態では、スイッチSW0,SW2のオンにより、キャパシタ201が、ノードN4及びN2の間、即ち、駆動トランジスタ202Aのゲート・ソース間に接続される。これにより、容量値Csを有するキャパシタ201は、このときにゲート及びソースの間の電圧差に応じた、Qc=Vt・Cs(ΔV・Cs)の電荷を保持した状態となる。

次に、スイッチSW1がオン(SW0,SW2がオフ)される第2の状態では、駆動トランジスタ202Aのゲートは、ノードN1(出力ノードNo)及びノードN4(出力端子12)から切り離される。一方で、キャパシタ201の負極側は、ノードN1(出力ノードNo)と接続されて、アナログ回路100の出力電圧VOUTを伝達される。

第1の状態及び第2の状態のそれぞれにおける出力端子12の出力電圧をVOUTts(1)及びVOUTts(2)と表記するとともに、第1及び第2の状態のそれぞれにおけるキャパシタ201の蓄積電荷をQc(1)及びQc(2)と表記すると、第1の状態では、下記の式(8),(9)が成立するとともに、第2の状態では、下記の式(10),(11)が成立する。式(10),(11)中の電圧Vxは、第2の状態において、ノードN1及びN4の両方と切り離された状態におけるノードN2の電圧、即ち、駆動トランジスタ202Aのゲート電圧を示している。

VOUTts(1)=VOUT-Vt …(8)

Qc(1)=Cs・(VOUT-VOUTts(1)) …(9)

VOUTts(2)=Vx-Vt …(10)

Qc(2)=Cs・(Vx-VOUT) …(11)

ここで、電荷保存則により、式(9)のQc(1)と、式(11)のQc(2)とは等しいから、下記の式(12)が成立する。

VOUT-VOUTts(1)=Vx-VOUT …(12)

式(12)をVxについて解くと、下記の式(13)が得られる。

Vx=2・VOUT-VOUTts(1)=VOUT+Vt …(13)

式(13)を式(10)に代入すると、式(14)が得られる。

VOUTts(2)=Vx-(Vx-VOUT)=VOUT …(14)

従って、第2の状態での出力端子12の出力電圧VOUTts(2)は、駆動トランジスタ202Aのしきい値電圧の影響が排除されて、アナログ回路100の出力電圧VOUTと同等となることが理解される。即ち、駆動トランジスタ202Aとして配置されたネイティブNMOSトランジスタのしきい値電圧Vtが、設計値であるVt*=0からΔV変動して、Vt=ΔVとなっても、しきい値電圧の変動分を相殺して、出力電圧VOUTと同等の電圧を、駆動トランジスタ202Aのゲート、即ち、出力端子12に発生することができる。

言い換えると、アナログ電圧出力回路200は、第1の状態では、ゲートに出力電圧VOUTが入力されたときの駆動トランジスタ202Aのゲート及びソースの電圧差(正又は負のいずれも可)をキャパシタ201に保持する。更に、第2の状態では、出力電圧VOUTに対して、キャパシタ201に保持された電圧を加算した電圧をゲートに入力することで、ゲート電圧及びソース電圧が等しくなる様な駆動トランジスタ202Aの動作状態を設定することができる。即ち、実施の形態1では、キャパシタ201及びスイッチSW0~SW3によって「駆動トランジス制御回路」の一実施例を構成することができる。

尚、図1のアナログ電圧出力回路において、ノードN1は「入力ノード」の一実施例に対応し、ノードN3は「内部ノード」の一実施例に対応し、出力端子12は「第1の端子」の一実施例に対応する。又、スイッチSW0、スイッチSW1、及び、スイッチSW2は、「第1のスイッチ」、「第2のスイッチ」、及び、「第3のスイッチ」の一実施例にそれぞれ対応する。

以上説明した様に、実施の形態1に係る半導体装置10Aでは、アナログ電圧出力回路200によって、試験時のみに用いられる駆動トランジスタ202Aの電流によって、出力電圧VOUTと同等の電圧を出力端子12に出力することで、当該出力電圧VOUTを外部から測定する試験モードを実現することができる。特に、スイッチSW0~SW2及びキャパシタ201を用いた制御によって、駆動トランジスタ202Aのしきい値電圧の影響が取り除かれた、出力電圧VOUTとの誤差が小さい電圧を、駆動トランジスタ202Aから高精度に出力することができる。

ノンオーバラッピングクロックである制御信号φa及びφbを用いることで、以下の効果が生じる。まず、第1の状態及び第2の状態を繰り返し設けることにより、キャパシタ201に生じるリーク電流の影響を抑制して、出力端子12の出力電圧を安定化することができる。更に、第1の状態及び第2の状態の間での遷移の際に、スイッチSW0~SW2の全てをオフする第3の状態の期間(ノンオーバラップ期間)を設けることによって、第1の状態及び第2の期間のそれぞれでの電荷Qcが、ノードN2から流出することなく保持される。これにより、電荷保存則を厳密化することで、出力電圧VOUT及び出力電圧VOUTtsの差を抑制して高精度化を図ることができる。尚、クロック信号TCKの周波数は、キャパシタ201の充電に要する時間よりも、制御信号φa,φbの各Hレベル期間が長くなる様に考慮して定めることができる。

更に、アナログ電圧出力回路200の出力インピーダンスは、駆動トランジスタ202Aの出力インピーダンスに相当し、通常、数十[kΩ]程度であるので、上述した、比較例に係るアナログ回路100の出力段の抵抗素子Roの電気抵抗値(100[kΩ]オーダ)と同等かそれよりも低い。このため、テスタ測定時に数[pF]程度の寄生容量が付加された際のCR時定数は数十[ns]程度である。この結果、セトリング時間を100[ns]オーダに短縮できるので、測定時の待ち時間は1[μs]以下に短縮できる。この結果、アナログ回路100の出力電圧VOUT(アナログ電圧)の測定時間が、半導体装置の試験の全体所要時間に及ぼす影響を大幅に抑制することができる。

この様に、実施の形態1に係る半導体装置10Aでは、nAオーダに設計された極低消費電力のアナログ回路100の出力電圧VOUTを、駆動トランジスタ202Aを有するアナログ電圧出力回路200を用いて高速に、具体的には、nsオーダのセトリング時間にて測定することができる。この際に、アナログ電圧出力回路200は、駆動トランジスタ202Aの素子ばらつき(しきい値電圧のばらつき)の影響を排除して、アナログ回路100の出力電圧VOUTと同等の出力電圧VOUTtsを高精度に出力することができる。

アナログ電圧出力回路200は、半導体装置10Aの試験時において、上述の様に、入力端子13にクロック信号TCLKが入力されるとともに、出力端子12にテスタが接続されることで動作する。一方で、半導体装置10Aの試験時以外(半導体装置10Aの通常動作時)には、出力端子12が開放状態とされることより、駆動トランジスタ202Aに電流が生じなくなるので、アナログ電圧出力回路200は動作を停止する。この場合には、例えば、入力端子13に対して基準電圧AVSS相当の電圧(接地電圧)が固定的に入力される。

尚、アナログ電圧出力回路200の駆動トランジスタは、ネイティブNMOSに限定されることはない。図4には、実施の形態1に係るアナログ電圧出力回路を備える半導体装置の構成の変形例を説明する回路図が示される。

図4に示される様に、実施の形態1に係る半導体装置10Aにおいて、アナログ電圧出力回路200の駆動トランジスタ202A(図1)を、エンハンスメント型NMOSトランジスタで構成された駆動トランジスタ202Bに置換することも可能である。

エンハンスメント型NMOSトランジスタのしきい値電圧Vtについても、1[V]程度の設計値Vt*と変動分ΔVとの和(Vt=Vt*+ΔVt)で示される。従って、駆動トランジスタ202Bが適用されたアナログ電圧出力回路200においても、図1で説明した、スイッチSW0~SW2及びキャパシタ201の制御を適用することで、式(8)~式(14)が同様に成立する。この結果、図1で説明したのと同様に、アナログ回路100の出力電圧VOUTを、半導体装置10Aの出力端子12から、高精度に、かつ、高速に測定することができる。

但し、エンハンスメント型NMOSは、ネイティブNMOSトランジスタと比較すると、変動分ΔVtを含めてしきい値電圧Vtの絶対値が大きくなるため、アナログ電圧出力回路200中のキャパシタ201に保持される電荷量が多くなる。従って、キャパシタ201での当該電荷量の充電所要時間を考慮して、出力端子12の出力電圧VOUTtsの計測タイミングを遅くする必要がある。一方で、エンハンスメント型NMOSは、ネイティブNMOSトランジスタと比較すると、駆動能力が高いという利点を有する。

反対に、ネイティブNMOSトランジスタは、エンハンスメント型NMOSトランジスタと比較するとしきい値電圧Vtの絶対値が小さいため、上述したキャパシタ201での充電所要時間が短くなるので、測定の高速化に適している。一方で、駆動能力が低いので、低インピーダンス出力を要求されるような、アプリケーション及びテスタ等を用いることが難しいので、試験の自由度の面では不利になる。

又、エンハンスメント型NMOS及びネイティブNMOSトランジスタの中間的なしきい値電圧を有する、所謂、低Vt-NMOSトランジスタを、アナログ電圧出力回路200の駆動トランジスタ202(202A及び202Bを総称するもの)として用いることで、アナログ電圧出力回路200の特性を中間的にすることも可能である。但し、低Vt-NMOSは、製造時にマスク追加の必要があるので、アナログ電圧出力回路200の他の回路で低Vt-NMOSトランジスタが使用されない場合には、アナログ電圧出力回路200の配置に起因して、コストアップが発生することが懸念される。

又、図1から理解される様に、実施の形態1に係るアナログ電圧出力回路200では、キャパシタ201は、正のゲート電圧、及び、負のゲート電圧の両方を保持することができる。従って、駆動トランジスタ202A,202Bのしきい値電圧が正及び負のいずれであっても対応することができるので、デプレッション型のNMOSトランジスタによって、駆動トランジスタ202を構成することも可能である。

又、電源ノードNP2の電源電圧AVDD2を高く設定することで(AVDD2>AVDD1)、出力端子12にテスタ等が接続された状態において、出力電圧VOUT相当の電圧を発生するために駆動トランジスタ202A,202Bが供給する電流量が低減される。これにより、アナログ電圧出力回路200の消費電力を削減することができる。

この様に、実施の形態1に係るアナログ電圧出力回路200では、駆動トランジスタ202のしきい値電圧が正及び負のいずれであっても、半導体装置10Aにおいて、アナログ回路100の出力電圧VOUTと、第2の状態における出力端子12の出力電圧VOUTtsとを同等として、高速、かつ、高精度な電圧測定を実現することができる。

実施の形態1の変形例.

実施の形態1の構成では、アナログ電圧出力回路200において、キャパシタ201は、アナログ回路100の出力段の電流Io(枝電流)によって充電される。厳密には、駆動トランジスタのゲート容量も、キャパシタ201と並列に充電される。

この際に、極低消費電力のアナログ回路100の出力段の電流がnAオーダであることを考慮すると、キャパシタ201の充電に時間を要することが懸念される。例えば、駆動トランジスタ202による充電電流I=10[nA]、出力電圧VOUT=1[V]、かつ、キャパシタ201の容量及び駆動トランジスタ202のゲート容量の和をCsum=10[pF]とすると、Csum・VOUT=I・tを解いた、t=1[ms]程度が、出力端子12に接続されたテスタによる測定を開始するまでの準備時間として必要となってしまう。

図5は、実施の形態1の変形例に係るアナログ電圧出力回路を備える半導体装置の構成例を説明する回路図である。

図5に示される様に、実施の形態1の変形例に係る半導体装置10Bは、実施の形態1に係る半導体装置10Aと比較して、アナログ電圧出力回路200に代えて、アナログ電圧出力回路210を備える点で異なる。アナログ電圧出力回路210は、図1のアナログ電圧出力回路200に加えて、レプリカ回路300を更に備える点で異なる。又、図5では、駆動トランジスタ202A(図1)及び202B(図4)を包括して、駆動トランジスタ202と表記している。

レプリカ回路300は、アナログ電圧出力回路200のノードN1と、アナログ回路100との間に接続されて、キャパシタ201及び駆動トランジスタ202のゲートを高速に充電するために動作する。

レプリカ回路300は、P型のトランジスタMP5と、スイッチSW3a,SW3b,SW4a,SW4bと、抵抗素子R5と、ダイオードD5とを有する。トランジスタMP5は、電源ノードNP1及びノードN5の間に接続される。トランジスタMP5は、アナログ回路100の出力段のトランジスタMP3のK倍(K>1)のトランジスタサイズを有する。例えば、トランジスタMP5は、トランジスタMP3と同等のトランジスタサイズを有するPMOSトランジスタを、K個(K:2以上の整数)並列接続することによって構成できる。

抵抗素子R5及びダイオードD5は、ノードN5及び基準電圧ノードNGの間に直列接続される。ダイオードD5のカソードは、基準電圧ノードNGと電気的に接続される。

ダイオードD5は、アナログ回路100の出力段のダイオードD3と同等のダイオードをK個並列接続する様に構成される。反対に、抵抗素子R5の電気抵抗値は、アナログ回路100の出力段の抵抗素子Roの電気抵抗値(1/K)倍に設定される。

トランジスタMP5のゲートは、スイッチSW3aを介して、アナログ回路100のノードNs1と接続されるとともに、スイッチSW3bを介して、電源ノードNP1と接続される。スイッチSW4aは、ノードN5と、ノードN1との間に接続される。スイッチSW4bは、アナログ回路100の出力ノードNoと、ノードN1との間に接続される。

スイッチSW3a,SW4aは、制御信号SL1に応じてオンオフされる。スイッチSW3b,SW4bは、制御信号SL1を反転した制御信号SL2に応じてオンオフされる。従って、スイッチSW3a,SW4aのオン時には、スイッチSW3b,SW4bはオフされる。反対に、スイッチSW3b,SW4bのオン時には、スイッチSW3a,SW4aはオフされる。

図6には、アナログ電圧出力回路210の動作を説明するためのタイミングチャートが示される。

図6に示される様に、制御信号φa,φbの波形は、実施の形態1(図2)と同様である。レプリカ回路300の制御信号SL1は、試験開始時から予め定められた時間が経過する時刻txまでは、Hレベル(電源電圧AVDD1)に設定される一方で、時刻tx以降では、Lレベル(基準電圧AVSS)に設定される。反対に、制御信号SL2は、時刻txまでは、Lレベル(基準電圧AVSS)に設定される一方で、時刻tx以降では、Hレベル(電源電圧AVDD1)に設定される。

例えば、半導体装置10Aの試験開始時に入力されるトリガ信号と、図示しないタイマとを用いて、制御信号SL1,SL2を生成することができる。

再び、図5を参照して、レプリカ回路300は、制御信号SL1=Hレベル、かつ、制御信号SL2=Lレベルに設定された期間では、スイッチSW3a,SW4aがオンされ、スイッチSW3b,SW4bがオフされることで動作する。この状態では、トランジスタMP5のゲートが、トランジスタMP1~MP3と共通にノードNs1と接続され、ノードN5(即ち、トランジスタMP5のドレイン)が、ノードN1と接続される。

これにより、レプリカ回路300は、動作時において、アナログ回路100の出力段の電流IoのK倍のレプリカ電流Irpを、ノードN5に生じさせる。更に、抵抗素子R5の電気抵抗値が、抵抗素子Roの電気抵抗値の(1/K)倍であるので、ノードN5に出力されるレプリカ電圧Vrpは、式(7)と同様に、式(15)で示される。

Vrp=Vd5+K・Ic・R5

=Vd5+(Ro/K)・(K・VT・ln(M)/R1)

=Vd5+VT・(Ro/R1)・ln(M) …(15)

式(15)中において、ダイオードD5の順方向電圧Vd5は、ダイオードD5がダイオードD3の並列接続によって構成されることから、式(7)中の順方向電圧Vd3と同等である。

従って、式(15)及び式(7)の対比から、レプリカ電圧Vrpは、アナログ回路100の出力電圧VOUTと同等にできることが理解できる。実際には、素子ばらつきのよって、出力電圧VOUT及びレプリカ電圧Vrpの間には、50~100[mv]程度の電圧差が生じるが、後述する様に、出力電圧VOUT及びレプリカ電圧Vrpの間に、ある程度の電圧差は許容される。

実施の形態1の変形例に係るアナログ電圧出力回路210では、スイッチSW4aのオンによってノードN5がノードN1と接続されることにより、キャパシタ201は、アナログ回路100の出力段の電流I0のK倍のレプリカ電流Irpによって充電される。

これにより、電流I0によって上記容量Cを充電する場合と比較すると、充電に要する時間を(1/K)に短縮することができる。例えば、上記の様に、電流I0での充電に1[ms]を要する条件下で、K=100に設計すると、上述の容量Csumを10[μs]で充電することができる。

次に、レプリカ回路300は、制御信号SL1=Lレベル、かつ、制御信号SL2=Hレベルに設定された期間では、スイッチSW3b,SW4bがオンされ、スイッチSW3a,SW4aがオフされることで、動作を停止する。この停止時には、トランジスタMP5のゲートが電源ノードNP1(電源電圧AVDD1)と接続されるので、トランジスタMP5はオフされて、レプリカ電流Irpはゼロになる(Irp=0)。更に、ノードN5はノードN1から切り離されて、ノードN1は、アナログ回路100の出力ノードNoと接続される。即ち、レプリカ回路300がアナログ回路100及びアナログ電圧出力回路200から切り離されて、実施の形態1(図1)でのアナログ回路100及びアナログ電圧出力回路200の接続関係が再現される。

これにより、レプリカ回路300が動作を停止すると(Irp=0)、アナログ電圧出力回路210は、実施の形態1(図1)と同様に、出力端子12から、アナログ回路100の出力電圧VOUTと同等の電圧(出力電圧VOUTts)を出力することができる。

再び図6を参照して、実施の形態1に係る変形例では、レプリカ回路300が動作する下で、アナログ電圧出力回路200が実施の形態1と同様に動作する期間(時刻tx以前)の後に、レプリカ回路300が停止状態の下で、アナログ電圧出力回路200が実施の形態1と同様に動作する期間(時刻tx以降)が設けられる。

従って、時刻txにおいて、アナログ電圧出力回路200のキャパシタ201は、レプリカ電流Irpによってレプリカ電圧Vrpまで充電された状態となる。時刻txにおいて、レプリカ回路300がアナログ回路100及びアナログ電圧出力回路200から切り離されると、アナログ回路100は、当該時点でのキャパシタ201の電圧と、出力電圧VOUTとの電圧差を、出力段の電流Ioによって、充電又は放電する様に動作することができる。そして、キャパシタ201の電圧が出力電圧VOUTと同等となると、実施の形態1と同様に、出力電圧VOUTと同等の出力電圧VOUTtsを、高精度に出力端子12に生成することができる。

時刻txにおける上記電圧差は、上述の様に素子ばらつきに起因するものであり、最大でも100[mv]程度であることが想定される。従って、実施の形態1において、出力段の電流Ioでキャパシタ201を0[V]からVOUT(例えば、1.0[V])まで充電するのに比較して、当該電圧差の充放電は短時間(例えば、100[mV]/1「V]=0.1倍)で完了することができる。

この様に、実施の形態1の変形例に係るアナログ電圧出力回路によれば、アナログ電圧出力回路が動作を開始してから、アナログ回路100の出力電圧VOUTと同等の出力電圧VOUTtsが、高精度に出力端子12に生成されるまでの所要時間、即ち、出力端子12にテスタを接続するまでの準備時間を短縮することができる。これにより、実施の形態1での効果に加えて、電圧測定を更に高速化することができる。

例えば、実施の形態1の変形例の冒頭で例示した様に、キャパシタ201を0[V]から出力電圧VOUT=1[V]まで充電するのに1[ms]程度を要していたのに対して、上述の電圧差(最大で100[mv])の充放電の所要時間(100[μs])、及び、レプリカ回路300による充電時間(上述の様に、10[μs])の和、即ち、約(1/10)まで、出力端子12に接続されたテスタによる測定を開始するまでの準備時間を短縮することができる。

実施の形態2.

実施の形態2では、クロック信号を用いずに動作可能なアナログ電圧出力回路の構成を説明する。

図7には、実施の形態2に係るアナログ電圧出力回路を備える半導体装置の構成例を説明する回路図が示される。

図7に示される様に、実施の形態2に係る半導体装置10Cは、実施の形態1と同様のアナログ回路100と、アナログ回路100の出力電圧VOUT(アナログ電圧)を、半導体装置10Cの外部から測定するためのアナログ電圧出力回路250とを備える。即ち、実施の形態2に係る半導体装置10Cは、アナログ電圧出力回路200(図1)に代えて、アナログ電圧出力回路250を備える点で異なる。

アナログ電圧出力回路250は、アナログ電圧出力回路200と同様に、出力端子12及び入力端子13と、アナログ回路100との間に配置される。実施の形態2では、入力端子13には、半導体装置10Cの外部から、例えば、図示しない試験用回路からの試験用アナログ電圧が、テスト電圧VINtsとして入力される。テスト電圧VINtsは、アナログ回路100の出力電圧VOUTの設計値と同等に決定される。

入力端子13は、ノードN1と接続される。出力端子12は、実施の形態1と同様に、ノードN4、即ち、駆動トランジスタ202Aのソースと接続される。

アナログ電圧出力回路250は、ネイティブNMOSトランジスタによって構成される駆動トランジスタ202Aと、可変抵抗回路205と備える。駆動トランジスタ202Aは、電源ノードNP2と接続されるドレインと、出力端子12と接続されるノードN4に接続されたソースと、ノードN1に接続されるゲートとを有する。実施の形態2では、駆動トランジスタ202Aのゲートは、アナログ回路100の出力ノードNo、及び、入力端子13と接続される。

可変抵抗回路205は、ノードN4及び基準電圧ノードNGの間に接続された複数の抵抗素子R10~R12と、ノードN4及び基準電圧ノードNGの間の電気抵抗値Rsを調整するための制御スイッチSW10~SW12とを有する。制御スイッチSW10~SW12のオンオフは、制御信号SL10~SL12によってそれぞれ制御される。制御信号SL10~SL12は、図示しない経路により、半導体装置10Cの外部から入力することができる。例えば、テスト電圧VINtsを発生する試験用回路(図示せず)によって、制御信号SL10~SL12は設定される。

例えば、抵抗素子R10~R12の電気抵抗値が同等である場合には(R10=R11=R12=R)、制御スイッチSW10~SW12のオンオフの組み合わせ(スイッチングパターン)によって、Rs=R(SW10オン)、Rs=2R(SW11オン)、及び、Rs=3R(SW12オン)の3段階に設定できる。この様に、複数の制御スイッチSW10~SW12によって、複数の抵抗素子R10~R12と基準電圧ノードNGとの間の接続態様を切替えることで、電気抵抗値Rsが調整される。

更に、制御スイッチSW10~SW12の全てをオフすることで、Rs=∞にも設定することができる。即ち、制御スイッチSW10~SW12のスイッチングパターンのうちの1つにおいて、駆動トランジスタ202のソースと、基準電圧ノードNGとは、電気的に切り離される。

図8には、アナログ電圧出力回路250の動作を説明する概念的な波形図が示される。

図8に示される様に、アナログ電圧出力回路250は、時刻taまでの期間では、入力端子13にテスト電圧VINtsが入力された「第1の状態」で動作する。即ち、第1の状態では、駆動トランジスタ202Aのゲート電圧は、テスト電圧VINtsと同等となる。

アナログ電圧出力回路200は、第1の状態では、制御信号SL10~SL12による可変抵抗回路205の電気抵抗値Rsの調整を伴って、出力端子12の出力電圧VOUTtsを測定し、VINts=VOUTtsとなる電気抵抗値Rs(制御信号SL10~SL12の組み合わせ)を探索する。

一方で、上記探索による電気抵抗値Rsの調整が終了すると、時刻ta以降では、入力端子13は開放状態とされる。これにより、アナログ電圧出力回路250は、駆動トランジスタ202Aのゲート電圧が、アナログ回路100の出力電圧VOUTと同等となる「第2の状態」で動作する。

再び、図7を参照して、アナログ電圧出力回路250の第1の状態での動作を説明する。

駆動トランジスタ202Aのしきい値電圧Vtは、実施の形態1と同様に、0[V]の設計値Vt*と変動分ΔVとの和(Vt=Vt*+ΔVt)で示される。第1の状態では、駆動トランジスタ202Aのゲート・ソース間電圧Vgs、しきい値電圧Vt、及び、ドレイン電流Idsの間には、下記の式(16)が成立することが知られている。

Ids=(β/2)・(Vgs-Vt)2 …(16)

尚、式(16)中の利得係数βは、下記の式(17)に示されるように、表面平均移動度μ、チャネル長L,チャネル幅W、及び、単位面積当たりのゲート容量Coxによって決まる素子定数である。

β=(W/L)・μ・Cox …(17)

式(15)を変形すると、下記の式(18)が得られる。

Vgs=√(2・Ids/β)+Vt …(18)

式(18)の左辺第1項は、ゲート・ソース間電圧Vgsと、しきい値電圧Vtとの差電圧を示しており、当該差電圧は、ドレイン電流Idsに依存して変化することが理解される。ここで、図7のアナログ電圧出力回路250では、可変抵抗回路205の電気抵抗値Rsを変化させることで、ドレイン電流Idsを変えることができる。

アナログ電圧出力回路250は、第1の状態では、Vgs=VINts-VOUTtsである。従って、テスト電圧VINtsを固定した下で、制御スイッチSW10~SW12のスイッチングパターンに応じて電気抵抗値Rsを調整することでドレイン電流Idsを変化させながら、出力電圧VOUTtsを測定する。そして、VOUts=VINtsとなったドレイン電流Idsが流れている状態に、可変抵抗回路205の電気抵抗値Rsを固定する。これにより、式(17)中において、変動分ΔVtを含む、駆動トランジスタ202Aの実際のしきい値電圧Vtを相殺する差電圧を生じさせるドレイン電流Ids、即ち、駆動トランジスタ202AにおいてVgs=0となるときのドレイン電流Idsを発生させるための電気抵抗値Rsがメモリされた状態となる。尚、ΔVt=0で、駆動トランジスタ202Aのしきい値電圧Vt=0の場合には、Ids=0、即ち、制御スイッチSW10~SW12の全てがオフ(Rs=∞)された状態がメモリされることになる。

上記の様な電気抵抗値Rsによるドレイン電流Idsの調整により、アナログ電圧出力回路250では、ゲート電圧及びソース電圧が等しくなる様な駆動トランジスタ202Aの動作状態が設定されることになる。即ち、実施の形態2では、可変抵抗回路205によって「駆動トランジス制御回路」の一実施例を構成することができる。又、実施の形態2において、入力端子13は「第2の端子」の一実施例に対応する。

アナログ電圧出力回路250は、第1の状態でのドレイン電流Idsが維持されたままで、入力端子13を開放状態にすることで第2の状態に移行する。これにより、第2の状態では、駆動トランジスタ202Aのゲートに、アナログ回路100の出力電圧VOUTが入力されるので、駆動トランジスタ202Aのソースには、ゲートと同電圧(Vgs=0)が出力される。これにより、出力端子12の出力電圧VOUTtsは、駆動トランジスタ202A(ネイティブNMOSトランジスタ)のしきい値電圧のばらつきΔVtの影響を排除して、出力電圧VOUTと同等となる。

言い換えると、可変抵抗回路205によって差電圧(Vgs-Vt)がゼロとなる様にドレイン電流Idsを調整することで、駆動トランジスタ202Aのしきい値電圧の影響を取り除いて、ゲート電圧及びソース電圧が等しくなる様な駆動トランジスタ202Aの動作状態を設定することができる。この結果、実施の形態2に係るアナログ電圧出力回路250によっても、駆動トランジスタ202Aの電流によって、出力電圧VOUTと同等の電圧を出力端子12に出力することができる。

尚、しきい値電圧のばらつきは、一般的には正規分布に従うことが知られているが、通常、ネイティブNMOSトランジスタでは、負のばらつきを考慮する必要はない。又、ネイティブNMOSトランジスタでは、構造的に、バックゲート電圧には、基板電位である、基準電圧AVSS(接地電圧)が供給される。そして、出力電圧VOUTに対応してソース電圧が1[V]程度になることを考慮すると、基板バイアス効果の影響を受けて、100[mV]程度が、等価的にしきい値電圧Vtに加算されることなる。従って、一般的には、ネイティブNMOSトランジスタのしきい値電圧の素子ばらつきΔVtが数十[mV]程度であることを考えると、基板バイアス効果を含んだ、ネイティブNMOSトランジスタのしきい値電圧Vt(Vt=0+ΔVt)は、Vt>0の範囲内の分布となる。

このため、図7では、ドレイン電流Idsは、向きが固定された下で調整されるが、正のしきい値電圧Vt(Vt>0)に対応して、Vgs=0となるドレイン電流Idsを見つけ出すことで、駆動トランジスタ202Aのしきい値電圧の影響を排除して、高精度に出力電圧VOUTtsを生成することができる。

尚、アナログ電圧出力回路250は、半導体装置10Cの試験時以外(半導体装置10Cの通常動作時)には、出力端子12及び入力端子13が開放状態とされるとともに、制御スイッチSW10~SW12の全てがオフされた状態、即ち、可変抵抗回路205がノードN4と基準電圧ノードNGとの間の電流経路を遮断する状態に維持されることで停止する。これにより、アナログ電圧出力回路250の停止状態における消費電流が生じない様にすることができる。

この様に、実施の形態2に係る半導体装置10Cによっても、nAオーダに設計された極低消費電力のアナログ回路100の出力電圧VOUTを、駆動トランジスタ202Aを有するアナログ電圧出力回路250を用いて高速に測定することができる。この際に、アナログ電圧出力回路200は、駆動トランジスタ202Aの素子ばらつき(しきい値電圧のばらつき)の影響を排除して、アナログ回路100の出力電圧VOUTと同等の出力電圧VOUTtsを高精度に出力することができる。又、クロック信号を用いずに電圧測定が実行できるので、クロック信号に起因するノイズが測定誤差となることを防止できる。又、実施の形態2においても、又、電源ノードNP2の電源電圧AVDD2を高く設定することで(AVDD2>AVDD1)、アナログ電圧出力回路250の消費電力を削減することができる。

尚、実施の形態2のアナログ電圧出力回路250では、ネイティブNMOSトランジスタの駆動トランジスタ202Aに代えて、エンハンスメント型のNMOSトランジスタ(Vt>0)を適用することも可能であるが、Vt<0のデプレッション型NMOSトランジスタの適用は困難である。

実施の形態2の変形例.

図9は、実施の形態2の変形例に係るアナログ電圧出力回路を備える半導体装置の構成例を説明する回路図である。

図9に示される様に、実施の形態2の変形例に係る半導体装置10Dは、実施の形態2に係る半導体装置10Cと比較して、アナログ電圧出力回路250に代えて、アナログ電圧出力回路260を備える点で異なる。アナログ電圧出力回路260は、図7のアナログ電圧出力回路250に加えて、図5と同様のレプリカ回路300を更に備える点で異なる。

レプリカ回路300の構成及び動作は、図5と同様であるので説明は繰り返さない。従って、レプリカ回路300は、制御信号SL1がHレベル(AVDD1)に設定される期間では、アナログ回路100の出力段の電流IoのK倍のレプリカ電流Irpによって、ノードN1、即ち、駆動トランジスタ202Aのゲート容量を、出力電圧VOUTと同等のレプリカ電圧Vrpまで充電する様に動作する。更に、レプリカ回路300は、制御信号SL2がHレベル(AVDD1)に設定される期間では、アナログ回路100及びアナログ電圧出力回路250から切り離されて、動作を停止する。

図10には、図9に示されたアナログ電圧出力回路250の動作を説明する概念的な波形図が示される。

図10に示される様に、時刻tsから、図8で説明したアナログ電圧出力回路250の動作が開始される。時刻tsまでの間に、レプリカ回路300の制御信号SL1がHレベル(AVDD1)に設定される期間が設けられる。

これにより、アナログ電圧出力回路250が実施の形態2で説明した動作を開始する時点(時刻ts)において、ノードN1の電圧、即ち、駆動トランジスタ202Aのゲート電圧は、出力電圧VOUT、即ち、入力端子13から入力されるテスト電圧VINtsと近い電圧レベルまで上昇している。

時刻ts以降では、制御信号SL2がHレベル(AVDD1)に設定されて、制御信号SL1はLレベル(AGND)に設定されるので、レプリカ回路300がアナログ回路100及びアナログ電圧出力回路250から切り離されることにより、実施の形態2と同様のアナログ電圧出力回路250によるアナログ回路100の出力電圧VOUTの測定が実行される。

この様に、実施の形態2の変形例に係るアナログ電圧出力回路によれば、時刻tsを起点とした、駆動トランジスタ202Aのゲート充電の所要時間が短縮されることにより、アナログ電圧出力回路250による出力電圧VOUTの測定に要する時間を短縮することが可能となる。即ち、実施の形態2での効果に加えて、電圧測定を更に高速化することができる。

尚、実施の形態1及び2,並びに、それらの変形例に係るアナログ電圧出力回路200,210,250,260による測定対象となるアナログ回路100は、例示されたバンドギャップリファレンスに限定されることなく、アナログ電圧を出力電圧とする任意の回路とすることができる。即ち、本実施の形態に係るアナログ電圧出力回路は、アナログ回路を備える任意の半導体装置に搭載可能であり、当該半導体装置の外部から当該アナログ回路の出力電圧を測定するDFTに適宜用いることが可能である。

実施の形態3.

実施の形態1及び2では、アナログ回路に対してアナログ電圧出力回路を1対1で配置する構成例を説明したが、実施の形態3では、1個のアナログ電圧出力回路を効率的に共有して、複数個のアナログ回路からのアナログ電圧を測定するための構成を説明する。

図11は、実施の形態3に係るアナログ電圧出力回路250Xを備える半導体装置10Eの構成例を説明する回路図である。

図11に示される様に、実施の形態3に係る半導体装置10Eは、複数のアナログ回路100H,100Lと、選択スイッチSWH,SWLと、アナログ電圧出力回路250Xとを備える。

アナログ回路100Hの出力ノードNoHには、出力電圧VOUTHが生成される一方で、アナログ回路100Lの出力ノードNoLには、出力電圧VOULLが生成される(VOUTH>VOUTL)。以下では、VOUTH=2.4[V]、VOUTL=1.2[V]の例を説明する。又、以下では、電圧比(VOUTH/VOUTL)=Kvと表記する。

アナログ回路100H,100Lの構成は、アナログ回路100と同様に任意であるが、例えば、図1等で例示したアナログ回路100の構成と同様とすることができる。図1と同様の構成において、ダイオードD1~D3による電流量を、アナログ回路100H及び100Lの間でKv:1(例えば、2:1)とすることで、上述した出力電圧VOUT,VOUTLを生成することができる。

アナログ電圧出力回路250Xは、図5のアナログ電圧出力回路200の構成に加えて、可変抵抗回路206を更に含む。図11の構成では、可変抵抗回路205及び206は、駆動トランジスタ202Aのソースに対して直列接続されており、可変抵抗回路205は「第1の可変抵抗回路」の一実施例に対応し、可変抵抗回路206は「第2の可変抵抗回路」の一実施例に対応する。

選択スイッチSWHは、アナログ回路100Hの出力ノードNoHと、アナログ電圧出力回路250XのノードN1との間に接続される。又、選択スイッチSWLは、アナログ回路100Lの出力ノードNoLと、アナログ電圧出力回路250XのノードN1との間に接続される。選択スイッチSWHは、制御信号SLhに応じてオンオフされ、選択スイッチSWLは、制御信号SLlに応じてオンオフされる。

アナログ電圧出力回路250Xでは、可変抵抗回路205の抵抗素子R10~R12はノードN4及びノードNxの間に直列接続されており、制御信号SW10~SW12に応じた制御スイッチSW10~SW12のオンオフの組み合わせによって、ノードN4及びノードNxの間の電気抵抗値Rsが可変に設定される。

可変抵抗回路206は、ノードNx及び基準電圧ノードNGの間に直列接続された抵抗素子R20,R21と、ノードNx及び基準電圧ノードNGの間の電気抵抗値Rxを調整するための制御スイッチSW20とを有する。制御スイッチSW20のオンオフは、選択スイッチSWLと共通の制御信号SLlによって制御される。

尚、図11で追加された、制御信号SLh及びSLlについても、図示しない経路により、半導体装置10Eの外部から入力することができる。例えば、テスト電圧VINtsを発生する試験用回路(図示せず)によって、制御信号SLh,SLlは設定される。

抵抗素子R20,R21の電気抵抗値は、制御スイッチSW20のオフ時における電気抵抗値Rxと、制御スイッチSW20のオフ時における電気抵抗値Rxとの比が、Kv:1になる様に決定される。例えば、Kv=2のときには、抵抗素子R20及びR21は同等の電気抵抗値を有する様に決定される。

可変抵抗回路205の電気抵抗値Rsは、選択スイッチSWL,SWHの一方がオンされた状態において、図5と同様に、VINts=VOUTtsとなる様に調整される。又、可変抵抗回路205の電気抵抗値Rxは、可変抵抗回路205の電気抵抗値Rsよりも非常に大きな値に設定される(Rx>>Rs)。即ち、可変抵抗回路205の電気抵抗値Rsは「第1の電気抵抗値」に対応し、可変抵抗回路206の電気抵抗値Rxは「第2の電気抵抗値」に対応する。

次にアナログ電圧出力回路250Xの動作について、詳細に説明する。

まず、選択スイッチSWHがオンされる一方で、選択スイッチSWLがオフされる状態として、アナログ回路100Hの出力電圧VOUTHが、アナログ電圧出力回路250Xに伝達される。この状態では、選択スイッチSWHのオンと連動して、制御スイッチSW20がオフされる。これにより、Rx=Rx(ON)=R20+R21となる。

この状態で、入力端子13にテスト電圧VINts(VOUTHと同等の電圧値)が入力された「第1の状態」において、VINts=VOUTtsとなる様な、制御スイッチSW10~SW12のスイッチングパターン、即ち、可変抵抗回路205の電気抵抗値Rsが探索される。

実施の形態2で説明した様に、上述の電気抵抗値Rsの調整後に入力端子13(VINts)を開放状態とすることで「第2の状態」が形成されて、出力端子12には、VOUTts=VOUTHを得ることができる。これにより、アナログ回路100Hの出力電圧VOUTHを測定することができる。

次に、アナログ回路100Lの出力電圧VOUTLを測定するために、選択スイッチSWLがオンされる一方で、選択スイッチSWHがオフされる。これにより、出力電圧VOUTL(VOUTL=VOUTH/Kv)が、アナログ電圧出力回路250XのノードN1に伝達される。この状態では、選択スイッチSWLのオンと連動して、制御スイッチSW20がオンされる。これにより、Rx=Rx(OFF)=R20=Rx(ON)/Kvとなる。

従って、駆動トランジスタ202Aのドレイン電流Idsは、出力電圧VOUTHの測定時(選択スイッチSWHのオン時)には、Ids=VOUTH/Rx(ON)である一方で、出力電圧VOUTLの測定時(選択スイッチSWLのオン時)には、Ids=VOUTL/Rx(OFF)である。一方で、上述の様に、VOUTL=VOUTH/Kv、かつ、RX(OFF)=Rx(ON)/Kvが成立する。

従って、アナログ電圧出力回路250Xでは、出力電圧VOUTHの測定時と、出力電圧VOUTLの測定時との間で、駆動トランジスタ202Aのドレイン電流Idsを一定に維持できることが理解される。

この結果、出力電圧VOUTH及びVOUTLの一方の測定時に調整された電気抵抗値Rs(可変抵抗回路205)の下で、出力電圧VOUTH及びVOUTLの他方についても同様の精度で測定することが可能となる。

この様に、実施の形態3に係るアナログ電圧出力回路250Xでは、入力ノードN1へ入力されるアナログ電圧が、電圧比がKvである出力電圧VOULH及びVOUTLの間で変化する際に、可変抵抗回路205を流れるドレイン電流Idsを一定に維持する様に、可変抵抗回路206の電気抵抗値がKv倍、又は、(1/Kv)倍に切り換えられる。これにより、可変抵抗回路205による調整結果(電気抵抗値Rs)を共通に用いて、出力電圧VOULH及びVOUTLの両方を高精度に測定することが可能である。

尚、図11の例では、2個のアナログ電圧(出力電圧VOUT)の測定に1個のアナログ電圧出力回路250Xを共通に用いる構成を例示したが、3以上のN個(N:自然数)のアナログ電圧(出力電圧VOUT)に対して、1個のアナログ電圧出力回路250Xを配置する構成とすることも可能である。この場合には、N個のアナログ電圧の間の電圧比に連動して、可変抵抗回路206の電気抵抗値RxをN段階に切り替えることで、N個のアナログ電圧(出力電圧VOUT)を、1個のアナログ電圧出力回路250Xによって共通に測定することができる。

実施の形態3の変形例.

図12は、実施の形態3の変形例に係るアナログ電圧出力回路250Yを備える半導体装置10Fの構成例を説明する回路図である。

図12に示される様に、実施の形態3の変形例に係る半導体装置10Fは、複数のアナログ回路100H,100Lと、選択スイッチSWH,SWLと、アナログ電圧出力回路250Yとを備える。即ち、半導体装置10Fは、アナログ電圧出力回路250Xに代えてアナログ電圧出力回路250Yを備える点で、半導体装置10E(図11)と異なる。半導体装置10Fのその他の部分の構成は、半導体装置10Eと同様であるので詳細な説明は繰り返さない。

図12においても、アナログ回路100Hの出力電圧VOUTH(出力ノードNoH)VOUTH=2.4[V]、かつ、アナログ回路100Lの出力電圧VOUTL(出力ノードNoL)VOUTL=1.2[V]の例を説明する。即ち、電圧比Kv=(VOUTH/VOUTL)=2である。

アナログ電圧出力回路250Yは、アナログ電圧出力回路250X(図11)と比較して、可変抵抗回路206に代えて抵抗素子R20が固定的に配置されるともに、電源ノードNP及びノードN4の間に複数の駆動トランジスタが並列接続される構成を有する。更に、アナログ電圧出力回路250Yは、可変抵抗回路206の電気抵抗値Rsを調整するための制御スイッチSW20(図11)に代えて、ノードN1と複数の駆動トランジスタのゲートとの接続をオンオフするための制御スイッチSW21が設けられる点で、アナログ電圧出力回路250Xと異なる。

図12の構成例では、駆動トランジスタ202A及び203Aが、電源ノードNP及びノードN4の間に並列接続されており、制御スイッチSW21が、ノードN1及び駆動トランジスタ203Aのゲートの間に接続される。ここでは、制御スイッチSW21は、選択スイッチSWHと共通の制御信号SLhに応じてオンオフされる。アナログ電圧出力回路250Yのその他の部分の構成は、アナログ電圧出力回路250Xと同様であるので詳細な説明は繰り返さない。

アナログ電圧出力回路250Yでは、アナログ電圧出力回路200(図5)と同様に、ノードN4及び基準電圧ノードNGの間の電気抵抗値は、可変抵抗回路205(電気抵抗値Rs)によって調整される。

並列接続された駆動トランジスタ202A,203Aのゲートと、ノードN1との間の接続(制御スイッチSW21のオンオフ)は、選択スイッチSWH,SWLのオンオフと連動して制御される。具体的には、ゲートがノードN1と接続された駆動トランジスタによる、ノードN4への電流駆動力の合計が、ノードN1に伝達されるアナログ電圧(出力電圧VOUTH,VOULL)の電圧比Kvに連動して切り換えられる様に、制御スイッチSW21のオンオフが制御される。尚、電流駆動力は、上述の式(16),(17)での利得係数βに相当する。代表的には、電流駆動力が同等、即ち、同一サイズの駆動トランジスタを並列接続して、ゲートがノードN1と接続される駆動トランジスタの個数を変化させることで、ノードN4への電流駆動力の合計を可変に設定することが可能となる。

次にアナログ電圧出力回路250Yの動作について、詳細に説明する。

まず、選択スイッチSWHがオンされる一方で、選択スイッチSWLがオフされる状態として、アナログ回路100Hの出力電圧VOUTHが、アナログ電圧出力回路250Yに伝達される。この状態では、選択スイッチSWHのオンと連動して、制御スイッチSW21がオンされる。これにより、駆動トランジスタ202A及び203Aの両方の電流駆動力によって、ノードN4へのドレイン電流Idsが供給される。

この状態で、テスト電圧VINts(VOUTHと同等の電圧値)を固定した下で、VINts=VOUTtsとなる様な、制御スイッチSW10~SW12のスイッチングパターン、即ち、可変抵抗回路205の電気抵抗値Rsが探索される。

実施の形態2で説明した様に、上述の電気抵抗値Rsの調整後に入力端子13(VINts)を開放状態とすることで、出力端子12には、VOUTts=VOUTHを得ることができる。これにより、アナログ回路100Hの出力電圧VOUTHを測定することができる。

次に、アナログ回路100Lの出力電圧VOUTLを測定するために、選択スイッチSWLがオンされる一方で、選択スイッチSWHがオフされる。これにより、出力電圧VOUTL(VOUTL=VOUTH/Kv)が、アナログ電圧出力回路250YのノードN1に伝達される。この状態では、選択スイッチSWHのオフと連動して、制御スイッチSW20がオフされる。駆動トランジスタ202のみの電流駆動力によって、ノードN4へのドレイン電流Idsが供給される。

従って、出力電圧VOUTL(=VOUTL/Kv)の測定時には、出力電圧VOUTHの測定時と比較すると、ノードN4への電流駆動力は(1/Kv)倍に設定される。これにより、出力電圧VOUTH及びVOUTLのそれぞれの測定間で、ノードN4及び基準電圧ノードNGの間を流れるドレイン電流Idsが同等に維持される。この結果、出力電圧VOUTH及びVOUTLの一方の測定時に調整された電気抵抗値Rs(可変抵抗回路205)の下で、出力電圧VOUTH及びVOUTLの他方についても同様の精度で測定することが可能となる。

この様に、実施の形態3の変形例に係るアナログ電圧出力回路250Yでは、入力ノードN1へ入力されるアナログ電圧が、電圧比Kvの出力電圧VOULH及びVOUTLの間で変化する際に、並列接続された複数の駆動トランジスタの少なくとも一部を用いた、ノードN4に対する電流駆動能力の比がKv倍、又は、(1/Kv)倍に切り換えられる。これにより、可変抵抗回路205を流れるドレイン電流Idsが一定に維持されるので、可変抵抗回路205による調整結果(電気抵抗値Rs)を共通に用いて、出力電圧VOULH及びVOUTLの両方を高精度に測定することが可能である。

尚、図12の例では、2個のアナログ電圧(出力電圧VOUT)の測定に1個のアナログ電圧出力回路250Yを共通に用いる構成を例示したが、3以上のN個(N:自然数)のアナログ電圧(出力電圧VOUT)に対して、1個のアナログ電圧出力回路250Yを配置する構成とすることも可能である。この場合には、N個のアナログ電圧の間の電圧比に連動して、並列接続された複数の駆動トランジスタの少なくとも一部を用いた、ノードN4への電流駆動力をN段階に切り替えることで、N個のアナログ電圧(出力電圧VOUT)を、1個のアナログ電圧出力回路250Yによって共通に測定することができる。

この様に、実施の形態3又はその変形例に係るアナログ電圧出力回路250X,250Yによれば、選択スイッチを設けることにより、複数のアナログ回路によって1個のアナログ電圧出力回路を共有する際に、1個のアナログ回路からの出力電圧(アナログ電圧)を高精度に測定するための調整を、他のアナログ回路からの出力電圧の測定時にも共通に用いることができるので、1個のアナログ電圧出力回路250X,250Yによる、複数のアナログ回路の出力電圧の測定を高速化できる。

これに対して、実施の形態1及び2に係るアナログ電圧出力回路についても、図11及び図12の選択スイッチSWH,SWLと同様の選択スイッチの配置によって、複数のアナログ回路の出力電圧(アナログ電圧)を測定する構成することが可能である。しかしながら、この場合には、実施の形態3及びその変形例とは異なり、高精度に測定するための調整は、アナログ回路毎(出力電圧毎)に個別に実行することが必要となる。

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本開示の範囲は上記した説明ではなくて請求の範囲によって示され、請求の範囲と均等の意味及び範囲内でのすべての変更が含まれることが意図される。