JP7253233B2 - フィルタ装置、フィルタプログラム、フィルタ設計プログラム、参照信号生成装置及び参照信号生成プログラム - Google Patents

フィルタ装置、フィルタプログラム、フィルタ設計プログラム、参照信号生成装置及び参照信号生成プログラム Download PDFInfo

- Publication number

- JP7253233B2 JP7253233B2 JP2019039430A JP2019039430A JP7253233B2 JP 7253233 B2 JP7253233 B2 JP 7253233B2 JP 2019039430 A JP2019039430 A JP 2019039430A JP 2019039430 A JP2019039430 A JP 2019039430A JP 7253233 B2 JP7253233 B2 JP 7253233B2

- Authority

- JP

- Japan

- Prior art keywords

- transfer function

- reference signal

- controller

- output signal

- input

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Feedback Control In General (AREA)

Description

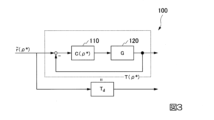

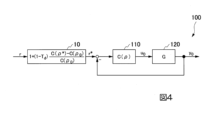

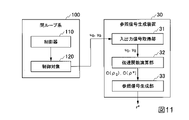

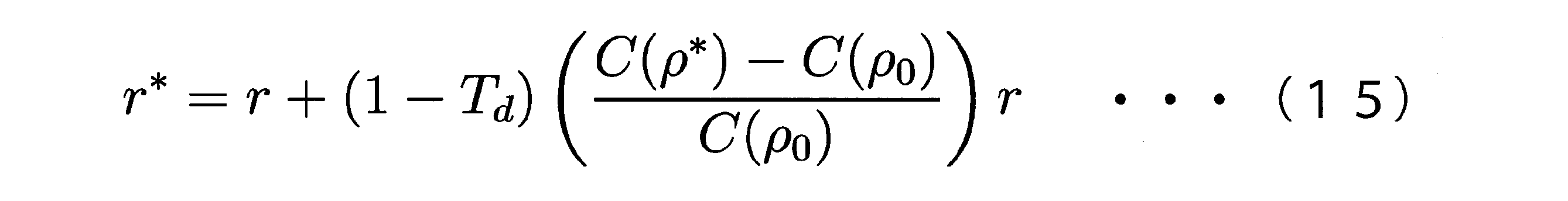

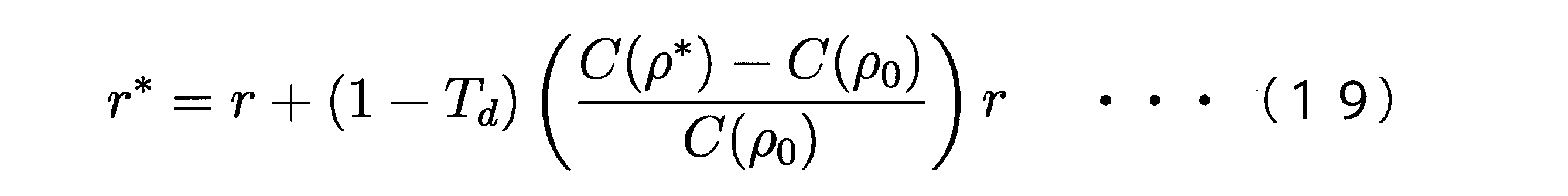

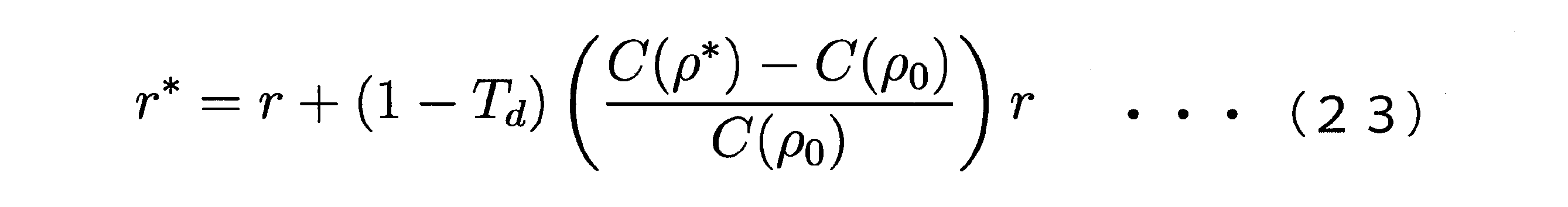

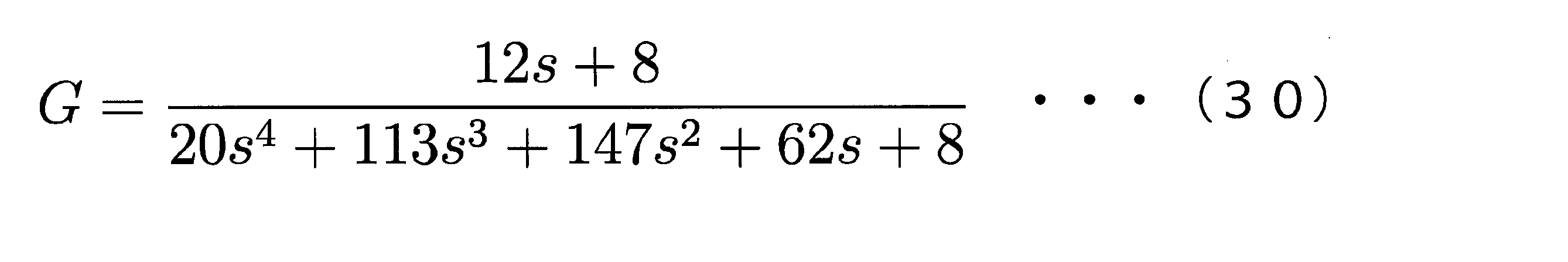

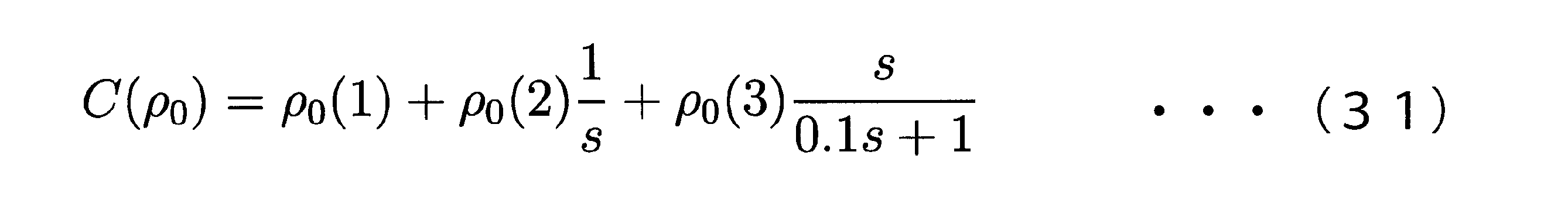

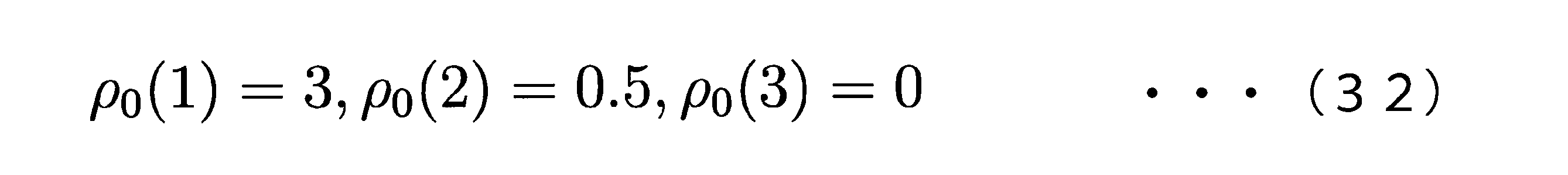

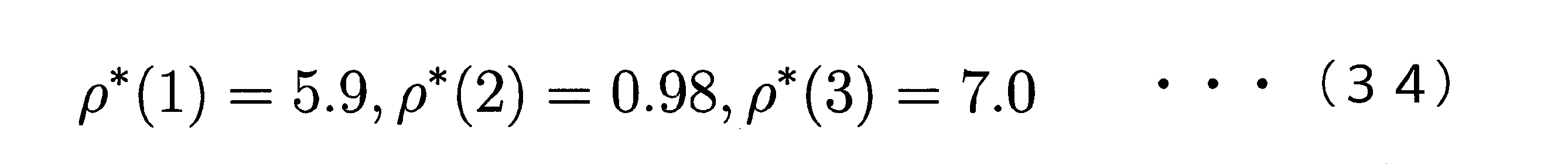

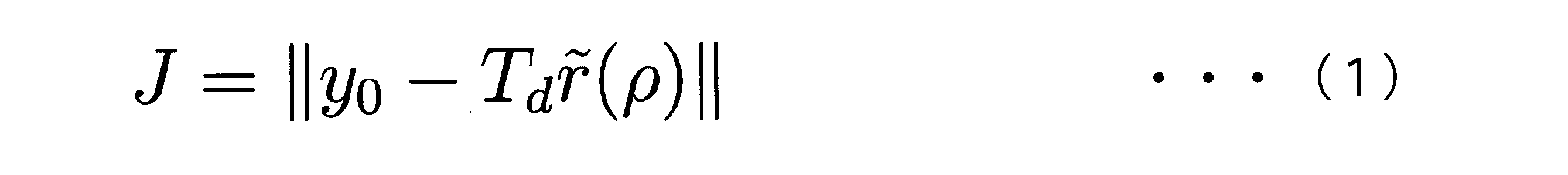

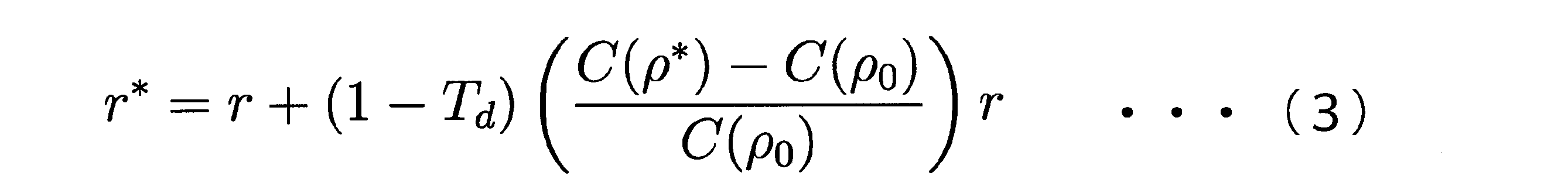

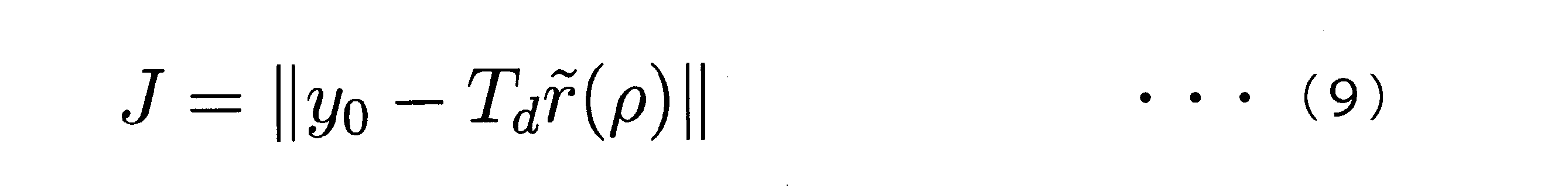

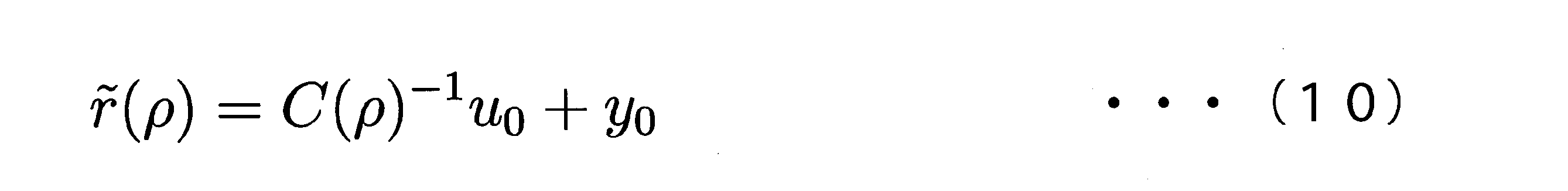

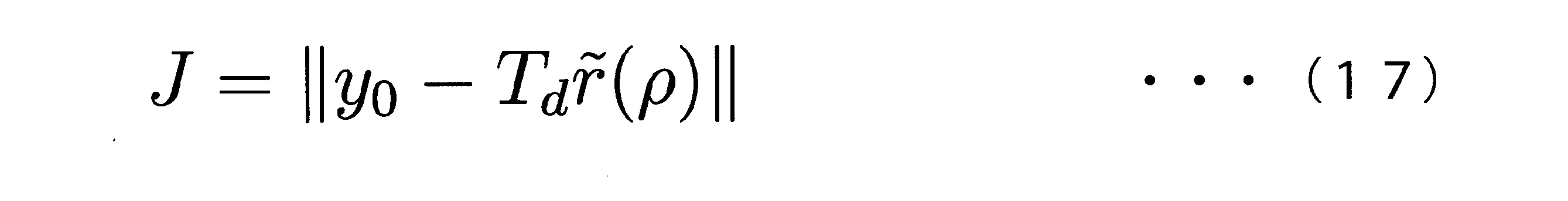

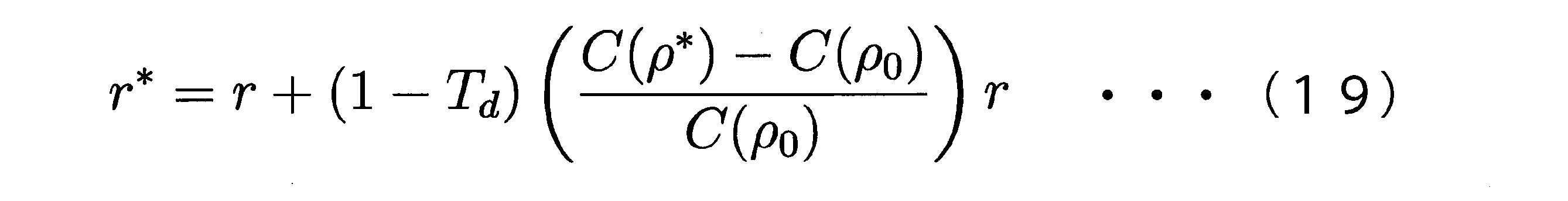

図3の上下のブロックの出力が等しくなるように、

y0=T(ρ*)r(~)(ρ*)=Tdr(~)(ρ*)

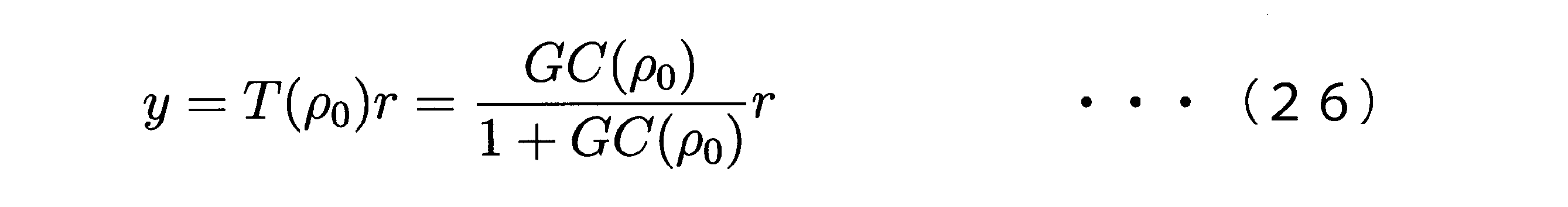

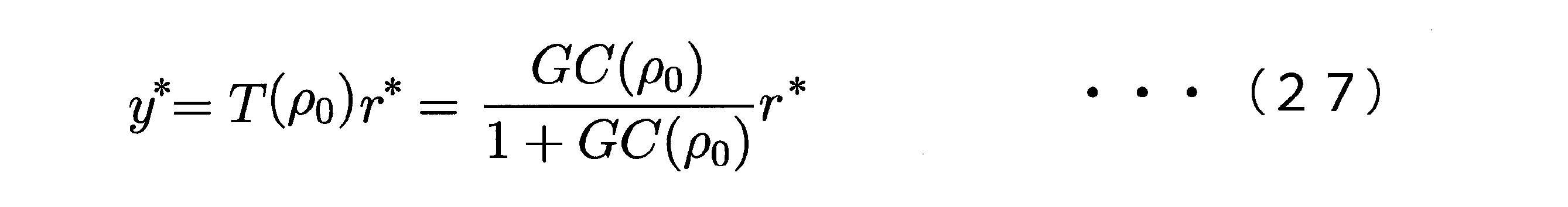

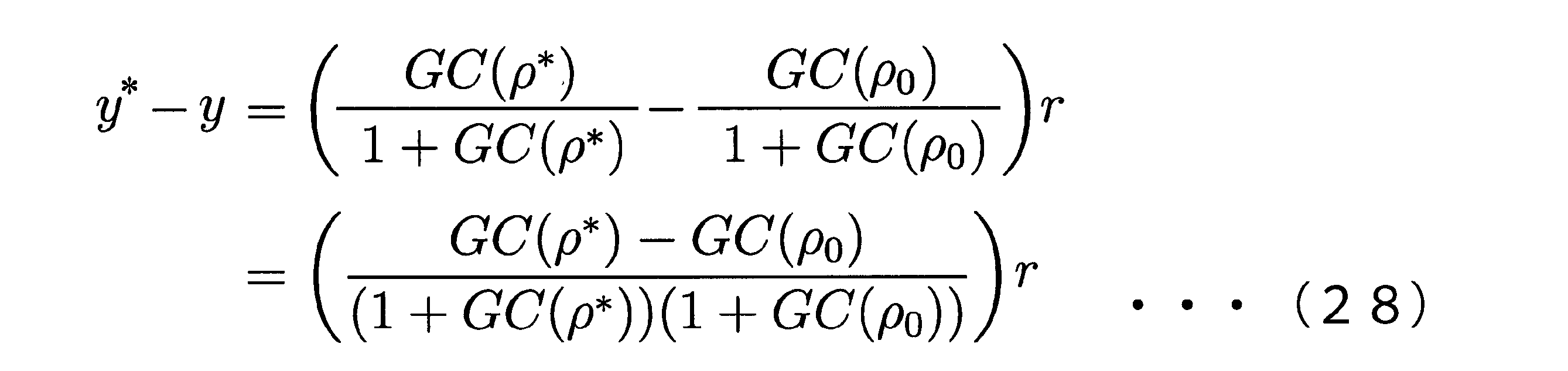

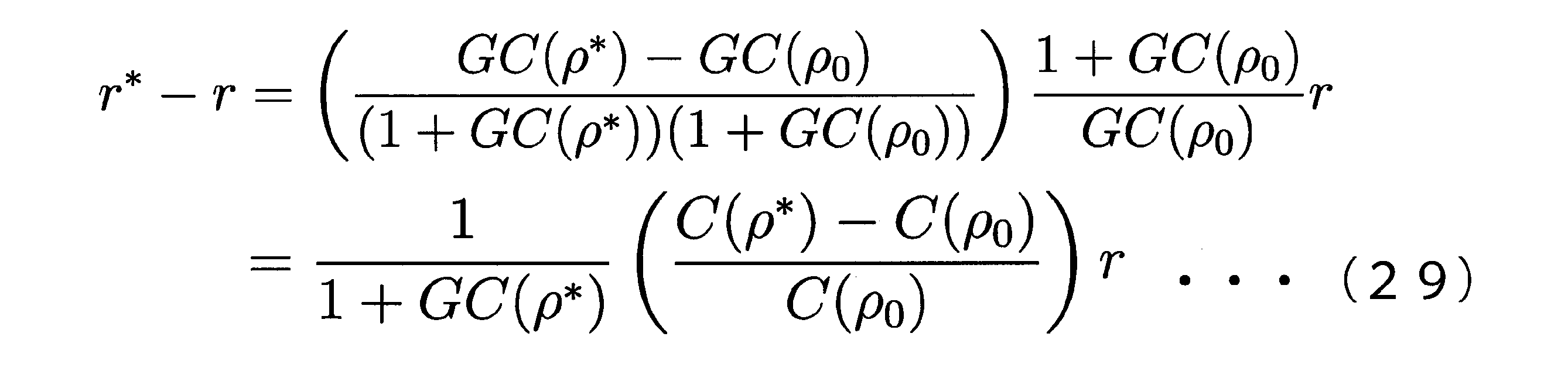

とし、T(ρ*)≒Tdとみなすと、T(ρ*)は、制御対象Gと制御器C(ρ*)からなる閉ループ系であるから、C(ρ*)を実装し、本来の参照信号rを印加することで、

y(ρ*)=GC(ρ*)/(1+GC(ρ*))r≒Tdr

となり、ρ*を用いた閉ループ系の応答y(ρ*)が所望の応答Tdrとなる。

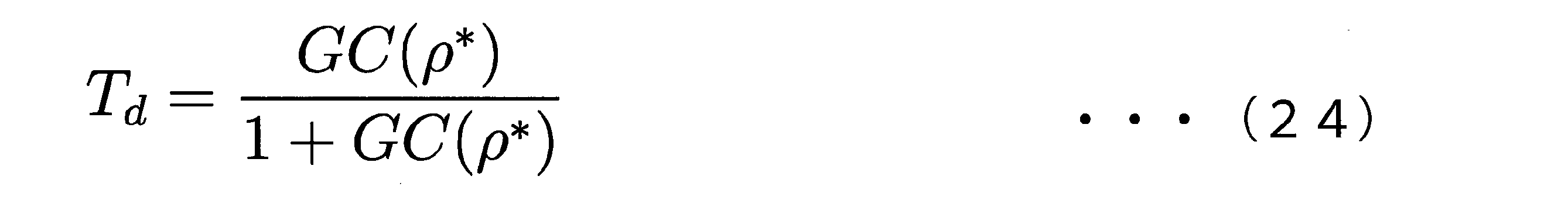

よって、仮想制御器の伝達関数C(ρ*)は、パラメータρ*により与えられる。また、目標伝達関数Tdと、仮想制御器の伝達関数C(ρ*)と、制御対象120の伝達関数Gとの関係は、図3に示すような関係となり、数式で表現すると、後述する式(24)のような関係となる。

Claims (15)

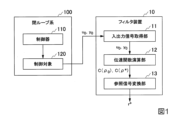

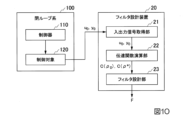

- 制御対象に入力される入力信号を取得し、前記入力信号の入力に応じて前記制御対象から出力される出力信号を取得する入出力信号取得部と、

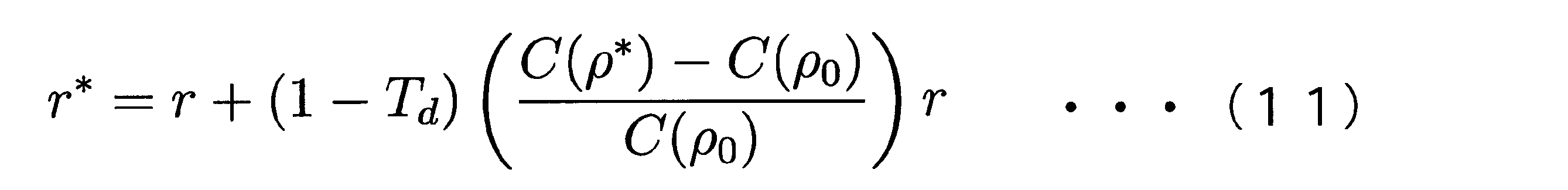

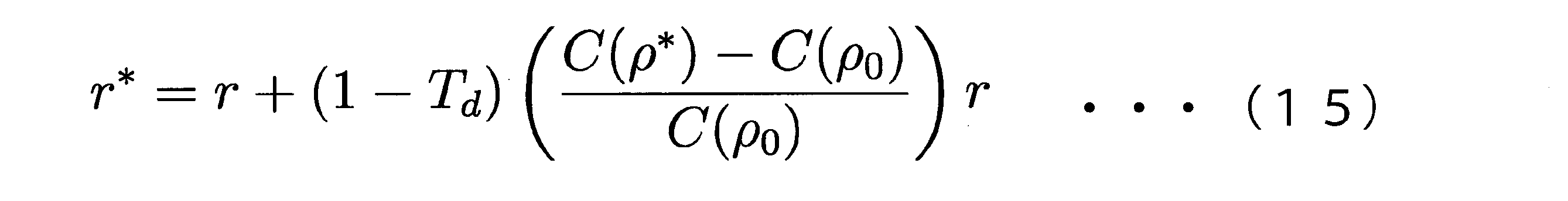

前記制御対象を制御している実装済制御器の伝達関数のパラメータを前記入力信号及び前記出力信号に基づくデータ駆動制御により更新して仮想制御器の伝達関数を演算する伝達関数演算部と、

前記制御対象の伝達関数、前記実装済制御器の伝達関数及び前記仮想制御器の伝達関数を使用して前記制御対象及び前記実装済制御器を含む閉ループ系に入力される更新前参照信号を前記制御対象に目標出力信号又は前記出力信号よりも前記目標出力信号に近似している近似目標出力信号を出力させる更新後参照信号に変換する参照信号変換部と、

を備えるフィルタ装置。 - コンピュータに、

制御対象に入力される入力信号を取得し、前記入力信号の入力に応じて前記制御対象から出力される出力信号を取得する入出力信号取得機能と、

前記制御対象を制御している実装済制御器の伝達関数のパラメータを前記入力信号及び前記出力信号に基づくデータ駆動制御により更新して仮想制御器の伝達関数を演算する伝達関数演算機能と、

前記制御対象の伝達関数、前記実装済制御器の伝達関数及び前記仮想制御器の伝達関数を使用して前記制御対象及び前記実装済制御器を含む閉ループ系に入力される更新前参照信号を前記制御対象に目標出力信号又は前記出力信号よりも前記目標出力信号に近似している近似目標出力信号を出力させる更新後参照信号に変換する参照信号変換機能と、

を実現させるためのフィルタプログラム。 - コンピュータに、

制御対象に入力される入力信号を取得し、前記入力信号の入力に応じて前記制御対象から出力される出力信号を取得する入出力信号取得機能と、

前記制御対象を制御している実装済制御器の伝達関数のパラメータを前記入力信号及び前記出力信号に基づくデータ駆動制御により更新して仮想制御器の伝達関数を演算する伝達関数演算機能と、

前記制御対象の伝達関数、前記実装済制御器の伝達関数及び前記仮想制御器の伝達関数を使用して前記制御対象及び前記実装済制御器を含む閉ループ系に入力される更新前参照信号を前記制御対象に目標出力信号又は前記出力信号よりも前記目標出力信号に近似している近似目標出力信号を出力させる更新後参照信号に変換するフィルタを設計するフィルタ設計機能と、

を実現させるためのフィルタ設計プログラム。 - 制御対象に入力される入力信号を取得し、前記入力信号の入力に応じて前記制御対象から出力される出力信号を取得する入出力信号取得部と、

前記制御対象を制御している実装済制御器の伝達関数のパラメータを前記入力信号及び前記出力信号に基づくデータ駆動制御により更新して仮想制御器の伝達関数を演算する伝達関数演算部と、

前記制御対象の伝達関数、前記実装済制御器の伝達関数及び前記仮想制御器の伝達関数を使用して前記制御対象及び前記実装済制御器を含む閉ループ系に入力される更新前参照信号から前記制御対象に目標出力信号又は前記出力信号よりも前記目標出力信号に近似している近似目標出力信号を出力させる更新後参照信号を生成する参照信号生成部と、

を備える参照信号生成装置。 - コンピュータに、

制御対象に入力される入力信号を取得し、前記入力信号の入力に応じて前記制御対象から出力される出力信号を取得する入出力信号取得機能と、

前記制御対象を制御している実装済制御器の伝達関数のパラメータを前記入力信号及び前記出力信号に基づくデータ駆動制御により更新して仮想制御器の伝達関数を演算する伝達関数演算機能と、

前記制御対象の伝達関数、前記実装済制御器の伝達関数及び前記仮想制御器の伝達関数を使用して前記制御対象及び前記実装済制御器を含む閉ループ系に入力される更新前参照信号から前記制御対象に目標出力信号又は前記出力信号よりも前記目標出力信号に近似している近似目標出力信号を出力させる更新後参照信号を生成する参照信号生成機能と、

を実現させるための参照信号生成プログラム。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2019039430A JP7253233B2 (ja) | 2019-03-05 | 2019-03-05 | フィルタ装置、フィルタプログラム、フィルタ設計プログラム、参照信号生成装置及び参照信号生成プログラム |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2019039430A JP7253233B2 (ja) | 2019-03-05 | 2019-03-05 | フィルタ装置、フィルタプログラム、フィルタ設計プログラム、参照信号生成装置及び参照信号生成プログラム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2020144506A JP2020144506A (ja) | 2020-09-10 |

| JP7253233B2 true JP7253233B2 (ja) | 2023-04-06 |

Family

ID=72354157

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019039430A Active JP7253233B2 (ja) | 2019-03-05 | 2019-03-05 | フィルタ装置、フィルタプログラム、フィルタ設計プログラム、参照信号生成装置及び参照信号生成プログラム |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP7253233B2 (ja) |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009237916A (ja) | 2008-03-27 | 2009-10-15 | Yaskawa Electric Corp | サーボ制御装置 |

| WO2016092872A1 (ja) | 2014-12-11 | 2016-06-16 | 富士電機株式会社 | 制御装置、そのプログラム、プラント制御方法 |

Family Cites Families (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5430535B2 (ja) * | 2010-10-25 | 2014-03-05 | 本田技研工業株式会社 | プラントの制御装置 |

-

2019

- 2019-03-05 JP JP2019039430A patent/JP7253233B2/ja active Active

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009237916A (ja) | 2008-03-27 | 2009-10-15 | Yaskawa Electric Corp | サーボ制御装置 |

| WO2016092872A1 (ja) | 2014-12-11 | 2016-06-16 | 富士電機株式会社 | 制御装置、そのプログラム、プラント制御方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2020144506A (ja) | 2020-09-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4223894B2 (ja) | Pidパラメータ調整装置 | |

| US10935939B2 (en) | Machine learning device, servo control apparatus, servo control system, and machine learning method | |

| US20160363939A1 (en) | Control device for machine apparatus and gain determination method for friction compensation | |

| JP6740279B2 (ja) | 調整装置及び調整方法 | |

| Günay et al. | Enhancement of real‐time hybrid simulation on a shaking table configuration with implementation of an advanced control method | |

| JP2021081786A (ja) | 推論システム、推論装置、推論方法及び推論プログラム | |

| JP6779035B2 (ja) | 制御装置、水中航走体、制御方法およびプログラム | |

| JP7253233B2 (ja) | フィルタ装置、フィルタプログラム、フィルタ設計プログラム、参照信号生成装置及び参照信号生成プログラム | |

| JP2016164697A (ja) | 位置制御システム | |

| CN108388136B (zh) | 一种具有非线性输入的柔性弦线系统的振动控制方法 | |

| Ordóñez et al. | Adaptive control for a class of nonlinear systems with a time-varying structure | |

| KR20200122834A (ko) | 가상 환경에서 학습된 지능형 에이전트를 이용하여 실제 사물의 움직임을 제어하는 방법 및 장치 | |

| US20160065499A1 (en) | Method for provisioning a customized cloud stack | |

| JP2019133626A (ja) | 情報処理方法及び情報処理システム | |

| JP2020038656A (ja) | 制御器更新装置及び制御器更新プログラム | |

| JP6708925B2 (ja) | 制御システム | |

| JPH09136698A (ja) | 航空機舵面のサーボ制御システム | |

| JP2006268566A (ja) | 予測制御装置、予測制御方法、予測制御プログラム及び記憶媒体 | |

| Grimble | Reduced‐order non‐linear generalised minimum variance control for quasi‐linear parameter varying systems | |

| JP2021105818A (ja) | 2自由度制御システムの制御器設定方法 | |

| JP2025095227A (ja) | 制御システム、システム設計ツール、制御方法、および、コンピュータプログラム | |

| CN116075782B (zh) | 参数调整装置及参数调整方法 | |

| CN112415897B (zh) | 控制系统的优化方法、装置、系统、车辆、介质及设备 | |

| JP2012226551A (ja) | Pidゲイン調整装置及びpidゲイン調整方法 | |

| JP6838454B2 (ja) | 制御方法、制御装置及び制御プログラム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20220301 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20230220 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20230307 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20230317 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7253233 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |