JP7250641B2 - アライメント装置及び半導体装置の製造方法 - Google Patents

アライメント装置及び半導体装置の製造方法 Download PDFInfo

- Publication number

- JP7250641B2 JP7250641B2 JP2019144962A JP2019144962A JP7250641B2 JP 7250641 B2 JP7250641 B2 JP 7250641B2 JP 2019144962 A JP2019144962 A JP 2019144962A JP 2019144962 A JP2019144962 A JP 2019144962A JP 7250641 B2 JP7250641 B2 JP 7250641B2

- Authority

- JP

- Japan

- Prior art keywords

- alignment

- pitch

- patterns

- semiconductor

- stage

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/68—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for positioning, orientation or alignment

- H01L21/681—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for positioning, orientation or alignment using optical controlling means

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/67005—Apparatus not specifically provided for elsewhere

- H01L21/67011—Apparatus for manufacture or treatment

- H01L21/67092—Apparatus for mechanical treatment

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/544—Marks applied to semiconductor devices or parts, e.g. registration marks, alignment structures, wafer maps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/02—Bonding areas ; Manufacturing methods related thereto

- H01L24/07—Structure, shape, material or disposition of the bonding areas after the connecting process

- H01L24/08—Structure, shape, material or disposition of the bonding areas after the connecting process of an individual bonding area

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/93—Batch processes

- H01L24/94—Batch processes at wafer-level, i.e. with connecting carried out on a wafer comprising a plurality of undiced individual devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/065—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L25/0657—Stacked arrangements of devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/18—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof the devices being of types provided for in two or more different subgroups of the same main group of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/50—Multistep manufacturing processes of assemblies consisting of devices, each device being of a type provided for in group H01L27/00 or H01L29/00

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06V—IMAGE OR VIDEO RECOGNITION OR UNDERSTANDING

- G06V2201/00—Indexing scheme relating to image or video recognition or understanding

- G06V2201/06—Recognition of objects for industrial automation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L22/00—Testing or measuring during manufacture or treatment; Reliability measurements, i.e. testing of parts without further processing to modify the parts as such; Structural arrangements therefor

- H01L22/20—Sequence of activities consisting of a plurality of measurements, corrections, marking or sorting steps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2223/00—Details relating to semiconductor or other solid state devices covered by the group H01L23/00

- H01L2223/544—Marks applied to semiconductor devices or parts

- H01L2223/5442—Marks applied to semiconductor devices or parts comprising non digital, non alphanumeric information, e.g. symbols

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2223/00—Details relating to semiconductor or other solid state devices covered by the group H01L23/00

- H01L2223/544—Marks applied to semiconductor devices or parts

- H01L2223/54426—Marks applied to semiconductor devices or parts for alignment

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2223/00—Details relating to semiconductor or other solid state devices covered by the group H01L23/00

- H01L2223/544—Marks applied to semiconductor devices or parts

- H01L2223/54453—Marks applied to semiconductor devices or parts for use prior to dicing

- H01L2223/5446—Located in scribe lines

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/0212—Auxiliary members for bonding areas, e.g. spacers

- H01L2224/02122—Auxiliary members for bonding areas, e.g. spacers being formed on the semiconductor or solid-state body

- H01L2224/02163—Auxiliary members for bonding areas, e.g. spacers being formed on the semiconductor or solid-state body on the bonding area

- H01L2224/02165—Reinforcing structures

- H01L2224/02166—Collar structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/0212—Auxiliary members for bonding areas, e.g. spacers

- H01L2224/02122—Auxiliary members for bonding areas, e.g. spacers being formed on the semiconductor or solid-state body

- H01L2224/02233—Auxiliary members for bonding areas, e.g. spacers being formed on the semiconductor or solid-state body not in direct contact with the bonding area

- H01L2224/0224—Alignment aids

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/05001—Internal layers

- H01L2224/05075—Plural internal layers

- H01L2224/0508—Plural internal layers being stacked

- H01L2224/05085—Plural internal layers being stacked with additional elements, e.g. vias arrays, interposed between the stacked layers

- H01L2224/05089—Disposition of the additional element

- H01L2224/05093—Disposition of the additional element of a plurality of vias

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/07—Structure, shape, material or disposition of the bonding areas after the connecting process

- H01L2224/08—Structure, shape, material or disposition of the bonding areas after the connecting process of an individual bonding area

- H01L2224/081—Disposition

- H01L2224/0812—Disposition the bonding area connecting directly to another bonding area, i.e. connectorless bonding, e.g. bumpless bonding

- H01L2224/08135—Disposition the bonding area connecting directly to another bonding area, i.e. connectorless bonding, e.g. bumpless bonding the bonding area connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/08145—Disposition the bonding area connecting directly to another bonding area, i.e. connectorless bonding, e.g. bumpless bonding the bonding area connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/80001—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected by connecting a bonding area directly to another bonding area, i.e. connectorless bonding, e.g. bumpless bonding

- H01L2224/8012—Aligning

- H01L2224/80121—Active alignment, i.e. by apparatus steering, e.g. optical alignment using marks or sensors

- H01L2224/8013—Active alignment, i.e. by apparatus steering, e.g. optical alignment using marks or sensors using marks formed on the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/80001—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected by connecting a bonding area directly to another bonding area, i.e. connectorless bonding, e.g. bumpless bonding

- H01L2224/808—Bonding techniques

- H01L2224/80894—Direct bonding, i.e. joining surfaces by means of intermolecular attracting interactions at their interfaces, e.g. covalent bonds, van der Waals forces

- H01L2224/80895—Direct bonding, i.e. joining surfaces by means of intermolecular attracting interactions at their interfaces, e.g. covalent bonds, van der Waals forces between electrically conductive surfaces, e.g. copper-copper direct bonding, surface activated bonding

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/80001—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected by connecting a bonding area directly to another bonding area, i.e. connectorless bonding, e.g. bumpless bonding

- H01L2224/808—Bonding techniques

- H01L2224/80894—Direct bonding, i.e. joining surfaces by means of intermolecular attracting interactions at their interfaces, e.g. covalent bonds, van der Waals forces

- H01L2224/80896—Direct bonding, i.e. joining surfaces by means of intermolecular attracting interactions at their interfaces, e.g. covalent bonds, van der Waals forces between electrically insulating surfaces, e.g. oxide or nitride layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06524—Electrical connections formed on device or on substrate, e.g. a deposited or grown layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06593—Mounting aids permanently on device; arrangements for alignment

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/02—Bonding areas ; Manufacturing methods related thereto

- H01L24/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L24/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

- H01L2924/143—Digital devices

- H01L2924/1431—Logic devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

- H01L2924/143—Digital devices

- H01L2924/1434—Memory

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Manufacturing & Machinery (AREA)

- Container, Conveyance, Adherence, Positioning, Of Wafer (AREA)

- Multimedia (AREA)

- Theoretical Computer Science (AREA)

Description

このため、半導体基板にアライメント・マークが配置され、カメラ等を用いて、アライメント・マークの位置が確認される。

しかしながら、半導体基板毎にアライメント・マークの確認、アライメントを行うのは、煩雑であり、効率性に欠ける。

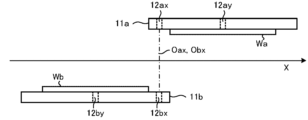

図1は、実施形態に係る半導体ウェハアライメント装置である。半導体ウェハアライメント装置は、ステージ11(11a,11b)、検出器12(12ax、12ay、12bx、12by)、ステージ移動機構13(13a,13b)、ローダ14(14a,14b)、オーバレイ計測器15,制御部16を有する。

半導体ウェハWa、Wbそれぞれに、位置合わせのための、アライメント・マークM(Ma,Mb)が形成される。

アライメント・マークMaは,半導体ウェハWaの下面に、アライメント・マークMbは,半導体ウェハWbの上面に、配置される。すなわち、アライメント・マークMa、Mbは、互いに向かい合う半導体ウェハWa、Wb上に配置される。

アライメント・マークMa,Mbは、例えば、半導体ウェハWa、Wbをチップに個片化する際のチップ間の境界領域であるダイシングライン上に配置されている。

また、ここでは、半導体ウェハWa、Wbそれぞれにアライメント・マークMa,Mbが1箇所ずつ配置されているが、複数箇所にアライメント・マークが配置されてもよい。

マークMax(Mbx)およびMay(Mby)はそれぞれ、X軸方向およびY軸方向の位置合わせに用いられる。

パターンPax1、Pax2(Pbx1、Pbx2)はそれぞれ、X方向に並ぶL(ライン)&S(スペース)のパターンである。

すなわち、X軸方向に沿って複数のラインパターンが、略同一の間隔(ピッチ)を有して配置される。パターンPax1、Pax2間(Pbx1、Pbx2間)で、ピッチが異なる。

パターンPbx1は、第3のピッチで配置される第3の複数のパターンに対応し、パターンPbx2は、前記第3のピッチと異なる第4のピッチで配置される第4の複数のパターンに対応する。

なお、第3のピッチは、第1のピッチと略等しくすることができ、第4のピッチは、第2のピッチと略等しくすることができる。

また、マークMay(Mby)に含まれ、X方向に並列して配置されるL&SパターンPay1、Pay2(あるいはPby1、Pby2)のラインが一致する箇所がY軸方向でのアライメント・ターゲット(アライメント位置)Tay(Tby)である。

図1,図2に示されるように、ステージ11a、11bに検出器12ax、12ay、12bx、12byが配置される。

検出器12axは、ステージ11aの下面上のX軸負方向側に配置され、検出器12bxは、ステージ11bの上面上のX軸正方向側に配置される。すなわち、検出器12ax、12bxは、ステージ11a,11bを位置合わせしたときに、X軸方向に離間して配置される。この結果、後述のように、検出器12ax、12bxそれぞれで、アライメント・マークMb(特に、Mbx),Ma(特に、Max)を同時に読み取ることが容易となる。

検出器12ay、12byはそれぞれ、ステージ11aの下面上のY軸正方向側、ステージ11bの上面上のY軸負方向側に配置される。検出器12ay、12byは、ステージ11a,11bを位置合わせしたときに、Y軸方向に離間して配置され、検出器12ay、12byそれぞれで、アライメント・マークMb(特に、Mby),Ma(特に、May)を同時に読み取ることが容易となる。

すなわち、ローダ14a,14bはそれぞれ、半導体ウェハWa,Wbをステージ11aの下面,ステージ11bの上面に載置する。載置された半導体ウェハWa,Wbは、ステージ11a,11bによって吸着、固定される。

この位置情報は、ステージ11a、11b間、ステージ11aと半導体ウェハWa間、およびステージ11bと半導体ウェハWb間で位置ズレを考慮しない仮の数値とすることができる。

制御部16は、ローダ14を制御して、アライメント・マークMaを有する半導体ウェハWaをステージ11aにロードし、かつアライメント・マークMbを有する半導体ウェハWbをステージ11bにロードさせる。

制御部16は、ステージ移動機構13および検出器12を制御して、検出器12ax、12bxの軸Oax、Obx(あるいは検出器12ay、12byの軸Oay、Oby)を一致させる。

このようにして、一致させた軸Oax、Obx(あるいは軸Oay、Oby)は、X軸(あるいはY軸)の位置の基準(原点)となる。

制御部16は、ステージ移動機構13および検出器12を制御して、検出器12ax、12bx(あるいは検出器12ay、12by)をアライメント・マークMb,Maに対向するように移動させ、検出する。すなわち、検出器12ax(あるいは検出器12ay)がアライメント・マークMbを検出し、検出器12bx(あるいは検出器12by)がアライメント・マークMaを検出する。

制御部16は、例えば、次の工程1)、2)によって、検出されたアライメント・マークMa,Mbに基づいて、半導体ウェハWa,Wbの位置ズレDxを算出する。

パターンPax1、Pax2(およびPbx1、Pbx2)中のパターンが互いに対応する第1(および第2)の位置(アライメント・ターゲットTax(、およびTbx))を算出する。

後述の式に基づいて、半導体ウェハWa,WbのX軸方向での位置ズレDxを算出できる。

制御部16は、ステージ移動機構13を制御して、半導体ウェハWa,Wbを相対的に距離Dx移動させる。

以下、半導体ウェハアライメント装置を用いる半導体装置の製造方法につき説明する。

ビット線BL、ソース配線層36、および選択ゲート配線層37は、他のプラグや配線層を介して、表層配線層41に接続されている。

表層配線層41は、パッド42、外部接続電極43に接続されている。

半導体装置は、アレイチップ、制御回路チップを貼り合わせた後、後述のように、基板30を除去し、外部接続電極44、保護層45を付加して作成される。

(1)半導体ウェハWa、Wbのロード(ステップS11および図5、図12,図13)

半導体ウェハWa、Wbをステージ11a,11bにロードする。ローダ14a,14bはそれぞれ、半導体ウェハWa,Wbをステージ11aの下面,ステージ11bの上面に載置する。載置された半導体ウェハWa,Wbは、ステージ11a,11bに吸着、固定される。

検出器12ax、12bxの軸を合わせる。すなわち、ステージ11a,11bを相対的にX軸方向に移動し、検出器12ax、12bxが互いを検出(撮影)できるようにする。その後、検出器12ax、12bxが互いを検出し、互いの軸Oax,Obxが一致するように、互いの位置を調節する。

ステージ11aをスキャンして(ここでは、X軸方向に距離Xoff移動)、検出器12axの軸Oaxが半導体ウェハWbのアライメント・マークMbが配置される座標近辺となるようにする。このときは、ウェハWa,Wbの位置ズレを無視する。

検出器12の中心軸のX座標Obx,Oaxからそれぞれアライメント位置Tax,Tbxまでの距離Xa,Xbを算出する。このとき、パターンPax1,Pax2およびPbx1、Pbx2のピッチの周期性の相違に基づき、ラインが一致する箇所Tax,Tbxを算出する。

1)パターンPax1のラインの配置と、ピッチの決定

画像処理により、パターンのPax1のライン毎に、その中心を決定する。例えば、ラインを構成する画素のX座標を加算し、画素数で除することで、各ラインの中心のX座標を算出できる。この処理をライン毎に行うことで、各ライン中心のX座標が求まる。このX座標の並びの差分(ピッチ)を求めることで、視野外のラインの配置を外挿できる。

パターンPax2においても同様に、ラインの中心のX座標方向での配置を求めることができる。

パターンPax1,パターンPax2のライン中心が最も近接するX座標がアライメント位置Taxに対応する。

検出器12の中心軸(X軸の基準:原点)Obx,Oaxそれぞれから、アライメント位置Tax,Tbxまでの距離Xa,Xbを算出する。

検出器12は、軸合わせされていることから、その後に(ステップS13において)ステージ11(ウェハWa)をX軸方向に相対移動した距離(第1のステージの相対的な移動量)Xoffが、軸Oax,Obx間の距離である。

この結果、半導体ウェハWa,Wb間のX軸方向のずれDxは、次の式(1)で算出できる。

Dx=Xa+Xb+Xoff …… 式(1)

ステージ11aをX軸方向に距離Dx移動し、半導体ウェハWa,WbをX軸方向で位置合わせを行う。

すなわち、アライメント位置Tax,Tbxを一致させる。これは、アライメント・マークMa,Mbを重ね合わせることにもなる。

なお、アライメント位置Taxpは、ステップS15においてステージ11aを移動する前のアライメント位置Taxである。

以上は、X軸方向での位置合わせである。Y軸方向でも同様にステップS12~S15のプロセスを行う。

このようにして、X軸、Y軸方向双方での半導体ウェハWa,Wbの位置合わせが完了する。

半導体ウェハWa,Wbの位置合わせが完了すると、半導体ウェハWa,Wbが貼り合わされる。ここでは、半導体ウェハWa,Wbの面を接触した状態で、半導体ウェハWa,Wbを加熱し、表層配線層41、回路側配線層51を接合する。

半導体ウェハWa,Wbの貼合後、これらの加工前(例えば、基板30の除去前)に、オーバレイ計測部15によってオーバーレイ計測を行う。この計測に、アライメント・マークMa,Mbが用いられる。

レンズ22a~22cは、収束光を平行光に、あるいはその逆に変換する。

ハーフミラー23は、入射した光の一部を反射し、一部を透過させる反射板である。

検出器24は、入射した光の像を撮影する、例えば、光学的撮像装置(一例として、CCD:Charge Coupled Device)である。

ここでは、マークMax,Mbxを用いて、X軸方向の位置ズレを測定しているが、マークMay,Mbyを用いて、Y軸方向の位置ズレを測定できる。

また、アライメント・マークMa,Mbの一部の仮像から、アライメント位置Tax,Tbxを求めることも可能であり、この点も、効率的なアライメントに寄与する。

Claims (5)

- 第1、第2のアライメント・マークが配置される第1、第2の半導体基板をそれぞれ保持する第1および第2のステージと、

前記第1、第2のステージにそれぞれ配置される第1、第2の検出器と、

前記第1、第2のステージを相対的に移動させる移動機構と、

前記第1、第2の検出器、および前記移動機構を制御して、前記第1の検出器に前記第2のアライメント・マークを検出させ、前記第2の検出器に前記第1のアライメント・マークを検出させ、

前記検出の結果に基づいて、前記第1および第2の半導体基板の位置ズレを算出する、制御部と、

を具備し、

前記第1のアライメント・マークが、

第1のピッチで配置される第1の複数のパターンと、

前記第1のピッチと異なる第2のピッチで配置される第2の複数のパターンと、を有し、

前記第2のアライメント・マークが、

第3のピッチで配置される第3の複数のパターンと、

前記第3のピッチと異なる第4のピッチで配置される第4の複数のパターンと、を有する、アライメント装置。 - 前記第1、第2の複数のパターンが、並列して配置される

請求項1に記載のアライメント装置。 - 前記制御部が、

前記第1、第2の複数のパターンのいずれかが互いに対応する第1の位置を算出し、前記第3、第4の複数のパターンのいずれかが互いに対応する第2の位置を算出し、

前記第1の位置および前記第2の位置に基づいて、前記第1、第2の半導体基板の位置ズレを算出する、

請求項1または2に記載のアライメント装置。 - 前記制御部が、前記第1または第2の複数のパターンの傾きに基づいて、前記移動機構を制御して、前記第1の半導体基板を回転させる、

請求項1乃至3のいずれか1項に記載のアライメント装置。 - 第1のアライメント・マークを有する第1の半導体基板を第1のステージにロードし、かつ第2のアライメント・マークを有する第2の半導体基板を第2のステージにロードする工程と、

前記第1のステージに配置される第1の検出器が前記第2のアライメント・マークを検出し、前記第2のステージに配置される第2の検出器が前記第1のアライメント・マークを検出する工程と、

前記検出の結果に基づいて、前記第1および第2の半導体基板の位置を合わせる工程と、

前記第1、第2の半導体基板を貼り合わせる工程と、

を具備し、

前記第1のアライメント・マークが、

第1のピッチで配置される第1の複数のパターンと、

前記第1のピッチと異なる第2のピッチで配置される第2の複数のパターンと、を有し、

前記第2のアライメント・マークが、

第3のピッチで配置される第3の複数のパターンと、

前記第3のピッチと異なる第4のピッチで配置される第4の複数のパターンと、を有する、半導体装置の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2019144962A JP7250641B2 (ja) | 2019-08-06 | 2019-08-06 | アライメント装置及び半導体装置の製造方法 |

| US16/810,945 US11387131B2 (en) | 2019-08-06 | 2020-03-06 | Alignment apparatus and method of manufacturing semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2019144962A JP7250641B2 (ja) | 2019-08-06 | 2019-08-06 | アライメント装置及び半導体装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2021027208A JP2021027208A (ja) | 2021-02-22 |

| JP2021027208A5 JP2021027208A5 (ja) | 2022-04-11 |

| JP7250641B2 true JP7250641B2 (ja) | 2023-04-03 |

Family

ID=74498344

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019144962A Active JP7250641B2 (ja) | 2019-08-06 | 2019-08-06 | アライメント装置及び半導体装置の製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US11387131B2 (ja) |

| JP (1) | JP7250641B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11688717B2 (en) * | 2021-08-26 | 2023-06-27 | Taiwan Semiconductor Manufacturing Company, Ltd. | Mechanical wafer alignment detection for bonding process |

| US20230275149A1 (en) * | 2022-02-28 | 2023-08-31 | Taiwan Semiconductor Manufacturing Company, Ltd. | Gaa ldmos structure for hv operation |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010267682A (ja) | 2009-05-12 | 2010-11-25 | Bondtech Inc | アライメント装置、アライメント方法および半導体装置 |

| JP2014168089A (ja) | 2014-04-23 | 2014-09-11 | Nikon Corp | 基板重ね合わせ装置、基板重ね合わせ方法、及びデバイスの製造方法 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002032031A (ja) * | 2000-05-12 | 2002-01-31 | Seiko Epson Corp | 電気光学装置の製造方法、端子の接続方法、電気光学装置および電子機器 |

| TW526573B (en) | 2000-12-27 | 2003-04-01 | Koninkl Philips Electronics Nv | Method of measuring overlay |

| JP5369588B2 (ja) | 2008-10-01 | 2013-12-18 | 株式会社ニコン | 接合評価方法、接合評価装置、基板貼り合わせ装置、評価ゲージおよび積層型半導体装置 |

| JP2011159908A (ja) | 2010-02-03 | 2011-08-18 | Sony Corp | 薄膜トランジスタおよびその製造方法、並びに表示装置 |

| US9851645B2 (en) * | 2013-12-06 | 2017-12-26 | Ev Group E. Thallner Gmbh | Device and method for aligning substrates |

| KR102429940B1 (ko) | 2016-07-12 | 2022-08-08 | 가부시키가이샤 니콘 | 적층 기판 제조 방법, 적층 기판 제조 장치, 적층 기판 제조 시스템, 및 기판 처리 장치 |

-

2019

- 2019-08-06 JP JP2019144962A patent/JP7250641B2/ja active Active

-

2020

- 2020-03-06 US US16/810,945 patent/US11387131B2/en active Active

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010267682A (ja) | 2009-05-12 | 2010-11-25 | Bondtech Inc | アライメント装置、アライメント方法および半導体装置 |

| JP2014168089A (ja) | 2014-04-23 | 2014-09-11 | Nikon Corp | 基板重ね合わせ装置、基板重ね合わせ方法、及びデバイスの製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20210043488A1 (en) | 2021-02-11 |

| JP2021027208A (ja) | 2021-02-22 |

| US11387131B2 (en) | 2022-07-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| TWI685037B (zh) | 用於晶圓鍵合對準補償的方法和系統 | |

| TWI478271B (zh) | Substrate bonding device and substrate bonding method | |

| US9960063B2 (en) | Substrate transport apparatus and substrate transport method | |

| JP3203719B2 (ja) | 露光装置、その露光装置により製造されるデバイス、露光方法、およびその露光方法を用いたデバイス製造方法 | |

| US7737426B2 (en) | Substrate positioning device and substrate positioning method for a substrate having a transparent layer and a nontransparent layer | |

| TWI225841B (en) | Robot system for transferring substrates and substrate transferring container used by the same | |

| JP7250641B2 (ja) | アライメント装置及び半導体装置の製造方法 | |

| TWI726748B (zh) | 高精度鍵合頭定位方法及設備 | |

| TWI442494B (zh) | Probe device and detection method | |

| TWI598986B (zh) | 判定對準誤差的方法及裝置 | |

| US9607389B2 (en) | Alignment apparatus | |

| TWI675431B (zh) | 基板搬送裝置及求出基板搬送機器人與基板載置部之位置關係之方法 | |

| US20180096903A1 (en) | Fan-out panel level package and method of fabricating the same | |

| JPH09306977A (ja) | ウエハ検査装置等におけるウエハの位置決め方法 | |

| TWI543294B (zh) | 半導體晶圓之對準方法 | |

| JPH05198662A (ja) | プローブ装置及び同装置におけるアライメント方法 | |

| US20180005369A1 (en) | Inspection method, inspection system, and method of manufacturing semiconductor package using the same | |

| JP4702888B2 (ja) | 位置検出方法および位置合わせ方法 | |

| JP2007227627A (ja) | 基板処理装置及び基板の受け渡し位置の調整方法並びに記憶媒体 | |

| US20150355108A1 (en) | Inspection system and methods of fabricating and inspecting semiconductor device using the same | |

| TW201908692A (zh) | 攝影裝置、凸塊檢查裝置以及攝影方法 | |

| TWI740266B (zh) | 檢查鍵合的半導體晶片的設備和方法 | |

| JP2023045194A (ja) | プリアライメント装置及び方法 | |

| TWI525737B (zh) | 可挑揀高長寬比晶粒之晶粒挑揀裝置及方法 | |

| US20230411197A1 (en) | Bonding apparatus, bonding method, and method of manufacturing semiconductor device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220401 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20220401 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20230221 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20230224 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20230322 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 7250641 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |