JP7166324B2 - リン化インジウム基板、リン化インジウム基板の製造方法及び半導体エピタキシャルウエハ - Google Patents

リン化インジウム基板、リン化インジウム基板の製造方法及び半導体エピタキシャルウエハ Download PDFInfo

- Publication number

- JP7166324B2 JP7166324B2 JP2020211685A JP2020211685A JP7166324B2 JP 7166324 B2 JP7166324 B2 JP 7166324B2 JP 2020211685 A JP2020211685 A JP 2020211685A JP 2020211685 A JP2020211685 A JP 2020211685A JP 7166324 B2 JP7166324 B2 JP 7166324B2

- Authority

- JP

- Japan

- Prior art keywords

- indium phosphide

- wafer

- substrate

- phosphide substrate

- edge portion

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- C—CHEMISTRY; METALLURGY

- C30—CRYSTAL GROWTH

- C30B—SINGLE-CRYSTAL GROWTH; UNIDIRECTIONAL SOLIDIFICATION OF EUTECTIC MATERIAL OR UNIDIRECTIONAL DEMIXING OF EUTECTOID MATERIAL; REFINING BY ZONE-MELTING OF MATERIAL; PRODUCTION OF A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; SINGLE CRYSTALS OR HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; AFTER-TREATMENT OF SINGLE CRYSTALS OR A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; APPARATUS THEREFOR

- C30B29/00—Single crystals or homogeneous polycrystalline material with defined structure characterised by the material or by their shape

- C30B29/10—Inorganic compounds or compositions

- C30B29/40—AIIIBV compounds wherein A is B, Al, Ga, In or Tl and B is N, P, As, Sb or Bi

-

- C—CHEMISTRY; METALLURGY

- C30—CRYSTAL GROWTH

- C30B—SINGLE-CRYSTAL GROWTH; UNIDIRECTIONAL SOLIDIFICATION OF EUTECTIC MATERIAL OR UNIDIRECTIONAL DEMIXING OF EUTECTOID MATERIAL; REFINING BY ZONE-MELTING OF MATERIAL; PRODUCTION OF A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; SINGLE CRYSTALS OR HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; AFTER-TREATMENT OF SINGLE CRYSTALS OR A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; APPARATUS THEREFOR

- C30B25/00—Single-crystal growth by chemical reaction of reactive gases, e.g. chemical vapour-deposition growth

- C30B25/02—Epitaxial-layer growth

- C30B25/18—Epitaxial-layer growth characterised by the substrate

- C30B25/186—Epitaxial-layer growth characterised by the substrate being specially pre-treated by, e.g. chemical or physical means

-

- C—CHEMISTRY; METALLURGY

- C30—CRYSTAL GROWTH

- C30B—SINGLE-CRYSTAL GROWTH; UNIDIRECTIONAL SOLIDIFICATION OF EUTECTIC MATERIAL OR UNIDIRECTIONAL DEMIXING OF EUTECTOID MATERIAL; REFINING BY ZONE-MELTING OF MATERIAL; PRODUCTION OF A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; SINGLE CRYSTALS OR HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; AFTER-TREATMENT OF SINGLE CRYSTALS OR A HOMOGENEOUS POLYCRYSTALLINE MATERIAL WITH DEFINED STRUCTURE; APPARATUS THEREFOR

- C30B33/00—After-treatment of single crystals or homogeneous polycrystalline material with defined structure

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/80—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials

- H10D62/85—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials being Group III-V materials, e.g. GaAs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

- H10P14/29—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials characterised by the substrates

- H10P14/2901—Materials

- H10P14/2907—Materials being Group IIIA-VA materials

- H10P14/2909—Phosphides

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P52/00—Grinding, lapping or polishing of wafers, substrates or parts of devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P90/00—Preparation of wafers not covered by a single main group of this subclass, e.g. wafer reinforcement

- H10P90/12—Preparing bulk and homogeneous wafers

- H10P90/126—Preparing bulk and homogeneous wafers by chemical etching

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P90/00—Preparation of wafers not covered by a single main group of this subclass, e.g. wafer reinforcement

- H10P90/12—Preparing bulk and homogeneous wafers

- H10P90/128—Preparing bulk and homogeneous wafers by edge treatment, e.g. chamfering

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P90/00—Preparation of wafers not covered by a single main group of this subclass, e.g. wafer reinforcement

- H10P90/12—Preparing bulk and homogeneous wafers

- H10P90/129—Preparing bulk and homogeneous wafers by polishing

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

- H10P14/29—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials characterised by the substrates

- H10P14/2924—Structures

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

- H10P14/29—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials characterised by the substrates

- H10P14/2924—Structures

- H10P14/2925—Surface structures

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

- H10P14/32—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials characterised by intermediate layers between substrates and deposited layers

- H10P14/3202—Materials thereof

- H10P14/3214—Materials thereof being Group IIIA-VA semiconductors

- H10P14/3221—Arsenides

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

- H10P14/34—Deposited materials, e.g. layers

- H10P14/3402—Deposited materials, e.g. layers characterised by the chemical composition

- H10P14/3414—Deposited materials, e.g. layers characterised by the chemical composition being group IIIA-VIA materials

- H10P14/3418—Phosphides

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

- H10P14/36—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials characterised by treatments done before the formation of the materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P90/00—Preparation of wafers not covered by a single main group of this subclass, e.g. wafer reinforcement

- H10P90/12—Preparing bulk and homogeneous wafers

Landscapes

- Chemical & Material Sciences (AREA)

- Engineering & Computer Science (AREA)

- Crystallography & Structural Chemistry (AREA)

- Materials Engineering (AREA)

- Metallurgy (AREA)

- Organic Chemistry (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- Inorganic Chemistry (AREA)

- Mechanical Treatment Of Semiconductor (AREA)

- Crystals, And After-Treatments Of Crystals (AREA)

- Recrystallisation Techniques (AREA)

Description

(1)基板のエッジ部が、前記基板の一方の表面から傾斜した面、及び、前記基板の一方の表面から傾斜した面が終了する位置から、前記基板の他方の表面から傾斜した面が終了する位置までの、曲率をもった面を有し、前記基板のエッジ部は、前記一方の表面から傾斜した面におけるレーザー顕微鏡によって測定された、二乗平均平方根高さSqが0.15μm以下であり、前記曲率をもった面におけるレーザー顕微鏡によって測定された、二乗平均平方根高さSqが0.15μm以下である、リン化インジウム基板。

(2)前記曲率をもった面における前記二乗平均平方根高さSqが0.07μm以下である、(1)に記載のリン化インジウム基板。

(3)リン化インジウムのウエハのエッジ部が、

前記ウエハの一方の表面から傾斜した面、及び、

前記ウエハの一方の表面から傾斜した面が終了する位置から、前記ウエハの他方の表面から傾斜した面が終了する位置までの、曲率をもった面

を有するように、前記ウエハの外周部分の面取りを行う工程と、

前記面取り後に生じたウエハのエッジ部の表面全体を、番手#4000の研磨フィルムにて研磨する工程と、

前記エッジ部の研磨後のウエハをエッチングする工程と、

を含む、(1)または(2)に記載のリン化インジウム基板の製造方法。

(4)前記リン化インジウムのウエハの外周部分の面取りを行う工程と、前記面取り後に生じたウエハのエッジ部の表面全体を、番手#4000の研磨フィルムにて研磨する工程と、の間に、ウエハの少なくとも一方の表面を研磨する工程を更に含む、(3)に記載のリン化インジウム基板の製造方法。

(5)(1)または(2)に記載のリン化インジウム基板と、前記リン化インジウム基板の主面に設けられたエピタキシャル結晶層と、を有する、半導体エピタキシャルウエハ。

以下、本実施形態のリン化インジウム基板の構成について説明する。

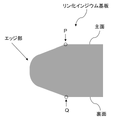

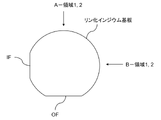

本実施形態のリン化インジウム(InP)基板は、基板表面、基板裏面、及び、エッジ部を備える。エッジ部は、結晶の方位を示すオリエンテーションフラット(OF)、及び、基板の主面と裏面とを見分けるためのインデックスフラット(IF)を有していてもよい。

次に、本発明の実施形態に係るリン化インジウム基板の製造方法について説明する。

リン化インジウム基板の製造方法としては、まず、公知の方法にてリン化インジウムのインゴットを作製する。

次に、リン化インジウムのインゴットを研削して円筒にする。このとき、ウエハの外周部分の所定位置に、オリエンテーションフラット(OF)、及び、インデックスフラット(IF)を形成してもよい。

次に、研削したリン化インジウムのインゴットから主面及び裏面を有するウエハを切り出す。このとき、リン化インジウムのインゴットの結晶両端を所定の結晶面に沿って、ワイヤーソー等を用いて切断し、複数のウエハを所定の厚さに切り出す。

次に、ウエハの主面を鏡面研磨用の研磨材で研磨して鏡面に仕上げる。

次に、洗浄を行うことで、本発明の実施形態に係るリン化インジウム基板が製造される。

本発明の実施形態に係るリン化インジウム基板の主面に対し、公知の方法で半導体薄膜をエピタキシャル成長させることで、エピタキシャル結晶層を形成し、半導体エピタキシャルウエハを作製することができる。当該エピタキシャル成長の例としては、リン化インジウム基板の主面に、InAlAsバッファ層、InGaAsチャネル層、InAlAsスペーサ層、InP電子供給層をエピタキシャル成長させたHEMT構造を形成してもよい。このようなHEMT構造を有する半導体エピタキシャルウエハを作製する場合、一般には、鏡面仕上げしたリン化インジウム基板に、硫酸/過酸化水素水などのエッチング溶液によるエッチング処理を施して、基板表面に付着したケイ素(Si)等の不純物を除去する。このエッチング処理後のリン化インジウム基板の裏面をサセプターに接触させて支持した状態で、リン化インジウム基板の主面に、分子線エピタキシャル成長法(MBE:Molecular Beam Epitaxy)又は有機金属気相成長(MOCVD:Metal Organic Chemical Vapor Deposition)によりエピタキシャル膜を形成する。

まず、所定の直径で育成したリン化インジウムの単結晶のインゴットを準備した。

次に、リン化インジウムの単結晶のインゴットの外周を研削し、円筒にした。このとき、ウエハの外周部分の所定位置に、オリエンテーションフラット(OF)、及び、インデックスフラット(IF)を形成した。

比較例1として、上述の実施例1において、ラッピング工程の後、研磨フィルムによるエッジ部の研磨を実施せず、二次エッチングを実施した以外は、実施例1と同様にしてリン化インジウム基板を作製した。

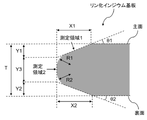

リン化インジウム基板の測定対象となるエッジ部は、図2に示すように、OFの反対側に位置する領域(A-領域)と、IFの反対側に位置する領域(B-領域)とに分け、さらに、図3に示すように、(1)主面から傾斜した面を測定領域1とし、さらに、(2)測定領域1の主面から傾斜した面が終了する位置から、裏面から傾斜した面が終了する位置までの、曲率をもった面となるエッジ部の円弧領域を測定領域2とした。

そして、A-領域における測定領域1を「A-領域1」とし、A-領域における測定領域2を「A-領域2」とし、B-領域における測定領域1を「B-領域1」とし、B-領域における測定領域2を「B-領域2」とした。

なお、エッジ部の曲率を除去して評価するため、カットオフフィルター(Lフィルター:カットする波長20μm)を用いて測定を実施した。

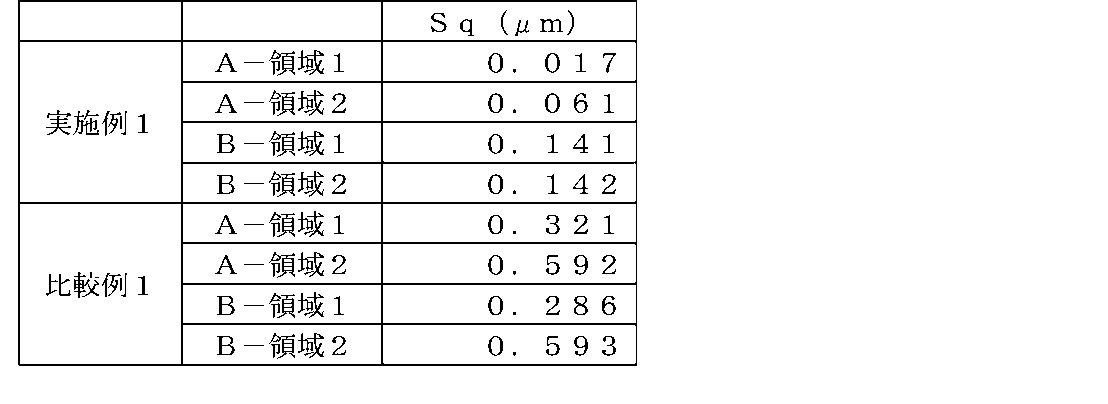

評価結果を表1に示す。

実施例1では、基板のエッジ部のA-領域1、2、及び、B-領域1、2の、各表面粗さについて、レーザー顕微鏡によって測定された、二乗平均平方根高さSqが0.15μm以下である、リン化インジウム基板が得られた。基板のエッジ部表面全体において、番手#4000の研磨フィルムにて研磨したものであり、エッジ部表面全体において、測定領域1に対応する傾斜領域は、A-領域1及びB-領域1と同様の表面粗さが得られているものと考えられる。また、エッジ部表面全体において、上述の測定領域2のようなエッジ部の測定領域2に対応する比較的平坦な領域(円弧領域)は、A-領域2及びB-領域2と同様の表面粗さが得られているものと考えられる。

なお、エッジ部の領域1と領域2とで二乗平均平方根高さSqに違いが生じたのは、研磨フィルムにてエッジ部を研磨した後の、鏡面研磨などによる基板表面の研磨による影響が出ているものと考えられる。あくまで、基板のエッジ部表面全体において、番手#4000の研磨フィルムにて研磨した直後であれば、エッジ部表面全体において、どの領域を測定しても、二乗平均平方根高さSqは同様であるものと考えられる。

TOF-SIMS分析の分析条件は以下の通りである。

装置名:Physical Electronics TRIFT III

イオン源:Au+

一次イオンエネルギー:22kV

分析エリア:25μm×25μm

Claims (5)

- 基板のエッジ部が、

前記基板の一方の表面から傾斜した面、及び、

前記基板の一方の表面から傾斜した面が終了する位置から、前記基板の他方の表面から傾斜した面が終了する位置までの、曲率をもった面

を有し、

前記基板のエッジ部は、前記一方の表面から傾斜した面におけるレーザー顕微鏡によって測定された、二乗平均平方根高さSqが0.15μm以下であり、

前記曲率をもった面におけるレーザー顕微鏡によって測定された、二乗平均平方根高さSqが0.15μm以下である、リン化インジウム基板。 - 前記曲率をもった面における前記二乗平均平方根高さSqが0.07μm以下である、請求項1に記載のリン化インジウム基板。

- リン化インジウムのウエハのエッジ部が、

前記ウエハの一方の表面から傾斜した面、及び、

前記ウエハの一方の表面から傾斜した面が終了する位置から、前記ウエハの他方の表面から傾斜した面が終了する位置までの、曲率をもった面

を有するように、前記ウエハの外周部分の面取りを行う工程と、

前記面取り後に生じたウエハのエッジ部の表面全体を、番手#4000の研磨フィルムにて研磨する工程と、

前記エッジ部の研磨後のウエハをエッチングする工程と、

を含む、請求項1または2に記載のリン化インジウム基板の製造方法。 - 前記リン化インジウムのウエハの外周部分の面取りを行う工程と、前記面取り後に生じたウエハのエッジ部の表面全体を、番手#4000の研磨フィルムにて研磨する工程と、の間に、ウエハの少なくとも一方の表面を研磨する工程を更に含む、請求項3に記載のリン化インジウム基板の製造方法。

- 請求項1または2に記載のリン化インジウム基板と、前記リン化インジウム基板の主面に設けられたエピタキシャル結晶層と、を有する、半導体エピタキシャルウエハ。

Priority Applications (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2020211685A JP7166324B2 (ja) | 2020-12-21 | 2020-12-21 | リン化インジウム基板、リン化インジウム基板の製造方法及び半導体エピタキシャルウエハ |

| CN202180054263.9A CN116057212A (zh) | 2020-12-21 | 2021-10-07 | 磷化铟基板、磷化铟基板的制造方法以及半导体外延片 |

| US18/034,327 US20230392289A1 (en) | 2020-12-21 | 2021-10-07 | Indium phosphide substrate, method for manufacturing indium phosphide substrate, and semiconductor epitaxial wafer |

| EP21909886.0A EP4215650A4 (en) | 2020-12-21 | 2021-10-07 | INDIUM PHOSPHIDE SUBSTRATE, METHOD FOR MANUFACTURING INDIUM PHOSPHIDE SUBSTRATE, AND SEMICONDUCTOR EPITAXIAL WAFER |

| PCT/JP2021/037241 WO2022137728A1 (ja) | 2020-12-21 | 2021-10-07 | リン化インジウム基板、リン化インジウム基板の製造方法及び半導体エピタキシャルウエハ |

| TW110138696A TWI771208B (zh) | 2020-12-21 | 2021-10-19 | 磷化銦基板、磷化銦基板之製造方法及半導體磊晶晶圓 |

| JP2022020684A JP2022098504A (ja) | 2020-12-21 | 2022-02-14 | リン化インジウム基板、リン化インジウム基板の製造方法及び半導体エピタキシャルウエハ |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2020211685A JP7166324B2 (ja) | 2020-12-21 | 2020-12-21 | リン化インジウム基板、リン化インジウム基板の製造方法及び半導体エピタキシャルウエハ |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2022020684A Division JP2022098504A (ja) | 2020-12-21 | 2022-02-14 | リン化インジウム基板、リン化インジウム基板の製造方法及び半導体エピタキシャルウエハ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2022098257A JP2022098257A (ja) | 2022-07-01 |

| JP7166324B2 true JP7166324B2 (ja) | 2022-11-07 |

Family

ID=82158951

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2020211685A Active JP7166324B2 (ja) | 2020-12-21 | 2020-12-21 | リン化インジウム基板、リン化インジウム基板の製造方法及び半導体エピタキシャルウエハ |

| JP2022020684A Withdrawn JP2022098504A (ja) | 2020-12-21 | 2022-02-14 | リン化インジウム基板、リン化インジウム基板の製造方法及び半導体エピタキシャルウエハ |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2022020684A Withdrawn JP2022098504A (ja) | 2020-12-21 | 2022-02-14 | リン化インジウム基板、リン化インジウム基板の製造方法及び半導体エピタキシャルウエハ |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US20230392289A1 (ja) |

| EP (1) | EP4215650A4 (ja) |

| JP (2) | JP7166324B2 (ja) |

| CN (1) | CN116057212A (ja) |

| TW (1) | TWI771208B (ja) |

| WO (1) | WO2022137728A1 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7166323B2 (ja) * | 2020-12-21 | 2022-11-07 | Jx金属株式会社 | リン化インジウム基板、リン化インジウム基板の製造方法及び半導体エピタキシャルウエハ |

| WO2025098595A1 (en) * | 2023-11-07 | 2025-05-15 | Ams-Osram International Gmbh | Growth substrate and method for processing an optoelectronic device |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001135557A (ja) | 1999-11-08 | 2001-05-18 | Nikko Materials Co Ltd | 化合物半導体ウェハ |

| JP2012129416A (ja) | 2010-12-16 | 2012-07-05 | Shin Etsu Handotai Co Ltd | 半導体ウェーハ及びその製造方法 |

| JP2012174935A (ja) | 2011-02-22 | 2012-09-10 | Shin Etsu Handotai Co Ltd | エピタキシャルウェーハの製造方法 |

| JP2013153181A (ja) | 2009-03-04 | 2013-08-08 | Siltronic Ag | エピタキシャル被覆されたシリコンウェハ及びエピタキシャル被覆されたシリコンウェハの製造方法 |

| JP2019046859A (ja) | 2017-08-30 | 2019-03-22 | 昭和電工株式会社 | SiCエピタキシャルウェハ及びその製造方法 |

| JP2019219495A (ja) | 2018-06-19 | 2019-12-26 | 信越化学工業株式会社 | フォトマスクブランク関連基板の評価方法 |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4207976B2 (ja) * | 2006-05-17 | 2009-01-14 | 住友電気工業株式会社 | 化合物半導体基板の表面処理方法、および化合物半導体結晶の製造方法 |

| JPS6117257A (ja) | 1984-07-04 | 1986-01-25 | Victor Co Of Japan Ltd | 磁気記録再生装置 |

| JPH11204493A (ja) * | 1998-01-09 | 1999-07-30 | Komatsu Electron Metals Co Ltd | 半導体ウェハの製造方法 |

| JP3534115B1 (ja) * | 2003-04-02 | 2004-06-07 | 住友電気工業株式会社 | エッジ研磨した窒化物半導体基板とエッジ研磨したGaN自立基板及び窒化物半導体基板のエッジ加工方法 |

| DE102005034120B4 (de) * | 2005-07-21 | 2013-02-07 | Siltronic Ag | Verfahren zur Herstellung einer Halbleiterscheibe |

| JP2007042748A (ja) * | 2005-08-01 | 2007-02-15 | Hitachi Cable Ltd | 化合物半導体ウェハ |

| KR20080013059A (ko) * | 2006-08-07 | 2008-02-13 | 삼성전자주식회사 | 씨엠피공정설비의 웨이퍼 검사장치 및 그 방법 |

| JP4395812B2 (ja) * | 2008-02-27 | 2010-01-13 | 住友電気工業株式会社 | 窒化物半導体ウエハ−加工方法 |

| JP5644401B2 (ja) * | 2010-11-15 | 2014-12-24 | 株式会社Sumco | エピタキシャルウェーハの製造方法およびエピタキシャルウェーハ |

| JP5880449B2 (ja) * | 2011-01-26 | 2016-03-09 | 旭硝子株式会社 | フォトマスクの製造方法 |

| CN111952150B (zh) * | 2015-02-09 | 2023-06-20 | 住友电气工业株式会社 | 磷化铟衬底和制造磷化铟衬底的方法 |

| CN109689946B (zh) * | 2017-04-28 | 2021-03-12 | Jx金属株式会社 | 半导体晶圆及半导体晶圆的研磨方法 |

| JP7381214B2 (ja) * | 2019-03-27 | 2023-11-15 | 株式会社東京精密 | ブラストユニット付き面取り装置 |

| JP7166323B2 (ja) * | 2020-12-21 | 2022-11-07 | Jx金属株式会社 | リン化インジウム基板、リン化インジウム基板の製造方法及び半導体エピタキシャルウエハ |

-

2020

- 2020-12-21 JP JP2020211685A patent/JP7166324B2/ja active Active

-

2021

- 2021-10-07 US US18/034,327 patent/US20230392289A1/en active Pending

- 2021-10-07 WO PCT/JP2021/037241 patent/WO2022137728A1/ja not_active Ceased

- 2021-10-07 EP EP21909886.0A patent/EP4215650A4/en active Pending

- 2021-10-07 CN CN202180054263.9A patent/CN116057212A/zh active Pending

- 2021-10-19 TW TW110138696A patent/TWI771208B/zh active

-

2022

- 2022-02-14 JP JP2022020684A patent/JP2022098504A/ja not_active Withdrawn

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001135557A (ja) | 1999-11-08 | 2001-05-18 | Nikko Materials Co Ltd | 化合物半導体ウェハ |

| JP2013153181A (ja) | 2009-03-04 | 2013-08-08 | Siltronic Ag | エピタキシャル被覆されたシリコンウェハ及びエピタキシャル被覆されたシリコンウェハの製造方法 |

| JP2012129416A (ja) | 2010-12-16 | 2012-07-05 | Shin Etsu Handotai Co Ltd | 半導体ウェーハ及びその製造方法 |

| JP2012174935A (ja) | 2011-02-22 | 2012-09-10 | Shin Etsu Handotai Co Ltd | エピタキシャルウェーハの製造方法 |

| JP2019046859A (ja) | 2017-08-30 | 2019-03-22 | 昭和電工株式会社 | SiCエピタキシャルウェハ及びその製造方法 |

| JP2019219495A (ja) | 2018-06-19 | 2019-12-26 | 信越化学工業株式会社 | フォトマスクブランク関連基板の評価方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| TWI771208B (zh) | 2022-07-11 |

| EP4215650A1 (en) | 2023-07-26 |

| JP2022098504A (ja) | 2022-07-01 |

| WO2022137728A1 (ja) | 2022-06-30 |

| US20230392289A1 (en) | 2023-12-07 |

| CN116057212A (zh) | 2023-05-02 |

| JP2022098257A (ja) | 2022-07-01 |

| TW202225090A (zh) | 2022-07-01 |

| EP4215650A4 (en) | 2024-10-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7158594B2 (ja) | リン化インジウム基板 | |

| CN113207310A (zh) | 磷化铟基板、半导体外延晶片以及磷化铟基板的制造方法 | |

| JP7166324B2 (ja) | リン化インジウム基板、リン化インジウム基板の製造方法及び半導体エピタキシャルウエハ | |

| JP6761915B1 (ja) | リン化インジウム基板、半導体エピタキシャルウエハ、及びリン化インジウム基板の製造方法 | |

| JP6761916B1 (ja) | リン化インジウム基板、半導体エピタキシャルウエハ、及びリン化インジウム基板の製造方法 | |

| JP7166323B2 (ja) | リン化インジウム基板、リン化インジウム基板の製造方法及び半導体エピタキシャルウエハ | |

| TWI810847B (zh) | 磷化銦基板 | |

| US12065759B2 (en) | Indium phosphide substrate | |

| JP7713056B1 (ja) | リン化インジウム基板及び半導体エピタキシャルウエハ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20210311 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20210311 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20210407 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20210420 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210608 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20210907 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20211101 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20211130 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220214 |

|

| C60 | Trial request (containing other claim documents, opposition documents) |

Free format text: JAPANESE INTERMEDIATE CODE: C60 Effective date: 20220214 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20220224 |

|

| C21 | Notice of transfer of a case for reconsideration by examiners before appeal proceedings |

Free format text: JAPANESE INTERMEDIATE CODE: C21 Effective date: 20220301 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20220401 |

|

| C211 | Notice of termination of reconsideration by examiners before appeal proceedings |

Free format text: JAPANESE INTERMEDIATE CODE: C211 Effective date: 20220405 |

|

| C22 | Notice of designation (change) of administrative judge |

Free format text: JAPANESE INTERMEDIATE CODE: C22 Effective date: 20220726 |

|

| C22 | Notice of designation (change) of administrative judge |

Free format text: JAPANESE INTERMEDIATE CODE: C22 Effective date: 20220823 |

|

| C23 | Notice of termination of proceedings |

Free format text: JAPANESE INTERMEDIATE CODE: C23 Effective date: 20220913 |

|

| C03 | Trial/appeal decision taken |

Free format text: JAPANESE INTERMEDIATE CODE: C03 Effective date: 20221011 |

|

| C30A | Notification sent |

Free format text: JAPANESE INTERMEDIATE CODE: C3012 Effective date: 20221011 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20221025 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 7166324 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |