以下、本発明の実施の形態について図面を参照して詳細に説明する。なお以下では図中の同一または相当部分には同一符号を付して、その説明は原則的に繰返さないものとする。

[実施の形態1]

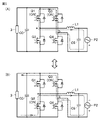

図1は、この発明の実施の形態1に従う電力変換装置1の主回路構成図である。本実施の形態1に従う電力変換装置1は、直流電力および交流電力の間で双方向の電力変換を行なうAC/DCコンバータである。

図1を参照して、本実施の形態1に従う電力変換装置1は、直流端子T1,T2と、交流端子T3,T4と、電力用半導体スイッチング素子(以下、単に「スイッチング素子」とも称する)Q1~Q4と、キャパシタC0,C5と、リアクトルL1と、制御回路5とを備える。

直流端子T1(高電位側直流端子)は直流電源P1の正極端子と電気的に接続され、直流端子T2(低電位側直流端子)は直流電源P1の負極端子と電気的に接続される。直流端子T1には直流正母線PL1が接続され、直流端子T2には直流負母線NL1が接続される。交流端子T3およびT4の間には、交流系統P2が電気的に接続される。本明細書において「電気的に接続」とは、直接的な接続、あるいは、他要素を介した接続によって電気エネルギの伝達が可能な接続状態を示すものとする。

スイッチング素子Q1は、直流正母線PL1(すなわち直流端子T1)およびノードaの間に電気的に接続される。スイッチング素子Q2は、ノードaおよび直流負母線NL1(すなわち直流端子T2)の間に電気的に接続される。ノードaは交流端子T3と電気的に接続される。ノードaは「第1のノード」に対応し、交流端子T3は「第1の交流端子」に対応する。

スイッチング素子Q3は、直流正母線PL1およびノードbの間に電気的に接続される。スイッチング素子Q4は、ノードbおよび直流負母線NL1の間に電気的に接続される。ノードbは交流端子T4と電気的に接続される。ノードbは「第2のノード」に対応し、交流端子T4は「第2の交流端子」に対応する。

なお、図1では、スイッチング素子として、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)を用いているが、IGBT(Insulated Gate Bipolar Transistor)などの任意の自己消弧型のスイッチング素子を用いることができる。スイッチング素子Q1~Q4にはそれぞれ、ダイオードD1~D4が逆並列に接続されている。ダイオードD1~D4の各々は、対応するスイッチング素子のオフ時にフリーホイール電流を流すために設けられている。スイッチング素子がMOSFETである場合、フリーホイールダイオードは寄生のダイオード(ボディダイオード)で構成してもよい。スイッチング素子がダイオードを内蔵しないIGBTである場合、フリーホイールダイオードはIGBTに逆並列に接続されたダイオードで構成される。

スイッチング素子Q1およびQ2は、「第1ハーフブリッジ回路A」を構成する。スイッチング素子Q3およびQ4は、「第2ハーフブリッジ回路B」を構成する。第1ハーフブリッジ回路Aおよび第2ハーフブリッジ回路Bは、直流正母線PL1および直流負母線NL1の間に互いに並列に接続される。すなわち、電力変換装置1はフルブリッジ回路を有する。

キャパシタC0は、直流正母線PL1および直流負母線NL1の間に接続され、直流端子T1およびT2間の電圧(すなわち直流電源P1の出力電圧)を平滑化する。

リアクトルL1は、ノードa(第1のノード)および交流端子T3の間に接続される。キャパシタC5は、交流端子T3およびT4の間に接続される。交流端子T3およびT4間の電圧を平滑化する。リアクトルL1およびキャパシタC5は、フルブリッジ回路から出力される交流電力に含まれるスイッチング周波数の成分を除去するためのフィルタを構成する。

制御回路5は、第1ハーフブリッジ回路Aおよび第2ハーフブリッジ回路の各々におけるスイッチング素子のオンオフを制御する。制御回路5は、スイッチング素子Q1~Q4をそれぞれオンオフするためのゲート信号G1~G4を出力する。スイッチング素子Q1~Q4の各々はH(論理ハイ)レベルのゲート信号Gに応答してオンし、L(論理ロー)レベルのゲート信号Gに応答してオフする。これにより、電力変換装置1は、直流電源P1から供給される直流電力を交流電力に変換して交流端子T3,T4から出力する逆変換動作および、交流系統P2から供給される交流電力を直流電力に変換して直流端子T1,T2から出力する順変換動作を実行することができる。

次に、図2および図3を用いて、電力変換装置1の逆変換動作について説明する。逆変換動作では、電力変換装置1は、直流電源P1の直流電力を交流電力に変換して負荷2に供給する。なお、以下の説明では、直流電源P1の出力電圧(電源電圧)をVdcとし、負荷2(または負荷3)に印加される電圧をVoutとし、リアクトルL1に印加される電圧をVLとする。

最初に、スイッチング素子Q1およびQ4をオンすると、図2(A)に示す回路状態となる。ノードaの電位Va=Vdcになり、ノードbの電位Vb=0になるので、リアクトルL1に電圧VL=Va-Vout-Vb=Vdc-Voutが加わり、図中の矢印で示すように、電流が次第に増加する形で流れる。このときの電圧・電流の向きを正(+)とし、これと逆の場合を負(-)として表す。

次に、スイッチング素子Q1をオフし、スイッチング素子Q2をオンすると、すなわちスイッチング素子Q2およびQ4をオンすると、図2(B)に示す回路状態となる。リアクトルL1を通過している電流は、リアクトルの電流維持作用のため、向きおよび大きさを急変できず、正の方向に流れ続ける。リアクトルL1および負荷2の直列回路は短絡され、電圧Vab=0となるため、リアクトルL1に電圧VL=-Voutが加わり、電流は次第に減少する。

図2(A)の回路状態と図2(B)の回路状態とが交互に繰り返されることにより、負荷2には正の電圧が印加されることとなる。この正の電圧の大きさは、スイッチング素子Q1,Q2をオンオフするスイッチング周期に対するスイッチング素子Q1のオン期間の比に依存し、理想的には0~Vdcの間で変化させることができる。なお、スイッチング素子Q4は、スイッチング素子Q1,Q2のスイッチング周期においてオンに固定されている。

次に、スイッチング素子Q2およびQ3をオンすると、図3(A)に示す回路状態となる。ノードbの電位Vb=Vdcになり、ノードaの電位Va=0なるので、リアクトルL1に電圧VL=Va-Vout-Vb=-Vdc-Voutが加わり、図中の矢印で示すように、負の電流が、絶対値が次第に増加する形で流れる。

次に、スイッチング素子Q1およびQ3をオンすると、図3(B)に示す回路状態となる。リアクトルL1を通過している電流は、電流維持作用のため即時0になれず、負の方向に流れ続ける。リアクトルL1および負荷2の直列回路は短絡され、電圧Vab=0となるため、リアクトルL1に電圧VL=-Voutが加わり、電流の絶対値は次第に減少する。

図3(A)の回路状態と図3(B)の回路状態とが交互に繰り返されることにより、負荷2には負の電圧が印加されることとなる。この負の電圧の大きさは、スイッチング素子Q1,Q2をオンオフするスイッチング周期に対するススイッチング素子Q2のオン期間の比に依存し、理想的には0~-Vdcの間で変化させることができる。なお、スイッチング素子Q3は、スイッチング素子Q1,Q2のスイッチング周期においてオンに固定されている。

電力変換装置1においては、交流端子T3,T4から出力する交流電力の周波数(交流周波数)に同期して、図2のスイッチング動作および図3のスイッチング動作を1/2周期ごとに交互に実行することにより、直流電力が当該周波数の交流電力に変換される。スイッチング素子Q1,Q2のオンオフ制御は、後述するように、パルス幅変調(PWM:Pulse Width Modulation)制御に従って実行される。これに対して、スイッチング素子Q3,Q4のオンオフ制御は、交流周波数で実行される。

次に、図4および図5を用いて、電力変換装置1の順変換動作について説明する。順変換動作では、電力変換装置1は、交流系統P2の交流電力を直流電力に変換して負荷3(直流電源P1を含む)に供給する。以下の説明では、交流系統P2の出力電圧(電源電圧)をV2とする。図4は、交流系統P2の出力電圧が正である場合の回路状態を示し、図5は、交流系統P2の出力電圧が負である場合の回路状態を示す。

図4を参照して、交流系統P2の出力電圧が正であるとき、スイッチング素子Q2およびQ4をオンすると、図4(A)に示す回路状態となる。リアクトルL1および交流系統P2の直列回路は短絡され、図中の矢印で示すように電流が流れる。このときの電流の向きを正(+)とし、これと逆の場合を負(-)として表す。

次に、スイッチング素子Q1をオンし、スイッチング素子Q2をオフすると、すなわちスイッチング素子Q1およびQ4をオンすると、図4(B)に示す回路状態となる。リアクトルL1を通過している電流は、リアクトルの電流維持作用のため、向きおよび大きさを急変できず、正の方向に流れ続ける。ノードaの電位Va=Voutになる。

図4(A)の回路状態と図4(B)の回路状態とが交互に繰り返されることにより、負荷3には正の電圧が印加されることとなる。この正の電圧の大きさは、スイッチング素子Q1,Q2をオンオフするスイッチング周期に対するスイッチング素子Q2のオン期間の比に依存し、理想的にはV2~∞の間で変化させることができる。なお、スイッチング素子Q4は、スイッチング素子Q1,Q2のスイッチング周期においてオンに固定されている。

図5を参照して、交流系統P2の出力電圧が負であるとき、スイッチング素子Q1およびQ3をオンすると、図5(A)に示す回路状態となる。リアクトルL1および交流系統P2の直列回路は短絡され、図中の矢印で示すように、負の方向に電流が流れる。

次に、スイッチング素子Q1をオフし、スイッチング素子Q2をオンすると、すなわちスイッチング素子Q2およびQ3をオンすると、図5(B)に示す回路状態となる。リアクトルL1を通過している電流は、電流維持作用のため即時0になれず、負の方向に流れ続ける。ノードaの電位Va=0になり、ノードbの電位Vb=Voutになる。

図5(A)の回路状態と図5(B)の回路状態とが交互に繰り返されることにより、負荷3には正の電圧が印加されることとなる。この正の電圧の大きさは、スイッチング素子Q1,Q2をオンオフするスイッチング周期に対するスイッチング素子Q1のオン期間の比に依存し、理想的にはV2~∞の間で変化させることができる。なお、スイッチング素子Q3は、スイッチング素子Q1,Q2のスイッチング周期においてオンに固定されている。

電力変換装置1においては、交流端子T3,T4に入力される交流電力の周波数に同期して、図4のスイッチング動作および図5のスイッチング動作を1/2周期ごとに交互に実行することにより、交流電力が直流電力に変換される。スイッチング素子Q1,Q2のオンオフ制御は、後述するように、PWM制御に従って実行される。これに対して、スイッチング素子Q3,Q4のオンオフ制御は、交流周波数で実行される。

図6は、電力変換装置1の逆変換動作時におけるスイッチング素子Q1~Q4のオンオフ制御を説明するための動作波形図である。図6には、スイッチング素子Q1~Q4の各々の動作波形と、ノードab間の電圧Vabの動作波形が示されている。

図6を参照して、電力変換装置1の制御回路5(図1)は、周期的な搬送波CW(三角波またはのこぎり波)の電圧と、正弦波信号V*(変調波)の電圧とを比較し、比較結果に基づいて、スイッチング素子Q1,Q2に対してゲート信号G1,G2をそれぞれ出力する。搬送波CWは、正弦波信号V*の極性に応じて2種類用意される。

具体的には、正弦波信号V*の電位が搬送波CWの電位よりも高いときには、スイッチング素子Q1がオンされ、スイッチング素子Q2がオフされる。一方、正弦波信号V*の電位が搬送波CWの電位よりも低いときには、スイッチング素子Q1がオフされ、スイッチング素子Q2がオンされる。すなわち、スイッチング素子Q1,Q2は、搬送波CWの周波数(以下、キャリア周波数とも称する)でオンオフが制御される。

これに対して、スイッチング素子Q3,Q4は、正弦波信号V*の周波数でオンオフが制御される。具体的には、正弦波信号V*の電圧が正となる期間では、スイッチング素子Q3がオフに固定され、スイッチング素子Q4がオンに固定される。正弦波信号V*の電圧が負となる期間では、スイッチング素子Q3がオンに固定され、スイッチング素子Q4がオフに固定される。

このように、本実施の形態1に係る電力変換装置においては、第1ハーフブリッジ回路A(スイッチング素子Q1,Q2)をキャリア周波数でオンオフさせるとともに、第2ハーフブリッジ回路B(スイッチング素子Q3,Q4)を交流電力の周波数でオンオフさせる。このような駆動方式は、「非対称駆動方式」とも呼ばれる。

ここで、電力変換装置の駆動方式には、非対称駆動方式以外に、第1ハーフブリッジ回路Aおよび第2ハーフブリッジ回路Bの双方をキャリア周波数でオンオフさせる方式がある。このような駆動方式は「対称駆動方式」とも呼ばれる。図7および図8を用いて、対称駆動方式での逆変換動作について説明する。

最初に、スイッチング素子Q1およびQ4をオンすると、図7(A)に示す回路状態となる。ノードaの電位Va=Vdcになり、ノードbの電位Vb=0になるので、リアクトルL1に電圧VL=Va-Vout-Vb=Vdc-Voutが加わり、図中の矢印で示すように、正の電流が次第に増加する形で流れる。

次に、スイッチング素子Q1をオフし、スイッチング素子Q2をオンすると、すなわちスイッチング素子Q2およびQ4をオンすると、図7(B)に示す回路状態となる。リアクトルL1を通過している電流は、リアクトルの電流維持作用のため即時0になれず、正の方向に流れ続ける。リアクトルL1および負荷2の直列回路は短絡され、電圧Vab=0となるため、リアクトルL1に電圧VL=-Voutが加わり、電流は次第に減少する。

次に、スイッチング素子Q1をオンし、スイッチング素子Q2をオフすると、すなわちスイッチング素子Q1およびQ4をオンすると、図7(C)に示す回路状態である。ノードaの電位Va=Vdcになり、ノードbの電位Vb=0になるので、リアクトルL1に電圧VL=Va-Vout-Vb=Vdc-Voutが加わり、図中の矢印で示すように、正の電流が次第に増加する形で流れる。

次に、スイッチング素子Q3をオンし、スイッチング素子Q4をオフすると、すなわちスイッチング素子Q1およびQ3をオンすると、図7(D)に示す回路状態となる。リアクトルL1を通過している電流は、リアクトルの電流維持作用のため即時0になれず、正の方向に流れ続ける。リアクトルL1および負荷2の直列回路は短絡され、電圧Vab=0となるため、リアクトルL1に電圧VL=-Voutが加わり、電流は次第に減少する。

図7(A)~(D)の回路状態が繰り返されることにより、負荷2には正の電圧が印加されることとなる。スイッチング素子Q1,Q2をオンオフするスイッチング周期およびスイッチング素子Q3,Q4をオンオフするスイッチング周期は互いに等しい。

次に、スイッチング素子Q2およびQ3をオンすると、図8(A)に示す回路状態となる。ノードbの電位Vb=Vdcになり、ノードaの電位Va=0なるので、リアクトルL1に電圧VL=Va-Vout-Vb=-Vdc-Voutが加わり、図中の矢印で示すように、負の電流が、絶対値が次第に増加する形で流れる。

次に、スイッチング素子Q3をオフし、スイッチング素子Q4をオンすると、すなわちスイッチング素子Q2およびQ4をオンすると、図8(B)に示す回路状態となる。リアクトルL1を通過している電流は、電流維持作用のため即時0になれず、負の方向に流れ続ける。リアクトルL1および負荷2の直列回路は短絡され、電圧Vab=0となるため、リアクトルL1に電圧VL=-Voutが加わり、電流の絶対値は次第に減少する。

次に、スイッチング素子Q3をオンし、スイッチング素子Q4をオフすると、すなわちスイッチング素子Q2およびQ3をオンすると、図8(C)に示す回路状態となる。ノードbの電位Vb=Vdcになり、ノードaの電位Va=0なるので、リアクトルL1に電圧VL=Va-Vout-Vb=-Vdc-Voutが加わり、図中の矢印で示すように、負の電流が、絶対値が次第に増加する形で流れる。

次に、スイッチング素子Q1をオンし、スイッチング素子Q2をオフすると、すなわちスイッチング素子Q1およびQ3をオンすると、図8(D)に示す回路状態となる。リアクトルL1を通過している電流は、電流維持作用のため即時0になれず、負の方向に流れ続ける。リアクトルL1および負荷2の直列回路は短絡され、電圧Vab=0となるため、リアクトルL1に電圧VL=-Voutが加わり、電流の絶対値は次第に減少する。

図8(A)~(D)の回路状態が繰り返されることにおり、負荷2には負の電圧が印加されることとなる。スイッチング素子Q1,Q2をオンオフするスイッチング周期およびスイッチング素子Q3,Q4をオンオフするスイッチング周期は互いに等しい。

図9は、対称駆動方式におけるスイッチング素子Q1~Q4のオンオフ制御を説明するための動作波形図である。図9には、スイッチング素子Q1~Q4の各々の動作波形と、ノードab間の電圧Vabの動作波形が示されている。

図9を参照して、搬送波CWの電圧と、正弦波信号V*(変調波)の電圧とを比較し、比較結果に基づいて、スイッチング素子Q1,Q2に対してゲート信号G1,G2がそれぞれ出力される。また、搬送波CWの電圧と正弦波信号V*を反転した信号/V*の電圧とを比較し、比較結果に基づいて、スイッチング素子Q3,Q4に対してゲート信号G3,G4がそれぞれ出力される。

具体的には、正弦波信号V*の電位が搬送波CWの電位よりも高いときには、スイッチング素子Q1がオンされ、スイッチング素子Q2がオフされる。一方、正弦波信号V*の電位が搬送波CWの電位よりも低いときには、スイッチング素子Q1がオフされ、スイッチング素子Q2がオンされる。すなわち、スイッチング素子Q1,Q2は、キャリア周波数でオンオフが制御される。

反転信号/V*の電位が搬送波CWの電位よりも高いときには、スイッチング素子Q3がオンされ、スイッチング素子Q4がオフされる。一方、反転信号/V*の電位が搬送波CWの電位よりも低いときには、スイッチング素子Q3がオフされ、スイッチング素子Q4がオンされる。すなわち、スイッチング素子Q3,Q4は、キャリア周波数でオンオフが制御される。

図6の動作波形図と図9の動作波形図とを比較すると、非対称駆動方式では、2つのハーフブリッジ回路の一方(図6では第2ハーフブリッジ回路B)がキャリア周波数よりも低い交流周波数でオンオフするため、2つのハーフブリッジ回路がともにキャリア周波数でオンオフする対称駆動方式に比べて、一方のハーフブリッジ回路のスイッチング回数を減らすことができる。スイッチング回数の減少は、該ハーフブリッジ回路で生じるスイッチング損失の低減に繋がるため、最適な素子を使用することで、電力変換装置全体の電力変換効率の向上が期待できる。

非対称駆動方式では、さらに、ハーフブリッジ回路のスイッチング周波数に応じて、ハーフブリッジ回路を構成するスイッチング素子を使い分けることができる。

例えば、スイッチング周波数がキャリア周波数であるハーフブリッジ回路(第1ハーフブリッジ回路A)については、高周波動作が可能なワイドバンドギャップ半導体材料(例えば、SiC(炭化珪素)、GaN(窒化ガリウム)など)を用いて形成されたスイッチング素子(例えばSiC-MOSFET、GaN-HEMTなど)を使用することができる。

電力変換動作においては、スイッチング素子のチャネルだけでなく、フリーホイールダイオードを通しても電流を流すモードが存在する。フリーホイールダイオードに電流を流したり、遮断したりする場合、逆回復現象により、瞬間的にダイオードの逆方向に電流が流れる。この逆方向に電流が流れる時間が長くなるほど、該時間に発生する損失が大きくなる。したがって、スイッチング周波数がキャリア周波数であるスイッチング素子は、逆回復時間が早いフリーホイールダイオード(ボディダイオードを含む)を有することが望ましい。好ましくは、逆回復時間は200ns以下である。例えば、IGBTに対して、SiCショットキーバリアダイオードまたはFRD(First Recovery Diode)を逆並列に接続することができる。あるいは、高速ボディダイオードタイプのMOSFETを使用することができる。

これに対して、スイッチング周波数が交流電力の周波数であるハーフブリッジ回路(第2ハーフブリッジ回路B)については、プレーナタイプのSiMOSFETに比べて、高耐圧を確保しながら導通損失を低減することができる、Siスーパージャンクション(Super Junction)MOSFETを使用することができる。

さらに、非対称駆動方式を採用することで、交流電力の周波数でスイッチングするハーフブリッジ回路(第2ハーフブリッジ回路B)のスイッチング損失を低減できるため、キャリア周波数でスイッチングするハーフブリッジ回路(第1ハーフブリッジ回路A)にのみ補助共振回路を設けることで、スイッチング素子のソフトスイッチングを実現することができる。これにより、簡易な構成でソフトスイッチングを実行できるため、電力変換装置の高効率化および低ノイズ化を実現することができる。

[実施の形態2]

以下の実施の形態2~5では、実施の形態1で説明した非対称駆動方式の電力変換装置1において、ソフトスイッチングを実現するための構成について説明する。

図10は、この発明の実施の形態2に従う電力変換装置1の主回路構成図である。図10を参照して、実施の形態2に従う電力変換装置1の回路構成は、図1に示した電力変換装置1の回路構成と基本的に同様であり、補助共振回路4および補助キャパシタCr1,Cr2を備える点が異なる。

補助キャパシタCr1は、スイッチング素子Q1に並列に接続される。補助キャパシタCr2は、スイッチング素子Q2に並列に接続される。補助キャパシタCr1,Cr2としては、外付けのキャパシタを用いてもよいし、回路構成上等価な位置にあるスイッチング素子の寄生容量を用いてもよい。

補助共振回路4は、キャパシタCp,Cnと、補助スイッチング素子Qr1,Qr2と、補助リアクトルLrとを含む。キャパシタCpおよびCnは、同容量であり、直流端子T1(直流正母線PL1)および直流端子T2(直流負母線NL1)の間に直列に接続される。キャパシタCp,Cnは、直流電源P1の電圧V1を2分割するためのキャパシタである。キャパシタCp,Cnには、一般的に、電圧の変動を安定させるべく、容量が大きい電解キャパシタが用いられる。

補助スイッチング素子Qr1およびQr2は、キャパシタCpおよびCnの接続点(ノードn)とノードaとの間に電気的に直列に接続される。補助スイッチング素子Qr1,Qr2のオンオフは、制御回路5から出力されるゲート信号Gr1,Gr2によってそれぞれ制御される。なお、図10では、補助スイッチング素子Qr1,Qr2として、MOSFETを用いているが、IGBTなどの任意の自己消弧型のスイッチング素子を用いることができる。補助スイッチング素子Qr1,Qr2にはそれぞれ、補助ダイオードDr1,Dr2が逆並列に接続されている。補助スイッチング素子Qr1,Qr2および補助ダイオードDr1,Dr2は「双方向スイッチ」の一実施例に対応する。

補助リアクトルLrは、補助スイッチング素子Qr1およびQr2の直列回路とノードaとの間に電気的に接続される。

次に、図11から図13を用いて、実施の形態2に従う電力変換装置1の動作、特に補助共振回路4によるソフトスイッチングを説明する。ここでは、負荷2に正の電圧を印加するとき(図2参照)のソフトスイッチングについて説明する。

以下の説明では、図10の補助スイッチング素子Qr1およびQr2の直列回路を補助スイッチSrで置き換えることとする。直流電源P1の出力電圧(電源電圧)をVdcとする。Ioは負荷2に流れる電流を示し、IL1はリアクトルL1に流れる電流を示し、ILrは補助リアクトルLrに流れるリアクトル電流を示す。

図11および図12は、スイッチング素子Q2のダイオードD2に電流IL1が流れている状態(モードM0)からスイッチング素子Q1へ転流するときの状態を示している。図12は、図11に示す動作が実行された場合の動作波形図である。

図11を参照して、スイッチング素子Q2およびQ4がオンの状態においては(モードM0)、リアクトルL1および負荷2の直列回路が短絡され、図中の矢印で示すように、正の電流IL1が次第に減少する形で流れる。

この状態で補助スイッチSr(補助スイッチング素子Qr1)のをターンオンすると(モードM1)、補助リアクトルLrに、正の電流ILrが流れ始める。転流期間中の電流ILrを一定とすれば、図13に示すように、リアクトル電流ILrはVdc/2Lrの傾きで直線的に増加し始める。

リアクトル電流ILrが電流IL1よりも大きくなると、その超過分の電流は補助リアクトルLrからスイッチング素子Q2に流れ込み、キャパシタCp,Cnおよび補助スイッチSrを介して補助リアクトルLrに帰還する(モードM2)。

スイッチング素子Q2のドレイン電流Idが正になったときに、スイッチング素子Q2をターンオフすると(モードM3)、補助リアクトルLrと補助キャパシタCr1,Cr2とが共振動作になるため、リアクトル電流ILrはピーク値を向かえた後0に向かって減少する。このとき、リアクトル電流ILrは補助キャパシタCr1に流れ込むとともに、補助キャパシタCr2に流れ込む。この電流によって補助キャパシタCr2が充電され、かつ、補助キャパシタCr1が放電されることによって、スイッチング素子Q1およびQ2の接続点(ノードa)の電位が上昇する。このため、図13に示すように、スイッチング素子Q1のドレイン・ソース間電圧Vdsは次第に減少する。

ノードaの電位Va=Vdcに達すると、スイッチング素子Q1のダイオードD1がオンする。このダイオードD1がオンしている期間にスイッチング素子Q1をターンオンさせれば、ゼロ電圧スイッチングが行なわれることになる(モードM4)。

スイッチング素子Q1をターンオンすることにより、電流が直流電源P1の正極端子からスイッチング素子Q1に流れ込み、リアクトルL1、負荷2およびスイッチング素子Q4を介して直流電源P1の負極端子に帰還する(モードM5)。スイッチング素子Q1のドレイン・ソース間に流れるドレイン電流Idが次第に増加し、それに伴ってリアクトル電流ILrが減少する。リアクトル電流ILr=0となった後に、補助スイッチSr(補助スイッチング素子Qr1)をオフする(モードM6)。補助スイッチング素子Qr2の補助ダイオードDr2により負の電流は流れない。

図14に、スイッチング素子Q1のドレイン・ソース間電圧Vdsおよびドレイン電流Idの動作波形の周波数スペクトルを示す。図14(A)には、実施の形態1に従う電力変換装置1(補助共振回路無し)のスイッチング素子Q1のVds波形の周波数スペクトル(波形k1)および、実施の形態2に従う電力変換装置1(補助共振回路有り)のスイッチング素子Q1のVds波形の周波数スペクトル(波形k2)が示されている。

図14(B)には、実施の形態1に従う電力変換装置1のスイッチング素子Q1のId波形の周波数スペクトル(波形k3)および、実施の形態2に従う電力変換装置1のスイッチング素子Q1のId波形の周波数スペクトル(波形k4)が示されている。

図14(A)に示されるように、補助共振回路4を利用してスイッチング素子Q1をソフトスイッチングしたことにより、スイッチング素子Q1をハードスイッチングした場合に比べて、Vdsの高周波領域での強度が小さくなっている。図14(B)においても、スイッチング素子Q1をソフトスイッチングしたことにより、スイッチング素子Q1をハードスイッチングした場合に比べて、Idの高周波領域での強度が小さくなっている。このように、第1ハーフブリッジ回路Aのスイッチング素子をソフトスイッチングすることで、電磁干渉(EMI)ノイズを低減することができる。

以上説明したように、実施の形態2に従う電力変換装置によれば、フルブリッジ回路において、キャリア周波数でスイッチングするハーフブリッジ回路にのみ補助共振回路を設けることによって、簡易な構成でスイッチング損失の低減およびEMIノイズの低減を実現することができる。

[実施の形態3]

上述した実施の形態2に従う電力変換装置1においては、補助共振回路4には、直流電源P1の電圧Vdcを2分割して中点電位(Vdc/2)を生成するためにキャパシタCp,Crの直列回路を用いている。そのため、負荷の大きさなどによって中点電位が変動する場合がある。また、キャパシタCp,Crに電解キャパシタを用いた場合、電解キャパシタは温度上昇によって容量が低下する電気部品であるため、キャパシタCp,Cnの劣化が進行することで、電力変換装置全体の寿命が短くなることが懸念される。

以下、実施の形態3~5では、キャパシタCp,Crの直列回路を用いずにスイッチング素子Q1,Q2のソフトスイッチングを実現するための補助共振回路の新たな構成について説明する。

図15は、この発明の実施の形態3に従う電力変換装置1の主回路構成図である。図15を参照して、実施の形態3に従う電力変換装置1は、補助共振回路4Aの構成が図10に示した実施の形態2に従う電力変換装置1の補助共振回路4の構成と異なる。その他の点については、実施の形態2と共通するので、同一または相当する部分には同一の参照符号を付して説明は繰返さない。

補助共振回路4Aは、補助スイッチング素子Qr1,Qr2および補助リアクトルLrを含む。補助スイッチング素子Qr1およびQr2は、直流端子T1(直流正母線PL1)および直流端子T2(直流負母線NL1)の間に電気的に直列に接続される。補助リアクトルLrは、補助スイッチング素子Qr1およびQr2の接続点(ノードc)とノードaとの間に電気的に接続される。

次に、図16から図19を用いて、実施の形態3に従う電力変換装置1の動作、特に補助共振回路4Aによるソフトスイッチングを説明する。図16および図17では、負荷2に正の電圧を印加するときのソフトスイッチングについて説明する。

図16は、スイッチング素子Q2のダイオードD2に電流IL1が流れている状態(モードM0)からスイッチング素子Q1へ転流するときの状態を示している。図17は、図16に示す動作が実行された場合の動作波形図である。

図16を参照して、スイッチング素子Q2およびQ4がオンの状態においては(モードM0)、リアクトルL1および負荷2の直列回路が短絡され、図中の矢印で示すように、正の電流IL1が次第に減少する形で流れる。

この状態で補助スイッチング素子Qr1をターンオンすると(モードM1)、補助リアクトルLrに、正のリアクトル電流ILrが流れ始める。リアクトル電流ILrは、直流電源P1の正極端子から補助スイッチSr1、補助リアクトルLr、リアクトルL1、負荷2、スイッチング素子Q4を介して直流電源P1の負極端子に帰還される。転流期間中の電流IL1を一定とすれば、図17に示すように、リアクトル電流ILrはVdc/Lrの傾きで直線的に増加し始める。

リアクトル電流ILrが電流IL1よりも大きくなると、その超過分は補助リアクトルLrからスイッチング素子Q2に流れ込む。スイッチング素子Q2のドレイン電流Idが正になったときに、スイッチング素子Q2をターンオフすると(モードM2)、補助リアクトルLrと補助キャパシタCr1,Cr2とが共振動作になる。このとき、リアクトル電流ILrは補助キャパシタCr1に流れ込むとともに、補助キャパシタCr2に流れ込む。この電流によって補助キャパシタCr2が充電され、かつ、補助キャパシタCr1が放電されることによって、スイッチング素子Q1およびQ2の接続点(ノードa)の電位が上昇する。このため、図17に示すように、スイッチング素子Q1のドレイン・ソース間電圧Vdsは次第に減少する。

ノードaの電位Va=Vdcに達すると、スイッチング素子Q1のダイオードD1がオンする。このダイオードD1がオンしている期間にスイッチング素子Q1をターンオンさせれば、ゼロ電圧スイッチングが行なわれることになる(モードM3)。スイッチング素子Q1のターンオンと同じタイミングで、補助スイッチング素子Qr1をターンオフする。

スイッチング素子Q1をターンオンすると(モードM3)、補助リアクトルLrの電流維持作用により、リアクトル電流ILrは、補助リアクトルLrからスイッチング素子Q1のダイオードD1、直流電源P1の正極端子、補助スイッチング素子Qr2の順に流れるとともに、補助リアクトルLrからリアクトルL1、負荷2、スイッチS4、補助スイッチング素子Qr2の補助ダイオードDr2の順に流れることとなる。図17に示すように、リアクトル電流ILrは直線的に減少し始める。

リアクトル電流ILrが減少し始めると、電流IL1を一定とするために、直流電源P1の正極端子からリアクトルL1に電流が流れ込み、負荷2、スイッチング素子Q4を介して直流電源P1の負極端子に帰還する(モードM4)。スイッチング素子Q1のドレイン・ソース間に流れるドレイン電流Idが次第に増加する。この状態でリアクトル電流ILr=0になると(モードM5)、ドレイン電流Idが一定となる。

次に、図18および図19を用いて、負荷2に負の電圧を印加するときのソフトスイッチングについて説明する。

図18は、スイッチング素子Q1のダイオードD1に電流IL1が流れている状態(モードM0)からスイッチング素子Q2へ転流するときの状態を示している。図19は、図18に示す動作が実行された場合の動作波形図である。

図18を参照して、スイッチング素子Q1およびQ3がオンの状態においては(モードM0)、リアクトルL1および負荷2の直列回路が短絡され、図中の矢印で示すように、負の電流IL1の絶対値が次第に減少する形で流れる。

この状態で補助スイッチング素子Qr2をターンオンすると(モードM1)、補助リアクトルLrに、負のリアクトル電流ILrが流れ始める。リアクトル電流ILrは、直流電源P1の正極端子からスイッチング素子Q3、負荷2、リアクトルL1、補助リアクトルLr、補助スイッチング素子Qr2を介して直流電源P1の負極端子に帰還される。転流期間中の電流IL1を一定とすれば、図19に示すように、リアクトル電流ILrは直線的に減少し始める。

この状態でスイッチング素子Q1をターンオフすると(モードM2)、補助リアクトルLrと補助キャパシタCr1,Cr2とが共振動作になる。このとき、リアクトル電流ILrは補助キャパシタCr1に流れ込むとともに、補助キャパシタCr2に流れ込む。この電流によって補助キャパシタCr2が放電され、かつ、補助キャパシタCr1が充電されることによって、スイッチング素子Q1およびQ2の接続点(ノードa)の電位が低下する。このため、図19に示すように、スイッチング素子Q2のドレイン・ソース間電圧Vdsは次第に減少する。

ノードaの電位Va=0に達すると、スイッチング素子Q2のダイオードD2がオンする。このダイオードD2がオンしている期間にスイッチS2のスイッチング素子Q2をターンオンさせれば、ゼロ電圧スイッチングが行なわれることになる(モードM3)。スイッチング素子Q2のターンオンと同じタイミングで、補助スイッチング素子Qr2をターンオフする。

補助スイッチング素子Qr2がターンオフすると(モードM3)、補助リアクトルLrの電流維持作用により、リアクトル電流ILrは、補助リアクトルLrから補助スイッチング素子Qr1のダイオードDr1を介して直流電源P1の正極端子、負極端子、スイッチング素子Q2のダイオードD2の順に流れるとともに、補助リアクトルLrからスイッチング素子Q3、負荷2、リアクトルL1の順に流れることとなる。図19に示すように、リアクトル電流ILrは直線的に増加し始める。

リアクトル電流ILrが増加し始めると、電流IL1を一定とするために、直流電源P1の正極端子からスイッチング素子Q3および負荷2を介してリアクトルL1に電流が流れ込み、スイッチング素子Q2を介して直流電源P1の負極端子に帰還する(モードM4)。スイッチング素子Q3のドレイン・ソース間に流れるドレイン電流Idが次第に増加する。この状態でリアクトル電流ILrが0になると(モードM5)、ドレイン電流Idが一定となる。

以上説明したように、この発明の実施の形態3に従う電力変換装置1によれば、補助共振回路にキャパシタCp,Crの直列回路が含まれていないため、直列回路の中点電位の変動を抑制することができる。また、キャパシタCp,Crの劣化に起因した電力変換装置の寿命の低下を防ぐことができる。

[実施の形態4]

上述した実施の形態3に従う補助共振回路4Aにおいては、補助リアクトルLrと補助キャパシタCr1,Cr2との共振動作により、補助スイッチング素子Qr1に電流が流れている状態(図16のモードM2)において、補助スイッチング素子Qr1をターンオフさせている(モードM3)。そのため、半導体スイッチング素子Q1をソフトスイッチングできる一方で、補助スイッチング素子Qr1がハードスイッチングになることが懸念される。

補助スイッチング素子Qr1,Qr2をソフトスイッチングするためには、実施の形態2で示したように、直流電源P1の電圧Vdcを2分割した電圧を作ることが必要になるが、上記の理由からキャパシタCp,Cnの直列回路を用いることは得策ではない。

以下の実施の形態4および5では、キャパシタCp,Cnの直列回路を用いずに、直流電源P1の電圧Vdcを2分割した電圧を生成することができる補助共振回路の構成について説明する。

図20は、この発明の実施の形態4に従う電力変換装置1の主回路構成図である。図20を参照して、実施の形態4に従う電力変換装置1は、補助共振回路4Bの構成が図10に示した実施の形態2に従う電力変換装置1の補助共振回路4の構成と異なる。その他の点については、実施の形態2と共通するので、同一または相当する部分には同一の参照符号を付して説明は繰返さない。

補助共振回路4Bは、補助スイッチング素子Qr1,Qr2、補助リアクトルLr、およびトランスTr1を含む。トランスTr1は、一次巻線n1および二次巻線n2を含む。トランスTr1は、理想トランスに加えて、励磁インダクタンスLmおよび漏れインダクタンスを有している。一次巻線n1と二次巻線n2とが電磁的に結合されることにより、一次巻線n1および二次巻線n2に同極性の起電力が誘起される。一次巻線n1と二次巻線n2との巻線比は2:1である。トランスTr1は「第1のトランス」の一実施例に対応する。

トランスTr1の一次巻線n1は、直流端子T1(直流正母線PL1)および直流端子T2(直流負母線NL1)の間に電気的に接続される。トランスTr1の二次巻線n2は、第1ハーフブリッジ回路Aのノードaおよび直流負母線NL1の間に電気的に接続される。

補助スイッチング素子Qr1は、トランスTr1の一次巻線n1および直流負母線NL1の間に電気的に接続される。補助スイッチング素子Qr2は、トランスTr1の二次巻線n2および直流負母線NL1の間に電気的に接続される。補助スイッチング素子Qr1,Qr2にはそれぞれ、補助ダイオードDr1,Dr2が逆並列に接続されている。

補助リアクトルLrは、二次巻線n2およびノードaの間に接続される。補助リアクトルLrは、トランスTr1の漏れインダクタンスを利用してもよく、外付けしてもよい。

次に、図21から図26を用いて、実施の形態4に従う電力変換装置1の動作、特に補助共振回路4Bによるソフトスイッチングを説明する。図21から図23では、負荷2に正の電圧を印加するときのソフトスイッチングについて説明する。

図21および図22は、スイッチング素子Q2のダイオードD2に電流IL1が流れている状態(モードM0)からスイッチング素子Q1へ転流するときの状態を示している。図23は、図21および図22に示す動作が実行された場合の動作波形図である。

図21を参照して、スイッチング素子Q2およびQ4がオンの状態においては(モードM0)、リアクトルL1および負荷2の直列回路が短絡され、図中の矢印で示すように、正の電流IL1が次第に減少する形で流れる。

この状態で補助スイッチング素子Qr1をターンオンすると(モードM1)、トランスTr1の一次巻線n1には直流電源P1の電圧Vdcが印加され、一次巻線n1と二次巻線n2との巻線比が2:1であるので、二次巻線n2および補助リアクトルLrの接続点には電圧Vdcの1/2の電圧が印加される。これにより、補助リアクトルLrに、正のリアクトル電流ILrが流れ始める。リアクトル電流ILrは、トランスTr1の二次巻線n2から補助リアクトルLr、スイッチング素子Q4、補助スイッチング素子Qr2の補助ダイオードDr2を介して二次巻線n2に帰還される。転流期間中の電流IL1を一定とすれば、図23に示すように、リアクトル電流ILrはVdc/2Lrの傾きで直線的に増加し始める。また、スイッチング素子Q2のドレイン電流Idは0に向かって直線的に増加し始める。

リアクトル電流ILrが電流IL1よりも大きくなると、その超過分の電流は補助リアクトルLrからスイッチング素子Q2に流れ込む(モードM2)。

スイッチング素子Q2のドレイン電流Idが正になったときに、スイッチング素子Q2をターンオフすると(モードM3)、補助リアクトルLrと補助キャパシタCr1,Cr2とが共振動作になる。このとき、リアクトル電流ILrは、補助キャパシタCr2に流れ込むとともに、補助キャパシタCr1に流れ込む。この電流によって補助キャパシタCr2が充電され、かつ、補助キャパシタCr1が放電されることによって、スイッチング素子Q1およびQ2の接続点(ノードa)の電位が上昇する。このため、図23に示すように、スイッチング素子Q1のドレイン・ソース間電圧Vdsは次第に減少する。

ノードaの電位Va=Vdcに達すると、スイッチング素子Q1のダイオードD1がオンする。このダイオードD1がオンしている期間にスイッチング素子Q1をターンオンさせれば、ゼロ電圧スイッチングが行なわれることになる(モードM4)。

スイッチング素子Q1をターンオンすると(モードM5)、電流が直流電源P1の正極端子からスイッチング素子Q1に流れ込み、リアクトルL1、負荷2、スイッチング素子Q4を介して直流電源P1の負極端子に帰還する。スイッチング素子Q1のドレイン・ソース間に流れるドレイン電流Idが次第に増加する。リアクトル電流ILr=0となったときに、補助スイッチング素子Qr1をターンオフすることにより(モードM6)、補助スイッチング素子Qr1のゼロ電流スイッチングが行なわれる。

次に、図24および図26を用いて、負荷2に負の電圧を印加するときのソフトスイッチングについて説明する。

図24および図25は、スイッチング素子Q1のダイオードD1に電流IL1が流れている状態(モードM0)からスイッチング素子Q2へ転流するときの状態を示している。図26は、図24および図25に示す動作が実行された場合の動作波形図である。

図24を参照して、スイッチング素子Q1およびQ3がオンの状態においては(モードM0)、リアクトルL1および負荷2の直列回路が短絡され、図中の矢印で示すように、負の電流IL1の絶対値が次第に減少する形で流れる。

この状態で補助スイッチング素子Qr2をターンオンすると(モードM1)、補助リアクトルLrに、負のリアクトル電流ILrが流れ始める。リアクトル電流ILrは、直流電源P1の正極端子からスイッチング素子Q3、負荷2、リアクトルL1、補助リアクトルLr、補助スイッチング素子Qr2を介して直流電源P1の負極端子に帰還される。このとき、補助ダイオードDr1、一次巻線n1、直流電源P1、補助ダイオードDr1の経路で電流が流れる。一次巻線n1には電圧Vdcが印加され、一次巻線nと二次巻線n2との巻線比が2:1であるので、二次巻線n2および補助リアクトルLrの接続点には電圧Vdcの1/2の電圧が印加される。転流期間中の電流IL1を一定とすれば、図26に示すように、リアクトル電流ILrは-Vdc/2Lrの傾きで直線的に減少し始める。また、スイッチング素子Q1のドレイン電流Idは0に向かって直線的に増加し始める。

リアクトル電流ILrが電流IL1よりも小さくなると、その超過分の電流はスイッチング素子Q3に流れ込む(モードM2)。

スイッチング素子Q1のドレイン電流Idが正になったときに、スイッチング素子Q1をターンオフすると(モードM3)、補助リアクトルLrと補助キャパシタCr1,Cr2とが共振動作になる。このとき、リアクトル電流ILrは、補助キャパシタCr2に流れ込むとともに、補助キャパシタCr1に流れ込む。この電流によって補助キャパシタCr1が充電され、かつ、補助キャパシタCr2が放電されることによって、スイッチング素子Q1およびQ2の接続点(ノードa)の電位が低下する。このため、図26に示すように、スイッチング素子Q2のドレイン・ソース間電圧Vdsは次第に減少する。

ノードaの電位Va=0に達すると、スイッチング素子Q2のダイオードD2がオンする。このダイオードD2がオンしている期間にスイッチング素子Q2をターンオンさせれば、ゼロ電圧スイッチングが行なわれることになる(モードM4)。

スイッチング素子Q2をターンオンすると、電流が直流電源P1の正極端子からスイッチング素子Q3に流れ込み、負荷2、リアクトルL1、スイッチング素子Q2を介して直流電源P1の負極端子に帰還する(モードM5)。スイッチング素子Q2のドレイン・ソース間に流れるドレイン電流Idが次第に増加する。リアクトル電流ILr=0となったときに、補助スイッチング素子Qr2をターンオフすることにより(モードM6)、補助スイッチング素子Qr1のゼロ電流スイッチングが行なわれる。

以上説明したように、この発明の実施の形態4に従う電力変換装置1によれば、キャパシタCp,Cnの直列回路を用いずに、直流電源P1の電圧Vdcを2分割した電圧を生成することができるため、補助スイッチング素子Qr1,Qr2をソフトスイッチングすることができる。

また、本実施の形態4に従う電力変換装置1において、補助スイッチング素子Qr1およびQr2はともに、直流電源P1の負極端子(直流負母線NL1)に接続されているため、補助スイッチング素子Qr1のゲート信号Gr1と、補助スイッチング素子Qr2のゲート信号Gr2とを同電位の信号とすることができる。図15に示した実施の形態3に従う電力変換装置1においては、補助スイッチング素子Qr1およびQr2が直流正母線PL1および直流負母線NL1の間に直列に接続されるため、高電位側の補助スイッチング素子Qr1のゲート信号Gr1の電位を、低電位側の補助スイッチング素子Qr1のゲート信号Gr2の電位よりも高くする必要がある。そのため、補助スイッチング素子Qr1のゲート駆動回路は、ゲート信号Gr1の電位を上げるためのレベルシフタが内蔵されており、補助スイッチング素子Qr2のゲート駆動回路とは電気的に分離されている。

これに対して、本実施の形態4においては、補助スイッチング素子Qr1およびQr2が同電位にあるため、互いのゲート駆動回路を電気的に分離することが不要となる。したがって、ゲート駆動回路を簡素化でき、結果的に電力変換装置1を小型化および低コスト化することができる。

[変形例]

図27は、本実施の形態4の変形例に従う電力変換装置1の主回路構成図である。図27を参照して、実施の形態4の変形例に従う電力変換装置1は、補助共振回路4Cの構成が図20に示した実施の形態4に従う電力変換装置1の補助共振回路4Bの構成と異なる。その他の点については、実施の形態2と共通するので、同一または相当する部分には同一の参照符号を付して説明は繰返さない。

本変形例に従う電力変換装置1においては、図20に示した電力変換装置1のトランスTr1がトランスTr2に置き換えられるとともに、ダイオードDa2が追加されている。

トランスTr2は、一次巻線n1、二次巻線n2およびリセット巻線n3を含む。リセット巻線n3は、一方端が直流正母線PLに接続され、他方端がダイオードDa2のカソードに接続されている。ダイオードDa2のアノードは直流負母線NL1に接続されている。すなわち、ダイオードDa2およびリセット巻線n3の直列回路は、直流負母線NL1から直流正母線PL1に向かう方向がダイオードDa2の順方向となるように、直流正母線PL1および直流負母線NL1の間に電気的に接続されている。

リセット巻線n3およびダイオードDa2は、トランスTr2の励磁インダクタンスLmに蓄積された電磁エネルギを放出するためのリセット回路を構成する。

具体的には、補助スイッチング素子Qr1,Qr2がオフしたときには、トランスTr2の励磁インダクタンスLmによる逆起電力が発生する。この逆起電力によって一次巻線n1および二次巻線n2に発生した電圧(サージ電圧)が補助スイッチング素子Qr1,Qr2に印加されることで、補助スイッチング素子Qr1,Qr2は損傷する虞がある。

リセット巻線n3およびダイオードDa2の直列回路は、この逆起電力を直流電源P1に回生することができる。これにより、補助スイッチング素子Qr1,Qr2に過電圧が印加されることを回避できるため、補助スイッチング素子Qr1,Qr2の損傷を防ぐことができる。

[実施の形態5]

図28は、この発明の実施の形態5に従う電力変換装置1の主回路構成図である。図28を参照して、本実施の形態5に従う電力変換装置1は、補助共振回路4Dの構成が図15に示した実施の形態3に従う電力変換装置1の補助共振回路4Aの構成と異なる。その他の点については、実施の形態2と共通するので、同一または相当する部分には同一の参照符号を付して説明は繰返さない。

補助共振回路4Dは、補助スイッチング素子Qr1,Qr2、補助リアクトルLr、トランスTr3、およびダイオードDb1,Db2,Dc1,Dc2,Dr3,Dr4を含む。

補助スイッチング素子Qr1およびQr2は、直流端子T1(直流正母線PL1)および直流端子T2(直流負母線NL1)の間に電気的に直列に接続される。補助リアクトルLrは、補助スイッチング素子Qr1およびQr2の接続点(ノードc)とノードaとの間に電気的に接続される。

ダイオードDr3は、直流正母線PL1およびノードcの間に、補助スイッチング素子Qr1と電気的に直列に接続される。ダイオードDr4は、直流負母線NL1およびノードcの間に、補助スイッチング素子Qr2と電気的に直列に接続される。図27の構成例では、ダイオードDr3のアノードが補助スイッチング素子Qr1に接続され、カソードがノードcに接続されている。ダイオードDr3は、直流負母線PL1および補助スイッチング素子Qr1の間に接続されていてもよい。図28の構成例では、また、ダイオードDr4のアノードがノードcに接続され、カソードが補助スイッチング素子Qr2に接続されている。ダイオードDr4は、補助スイッチング素子Qr2および直流負母線NL1の間に接続されていてもよい。ダイオードDr3は「第5のダイオード」の一実施例に対応し、ダイオードDr4は「第6のダイオード」の一実施例に対応する。

ダイオードDb1およびDb2は、直流端子T1(直流正母線PL1)および直流端子T2(直流負母線NL1)の間に電気的に直列に接続される。ダイオードDb2のアノードは直流負母線NL1と電気的に接続され、ダイオードDb1のカソードは直流正母線PL1と電気的に接続される。ダイオードDb1は「第1のダイオード」の一実施例に対応し、ダイオードDb2は「第2のダイオード」の一実施例に対応する。

ダイオードDc1およびDc2は、直流端子T1(直流正母線PL1)および直流端子T2(直流負母線NL1)の間に電気的に直列に接続される。ダイオードDc2のアノードは直流負母線NL1と電気的に接続され、ダイオードDc1のカソードは直流正母線PL1と電気的に接続される。ダイオードDc1は「第3のダイオード」の一実施例に対応し、ダイオードDc2は「第4のダイオード」の一実施例に対応する。

トランスTr3は、一次巻線n1および二次巻線n2を含む。トランスTr3は、理想トランスに加えて、励磁インダクタンスLmおよび漏れインダクタンスを有している。一次巻線n1と二次巻線n2とが電磁的に結合されることにより、一次巻線n1および二次巻線n2に同極性の起電力が誘起される。一次巻線n1と二次巻線n2との巻線比は1:2である。トランスTr3は「第2のトランス」の一実施例に対応する。

トランスTr3の二次巻線n2は、ダイオードDb1およびDb2の接続点(ノードd)と、ダイオードDc1およびDc2の接続点(ノードe)との間に接続される。トランスTr3の一次巻線n1は、補助スイッチング素子Qr1およびQr2の接続点(ノードc)とノードaとの間に、補助リアクトルLrと電気的に直列に接続される。補助リアクトルLrは、トランスTr3の漏れインダクタンスを利用してもよく、外付けしてもよい。

ダイオードDb1,Db2,Dc1,Dc2およびトランスTr3の二次巻線n2は、ダイオードブリッジ回路を構成する。ダイオードブリッジ回路は、ダイオードDb1およびDc1の接続点(すなわち直流正母線PL1)と、ダイオードDb2およびDc2の接続点(すなわち直流負母線NL1)とを出力端子とし、ダイオードDb1およびDb2の接続点(ノードd)とダイオードDc1およびDc2の接続点(ノードe)とを入力端子とする。

補助スイッチング素子Qr1またはQr2をオンしてトランスTr3の一次巻線n1に電流を流すと、電磁誘導により、二次巻線n2に電流が生じる。この二次巻線n2に生じた電流が、二次巻線n2の両端に接続される2つのダイオードを流れることにより、二次巻線n2には電圧Vdcまたは-Vdcが印加される。一次巻線n1と二次巻線n2との巻線比が2:1であるので、一次巻線n1には、電圧Vdcまたは-Vdcの1/2の電圧が印加されることになる。

実施の形態5に従う電力変換装置1の動作は、図23および図26に示した実施の形態4に従う電力変換装置1の動作と同じである。すなわち、負荷2に正の電圧を印加するときの補助共振回路4Dによるソフトスイッチングは、図23に示した補助共振回路4Bによるソフトスイッチングと同じである。

具体的には、図23のモードM1で示したように、スイッチング素子Q1をゼロ電圧スイッチングでターンオンするためには、補助スイッチング素子Qr1をオンとする。したがって、図29に示すように、ノードcの電位Vc=Vdcとなる。一方、スイッチング素子Q2がオンのため、ノードaの電位Va=0である。

この場合、図中に矢印で示すように、ノードcからノードaに向かって電流が流れることとなる。トランスTr3では、一次巻線n1に流れる電流によって、ダイオードDc2、二次巻線n2およびダイオードDb1を通って流れる電流が誘導される。これにより、二次巻線n2にはノードd側の端子が高電位となり、ノードe側の端子が低電位となるように電圧Vdcが印加されるため、一次巻線n1には、ノードc側の端子を高電位として電圧Vdcの1/2の電圧が印加される。その結果、補助リアクトルLrおよび一次巻線n1の接続点に電圧Vdcの1/2の電圧を印加することができる。補助リアクトルLrおよび補助キャパシタCr1,Cr2の共振動作によってノードaの電位Va=Vdcとなったときに、スイッチング素子Q1をターンオンすれば、ゼロ電圧スイッチングを実現できる。

スイッチング素子Q1をターンオンした後(図23のモードM4)、リアクトル電流ILr=0となったときに、補助スイッチング素子Qr1をターンオフすることにより(モードM6)、補助スイッチング素子Qr1のゼロ電流スイッチングが行なわれる。ダイオードDr3は、リアクトル電流ILrが逆方向(負方向)に流れ始めるのを阻止するために設けられている。

同様に、負荷2に負の電圧を印加するときの補助共振回路4Dによるソフトスイッチングは、図26に示した補助共振回路4Bによるソフトスイッチングと同じである。図26のモードM1で示したように、スイッチング素子Q2をゼロ電圧スイッチングでターンオンするためには、補助スイッチング素子Qr2をオンとする。したがって、図30に示すように、ノードcの電位Vc=0となる。一方、スイッチング素子Q1がオンのため、ノードaの電位Va=Vdcである。

この場合、図中に矢印で示すように、ノードaからノードcに向かって電流が流れることとなる。トランスTr3では、一次巻線n1に流れる電流によって、ダイオードDb2、二次巻線n2およびダイオードDc1を通って流れる電流が誘導される。これにより、二次巻線n2にはノードe側の端子が高電位となり、ノードd側の端子が低電位となるように電圧Vdcが印加されるため、一次巻線n1には、ノードa側の端子を高電位として電圧Vdcの1/2の電圧が印加される。その結果、補助リアクトルLrおよび一次巻線n1の接続点に電圧Vdcの1/2の電圧を印加することができる。補助リアクトルLrおよび補助キャパシタCr1,Cr2の共振動作によってノードaの電位Va=0となったときに、スイッチング素子Q2をターンオンすれば、ゼロ電圧スイッチングを実現できる。

スイッチング素子Q2をターンオンした後(図25のモードM4)、リアクトル電流ILr=0となったときに、補助スイッチング素子Qr2をターンオフすることにより、補助スイッチング素子Qr2のゼロ電流スイッチングが行なわれる。ダイオードDr4は、リアクトル電流ILrが逆方向(正方向)に流れ始めるのを阻止するために設けられている。

以上説明したように、この発明の実施の形態5に従う電力変換装置1によれば、キャパシタCp,Cnの直列回路を用いずに、直流電源P1の電圧Vdcを2分割した電圧を生成することができるため、補助スイッチング素子Qr1,Qr2をソフトスイッチングすることができる。

また、実施の形態5に従う電力変換装置1においては、ダイオードDb1,Db2,Dc1,Dc2にダイオードブリッジ回路を用いることができる。ダイオードブリッジ回路は通常、小型の素子であるため、電力変換装置1を大型化させることなく、電圧Vdcの1/2の電圧を作ることができる。

[電力変換装置の適用例]

上述した実施の形態2~5においては、実施の形態1で説明した非対称駆動方式のフルブリッジ回路からなる電力変換装置1において、ソフトスイッチングを実現するための構成について説明したが、各実施の形態で示した補助共振回路は、以下に示すようなハーフブリッジ回路を持つ全ての電力変換装置に対して適用することが可能である。

図31から図34には、ハーフブリッジ回路からなる電力変換装置1A~1Dがそれぞれ示されている。図31を参照して、電力変換装置1Aは、第1ハーフブリッジ回路Aと、図14の補助共振回路4Aとを有する。図32を参照して、電力変換装置1Bは、第1ハーフブリッジ回路Aと、図20の補助共振回路4Bとを有する。図33を参照して、電力変換装置1Cは、第1ハーフブリッジ回路Aと、図27の補助共振回路4Cとを有する。図34を参照して、電力変換装置1Dは、第1ハーフブリッジ回路Aと、図28の補助共振回路4Dとを有する。電力変換装置1A~1Dの動作は、第2ハーフブリッジ回路Bのオンオフを除いて、実施の形態2~5に従う電力変換装置の動作とそれぞれ同じである。

今回開示された実施の形態はすべての点で例示であって、制限的なものではないと考えられるべきである。この発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。