JP7139552B2 - 半導体集積回路の配線設計装置及び半導体集積回路の配線設計用プログラム - Google Patents

半導体集積回路の配線設計装置及び半導体集積回路の配線設計用プログラム Download PDFInfo

- Publication number

- JP7139552B2 JP7139552B2 JP2019125804A JP2019125804A JP7139552B2 JP 7139552 B2 JP7139552 B2 JP 7139552B2 JP 2019125804 A JP2019125804 A JP 2019125804A JP 2019125804 A JP2019125804 A JP 2019125804A JP 7139552 B2 JP7139552 B2 JP 7139552B2

- Authority

- JP

- Japan

- Prior art keywords

- line

- branch line

- pin

- point branch

- wiring

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Design And Manufacture Of Integrated Circuits (AREA)

Description

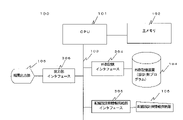

102 主メモリ

103 バス

104 外部記憶装置

105 配線設計用情報供給部

106 結果出力部

201 始点支線発生手段

202 最短距離接続手段

304 外部記憶インタフェース

305 配線設計用情報供給部インタフェース

306 出力部インタフェース

Claims (12)

- セルの位置情報及び大きさ情報、前記セル内のピンの位置情報及び大きさ情報、幹線配線の位置情報及び大きさ情報を含む配線設計情報に基づき、複数の幹線配線中の所定数本の幹線配線を始点とし前記幹線配線に直交する幹線始点支線と、セル内のピンを始点とし前記幹線配線に直交するように延びるピン始点支線とを発生する始点支線発生手段と、

発生された前記幹線始点支線と発生された前記ピン始点支線とに関する発生支線情報及び前記配線設計情報に基づき、発生された前記幹線始点支線と発生された前記ピン始点支線が他の配線に重ならぬように最短距離で接続する最短距離接続手段と

を具備し、

前記最短距離接続手段は、複数本の幹線配線に最も近接するセルのピンと幹線配線との間については、発生された前記幹線始点支線と発生された前記ピン始点支線とを直接接続した直線支線により接続を行う

ことを特徴とする半導体集積回路の配線設計装置。 - 前記最短距離接続手段は、前記幹線始点支線または前記ピン始点支線が他の配線と重なる場合には、前記幹線始点支線と前記ピン始点支線に直交する接続線を発生させて前記幹線始点支線と前記ピン始点支線とを接続することを特徴とする請求項1に記載の半導体集積回路の配線設計装置。

- 同じ大きさのセルであって、セル内の同じ位置にピンが配置されているセルが縦横に複数並べられた半導体集積回路について配線設計を行うことを特徴とする請求項1または2に記載の半導体集積回路の配線設計装置。

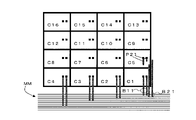

- 前記始点支線発生手段は、

前記複数の幹線配線から数えて第1行目のセルにおけるピンと接続する幹線始点支線に隣接させて、複数の幹線配線から数えて第2行目のセルにおけるピンと接続する幹線始点支線を発生させ、

前記複数の幹線配線から数えて第2行目のセルにおけるピンと接続する幹線始点支線に隣接させて、複数の幹線配線から数えて第3行目のセルにおけるピンと接続する幹線始点支線を発生させ、

以下同様に、前行のセルにおけるピンと接続する幹線始点支線と次行のセルにおけるピンと接続する幹線始点支線とを隣接させて幹線始点支線を発生させることを特徴とする請求項3に記載の半導体集積回路の配線設計装置。 - 前記始点支線発生手段は、前記幹線始点支線または前記ピン始点支線が他の配線と重なる場合には、セルを横方向にシフトさせてシフトした位置のピンと複数の幹線配線との間で支線を発生させることを特徴とする請求項3または4に記載の半導体集積回路の配線設計装置。

- 前記始点支線発生手段は、セルの大きさに応じてシフト量を決定してシフトを行うことを特徴とする請求項5に記載の半導体集積回路の配線設計装置。

- コンピュータを、

セルの位置情報及び大きさ情報、前記セル内のピンの位置情報及び大きさ情報、幹線配線の位置情報及び大きさ情報を含む配線設計情報に基づき、複数の幹線配線中の所定数本の幹線配線を始点とし前記幹線配線に直交する幹線始点支線と、セル内のピンを始点とし前記幹線配線に直交するように延びるピン始点支線とを発生する始点支線発生手段、

発生された前記幹線始点支線と発生された前記ピン始点支線とに関する発生支線情報及

び前記配線設計情報に基づき、発生された前記幹線始点支線と発生された前記ピン始点支線が他の配線に重ならぬように最短距離で接続する最短距離接続手段

として機能させ、

前記コンピュータを前記最短距離接続手段として、

複数本の幹線配線に最も近接するセルのピンと幹線配線との間については、発生された前記幹線始点支線と発生された前記ピン始点支線とを直接接続した直線支線により接続を行うように機能させる

ことを特徴とする半導体集積回路の配線設計用プログラム。 - 前記コンピュータを前記最短距離接続手段として、

前記幹線始点支線または前記ピン始点支線が他の配線と重なる場合には、前記幹線始点支線と前記ピン始点支線に直交する接続線を発生させて前記幹線始点支線と前記ピン始点支線とを接続するように機能させることを特徴とする請求項7に記載の半導体集積回路の配線設計用プログラム。 - 同じ大きさのセルであって、セル内の同じ位置にピンが配置されているセルが縦横に複数並べられた半導体集積回路について配線設計を行うことを特徴とする請求項7または8に記載の半導体集積回路の配線設計用プログラム。

- 前記コンピュータを前記始点支線発生手段として、

前記複数の幹線配線から数えて第1行目のセルにおけるピンと接続する幹線始点支線に隣接させて、複数の幹線配線から数えて第2行目のセルにおけるピンと接続する幹線始点支線を発生させ、

前記複数の幹線配線から数えて第2行目のセルにおけるピンと接続する幹線始点支線に隣接させて、複数の幹線配線から数えて第3行目のセルにおけるピンと接続する幹線始点支線を発生させ、

以下同様に、前行のセルにおけるピンと接続する幹線始点支線と次行のセルにおけるピンと接続する幹線始点支線とを隣接させて幹線始点支線を発生させるように機能させることを特徴とする請求項9に記載の半導体集積回路の配線設計用プログラム。 - 前記コンピュータを前記始点支線発生手段として、

前記幹線始点支線または前記ピン始点支線が他の配線と重なる場合には、セルを横方向にシフトさせてシフトした位置のピンと複数の幹線配線との間で支線を発生させるように機能させることを特徴とする請求項9または10に記載の半導体集積回路の配線設計用プログラム。 - 前記コンピュータを前記始点支線発生手段として、セルの大きさに応じてシフト量を決定してシフトを行うように機能させることを特徴とする請求項11に記載の半導体集積回路の配線設計用プログラム。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2019125804A JP7139552B2 (ja) | 2019-07-05 | 2019-07-05 | 半導体集積回路の配線設計装置及び半導体集積回路の配線設計用プログラム |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2019125804A JP7139552B2 (ja) | 2019-07-05 | 2019-07-05 | 半導体集積回路の配線設計装置及び半導体集積回路の配線設計用プログラム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2021012935A JP2021012935A (ja) | 2021-02-04 |

| JP7139552B2 true JP7139552B2 (ja) | 2022-09-21 |

Family

ID=74227578

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019125804A Active JP7139552B2 (ja) | 2019-07-05 | 2019-07-05 | 半導体集積回路の配線設計装置及び半導体集積回路の配線設計用プログラム |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP7139552B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN116956810B (zh) * | 2023-08-01 | 2024-09-03 | 北京华大九天科技股份有限公司 | 布线方法及装置、计算装置和存储介质 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012084862A (ja) | 2010-09-13 | 2012-04-26 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| US20170053054A1 (en) | 2015-08-20 | 2017-02-23 | Oracle International Corporation | Mitigating wire capacitance in an integrated circuit |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02278748A (ja) * | 1989-04-19 | 1990-11-15 | Matsushita Electric Ind Co Ltd | 電源配線方法 |

| JPH02305472A (ja) * | 1989-05-19 | 1990-12-19 | Fujitsu Ltd | Cpu内蔵ゲートアレイおよびその製造方法 |

| JP2833453B2 (ja) * | 1993-11-08 | 1998-12-09 | 日本電気株式会社 | 半導体装置のチャネル配線方法 |

-

2019

- 2019-07-05 JP JP2019125804A patent/JP7139552B2/ja active Active

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012084862A (ja) | 2010-09-13 | 2012-04-26 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| US20170053054A1 (en) | 2015-08-20 | 2017-02-23 | Oracle International Corporation | Mitigating wire capacitance in an integrated circuit |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2021012935A (ja) | 2021-02-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10083269B2 (en) | Computer implemented system and method for generating a layout of a cell defining a circuit component | |

| JP4090118B2 (ja) | Lsiの製造方法及びレイアウト用プログラムを記録した記録媒体 | |

| US20090138840A1 (en) | Cell, standard cell, standard cell library, a placement method using standard cell, and a semiconductor integrated circuit | |

| JP2006196627A (ja) | 半導体装置、及び半導体装置の設計プログラム | |

| JP3786398B2 (ja) | 半導体パッケージの配線方法 | |

| US6245599B1 (en) | Circuit wiring system circuit wiring method semi-conductor package and semi-conductor package substrate | |

| JPH10313058A (ja) | 半導体集積回路設計装置、半導体集積回路設計方法、半導体集積回路設計プログラムを記録したコンピュータ読み取り可能な記録媒体、及び、半導体集積回路製造方法 | |

| JP4993362B2 (ja) | 半導体集積回路の自動遅延調整方法 | |

| US8225268B2 (en) | Wiring design method for wiring board | |

| CN117764024A (zh) | 一种基于h树的时钟树综合优化方法 | |

| JP7139552B2 (ja) | 半導体集積回路の配線設計装置及び半導体集積回路の配線設計用プログラム | |

| JPH0421910B2 (ja) | ||

| JP2001306641A (ja) | 半導体集積回路の自動配置配線方法 | |

| Mattison | Design automation of MOS artwork | |

| US6487707B1 (en) | Layout design system of semiconductor ic device, layout design method of semiconductor ic device and computer-readable recording medium on which programs for allowing computer to execute respective means in the system or respective steps in the method are recorded | |

| JP5239766B2 (ja) | レイアウト設計方法 | |

| JP2010087244A (ja) | 半導体集積回路、半導体集積回路のレイアウト方法、及び半導体集積回路のレイアウトプログラム | |

| JPWO2013146276A1 (ja) | 電源系統ツリー設計支援システム及び電源系統ツリー設計方法 | |

| JP2921454B2 (ja) | 集積回路の配線方法 | |

| US6760896B2 (en) | Process layout of buffer modules in integrated circuits | |

| WO1998055950A1 (en) | Integrated circuit layout synthesis tool | |

| JP4907257B2 (ja) | 回路基板の配線方法及び配線支援装置 | |

| US20030135837A1 (en) | Method and apparatus for automatic arrangement and wiring for a semiconductor integrated circuit design and wiring program therefor | |

| JP3141588B2 (ja) | オングリッド自動配線方法 | |

| JPH06216249A (ja) | Icチップ自動レイアウト設計システム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20210719 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20220510 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20220531 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220726 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20220809 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20220809 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7139552 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |