JP6886355B2 - オペアンプ及びそれを用いたdc/dcコンバータ - Google Patents

オペアンプ及びそれを用いたdc/dcコンバータ Download PDFInfo

- Publication number

- JP6886355B2 JP6886355B2 JP2017122182A JP2017122182A JP6886355B2 JP 6886355 B2 JP6886355 B2 JP 6886355B2 JP 2017122182 A JP2017122182 A JP 2017122182A JP 2017122182 A JP2017122182 A JP 2017122182A JP 6886355 B2 JP6886355 B2 JP 6886355B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- resistor

- main electrode

- signal

- electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000001360 synchronised effect Effects 0.000 description 14

- 239000003990 capacitor Substances 0.000 description 10

- 230000010355 oscillation Effects 0.000 description 7

- 238000010586 diagram Methods 0.000 description 5

- 101000955967 Deinagkistrodon acutus Thrombin-like enzyme acutin Proteins 0.000 description 4

- 101150014330 dfa2 gene Proteins 0.000 description 4

- 230000002123 temporal effect Effects 0.000 description 2

- XIWFQDBQMCDYJT-UHFFFAOYSA-M benzyl-dimethyl-tridecylazanium;chloride Chemical compound [Cl-].CCCCCCCCCCCCC[N+](C)(C)CC1=CC=CC=C1 XIWFQDBQMCDYJT-UHFFFAOYSA-M 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 238000000034 method Methods 0.000 description 1

- 238000011084 recovery Methods 0.000 description 1

- 230000004043 responsiveness Effects 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

Images

Landscapes

- Dc-Dc Converters (AREA)

- Amplifiers (AREA)

Description

MOSトランジスタM4のドレイン(第2主電極)は抵抗R1の一端とMOSトランジスタM6のドレインに接続され第1回路点CP1を形成しており、MOSトランジスタM5のドレイン(第2主電極)は抵抗R2の一端とMOSトランジスタM7のドレインに接続され第2回路点CP2を形成しており、抵抗R1の他端は抵抗R2の他端とMOSトランジスタM6のゲートとMOSトランジスタM7のゲートと共通接続されている。

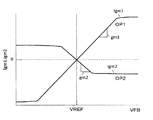

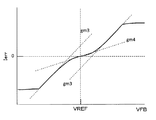

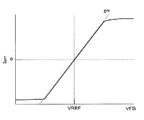

フィードバック電圧VFBが基準電圧VREFから離れたところではトランスコンダクタンスが大きくなっており、基準電圧VREF付近ではトランスコンダクタンスが小さくなっている。エラーアンプ3Aの出力電圧が設定電圧付近では、トランスコンダクタンスを下げて安定性を確保し、出力電圧が設定電圧から離れるとトランスコンダクタンスを上げてエラーアンプ3Aの帰還スピードをアップすることとなる。

すなわち基準電圧VREFから遠い電圧にある時は急速に、近いところにある時は緩やかに制御されることとなる。これにより基準電圧VREF付近における波形のうねりが小さくなる。

第2オペアンプOP2も同様であり、MOSトランジスタM8とMOSトランジスタM9がショートしないように抵抗R3及び抵抗R4は挿入されている。

また本発明においてはオペアンプ2つを加算する構成で説明を行ったが、加算されるオペアンプは2つ以上であればいくつでも構わない。要求されるトランスコンダクタンスに応じて組み合わせばよい。

2 同期整流素子

3 エラーアンプ

3A エラーアンプ

4 発振回路装置

5 合算手段

6 PWMコンパレータ

7 駆動制御回路

600 DC/DCコンバータ

Adder 加算器

AGND 接地端子

C41,C42 キャパシタ

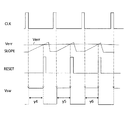

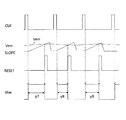

CLK クロック信号

CP1 第1回路点

CP2 第2回路点

DFA1 第1差動対トランジスタ

DFA2 第2差動対トランジスタ

FB フィードバック端子

gm1 第1トランスコンダクタンス

gm2 第2トランスコンダクタンス

gm3 トランスコンダクタンス

gm4 トランスコンダクタンス

GN ゲート信号

GND 接地電位

GP ゲート信号

I2 電流

I3 電流

Ierr 出力電流

Igm1 出力電流

Igm2 出力電流

IN 入力端子

IN1 第1入力端子

IN2 第2入力端子

ISET 電流源

ISW スイッチング電流

L ゲートチャネル長

L41 インダクタ

M1〜M15 MOSトランジスタ

OP1 第1オペアンプ

OP2 第2オペアンプ

OUT 出力端子

OUT1 電流出力端子

PGND 接地端子

R1〜R8,R41〜R43 抵抗

REF 基準端子

RESET リセット信号

SLOPE スロープ信号

VCC 電源電位

Verr 誤差信号

VFB フィードバック電圧

VOUT 出力電圧

VREF 基準電圧

Vsw スイッチング電圧

W ゲートチャネル幅

Claims (6)

- 第1主電極、第2主電極及び制御電極を有する第1トランジスタ、第2トランジスタ、第3トランジスタ、第4トランジスタ、第5トランジスタ、第6トランジスタ、第7トランジスタ及び第8トランジスタと、

第1抵抗、第2抵抗、第3抵抗及び第4抵抗と、を備え、

前記第1トランジスタの前記第1主電極と前記第2トランジスタの前記第1主電極は共通に接続され第1差動対トランジスタを形成し第1電流源に接続され、

前記第3トランジスタの前記第1主電極と前記第4トランジスタの前記第1主電極は共通に接続され第2差動対トランジスタを形成し第2電流源に接続され、

前記第1トランジスタの前記制御電極と前記第4トランジスタの前記制御電極は共通に接続され第1入力信号が印加される第1入力端子に接続され、

前記第2トランジスタの前記制御電極と前記第3トランジスタの前記制御電極は共通に接続され第2入力信号が印加される第2入力端子に接続され、

前記第1トランジスタの前記第2主電極と前記第3トランジスタの前記第2主電極は共通に接続されて第1回路点に接続され、

前記第2トランジスタの前記第2主電極と前記第4トランジスタの前記第2主電極は共通に接続されて第2回路点に接続され、

前記第5トランジスタの前記第2主電極と前記第1抵抗の第1端は共通に接続されて前記第1回路点に接続され、

前記第6トランジスタの前記第2主電極と前記第2抵抗の第1端は共通に接続されて前記第2回路点に接続され、

前記第7トランジスタの前記第2主電極と前記第3抵抗の第1端は共通に接続されて前記第1回路点に接続され、

前記第8トランジスタの前記第2主電極と前記第4抵抗の第1端は共通に接続されて前記第2回路点に接続され、

前記第5トランジスタの前記制御電極、前記第6トランジスタの前記制御電極、前記第1抵抗の第2端及び前記第2抵抗の第2端は共通に接続され、

前記第7トランジスタの前記制御電極、前記第8トランジスタの前記制御電極、前記第3抵抗の第2端及び前記第4抵抗の第2端は共通に接続され、

前記第5トランジスタの前記第1主電極、前記第6トランジスタの前記第1主電極、前記第7トランジスタの前記第1主電極及び前記第8トランジスタの前記第1主電極は共通に接続されて接地電位に接続され、

前記第1回路点及び前記第2回路点にそれぞれ前記第1入力信号と前記第2入力信号との第1差分信号及び第2差分信号が取り出され、

前記第1トランジスタと前記第2トランジスタの物理的サイズは同じ第1のサイズであり、前記第3トランジスタと前記第4トランジスタの物理的サイズは同じであるも前記第1のサイズと異なる第2のサイズであり、

前記第1差分信号及び前記第2差分信号はそれぞれ前記第1回路点及び前記第2回路点に電流に変換されて取り出され、

前記第1差分信号と前記第2差分信号は加算器で加算されて合成差分信号として出力端子から取り出される、オペアンプ。 - 前記第1トランジスタ,前記第2トランジスタ,前記第3トランジスタ及び前記第4トランジスタはMOSトランジスタで構成され、前記MOSトランジスタのゲートチャネル長,ゲートチャネル幅の少なくとも一方を異ならせて前記第1のサイズと前記第2のサイズが構成されている、請求項1に記載のオペアンプ。

- 前記第1電流源と前記第2電流源で生成される電流の大きさは異なっている、請求項1または2に記載のオペアンプ。

- 前記第1入力信号と前記第2入力信号の差分が比較的小さいときのトランスコンダクタンスは、前記第1入力信号と前記第2入力信号の差分が比較的大きいときのトランスコンダクタンスよりも小さい、請求項1〜3のいずれか一項に記載のオペアンプ。

- 前記加算器は、

第1主電極、第2主電極及び制御電極を有する第9トランジスタ、第10トランジスタ、第11トランジスタ及び第12トランジスタと、

第5抵抗、第6抵抗、第7抵抗及び第8抵抗と、を備え、

前記第9トランジスタの前記制御電極は前記第1回路点に接続され、前記第9トランジスタの前記第1主電極は前記第7抵抗の第1端に接続され、前記第9トランジスタの前記第2主電極は前記出力端子に接続され、

前記第10トランジスタの前記制御電極は前記第2回路点に接続され、前記第10トランジスタの前記第1主電極は前記第5抵抗の第1端に接続され、前記第10トランジスタの前記第2主電極は前記第11トランジスタの前記第2主電極に接続され、

前記第5抵抗の前記第2端と前記第7抵抗の前記第2端は共通に接続されて前記接地電位に接続され、

前記第11トランジスタの前記制御電極と前記第12トランジスタの前記制御電極は共通に接続されて前記第11トランジスタの前記第2主電極に接続され、

前記第12トランジスタの前記第2主電極は前記出力端に接続され、

前記第11トランジスタの前記第1主電極は前記第6抵抗の第1端に接続され、

前記第12トランジスタの前記第1主電極は前記第8抵抗の第1端に接続され、

前記第6抵抗の第2端と前記第7抵抗の第2端は共通に接続されて電源電位に接続される、請求項1〜4のいずれか一項に記載のオペアンプ。 - 入力電圧から出力電圧を生成するためにオン/オフされるスイッチング手段と、

前記出力電圧に応じたフィードバック電圧と基準電圧との差に応じた誤差信号を生成するエラーアンプと、

クロック信号と三角波または鋸波のスロープ信号を生成する発振回路装置と、

前記スロープ信号と前記誤差信号とを比較して、パルス幅が変調されたPWM信号を出力するPWMコンパレータと、

前記クロック信号と前記PWMコンパレータからの出力信号を受け、前記スイッチング手段を制御する駆動制御回路とを備えるDC/DCコンバータであって、

前記エラーアンプは、請求項1〜5のいずれか一項に記載のオペアンプで構成されることを特徴とするDC/DCコンバータ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017122182A JP6886355B2 (ja) | 2017-06-22 | 2017-06-22 | オペアンプ及びそれを用いたdc/dcコンバータ |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017122182A JP6886355B2 (ja) | 2017-06-22 | 2017-06-22 | オペアンプ及びそれを用いたdc/dcコンバータ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2019009548A JP2019009548A (ja) | 2019-01-17 |

| JP6886355B2 true JP6886355B2 (ja) | 2021-06-16 |

Family

ID=65029154

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017122182A Expired - Fee Related JP6886355B2 (ja) | 2017-06-22 | 2017-06-22 | オペアンプ及びそれを用いたdc/dcコンバータ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6886355B2 (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7170606B2 (ja) * | 2019-09-03 | 2022-11-14 | 株式会社東芝 | Dc-dcコンバータ |

| DE112020006170T5 (de) | 2019-12-17 | 2022-11-17 | Rohm Co., Ltd. | Ausgangsrückkopplungsregelkreis |

| US12166420B2 (en) * | 2020-03-17 | 2024-12-10 | Rohm Co., Ltd. | Output feedback control circuit and switching power supply |

| KR102713249B1 (ko) * | 2022-07-12 | 2024-10-11 | 한국과학기술원 | 전계효과 커패시턴스를 활용한 커패시티브 무선전력 전송 시스템 |

| CN116224033B (zh) * | 2023-03-15 | 2025-08-29 | 长沙泰科阳微电子有限公司 | 全差分放大器的快速共模检测电路 |

| CN116317996B (zh) * | 2023-05-23 | 2023-08-04 | 盈力半导体(上海)有限公司 | 一种误差放大器和电源转换装置 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR960027254A (ko) * | 1994-12-29 | 1996-07-22 | 조백제 | 선형성이 양호한 오퍼레이션널 트랜스콘덕턴스 증폭기 |

| US5699015A (en) * | 1996-03-19 | 1997-12-16 | Motorola, Inc. | Low voltage operational amplifier and method |

| JP3396415B2 (ja) * | 1997-12-18 | 2003-04-14 | 松下電器産業株式会社 | Dc帰還型ハイパスフィルタ |

| JP4851192B2 (ja) * | 2006-01-27 | 2012-01-11 | ルネサスエレクトロニクス株式会社 | 差動信号受信回路 |

| JP2008022468A (ja) * | 2006-07-14 | 2008-01-31 | Sanyo Electric Co Ltd | トランスコンダクタンス装置 |

| JP2011072102A (ja) * | 2009-09-25 | 2011-04-07 | Rohm Co Ltd | スイッチングレギュレータ |

| US8405457B2 (en) * | 2010-06-15 | 2013-03-26 | Aeroflex Colorado Springs Inc. | Amplitude-stabilized odd order pre-distortion circuit |

| JP6503663B2 (ja) * | 2014-09-10 | 2019-04-24 | 住友電気工業株式会社 | 差動増幅回路 |

| WO2017072911A1 (ja) * | 2015-10-29 | 2017-05-04 | 三菱電機株式会社 | トランスコンダクタンス増幅器及び移相器 |

| JP2017093159A (ja) * | 2015-11-10 | 2017-05-25 | ローム株式会社 | 降圧dc/dcコンバータおよびその制御回路、制御方法、車載用電源装置 |

-

2017

- 2017-06-22 JP JP2017122182A patent/JP6886355B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2019009548A (ja) | 2019-01-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6886355B2 (ja) | オペアンプ及びそれを用いたdc/dcコンバータ | |

| US7777472B2 (en) | Current detector circuit and current mode switching regulator | |

| US9454168B2 (en) | LDO regulator powered by its regulated output voltage for high PSRR | |

| TW202230070A (zh) | 功率轉換系統、功率轉換方法、以及脈寬調變控制器 | |

| US10168726B2 (en) | Self-adaptive startup compensation device | |

| KR20060085166A (ko) | 출력 커패시터값의 광범위에 걸쳐 안정성을 제공하는 보상기술 | |

| US12244230B2 (en) | Switched-mode power supply and control circuit for use in switched-mode power supply | |

| US12374983B2 (en) | Control device for a switching voltage regulator having improved control performance and control method | |

| TWI630781B (zh) | 直流對直流轉換器的自適應性開機補償方法及其裝置 | |

| JP2012130138A (ja) | スイッチング制御回路 | |

| US20150002113A1 (en) | Power supply circuit | |

| JP7199330B2 (ja) | レギュレータ回路 | |

| JP5703950B2 (ja) | 電圧電流変換回路 | |

| US20070200623A1 (en) | Amplifier, and step-down regulator and operational amplifier using the amplifier | |

| JP5141289B2 (ja) | Cmos差動増幅回路および電源制御用半導体集積回路 | |

| US11699947B2 (en) | DC-DC converters with loop control | |

| JP2012032940A (ja) | 電源制御回路 | |

| JP2021128530A (ja) | エラーアンプおよび電源回路 | |

| WO2012053133A1 (ja) | チョッパ増幅器、アクティブフィルタ、基準周波数生成回路 | |

| JP2012034472A (ja) | 電源制御回路、電源回路 | |

| JP4784139B2 (ja) | スイッチングレギュレータおよび電源システム | |

| JP5094512B2 (ja) | スイッチングレギュレータ | |

| US20250038661A1 (en) | Semiconductor circuit device and switching regulator | |

| US20250260322A1 (en) | Switching regulator | |

| US20210281169A1 (en) | Power supply circuit |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20200511 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20210218 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20210302 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210422 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20210511 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20210514 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6886355 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |