JP6869039B2 - 情報処理装置 - Google Patents

情報処理装置 Download PDFInfo

- Publication number

- JP6869039B2 JP6869039B2 JP2017014083A JP2017014083A JP6869039B2 JP 6869039 B2 JP6869039 B2 JP 6869039B2 JP 2017014083 A JP2017014083 A JP 2017014083A JP 2017014083 A JP2017014083 A JP 2017014083A JP 6869039 B2 JP6869039 B2 JP 6869039B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- transistor

- information

- function

- oxide semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2092—Details of a display terminals using a flat panel, the details relating to the control arrangement of the display terminal and to the interfaces thereto

- G09G3/2096—Details of the interface to the display terminal specific for a flat panel

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/16—Constructional details or arrangements

- G06F1/1613—Constructional details or arrangements for portable computers

- G06F1/1633—Constructional details or arrangements of portable computers not specific to the type of enclosures covered by groups G06F1/1615 - G06F1/1626

- G06F1/1637—Details related to the display arrangement, including those related to the mounting of the display in the housing

- G06F1/1643—Details related to the display arrangement, including those related to the mounting of the display in the housing the display being associated to a digitizer, e.g. laptops that can be used as penpads

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/16—Constructional details or arrangements

- G06F1/1613—Constructional details or arrangements for portable computers

- G06F1/1633—Constructional details or arrangements of portable computers not specific to the type of enclosures covered by groups G06F1/1615 - G06F1/1626

- G06F1/1684—Constructional details or arrangements related to integrated I/O peripherals not covered by groups G06F1/1635 - G06F1/1675

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

- G06F1/3234—Power saving characterised by the action undertaken

- G06F1/325—Power saving in peripheral device

- G06F1/3265—Power saving in display device

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/01—Input arrangements or combined input and output arrangements for interaction between user and computer

- G06F3/03—Arrangements for converting the position or the displacement of a member into a coded form

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/01—Input arrangements or combined input and output arrangements for interaction between user and computer

- G06F3/048—Interaction techniques based on graphical user interfaces [GUI]

- G06F3/0481—Interaction techniques based on graphical user interfaces [GUI] based on specific properties of the displayed interaction object or a metaphor-based environment, e.g. interaction with desktop elements like windows or icons, or assisted by a cursor's changing behaviour or appearance

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/01—Input arrangements or combined input and output arrangements for interaction between user and computer

- G06F3/048—Interaction techniques based on graphical user interfaces [GUI]

- G06F3/0484—Interaction techniques based on graphical user interfaces [GUI] for the control of specific functions or operations, e.g. selecting or manipulating an object, an image or a displayed text element, setting a parameter value or selecting a range

- G06F3/04842—Selection of displayed objects or displayed text elements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3275—Details of drivers for data electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3685—Details of drivers for data electrodes

- G09G3/3688—Details of drivers for data electrodes suitable for active matrices only

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/16—Constructional details or arrangements

- G06F1/1613—Constructional details or arrangements for portable computers

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/16—Constructional details or arrangements

- G06F1/1613—Constructional details or arrangements for portable computers

- G06F1/1633—Constructional details or arrangements of portable computers not specific to the type of enclosures covered by groups G06F1/1615 - G06F1/1626

- G06F1/1684—Constructional details or arrangements related to integrated I/O peripherals not covered by groups G06F1/1635 - G06F1/1675

- G06F1/1686—Constructional details or arrangements related to integrated I/O peripherals not covered by groups G06F1/1635 - G06F1/1675 the I/O peripheral being an integrated camera

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/01—Input arrangements or combined input and output arrangements for interaction between user and computer

- G06F3/03—Arrangements for converting the position or the displacement of a member into a coded form

- G06F3/033—Pointing devices displaced or positioned by the user, e.g. mice, trackballs, pens or joysticks; Accessories therefor

- G06F3/0354—Pointing devices displaced or positioned by the user, e.g. mice, trackballs, pens or joysticks; Accessories therefor with detection of 2D relative movements between the device, or an operating part thereof, and a plane or surface, e.g. 2D mice, trackballs, pens or pucks

- G06F3/03547—Touch pads, in which fingers can move on a surface

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/01—Input arrangements or combined input and output arrangements for interaction between user and computer

- G06F3/048—Interaction techniques based on graphical user interfaces [GUI]

- G06F3/0487—Interaction techniques based on graphical user interfaces [GUI] using specific features provided by the input device, e.g. functions controlled by the rotation of a mouse with dual sensing arrangements, or of the nature of the input device, e.g. tap gestures based on pressure sensed by a digitiser

- G06F3/0488—Interaction techniques based on graphical user interfaces [GUI] using specific features provided by the input device, e.g. functions controlled by the rotation of a mouse with dual sensing arrangements, or of the nature of the input device, e.g. tap gestures based on pressure sensed by a digitiser using a touch-screen or digitiser, e.g. input of commands through traced gestures

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0421—Structural details of the set of electrodes

- G09G2300/0426—Layout of electrodes and connections

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0439—Pixel structures

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0439—Pixel structures

- G09G2300/0456—Pixel structures with a reflective area and a transmissive area combined in one pixel, such as in transflectance pixels

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0439—Pixel structures

- G09G2300/046—Pixel structures with an emissive area and a light-modulating area combined in one pixel

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2360/00—Aspects of the architecture of display systems

- G09G2360/14—Detecting light within display terminals, e.g. using a single or a plurality of photosensors

- G09G2360/145—Detecting light within display terminals, e.g. using a single or a plurality of photosensors the light originating from the display screen

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/3406—Control of illumination source

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D10/00—Energy efficient computing, e.g. low power processors, power management or thermal management

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Engineering & Computer Science (AREA)

- Human Computer Interaction (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Liquid Crystal (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- User Interface Of Digital Computer (AREA)

- Control Of El Displays (AREA)

Description

本実施の形態では、本発明の一態様の情報処理装置の構成について、図1乃至図4を参照しながら説明する。

本実施の形態で説明する情報処理装置200は、入出力装置220と、演算装置210と、を有する(図3(A)参照)。

情報処理装置200は、演算装置210、入出力装置220、表示部230、検知部250または入力部240を有する。

演算装置210は、演算部211および記憶部212を備える。また、伝送路214および入出力インターフェース215を備える。

演算部211は、例えばプログラムを実行する機能を備える。

記憶部212は、例えば演算部211が実行するプログラム、初期情報、設定情報または画像等を記憶する機能を有する。またアイコン座標情報を記憶する機能を有する。

例えば、入力位置座標情報P1に基づいて制御情報SSのステータスを決定するプログラムを、演算装置210に用いることができる。

第1のステップにおいて、入力部240から供給される入力の有無を判断する。入力がある場合には第2のステップに進み、入力が無い場合には最初に戻る(図2(T1)参照)。

第2のステップにおいて、入力部240から供給される入力位置座標情報P1を読み込む(図2(T2)参照)。

第3のステップにおいて、記憶部212から供給されたアイコン座標情報を参照し、入力位置座標情報P1にて与えられた表示部の位置に、アイコン座標情報すなわちアイコンの表示との重なりがあるか判断する。重なりがある場合には第4のステップに進む。重なりが無い場合には、第5のステップに進む。

第4のステップにおいて、入力位置座標情報P1にて与えられた表示部の位置において、第3のステータスの制御情報SSを供給する(図2(T4)参照)。

第5のステップにおいて、入力位置座標情報P1にて与えられた表示部の位置において、第1のステータスまたは第2のステータスの制御情報SSを供給する(図2(T5)参照)。

以下第1のステータスの制御情報SSを供給する例を示す。

入出力インターフェース215は端子または配線を備え、情報を供給し、供給される機能を備える。例えば、伝送路214と電気的に接続することができる。また、入出力装置220と電気的に接続することができる。

入出力装置220は、表示部230、入力部240、検知部250または通信部290を備える。

例えば表示パネル、選択回路239、駆動回路SD1または駆動回路SD2を表示部230に用いることができる(図1(A)および図4参照)。

駆動回路GDは、選択信号を供給する機能を有する。

例えば、画像情報V1を表示する機能を備える表示領域231を表示パネルに用いることができる。また、一群の画素232(1,j)乃至画素232(m,j)を表示領域231に用いることができる(図1(A)参照)。

例えば、第1のマルチプレクサと第2のマルチプレクサを選択回路239に用いることができる(図1(B)参照)。

駆動回路SD1は、情報V11に基づいて画像信号を供給する機能を有し、駆動回路SD2は、情報V12に基づいて画像信号を供給する機能を有する。なお、駆動回路SD1および駆動回路SD2に換えて、駆動回路SD1および駆動回路SD2が集積された駆動回路SDを用いることができる。

例えば、反射型の表示素子および発光素子を画素232(i,j)に用いることができる(図4(C)参照)。

例えば、光の反射または透過を制御する機能を備える表示素子を、第1の表示素子235Aに用いることができる。なお、反射型の表示素子を用いると、表示パネルの消費電力を抑制することができる。

例えば、光を射出する機能を備える表示素子を第2の表示素子235Bに用いることができる。具体的には、有機EL素子を用いることができる。

第1の表示素子235Aまたは第2の表示素子235Bを駆動する機能を備える回路を画素回路に用いることができる。

例えば、同一の工程で形成することができる半導体膜を駆動回路および画素回路のトランジスタに用いることができる。

入力部240は入力パネルを備える。

周囲の状態を検知して検知情報P2を供給する機能を備えるセンサを、検知部250に用いることができる。

通信部290は、ネットワークに情報を供給する機能またはネットワークから情報を取得する機能を備える。

本実施の形態では、本発明の一態様の情報処理装置に用いることができるプログラムについて、図7を参照しながら説明する。

本発明の一態様のプログラムは、実施の形態1に記載のプログラムの構成に加え、、情報処理装置200の置かれる環境の照度と、入出力装置によりアイコンの選択された頻度と、に基づいて、以下の様に視認性をより向上させる構成を有することができる。

第1のステップ(図7(T1))から第3のステップ(図7(T3))までにおいて、図2(T1)から図2(T3)と同様に、入力部240から供給される入力の有無を判断し、入力部240から供給される入力位置座標情報P1を読み込み、アイコンの表示との範囲の重なりがあるか判断する。

第4のステップにおいて、演算装置210は、第3のステップ(図7(T3))で重なったと判断されたアイコン、すなわち選択されたアイコンに対して、その過去に選択された頻度を判断する。

第5のステップにおいて、照度センサを検知部250に用い、照度についての検知情報P2を検知部250に供給させ、検知情報P2を所定の値と比較する。

第6のステップにおいて、外環境すなわち照度についての検知情報P2から制御情報として第1のステータスの制御情報または第2のステータスの制御情報を供給するか決定する。情報処理装置200を使用する環境が明るい場合、第1のステータスの制御情報を供給し反射型の表示素子での表示をする(図7(T7−1))。同じく薄暗いまたは暗い場合、第2のステータスの制御情報を供給し発光素子での表示をする(図7(T7−2))。

本実施の形態では、本発明の一態様の情報処理装置に用いることができるプログラムについて、図8を参照しながら説明する。

<第1のステップ>

第1のステップ(図8(U1))において、入力部240から供給される入力の有無を判断し、入力がある場合、第2のステップに進む。

第2のステップ(図8(U2))において、入力部240から供給される入力位置座標情報P1を読み込む。本実施の形態では、入力位置座標情報P1の含む座標を中心として一定の半径の広がりをもつポインタを表示する。本明細書中ではこのポインタの表示される領域をポインタ表示領域と設定する。次いで第3のステップに進む。

第3のステップにおいて、第2のステップで設定したポインタ表示領域の、表示部の座標に、第3のステータスの制御情報SSを供給する(図8(U3))。これにより、入力された位置では反射型の表示素子および発光素子で表示し、欠陥領域の表示を補足することで視認性を向上することができる。

第4のステップにおいて、最後の入力部からの入力から、一定時間経過したかを判断する。一定時間経過するということは、つまり必要な表示を確認したことを意味し、通常の表示に戻すため第5のステップに進む。

第5のステップにおいて、ポインタ表示領域に対応する、表示部の座標に、通常表示の制御情報すなわち第1のステータスの制御情報、または第2のステータスの制御情報を供給する。通常表示の表示方法は、実施の形態2で示されるように、検知情報P2で選択頻度の低いアイコンに割り当てた表示方法である。このように元の表示に戻すことで、必要な強調する部分を更新することができる。

本実施の形態では、本発明の一態様の表示パネルの構成について、図9乃至図11、図19及び図20を参照しながら説明する。

本実施の形態で説明する表示パネル700は、信号線S1(j)と、画素702(i,j)と、を有する(図9(B−1)および図9(B−2)参照)。

本発明の一態様の表示パネルは、基板570、基板770、構造体KB1、封止材705または接合層505、を有する。

作製工程中の熱処理に耐えうる程度の耐熱性を有する材料を基板570等に用いることができる。具体的には厚さ0.7mmの無アルカリガラスを用いることができる。または、厚さ0.1mm程度まで研磨した無アルカリガラスを用いることができる。

例えば、透光性を備える材料を基板770に用いることができる。具体的には、基板570に用いることができる材料から選択された材料を基板770に用いることができる。具体的には厚さ0.7mmまたは厚さ0.1mm程度まで研磨した無アルカリガラスを用いることができる。

例えば、有機材料、無機材料または有機材料と無機材料の複合材料を構造体KB1等に用いることができる。これにより、構造体KB1等を挟む構成の間に所定の間隔を設けることができる。

無機材料、有機材料または無機材料と有機材料の複合材料等を封止材705等に用いることができる。

例えば、封止材705に用いることができる材料を接合層505に用いることができる。

例えば、絶縁性の無機材料、絶縁性の有機材料または無機材料と有機材料を含む絶縁性の複合材料を、絶縁膜521等に用いることができる。

例えば、絶縁膜521に用いることができる材料を絶縁膜528等に用いることができる。具体的には、厚さ1μmのポリイミドを含む膜を絶縁膜528に用いることができる。

例えば、絶縁膜521に用いることができる材料を絶縁膜501Cに用いることができる。具体的には、シリコンおよび酸素を含む材料を絶縁膜501Cに用いることができる。これにより、画素回路または第2の表示素子等への不純物の拡散を抑制することができる。

導電性を備える材料を配線等に用いることができる。具体的には、導電性を備える材料を、信号線S1(j)、信号線S2(j)、走査線G1(i)、走査線G2(i)、配線CSCOM、配線ANO、端子519B、端子519C、導電膜511Bまたは導電膜511C等に用いることができる。

例えば、配線等に用いることができる材料を第1の導電膜または第2の導電膜に用いることができる。

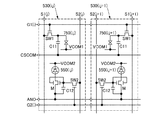

画素回路530(i,j)は、信号線S1(j)、信号線S2(j)、走査線G1(i)、走査線G2(i)、配線CSCOMおよび配線ANOと電気的に接続される(図10参照)。

例えば、ボトムゲート型またはトップゲート型等のトランジスタをスイッチSW1、スイッチSW2、トランジスタM、トランジスタMD等に用いることができる。

例えば、光の反射または透過を制御する機能を備える表示素子を、第1の表示素子750(i,j)等に用いることができる。例えば、液晶素子と偏光板を組み合わせた構成またはシャッター方式のMEMS表示素子等を用いることができる。具体的には、反射型の表示素子を用いることにより、表示パネルの消費電力を抑制することができる。例えば、反射型の液晶表示素子を第1の表示素子750に用いることができる。

例えば、配線等に用いる材料を第1の電極751(i,j)に用いることができる。具体的には、反射膜を第1の電極751(i,j)に用いることができる。

例えば、可視光を反射する材料を反射膜に用いることができる。具体的には、銀を含む材料を反射膜に用いることができる。例えば、銀およびパラジウム等を含む材料または銀および銅等を含む材料を反射膜に用いることができる。

非開口部の総面積に対する開口部751Hの総面積の比の値が大きすぎると、第1の表示素子750(i,j)を用いた表示が暗くなってしまう。また、非開口部の総面積に対する開口部751Hの総面積の比の値が小さすぎると、第2の表示素子550(i,j)を用いた表示が暗くなってしまう。

例えば、可視光について透光性を有し且つ導電性を備える材料を、第2の電極752に用いることができる。

例えば、ポリイミド等を含む材料を配向膜AF1または配向膜AF2に用いることができる。具体的には、所定の方向に配向するようにラビング処理または光配向技術を用いて形成された材料を用いることができる。

所定の色の光を透過する材料を着色膜CF1に用いることができる。これにより、着色膜CF1を例えばカラーフィルターに用いることができる。

光の透過を妨げる材料を遮光膜BMに用いることができる。これにより、遮光膜BMを例えばブラックマトリクスに用いることができる。

例えば、ポリイミド、エポキシ樹脂、アクリル樹脂等を絶縁膜771に用いることができる。

例えば、偏光板、位相差板、拡散フィルム、反射防止膜または集光フィルム等を機能膜770Pに用いることができる。または、2色性色素を含む偏光板を機能膜770Pに用いることができる。

例えば、発光素子を第2の表示素子550(i,j)に用いることができる。具体的には、有機エレクトロルミネッセンス素子、無機エレクトロルミネッセンス素子または発光ダイオードなどを、第2の表示素子550(i,j)に用いることができる。

シフトレジスタ等のさまざまな順序回路等を駆動回路GDに用いることができる。例えば、トランジスタMD、容量素子等を駆動回路GDに用いることができる。具体的には、トランジスタMと同一の工程で形成することができる半導体膜を備えるトランジスタを用いることができる。

例えば、集積回路を駆動回路SDに用いることができる。具体的には、シリコン基板上に形成された集積回路を駆動回路SDに用いることができる。

図20は本発明の一態様の表示パネル700Bの構成を説明する図である。図20(A)は図9(A)の切断線X1−X2、X3−X4、X5−X6、X7−X8、X9−X10、X11−X12における断面図である。図20(B)は表示パネルの一部の構成を説明する断面図である。

スイッチSW1Bに用いることができるトランジスタ、トランジスタMBおよびトランジスタMDBは、絶縁膜501Cと重なる領域を備える導電膜504と、絶縁膜501Cおよび導電膜504の間に配設される領域を備える半導体膜508と、を備える。なお、導電膜504はゲート電極の機能を備える(図20(B)参照)。

酸化物半導体膜の抵抗率を制御する方法について説明する。

本実施の形態では、本発明の一態様の表示パネルに用いることができるトランジスタの構成について、図12を参照しながら説明する。

図12(A)は、トランジスタ100の上面図であり、図12(C)は、図12(A)に示す切断線X1−X2間における切断面の断面図に相当し、図12(D)は、図12(A)に示す切断線Y1−Y2間における切断面の断面図に相当する。なお、図12(A)において、煩雑になることを避けるため、トランジスタ100の構成要素の一部(ゲート絶縁膜として機能する絶縁膜等)を省略して図示している。また、切断線X1−X2方向をチャネル長方向、切断線Y1−Y2方向をチャネル幅方向と呼称する場合がある。なお、トランジスタの上面図においては、以降の図面においても図12(A)と同様に、構成要素の一部を省略して図示する場合がある。

基板102の材質などに大きな制限はないが、少なくとも、後の熱処理に耐えうる程度の耐熱性を有している必要がある。例えば、ガラス基板、セラミック基板、石英基板、サファイア基板等を、基板102として用いてもよい。

ゲート電極として機能する導電膜104、及びソース電極として機能する導電膜112a、及びドレイン電極として機能する導電膜112bとしては、クロム(Cr)、銅(Cu)、アルミニウム(Al)、金(Au)、銀(Ag)、亜鉛(Zn)、モリブデン(Mo)、タンタル(Ta)、チタン(Ti)、タングステン(W)、マンガン(Mn)、ニッケル(Ni)、鉄(Fe)、コバルト(Co)から選ばれた金属元素、または上述した金属元素を成分とする合金か、上述した金属元素を組み合わせた合金等を用いてそれぞれ形成することができる。

トランジスタ100のゲート絶縁膜として機能する絶縁膜106、107としては、プラズマ化学気相堆積(PECVD:(Plasma Enhanced Chemical Vapor Deposition))法、スパッタリング法等により、酸化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜、窒化シリコン膜、酸化アルミニウム膜、酸化ハフニウム膜、酸化イットリウム膜、酸化ジルコニウム膜、酸化ガリウム膜、酸化タンタル膜、酸化マグネシウム膜、酸化ランタン膜、酸化セリウム膜および酸化ネオジム膜を一種以上含む絶縁膜を、それぞれ用いることができる。なお、絶縁膜106、107の積層構造とせずに、上述の材料から選択された単層の絶縁膜、または3層以上の絶縁膜を用いてもよい。

酸化物半導体膜108としては、先に示す材料を用いることができる。

絶縁膜114、116は、酸化物半導体膜108に酸素を供給する機能を有する。また、絶縁膜118は、トランジスタ100の保護絶縁膜としての機能を有する。また、絶縁膜114、116は、酸素を有する。また、絶縁膜114は、酸素を透過することのできる絶縁膜である。なお、絶縁膜114は、後に形成する絶縁膜116を形成する際の、酸化物半導体膜108へのダメージ緩和膜としても機能する。

本実施の形態では、本発明の一態様の表示パネルに用いることができるトランジスタの構成について、図13を参照しながら説明する。

図13(A)は、トランジスタ100の上面図であり、図13(B)は、図13(A)に示す切断線X1−X2間における切断面の断面図に相当し、図13(C)は、図13(A)に示す切断線Y1−Y2間における切断面の断面図に相当する。なお、図13(A)において、煩雑になることを避けるため、トランジスタ100の構成要素の一部(ゲート絶縁膜として機能する絶縁膜等)を省略して図示している。また、切断線X1−X2方向をチャネル長方向、切断線Y1−Y2方向をチャネル幅方向と呼称する場合がある。なお、トランジスタの上面図においては、以降の図面においても図13(A)と同様に、構成要素の一部を省略して図示する場合がある。

次に、酸化物導電体について説明する。導電膜120a、120bを形成する工程において、導電膜120a、120bは、絶縁膜114、116から酸素の放出を抑制する保護膜として機能する。また、導電膜120a、120bは、絶縁膜118を形成する工程の前においては、半導体としての機能を有し、絶縁膜118を形成する工程の後においては、導電膜120a、120bは、導電体としての機能を有する。

以下に、本実施の形態の半導体装置に含まれる構成要素について、詳細に説明する。

酸化物半導体膜108としては、先に示す材料を用いることができる。

絶縁膜114、116は、トランジスタ100の第2のゲート絶縁膜として機能する。また、絶縁膜114、116は、酸化物半導体膜108に酸素を供給する機能を有する。すなわち、絶縁膜114、116は、酸素を有する。また、絶縁膜114は、酸素を透過することのできる絶縁膜である。なお、絶縁膜114は、後に形成する絶縁膜116を形成する際の、酸化物半導体膜108へのダメージ緩和膜としても機能する。

先に記載の酸化物半導体膜108と同様の材料を、導電膜として機能する導電膜120a、及び第2のゲート電極として機能する導電膜120bに用いることができる。

絶縁膜118は、トランジスタ100の保護絶縁膜として機能する。

本実施の形態では、本発明の一態様の入出力装置の構成について、図14を参照しながら説明する。

タッチセンサ804は、表示パネル806と重なる領域を備える。なお、FPC803はタッチセンサ804に電気的に接続される。

例えば、実施の形態1で説明する表示パネルを表示パネル806に用いることができる。なお、FPC805等は、表示パネル806に電気的に接続される。

例えば、電源回路または信号処理回路等を駆動回路810に用いることができる。なお、バッテリまたは外部の商用電源が供給する電力を利用してもよい。

例えば、上部カバー801と、上部カバー801と嵌めあわせられる下部カバー802と、上部カバー801および下部カバー802で囲まれる領域に収納されるフレーム809と、を筐体部に用いることができる。

バッテリ811は、電力を供給する機能を備える。

本実施の形態では、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置(記憶装置)、およびそれを含むCPUについて説明する。本実施の形態で説明するCPUは、例えば、実施の形態1で説明する情報処理装置に用いる事が出来る。

電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置(記憶装置)の一例を図15に示す。なお、図15(B)は図15(A)を回路図で表したものである。

以下で、上記の記憶装置を含むCPUについて説明する。

本実施の形態では、本発明の一態様の情報処理装置を有する表示モジュール及び電子機器について、図18を用いて説明を行う。

AF2 配向膜

ANO 配線

C1 容量素子

C2 容量素子

CF1 着色膜

CSCOM 配線

G1 走査線

G2 走査線

GD 駆動回路

GDA 駆動回路

GDB 駆動回路

KB1 構造体

M トランジスタ

MB トランジスタ

MD トランジスタ

MDB トランジスタ

M1 ノード

M2 ノード

P1 入力位置座標情報

P2 検知情報

S1 信号線

S2 信号線

SD 駆動回路

SD1 駆動回路

SD2 駆動回路

sel0 信号線

sel1 信号線

SS 制御情報

SS1 制御情報

SS2 制御情報

SS3 制御情報

SW1 スイッチ

SW1B スイッチ

SW2 スイッチ

V0 電位

V00 背景情報

V1 画像情報

V11 情報

V12 情報

VCOM1 配線

VCOM2 配線

100 トランジスタ

102 基板

104 導電膜

106 絶縁膜

107 絶縁膜

108 酸化物半導体膜

108a 酸化物半導体膜

108b 酸化物半導体膜

108c 酸化物半導体膜

112a 導電膜

112b 導電膜

114 絶縁膜

116 絶縁膜

118 絶縁膜

120a 導電膜

120b 導電膜

200 情報処理装置

210 演算装置

211 演算部

212 記憶部

214 伝送路

215 入出力インターフェース

220 入出力装置

230 表示部

230B 表示部

231 表示領域

232 画素

233 領域

235A 表示素子

235B 表示素子

239 選択回路

240 入力部

250 検知部

290 通信部

501C 絶縁膜

504 導電膜

505 接合層

506 絶縁膜

508 半導体膜

508A 領域

508B 領域

508C 領域

511B 導電膜

511C 導電膜

512A 導電膜

512B 導電膜

516 絶縁膜

518 絶縁膜

519B 端子

519C 端子

520 機能層

521 絶縁膜

522 接続部

524 導電膜

528 絶縁膜

530 画素回路

550 表示素子

551 電極

552 電極

553 層

570 基板

591A 開口部

591B 開口部

591C 開口部

700 表示パネル

700B 表示パネル

702 画素

705 封止材

750 表示素子

751 電極

751H 開口部

752 電極

753 層

770 基板

770P 機能膜

771 絶縁膜

800 入出力装置

801 上部カバー

802 下部カバー

803 FPC

804 タッチセンサ

805 FPC

806 表示パネル

809 フレーム

810 駆動回路

811 バッテリ

1189 ROMインターフェース

1190 基板

1191 ALU

1192 ALUコントローラ

1193 インストラクションデコーダ

1194 インタラプトコントローラ

1195 タイミングコントローラ

1196 レジスタ

1197 レジスタコントローラ

1198 バスインターフェース

1199 ROM

1200 記憶素子

1201 回路

1202 回路

1203 スイッチ

1204 スイッチ

1206 論理素子

1207 容量素子

1208 容量素子

1209 トランジスタ

1210 トランジスタ

1213 トランジスタ

1214 トランジスタ

1220 回路

3001 配線

3002 配線

3003 配線

3004 配線

3005 配線

3200 トランジスタ

3300 トランジスタ

3400 容量素子

5000 筐体

5001 表示部

5002 表示部

5003 スピーカ

5004 LEDランプ

5005 操作キー

5006 接続端子

5007 センサ

5008 マイクロフォン

5009 スイッチ

5010 赤外線ポート

5011 記録媒体読込部

5012 支持部

5013 イヤホン

5014 アンテナ

5015 シャッターボタン

5016 受像部

5017 充電器

7302 筐体

7304 表示パネル

7305 アイコン

7306 アイコン

7312 操作ボタン

7313 接続端子

7321 バンド

7322 留め金

Claims (9)

- 入出力装置と、演算装置と、を有し、

前記入出力装置は、入力位置座標情報および検知情報を供給する機能を有し、

前記入出力装置は、画像情報および制御情報を供給される機能を備え、

前記演算装置は、前記入力位置座標情報および前記検知情報を供給される機能を備え、

前記演算装置は、前記画像情報および前記制御情報を供給する機能を備え、

前記入出力装置は、表示部、入力部および検知部を備え、

前記入力部は、前記入力位置座標情報を供給する機能を備え、

前記検知部は、前記検知情報を供給する機能を備え、

前記表示部は、前記画像情報を表示する機能を備え、

前記表示部は、選択回路、第1の駆動回路、第2の駆動回路および表示パネルを備え、

前記演算装置は、前記画像情報を生成する機能を備え、

前記演算装置は、前記入力位置座標情報、前記検知情報および前記画像情報に基づいて、前記制御情報を生成する機能を備え、

前記制御情報は、第1のステータスの制御情報、第2のステータスの制御情報、または第3のステータスの制御情報を含み、

前記選択回路は、

前記第1のステータスの制御情報が供給された場合に、前記画像情報を前記第1の駆動回路に供給し、かつ、背景情報を前記第2の駆動回路に供給する機能を備え、

前記選択回路は、

前記第2のステータスの制御情報が供給された場合に、背景情報を前記第1の駆動回路に供給し、かつ、前記画像情報を前記第2の駆動回路に供給する機能を備え、

前記選択回路は、

前記第3のステータスの制御情報が供給された場合に、前記画像情報を前記第1の駆動回路と前記第2の駆動回路とに供給する機能を備える情報処理装置。 - 請求項1において、

前記表示パネルは、第1の信号線と、第2の信号線と、一群の画素と、を備え、

前記一群の画素は列方向に配設され、

前記第1の信号線は前記列方向に配設される前記一群の画素と電気的に接続され、

前記第1の信号線は前記第1の駆動回路と電気的に接続され、

前記第2の信号線は前記列方向に配設される前記一群の画素と電気的に接続され、

前記第2の信号線は前記第2の駆動回路と電気的に接続される情報処理装置。 - 請求項2において、

前記画素は、第1の表示素子および第2の表示素子を備え、

前記第1の表示素子は、反射型の表示素子を備え、

前記第1の表示素子は、前記第1の信号線と電気的に接続され、

前記第2の表示素子は、発光素子を備え、

前記第2の表示素子は、前記第2の信号線と電気的に接続される情報処理装置。 - 請求項3において、

前記第1の表示素子は、表示をする方向に外光を反射する反射膜および反射する強度を制御する機能を備え、

前記反射膜は開口部を備え、

前記第2の表示素子は、前記開口部と重なる領域、前記開口部に向けて光を射出する機能、および発光性の有機化合物を含む層を備える情報処理装置。 - 請求項1乃至請求項4のいずれか一において、

前記演算装置は、アイコンが選択されたとき、前記アイコンの表示される領域の座標に対して前記第3のステータスの制御情報を供給する機能を備える情報処理装置。 - 請求項5において、

前記演算装置は、前記アイコンが選択された履歴に基づいて、特定のアイコンを決定する機能を備え、前記特定のアイコンの表示される領域の座標に対して前記第3のステータスの制御情報を供給する機能を備える情報処理装置。 - 請求項1乃至請求項4のいずれか一において、

前記演算装置は、

最後の前記入力部からの入力から一定時間経過する前は、

ポインタ表示領域に対して、前記第3のステータスの制御情報を供給する機能を備え、最後の前記入力部からの入力から前記一定時間経過した後は、

前記ポインタ表示領域に対して、前記第1のステータスの制御情報または前記第2のステータスの制御情報を供給する機能を備える情報処理装置。 - 請求項1乃至請求項7のいずれか一において、

前記検知部は、照度センサを備え、

前記照度センサは、使用される環境の照度情報を含む前記検知情報を供給する機能を備える情報処理装置。 - 請求項1乃至請求項8のいずれか一において、

前記入力部が、キーボード、ハードウェアボタン、ポインティングデバイス、タッチセンサ、照度センサ、撮像装置、音声入力装置、視点入力装置、姿勢検出装置、のうち一以上を含む情報処理装置。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016018553 | 2016-02-03 | ||

| JP2016018553 | 2016-02-03 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2017138980A JP2017138980A (ja) | 2017-08-10 |

| JP2017138980A5 JP2017138980A5 (ja) | 2020-03-12 |

| JP6869039B2 true JP6869039B2 (ja) | 2021-05-12 |

Family

ID=59386950

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017014083A Active JP6869039B2 (ja) | 2016-02-03 | 2017-01-30 | 情報処理装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US10176748B2 (ja) |

| JP (1) | JP6869039B2 (ja) |

| TW (1) | TWI724097B (ja) |

| WO (1) | WO2017134541A1 (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10114450B2 (en) * | 2015-08-31 | 2018-10-30 | Semiconductor Energy Laboratory Co., Ltd. | Information processing device |

| JP2017207747A (ja) | 2016-05-17 | 2017-11-24 | 株式会社半導体エネルギー研究所 | 表示システムおよび移動体 |

| WO2018073690A1 (en) | 2016-10-21 | 2018-04-26 | Semiconductor Energy Laboratory Co., Ltd. | Touch sensor, display device, display module, and electronic device |

| KR102358849B1 (ko) * | 2017-06-01 | 2022-02-08 | 삼성전자주식회사 | 스마트 워치에 대한 정보를 제공하는 전자 장치와 이의 동작 방법 |

| TWI700717B (zh) * | 2019-11-29 | 2020-08-01 | 新唐科技股份有限公司 | 發光鍵盤 |

| CN111462689B (zh) * | 2020-04-22 | 2021-07-06 | 深圳市华星光电半导体显示技术有限公司 | 寿命数据处理子系统及寿命补偿系统 |

Family Cites Families (44)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3767264B2 (ja) | 1999-08-25 | 2006-04-19 | セイコーエプソン株式会社 | 液晶表示装置および電子機器 |

| WO2001091098A1 (fr) | 2000-05-24 | 2001-11-29 | Hitachi, Ltd. | Terminal portable et afficheur commutable entre couleur et noir-et-blanc |

| JP2002196702A (ja) | 2000-12-25 | 2002-07-12 | Sony Corp | 画像表示装置 |

| JP4202030B2 (ja) | 2001-02-20 | 2008-12-24 | シャープ株式会社 | 表示装置 |

| JP4043864B2 (ja) | 2001-09-06 | 2008-02-06 | シャープ株式会社 | 表示装置及びその駆動方法 |

| JP4176400B2 (ja) | 2001-09-06 | 2008-11-05 | シャープ株式会社 | 表示装置 |

| JP3898012B2 (ja) | 2001-09-06 | 2007-03-28 | シャープ株式会社 | 表示装置 |

| US7248235B2 (en) | 2001-09-14 | 2007-07-24 | Sharp Kabushiki Kaisha | Display, method of manufacturing the same, and method of driving the same |

| JP2003098984A (ja) * | 2001-09-25 | 2003-04-04 | Rohm Co Ltd | 画像表示装置 |

| JP2003228304A (ja) | 2002-01-31 | 2003-08-15 | Toyota Industries Corp | 表示装置 |

| TW544944B (en) | 2002-04-16 | 2003-08-01 | Ind Tech Res Inst | Pixel element structure of sunlight-readable display |

| JP4122828B2 (ja) | 2002-04-30 | 2008-07-23 | 日本電気株式会社 | 表示装置及びその駆動方法 |

| US20060072047A1 (en) | 2002-12-06 | 2006-04-06 | Kanetaka Sekiguchi | Liquid crystal display |

| KR20050084379A (ko) * | 2002-12-19 | 2005-08-26 | 코닌클리즈케 필립스 일렉트로닉스 엔.브이. | 액정 디스플레이 장치 |

| JP3852931B2 (ja) | 2003-03-26 | 2006-12-06 | 株式会社東芝 | 発光表示装置 |

| KR20070001649A (ko) * | 2005-06-29 | 2007-01-04 | 엘지.필립스 엘시디 주식회사 | 반사투과형 액정 표시 장치 및 그 구동 방법 |

| US20070176847A1 (en) * | 2005-12-30 | 2007-08-02 | Shah Kamalesh R | Method and system to reduce display power consumption |

| JP2007232882A (ja) | 2006-02-28 | 2007-09-13 | Casio Comput Co Ltd | 表示装置及び電子機器 |

| JP3962084B2 (ja) * | 2006-05-24 | 2007-08-22 | 株式会社 空スペース | 情報表示入力装置 |

| JP2008225381A (ja) * | 2007-03-15 | 2008-09-25 | Toshiba Matsushita Display Technology Co Ltd | 表示装置 |

| TWI393950B (zh) | 2009-01-08 | 2013-04-21 | Au Optronics Corp | 半穿反型顯示面板 |

| US20100225640A1 (en) * | 2009-03-03 | 2010-09-09 | Vieri Carlin J | Switching Operating Modes of Liquid Crystal Displays |

| US8830424B2 (en) | 2010-02-19 | 2014-09-09 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device having light-condensing means |

| CN102782569B (zh) * | 2010-03-01 | 2015-02-25 | 诺基亚公司 | 用于显示的选择性像素控制的装置、方法和模块 |

| BR112012022900A2 (pt) * | 2010-03-11 | 2018-06-05 | Pixtronix Inc | modos de operação transflexivos e refletivos para um dispositivo de exibição |

| CN102290022A (zh) * | 2010-06-21 | 2011-12-21 | 李晓 | 自适应亮度平衡的方法和互补多屏电子设备 |

| US20120127140A1 (en) * | 2010-11-19 | 2012-05-24 | John Ryan | Multi-mode liquid crystal display with auxiliary non-display components |

| US8730154B2 (en) * | 2011-08-04 | 2014-05-20 | Gamma Dynamics Llc | Display apparatus |

| JP5792017B2 (ja) * | 2011-09-28 | 2015-10-07 | 京セラ株式会社 | 装置、方法、及びプログラム |

| US20130176263A1 (en) * | 2012-01-09 | 2013-07-11 | Harris Corporation | Display system for tactical environment |

| JP2013221965A (ja) | 2012-04-13 | 2013-10-28 | Seiko Epson Corp | 電気光学装置 |

| US10551928B2 (en) | 2012-11-20 | 2020-02-04 | Samsung Electronics Company, Ltd. | GUI transitions on wearable electronic device |

| US11157436B2 (en) | 2012-11-20 | 2021-10-26 | Samsung Electronics Company, Ltd. | Services associated with wearable electronic device |

| JP6463598B2 (ja) | 2012-11-20 | 2019-02-06 | 三星電子株式会社Samsung Electronics Co.,Ltd. | 着用式電子デバイスからのプロセッシングの委任 |

| US8994827B2 (en) | 2012-11-20 | 2015-03-31 | Samsung Electronics Co., Ltd | Wearable electronic device |

| US10185416B2 (en) | 2012-11-20 | 2019-01-22 | Samsung Electronics Co., Ltd. | User gesture input to wearable electronic device involving movement of device |

| US11372536B2 (en) | 2012-11-20 | 2022-06-28 | Samsung Electronics Company, Ltd. | Transition and interaction model for wearable electronic device |

| US10423214B2 (en) | 2012-11-20 | 2019-09-24 | Samsung Electronics Company, Ltd | Delegating processing from wearable electronic device |

| US11237719B2 (en) | 2012-11-20 | 2022-02-01 | Samsung Electronics Company, Ltd. | Controlling remote electronic device with wearable electronic device |

| US9030446B2 (en) | 2012-11-20 | 2015-05-12 | Samsung Electronics Co., Ltd. | Placement of optical sensor on wearable electronic device |

| US9477313B2 (en) | 2012-11-20 | 2016-10-25 | Samsung Electronics Co., Ltd. | User gesture input to wearable electronic device involving outward-facing sensor of device |

| USD763289S1 (en) | 2013-08-30 | 2016-08-09 | Samsung Electronics Co., Ltd. | Display screen or portion thereof with transitional graphical user interface |

| KR20150127499A (ko) * | 2014-05-07 | 2015-11-17 | 삼성전자주식회사 | 터치 감지 장치, 이를 포함하는 디스플레이 장치 및 터치 감지 방법 |

| US10114450B2 (en) | 2015-08-31 | 2018-10-30 | Semiconductor Energy Laboratory Co., Ltd. | Information processing device |

-

2017

- 2017-01-24 WO PCT/IB2017/050351 patent/WO2017134541A1/en active Application Filing

- 2017-01-26 US US15/416,317 patent/US10176748B2/en not_active Expired - Fee Related

- 2017-01-26 TW TW106103282A patent/TWI724097B/zh not_active IP Right Cessation

- 2017-01-30 JP JP2017014083A patent/JP6869039B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| WO2017134541A1 (en) | 2017-08-10 |

| TW201732388A (zh) | 2017-09-16 |

| US20170221410A1 (en) | 2017-08-03 |

| US10176748B2 (en) | 2019-01-08 |

| JP2017138980A (ja) | 2017-08-10 |

| TWI724097B (zh) | 2021-04-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6856802B2 (ja) | 表示パネル | |

| JP7003185B2 (ja) | 表示装置 | |

| JP6879693B2 (ja) | 情報処理装置 | |

| JP6849386B2 (ja) | 表示パネル及び情報処理装置 | |

| JP7044921B2 (ja) | 表示パネル | |

| JP6739274B2 (ja) | 表示装置 | |

| JP6869039B2 (ja) | 情報処理装置 | |

| JP6791661B2 (ja) | 表示パネル | |

| JP6830820B2 (ja) | 入出力装置、情報処理装置 | |

| JP7083594B2 (ja) | 表示装置 | |

| JP2017059239A (ja) | 入出力装置、情報処理装置 | |

| JP2017097342A (ja) | 表示装置、入出力装置、情報処理装置 | |

| JP2017182804A (ja) | 表示パネル、入出力装置、情報処理装置 | |

| JP6807683B2 (ja) | 入出力パネル | |

| JP6725226B2 (ja) | 表示パネル | |

| JP2024149681A (ja) | 表示パネル |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200128 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20200128 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20200812 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20200825 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20201026 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20210323 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20210413 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6869039 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |