JP6766243B2 - Iii族窒化物半導体発光素子およびその製造方法 - Google Patents

Iii族窒化物半導体発光素子およびその製造方法 Download PDFInfo

- Publication number

- JP6766243B2 JP6766243B2 JP2019198185A JP2019198185A JP6766243B2 JP 6766243 B2 JP6766243 B2 JP 6766243B2 JP 2019198185 A JP2019198185 A JP 2019198185A JP 2019198185 A JP2019198185 A JP 2019198185A JP 6766243 B2 JP6766243 B2 JP 6766243B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- type

- light emitting

- group iii

- nitride semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 105

- 150000004767 nitrides Chemical class 0.000 title claims description 96

- 238000004519 manufacturing process Methods 0.000 title claims description 17

- 239000000203 mixture Substances 0.000 claims description 150

- 230000004888 barrier function Effects 0.000 claims description 114

- 238000000034 method Methods 0.000 claims description 14

- 239000010410 layer Substances 0.000 description 510

- 239000007789 gas Substances 0.000 description 48

- 239000000758 substrate Substances 0.000 description 32

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 29

- 239000012159 carrier gas Substances 0.000 description 28

- 239000002019 doping agent Substances 0.000 description 25

- 229910002704 AlGaN Inorganic materials 0.000 description 23

- 239000000463 material Substances 0.000 description 17

- JLTRXTDYQLMHGR-UHFFFAOYSA-N trimethylaluminium Chemical compound C[Al](C)C JLTRXTDYQLMHGR-UHFFFAOYSA-N 0.000 description 17

- 239000010408 film Substances 0.000 description 15

- 239000011777 magnesium Substances 0.000 description 14

- 229910052757 nitrogen Inorganic materials 0.000 description 12

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 11

- 239000012535 impurity Substances 0.000 description 11

- 230000000052 comparative effect Effects 0.000 description 10

- 229910052594 sapphire Inorganic materials 0.000 description 10

- 239000010980 sapphire Substances 0.000 description 10

- 229910001873 dinitrogen Inorganic materials 0.000 description 9

- 230000000694 effects Effects 0.000 description 9

- 229910052739 hydrogen Inorganic materials 0.000 description 9

- 239000001257 hydrogen Substances 0.000 description 9

- 229910052782 aluminium Inorganic materials 0.000 description 8

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 7

- 230000004075 alteration Effects 0.000 description 7

- 125000004429 atom Chemical group 0.000 description 7

- 229910052733 gallium Inorganic materials 0.000 description 7

- 238000010438 heat treatment Methods 0.000 description 7

- 239000002994 raw material Substances 0.000 description 7

- XCZXGTMEAKBVPV-UHFFFAOYSA-N trimethylgallium Chemical compound C[Ga](C)C XCZXGTMEAKBVPV-UHFFFAOYSA-N 0.000 description 6

- 239000013078 crystal Substances 0.000 description 5

- 238000002347 injection Methods 0.000 description 5

- 239000007924 injection Substances 0.000 description 5

- 229910052749 magnesium Inorganic materials 0.000 description 5

- 238000004458 analytical method Methods 0.000 description 4

- 230000015572 biosynthetic process Effects 0.000 description 4

- 238000011156 evaluation Methods 0.000 description 4

- 230000006872 improvement Effects 0.000 description 4

- 230000003287 optical effect Effects 0.000 description 4

- 238000005530 etching Methods 0.000 description 3

- 229910021478 group 5 element Inorganic materials 0.000 description 3

- 150000002431 hydrogen Chemical class 0.000 description 3

- 238000005259 measurement Methods 0.000 description 3

- 229910052710 silicon Inorganic materials 0.000 description 3

- 230000005540 biological transmission Effects 0.000 description 2

- 150000001875 compounds Chemical class 0.000 description 2

- 239000002905 metal composite material Substances 0.000 description 2

- 238000005424 photoluminescence Methods 0.000 description 2

- 229910052725 zinc Inorganic materials 0.000 description 2

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 1

- 238000002441 X-ray diffraction Methods 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 229910021529 ammonia Inorganic materials 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 229910052790 beryllium Inorganic materials 0.000 description 1

- 229910052791 calcium Inorganic materials 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 238000011109 contamination Methods 0.000 description 1

- 239000013256 coordination polymer Substances 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 238000002474 experimental method Methods 0.000 description 1

- 238000000605 extraction Methods 0.000 description 1

- 239000000835 fiber Substances 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- 238000004020 luminiscence type Methods 0.000 description 1

- 229910052748 manganese Inorganic materials 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 238000001451 molecular beam epitaxy Methods 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 238000010926 purge Methods 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 229910052717 sulfur Inorganic materials 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 229910052718 tin Inorganic materials 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- 229910052726 zirconium Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/005—Processes

- H01L33/0062—Processes for devices with an active region comprising only III-V compounds

- H01L33/0066—Processes for devices with an active region comprising only III-V compounds with a substrate not being a III-V compound

- H01L33/007—Processes for devices with an active region comprising only III-V compounds with a substrate not being a III-V compound comprising nitride compounds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02367—Substrates

- H01L21/0237—Materials

- H01L21/0242—Crystalline insulating materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02367—Substrates

- H01L21/02433—Crystal orientation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02436—Intermediate layers between substrates and deposited layers

- H01L21/02439—Materials

- H01L21/02455—Group 13/15 materials

- H01L21/02458—Nitrides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02436—Intermediate layers between substrates and deposited layers

- H01L21/02494—Structure

- H01L21/02496—Layer structure

- H01L21/02505—Layer structure consisting of more than two layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02436—Intermediate layers between substrates and deposited layers

- H01L21/02494—Structure

- H01L21/02496—Layer structure

- H01L21/02505—Layer structure consisting of more than two layers

- H01L21/02507—Alternating layers, e.g. superlattice

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02538—Group 13/15 materials

- H01L21/0254—Nitrides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/0257—Doping during depositing

- H01L21/02573—Conductivity type

- H01L21/02579—P-type

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02612—Formation types

- H01L21/02617—Deposition types

- H01L21/0262—Reduction or decomposition of gaseous compounds, e.g. CVD

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/04—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a quantum effect structure or superlattice, e.g. tunnel junction

- H01L33/06—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a quantum effect structure or superlattice, e.g. tunnel junction within the light emitting region, e.g. quantum confinement structure or tunnel barrier

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/14—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a carrier transport control structure, e.g. highly-doped semiconductor layer or current-blocking structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/14—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a carrier transport control structure, e.g. highly-doped semiconductor layer or current-blocking structure

- H01L33/145—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a carrier transport control structure, e.g. highly-doped semiconductor layer or current-blocking structure with a current-blocking structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/26—Materials of the light emitting region

- H01L33/30—Materials of the light emitting region containing only elements of group III and group V of the periodic system

- H01L33/32—Materials of the light emitting region containing only elements of group III and group V of the periodic system containing nitrogen

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/26—Materials of the light emitting region

- H01L33/30—Materials of the light emitting region containing only elements of group III and group V of the periodic system

- H01L33/32—Materials of the light emitting region containing only elements of group III and group V of the periodic system containing nitrogen

- H01L33/325—Materials of the light emitting region containing only elements of group III and group V of the periodic system containing nitrogen characterised by the doping materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/0257—Doping during depositing

- H01L21/02573—Conductivity type

- H01L21/02576—N-type

Description

(1)発光波長が200〜350nmのIII族窒化物半導体発光素子において、

n型III族窒化物半導体層と、障壁層および前記障壁層のバンドギャップの小さい井戸層をこの順に交互にN層ずつ(但し、Nは整数である)積層してなるIII族窒化物半導体発光層と、AlNガイド層と、電子ブロック層と、p型III族窒化物半導体層とをこの順に有し、

前記電子ブロック層がp型のAlzGa1-zN(0.50≦z≦0.80)であり、

前記障壁層がn型のAlbGa1-bN(z+0.01≦b≦0.95)であること

を特徴とするIII族窒化物半導体発光素子。

前記III族窒化物半導体発光層における前記N層目の井戸層と、前記AlNガイド層との間に、Al組成比が前記障壁層以上前記AlNガイド層未満のファイナルバリア層を有し、該ファイナルバリア層の厚みが1.5nm以下である、前記(1)〜(3)のいずれかに記載のIII族窒化物半導体発光素子。

n型III族窒化物半導体層を形成する第1工程と、

前記n型III族窒化物半導体層上に障壁層および該障壁層のバンドギャップの小さい井戸層をこの順に交互にN層ずつ(但し、Nは整数である)積層してIII族窒化物半導体発光層を形成する第2工程と、

前記III族窒化物半導体発光層上にAlNガイド層を形成する第3工程と、

前記AlNガイド層上に電子ブロック層を形成する第4工程と、

前記電子ブロック層上にp型半導体層を形成する第5工程と、を含み、

前記電子ブロック層をp型のAlzGa1-zN(0.50≦z≦0.80)とし、

前記障壁層をn型のAlbGa1-bN(z+0.01≦b≦0.95)とすること

を特徴とするIII族窒化物半導体発光素子の製造方法。

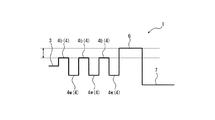

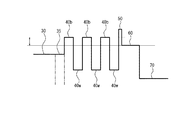

図2に示すように、本発明の一実施形態に従うIII族窒化物半導体発光素子100は、n型III族窒化物半導体層30と、障壁層40bおよび、障壁層40bよりもバンドギャップの小さい井戸層40wをこの順に交互にN層ずつ(但し、Nは整数である)積層してなるIII族窒化物半導体発光層40と、AlNガイド層50と、電子ブロック層60と、p型III族窒化物半導体層70と、をこの順に有する。本明細書において、障壁層40bのAl組成比をb、井戸層40wのAl組成比をw、電子ブロック層60のAl組成比をzと表記する。本発明によるIII族窒化物半導体発光素子100では、電子ブロック層60のAl組成比(z)よりも、障壁層40bのAl組成比(b)が大きい。以下、本明細書においてn型III族窒化物半導体層30を「n型層30」、III族窒化物半導体発光層40を「発光層40」、p型III族窒化物半導体層70を「p型層70」と、それぞれ略記する。

n型層30は、少なくともAlを含むIII族窒化物半導体層であり、III族窒化物半導体発光素子100におけるn型の半導体層として機能すれば一般的なn型半導体層を用いることができる。n型層30は、例えばAlGaN材料からなり、また、III族元素としてのAlとGaに対して5%以内の量のInを含んでいてもよい。n型層30には、n型のドーパント(不純物)がドープされ、n型ドーパントとしては、Si,Ge,Sn,S,O,Ti,Zr等を例示することができる。ドーパント濃度は、n型として機能することのできるドーパント濃度であれば特に限定されず、例えば1.0×1018atoms/cm3〜1.0×1020atoms/cm3とすることができる。また、n型層30のAl含有率は、特に制限はなく、一般的な範囲とすることができる。n型層30を単層または複数層からなる構造とする他、III族元素の組成比を結晶成長方向に組成傾斜させた組成傾斜層や超格子構造を含む構成することもできる。n型層30は、n側電極とのコンタクト部を形成するだけでなく、基板から発光層に至るまでに結晶性を高める機能を兼ねることができる。

なお、図2には図示しないが、発光層40とn型層30との間に、n型ガイド層35を設けても良い。n型ガイド層35はAlGaN材料を用いることが好ましく、そのAl組成比は、前記のn型層30のAl組成比以上、障壁層40bのAl組成比(b)以下とすることが好ましい。その厚さは3nm〜30nmとすることができる。また、n型ガイド層35には、n型層と同様にn型のドーパント(不純物)がドープされことが好ましいが、そのドーパント量はn型層よりも低いことが好ましい。

III族窒化物半導体発光素子100において、発光層40がn型層30に続いて設けられる。発光層40は、障壁層40bおよび、障壁層40bよりもバンドギャップの小さい井戸層40wをこの順に交互にN層ずつ(但し、Nは整数である)積層してなる。例えば、障壁層40bおよび井戸層40wとして、Al組成比の異なるAlGaN材料を用いることができる。障壁層40bおよび井戸層40wは、必要に応じて、In等のIII族元素を5%以内の組成比で導入し、AlGaInN材料等としてもよいが、III族元素としてはAlおよびGaのみを用いた三元系のAlGaN材料とすることがより好ましい。井戸層40wはn型およびi型のいずれとしてもよいが、障壁層40bはn型とする。電子濃度が増え、井戸層内の結晶欠陥を補償する効果があるためである。なお、発光層40は、障壁層40bおよび井戸層40wを繰り返し形成し、障壁層40bで挟み込んだ一般的な多重量子井戸(MQW:Multiple Quantum Well)構造から、p型の半導体層側の最後の障壁層を取り除いたものに相当すると言える。

障壁層40bとしてAlbGa1-bN材料を用い、井戸層40wとしてAlwGa1-wN材料を用いることができる。障壁層40bのAl組成比(b)を例えば0.51〜0.95、より好ましくは0.53〜0.85とすることができ、井戸層40wのAl組成比(w)を、例えば0.30〜0.80(但し、w<b)とすることができる。また、障壁層40bおよび井戸層40wのそれぞれの層数Nを、例えば1〜10の正の整数とすることができる。さらに、障壁層40bの厚みを3nm〜30nmとすることができ、井戸層40wの厚みを0.5nm〜5nmとすることができる。

そして、本発明者は、障壁層40bのAl組成比(b)を後述する電子ブロック層のAl組成比(z)よりも大きくし、z+0.01≦b≦0.95とすることにより、発光出力のさらなる向上が得られることを見出した。さらに、発光出力向上効果は確実なものとするためには、障壁層40bのAl組成比(b)の上限をz+0.2(b≦z+0.2)とすることが好ましく、z+0.17(b≦z+0.17)とすることがより好ましく、z+0.15(b≦z+0.15)とすることが特に好ましい。障壁層40bのAl組成比(b)をz+0.05≦b≦z+0.15とすることが特に好ましい。

図1Bのバンド構造と比べて、本発明の実施形態に従う図3Aでは、障壁層40bのAl組成比(b)の方が電子ブロック層60よりもバンドギャップを大きくする構成となっている。すなわち、障壁層40bのAl組成比(b)を電子ブロック層60(詳細は後述する)のAl組成比(z)よりも大きくし、z+0.01≦b≦0.95の関係を満足するようにしている。図3Aは、n型ガイド層35を障壁層40bと同じバンドギャップとした場合であり、図3Bはn型ガイド層35を障壁層40bとは異なり、n型層30と同じバンドギャップとした場合である。いずれも、障壁層40bのAl組成比(b)を電子ブロック層60のAl組成比(z)よりも大きくしている。

このような本発明による障壁層と電子ブロック層とでのバンドギャップの大小関係により、従来よりも優れた発光出力を有するIII族窒化物半導体発光素子を実現することができることを本発明者は実験的に確認した。本発明は理論に束縛されるものではないが、こうした効果が得られる理由について、本発明者は以下のとおり考えている。まず、DUV−LEDの材料として使われるAlGaN系の半導体材料は比較的大きなバンドギャップを有するため、低抵抗化が難しい。特にp型のAlGaN層ではホール濃度の向上が難しい。このため、電極部分ではコンタクト抵抗が増大し、素子のデバイス駆動には大きな順方向電圧Vfが必要となる。一方で、デバイス駆動のために大きな順方向電圧Vfが印加されるほど、キャリア濃度が高く拡散長も長い電子が、p型電子ブロック層にて比較的容易にオーバーフローすると考えられる。このとき、電子の注入効率が悪化する分、DUV−LEDの発光出力が低下する。しかし、障壁層のAl組成を高くすれば電子のオーバーフローを抑制する効果が得られるため、発光出力が向上すると考えられる。大きな順方向電圧Vfが必要となる200〜350nmの中でも、光の中心波長が300nm以下であれば、障壁層のAl組成を高くすることによる本発明の効果は特に大きい。一方で、中心波長が300nmを超える波長域では、中心波長が300nm以下の波長域に比べ、電子ブロック層のAl組成を低くして設けることができ、電子ブロック層でのホール注入効率向上の効果が得られやすい。この場合であっても、障壁層40wのAl組成を上げることによるオーバーフローの抑制効果は有効であり、300nm以下の波長域に比べれば小さいものの本発明の効果はある。障壁層のAl組成を高くすると、p型電子ブロック層に近い井戸層への電子濃度が下げられるためだとも考えられる。なお、p型電子ブロック層のAl組成を上げることでもオーバーフローを減らせる可能性は考えられるものの、この場合は結果的にホールの注入を減らす結果となり、光の中心波長が300nm以下ではかえって逆効果となると推察される。

発光層40に続き、AlNガイド層50が発光層40上に設けられる。AlNガイド層50は、最も好ましくはIII族元素のAl組成比を100%として形成したAlNからなる窒化物半導体層である。ただし、他のIII族元素(Ga等)が製造工程中に不可避に混入した場合や、変質時に発生するガスや変質の進行状況を考慮して、結果としてAl組成比が96%〜100%であれば、AlNガイド層50に含まれるものとする。AlNガイド層50の厚みは0.5nm以上2.0nm以下が好ましく、0.7nm以上1.7nm以下がより好ましい。AlNガイド層50は、アンドープ(i型)であることが好ましいが、Mgなどのp型ドーパントやSiなどのn型ドーパントを添加しても構わない。また、AlNガイド層50中の不純物濃度が均一である必要はなく、例えば、発光層40側とp型層70側との間で、不純物濃度が異なっていても良い。ドーパントを添加した際にはi型だけでなく、結果として一部もしくは全体がp型化、またはn型化してもよい。

ここで、III族窒化物半導体発光素子100は、発光層40におけるAlNガイド層50側のN層目の井戸層40wと、AlNガイド層50との間に、バンドギャップが障壁層40b以上かつAlNガイド層50未満のファイナルバリア層を更に有してもよい。ファイナルバリア層としてAlfGa1-fN材料を用いる場合、ファイナルバリア層のAl組成比(f)は、障壁層のAl組成比(b)に対しb≦f≦0.95であることが好ましい。この場合、ファイナルバリア層の厚みを1.5nm以下とし、0.1nm以上1.0nm以下と、従来技術で用いられるファイナルバリア層の厚みよりも非常に薄いことがより好ましい。前掲の特許文献2に記載されるキャリアガスの変更時における変質によってファイナルバリア層の一部がAlNガイド層となる場合、ファイナルバリア層の厚みが0.1nm以上であれば、変質の影響を受けない1原子層が残ることで、N層目(電子ブロック層60側)の井戸層40wの変質を避けることができる。

続いて、電子ブロック層60がAlNガイド層50上に隣接して設けられる。電子ブロック層60は一般的に、発光層として機能する量子井戸構造(MQW)とp型層(p型クラッド層またはp型コンタクト層)との間に設けることにより、電子を堰止めして、電子を発光層(MQWの場合には井戸層)内に注入して、電子の注入効率を高めるための層として用いられる。これは、発光層のAl組成比が高い場合には、p型層70のホール濃度が低いため、ホールを発光層に注入しにくく、一部の電子がp型層70側に流れてしまうところ、電子ブロック層60を設けることにより、こうした電子の流れを防止することができるからである。本実施形態でも、AlNガイド層50に隣接して設けられた電子ブロック層60は、上記したのと同様にp型層70側への電子の流れを防止することができ、電子の注入効率を高めることができる。

電子ブロック層60に続き設けられるp型層70は、正孔を発光層40に注入できる限りは、特に限定されず、一般的な構成とすることができ、Al組成比の異なるAlGaN材料を用いて、p型コンタクト層のみ、または、p型クラッド層およびその上のp型コンタクト層を含む複数層構造としてもよい(詳細を後述する)。また、p型層70にドープするp型ドーパントとしては、Mg,Zn,Ca,Be,Mn等を例示することができる。また、p型層70全体の平均ドーパント濃度は、p型として機能することのできるドーパント濃度であれば特に限定されず、例えば1.0×1018atoms/cm3〜5.0×1021atoms/cm3とすることができる。

以下に、図2に示した基板10、AlN層20、n型電極80およびp型電極90についてそれらの具体的な態様を例示的に説明するが、これらは種々の変形が可能である。既述のとおり、本発明に従う実施形態において、図2に示した基板10、AlN層20、n型電極80およびp型電極90は、本発明を何ら限定するものではない。

次に、本発明に従うIII族窒化物半導体発光素子100の製造方法の第1実施形態を説明する。第1実施形態に係る製造方法は、n型III族窒化物半導体層30(以下、n型層30)を形成する第1工程と、n型層30上に、障壁層40bおよび該障壁層40bよりもバンドギャップの小さい井戸層40wをこの順に交互にN層ずつ(但し、Nは整数である)積層してIII族窒化物半導体発光層40(以下、発光層40)を形成する第2工程と、発光層40上に、AlNガイド層50を形成する第3工程と、AlNガイド層50上に、電子ブロック層60を形成する第4工程と、電子ブロック層60上にp型III族窒化物半導体層70を形成する第5工程と、を含む。そして、電子ブロック層60をp型のAlzGa1-zN(0.50≦z≦0.80)とし、障壁層40bをn型のAlbGa1-bN(z+0.01≦b≦0.95)とすることについては先に述べたとおりであり、本発明による特に特徴的な事項である。

第2実施形態では、AlNガイド層50を発光層40上に直接には形成せず、第3工程において発光層40上にAl組成比が障壁層40b以上AlNガイド層50未満のAlGaN層を形成し、前記AlGaN層の変質によりAlNガイド層50を形成する以外は第1実施形態と同様である。電子ブロック層60を形成する前においてキャリアガスを窒素から水素へと切り替える際に、第3工程で形成したAlGaN層が成長時よりも窒素分圧の低いキャリアガス雰囲気(例えば水素を主成分とするキャリアガス雰囲気)に晒されることにより、表面からGaが抜けていく変質を生じる。その結果、表面側がAlGaN層からAlNガイド層50に転じ、発光層側がファイナルバリア層として残存する。AlGaN層の厚さやIII族元素の原料ガスの供給を止めて成長時よりも窒素分圧の低いキャリアガス雰囲気に晒される時間によって、前述のAlNガイド層50やファイナルバリア層の厚さを制御することができる。

サファイア基板(直径2インチ、厚さ:430μm、面方位:(0001)、m軸方向オフ角θ:0.5度)を用意した。次いで、MOCVD法により、上記サファイア基板上に中心膜厚0.60μm(平均膜厚0.61μm)のAlN層を成長させ、AlNテンプレート基板とした。その際、AlN層の成長温度は1300℃、チャンバ内の成長圧力は10Torrであり、V/III比が163となるようにアンモニアガスとTMAガスの成長ガス流量を設定した。V族元素ガス(NH3)の流量は200sccm、III族元素ガス(TMA)の流量は53sccmである。なお、AlN層の膜厚については、光干渉式膜厚測定機(ナノスペックM6100A;ナノメトリックス社製)を用いて、ウェーハ面内の中心を含む、等間隔に分散させた計25箇所の膜厚を測定した。

障壁層のAl組成比(b)を0.71とし、n型ガイド層のAl組成比を0.71とした以外は、実施例11と同様にしてIII族窒化物半導体発光素子を作製した。電子ブロック層のAl組成比(z)は0.68であり、障壁層のAl組成比(b)は電子ブロック層のAl組成比(z)よりも大きく、その差(b−z)は0.03である。

障壁層のAl組成比bを0.75とした以外は、実施例11と同様にしてIII族窒化物半導体発光素子を作製した。電子ブロック層のAl組成比(z)は0.68であり、障壁層のAl組成比(b)は電子ブロック層のAl組成比(z)よりも大きく、その差(b−z)は0.07である。

障壁層のAl組成比(b)を0.80とした以外は、実施例11と同様にしてIII族窒化物半導体発光素子を作製した。電子ブロック層のAl組成比(z)は0.68であり、障壁層のAl組成比(b)は電子ブロック層のAl組成比(z)よりも大きく、その差(b−z)は0.12である。

障壁層のAl組成比(b)を0.85とした以外は、実施例11と同様にしてIII族窒化物半導体発光素子を作製した。電子ブロック層のAl組成比(z)は0.68であり、障壁層のAl組成比(b)は電子ブロック層のAl組成比(z)よりも大きく、その差(b−z)は0.17である。

障壁層のAl組成比(b)を0.60とした以外は、実施例11と同様にしてIII族窒化物半導体発光素子を作製した。電子ブロック層のAl組成比(z)は0.68であり、障壁層のAl組成比(b)は電子ブロック層のAl組成比(z)よりも小さく、その差(b−z)は−0.08である。

障壁層のAl組成比(b)を0.65とした以外は、実施例1と同様にしてIII族窒化物半導体発光素子を作製した。電子ブロック層のAl組成比(z)は0.68であり、障壁層のAl組成比(b)は電子ブロック層のAl組成比(z)よりも小さく、その差(b−z)は−0.03である。

障壁層のAl組成比(b)を0.68とし、n型ガイド層のAl組成比を0.68とした以外は、実施例1と同様にしてIII族窒化物半導体発光素子を作製した。電子ブロック層のAl組成比(z)は0.68であり、障壁層のAl組成比(b)は電子ブロック層のAl組成比(z)と同じであるためその差(b−z)は0である。

障壁層のAl組成比(b)を0.65とし、電子ブロック層のAl組成比(z)を0.63とした以外は、実施例11と同様にしてIII族窒化物半導体発光素子を作製した。電子ブロック層のAl組成比(z)は0.63であり、障壁層のAl組成比(b)は電子ブロック層のAl組成比(z)よりも大きく、その差(b−z)は0.02である。

障壁層のAl組成比(b)を0.75とし、電子ブロック層のAl組成比(z)を0.63とした以外は、実施例11と同様にしてIII族窒化物半導体発光素子を作製した。電子ブロック層のAl組成比(z)は0.75であり、障壁層のAl組成比(b)は電子ブロック層のAl組成比(z)よりも大きく、その差(b−z)は0.12である。

障壁層のAl組成比(b)を0.80とし、電子ブロック層のAl組成比(z)を0.63とした以外は、実施例11と同様にしてIII族窒化物半導体発光素子を作製した。電子ブロック層のAl組成比(z)は0.80であり、障壁層のAl組成比(b)は電子ブロック層のAl組成比(z)よりも大きく、その差(b−z)は0.17である。

障壁層のAl組成比(b)を0.60とし、電子ブロック層のAl組成比(z)を0.63とした以外は、実施例1と同様にしてIII族窒化物半導体発光素子を作製した。電子ブロック層のAl組成比(z)は0.63であり、障壁層のAl組成比(b)は電子ブロック層のAl組成比(z)よりも小さく、その差(b−z)は−0.03である。

実施例11〜15,21〜23、比較例11〜13,21のそれぞれに対し、エピタキシャル成長により形成される各層の厚さは、光干渉式膜厚測定器を用いて測定した。

また、障壁層やブロック層を含め各層の厚さが数nm〜数十nmと薄い層は、透過型電子顕微鏡による各層の断面観察でのTEM−EDSを用いて各層厚さとAl組成比を測定した。

また、厚さが十分厚い層(例えば1μm以上)については、フォトルミネッセンス測定による発光波長(バンドギャップエネルギー)から、対象とする層のAl組成比を確認した。

実施例11〜15,21〜23、比較例11〜13,21のそれぞれに対し、Siフォトダイオード(S1227-1010BQ、浜松ホトニクス社製)を用いて、電流10mAでの発光出力を測定した。さらに、ファイバ光学分光器(USB2000+、Ocean Photonics社製)を用いて電流10mAでの発光波長も測定した。

なお、実施例21〜23および比較例21は、電子ブロック層のAl組成zを0.63とした場合である。電子ブロック層のAl組成zが0.68の場合であり、かつ、b−zが同じである場合に比べてこれらの発光出力は劣るものの、順方向電圧が低くなるメリットがあり、順方向電圧を低くすることが重要な用途ではAl組成zを小さくすることが好ましい場合もある。このように電子ブロック層のAl組成zは用途に応じて適宜設定されるが、zの値によらず、b−zの値が本発明の範囲となる場合に、発光出力が大きくなる傾向となることが示された。

10A 基板の主面

20 AlN層

30 n型層

40 発光層

40b 障壁層

40w 井戸層

50 AlNガイド層

60 電子ブロック層

70 p型層

80 n型電極

90 p型電極

100 III族窒化物半導体発光素子

Claims (4)

- 発光波長が200〜350nmのIII族窒化物半導体発光素子において、

n型III族窒化物半導体層と、障壁層および前記障壁層のバンドギャップの小さい井戸層をこの順に交互にN層ずつ(但し、Nは整数である)積層してなるIII族窒化物半導体発光層と、AlNガイド層と、電子ブロック層と、p型III族窒化物半導体層とをこの順に有し、

前記AlNガイド層の厚さが0.5nm以上2.0nm以下であり、

前記電子ブロック層がp型のAlzGa1-zN(0.50≦z≦0.80)であり、

前記障壁層がn型のAlbGa1-bN(z+0.01≦b≦0.95)であること

を特徴とするIII族窒化物半導体発光素子。 - 前記障壁層のAl組成比(b)が、b≦z+0.20である、請求項1に記載のIII族窒化物半導体発光素子。

- 前記III族窒化物半導体発光層における前記N層目の井戸層と、前記AlNガイド層とが接する、または、

前記III族窒化物半導体発光層における前記N層目の井戸層と、前記AlNガイド層との間に、Al組成比が前記障壁層以上前記AlNガイド層未満のファイナルバリア層を有し、該ファイナルバリア層の厚みが1.5nm以下である、請求項1または2に記載のIII族窒化物半導体発光素子。 - 発光波長が200〜350nmのIII族窒化物半導体発光素子の製造方法であって、

n型III族窒化物半導体層を形成する第1工程と、

前記n型III族窒化物半導体層上に障壁層および該障壁層のバンドギャップの小さい井戸層をこの順に交互にN層ずつ(但し、Nは整数である)積層してIII族窒化物半導体発光層を形成する第2工程と、

前記III族窒化物半導体発光層上に厚さ0.5nm以上2.0nm以下のAlNガイド層を形成する第3工程と、

前記AlNガイド層上に電子ブロック層を形成する第4工程と、

前記電子ブロック層上にp型半導体層を形成する第5工程と、を含み、

前記電子ブロック層をp型のAlzGa1-zN(0.50≦z≦0.80)とし、

前記障壁層をn型のAlbGa1-bN(z+0.01≦b≦0.95)とすること

を特徴とするIII族窒化物半導体発光素子の製造方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| PCT/JP2019/042891 WO2020095826A1 (ja) | 2018-11-05 | 2019-10-31 | Iii族窒化物半導体発光素子およびその製造方法 |

| KR1020217010691A KR20210083255A (ko) | 2018-11-05 | 2019-10-31 | Iii족 질화물 반도체 발광소자 및 그 제조 방법 |

| US17/283,544 US11984535B2 (en) | 2018-11-05 | 2019-10-31 | III-nitride semiconductor light-emitting device comprising barrier layers and well layers and method of producing the same |

| TW108139844A TWI734243B (zh) | 2018-11-05 | 2019-11-04 | Iii族氮化物半導體發光元件及其製造方法 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2018208392 | 2018-11-05 | ||

| JP2018208392 | 2018-11-05 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2020077874A JP2020077874A (ja) | 2020-05-21 |

| JP6766243B2 true JP6766243B2 (ja) | 2020-10-07 |

Family

ID=70724482

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019198185A Active JP6766243B2 (ja) | 2018-11-05 | 2019-10-31 | Iii族窒化物半導体発光素子およびその製造方法 |

Country Status (5)

| Country | Link |

|---|---|

| EP (1) | EP3879583A4 (ja) |

| JP (1) | JP6766243B2 (ja) |

| KR (1) | KR20210083255A (ja) |

| CN (1) | CN112970124A (ja) |

| TW (1) | TWI734243B (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6698925B1 (ja) | 2019-08-06 | 2020-05-27 | 日機装株式会社 | 窒化物半導体発光素子 |

| JP7141425B2 (ja) * | 2020-04-28 | 2022-09-22 | 日機装株式会社 | 窒化物半導体発光素子 |

| CN116154059A (zh) * | 2023-04-04 | 2023-05-23 | 江西兆驰半导体有限公司 | 氮化镓发光二极管外延结构、led及其制备方法 |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3555727B2 (ja) * | 1997-10-06 | 2004-08-18 | シャープ株式会社 | 半導体レーザ素子 |

| JP3279266B2 (ja) * | 1998-09-11 | 2002-04-30 | 日本電気株式会社 | 窒化ガリウム系半導体発光素子 |

| JP2002314205A (ja) * | 2001-04-19 | 2002-10-25 | Sharp Corp | 窒化物半導体発光素子ならびにそれを用いた光学装置および発光装置 |

| WO2003041234A1 (fr) * | 2001-11-05 | 2003-05-15 | Nichia Corporation | Element semi-conducteur |

| US7649195B2 (en) * | 2007-06-12 | 2010-01-19 | Seoul Opto Device Co., Ltd. | Light emitting diode having active region of multi quantum well structure |

| JP5641173B2 (ja) * | 2009-02-27 | 2014-12-17 | 独立行政法人理化学研究所 | 光半導体素子及びその製造方法 |

| KR102042181B1 (ko) * | 2012-10-22 | 2019-11-07 | 엘지이노텍 주식회사 | 발광소자 |

| JP6466653B2 (ja) | 2013-05-17 | 2019-02-06 | スタンレー電気株式会社 | 窒化物半導体発光素子、および窒化物半導体ウェーハ |

| KR20150039475A (ko) * | 2013-10-02 | 2015-04-10 | 엘지이노텍 주식회사 | 발광소자 |

| KR102268109B1 (ko) * | 2014-12-22 | 2021-06-22 | 엘지이노텍 주식회사 | 발광 소자 및 이를 구비한 발광 소자 패키지 |

| JP5953447B1 (ja) * | 2015-02-05 | 2016-07-20 | Dowaエレクトロニクス株式会社 | Iii族窒化物半導体発光素子およびその製造方法 |

| JP6092961B2 (ja) * | 2015-07-30 | 2017-03-08 | Dowaエレクトロニクス株式会社 | Iii族窒化物半導体発光素子およびその製造方法 |

| CN108140695B (zh) * | 2015-09-17 | 2021-02-09 | 晶体公司 | 包含二维空穴气体的紫外发光器件 |

| JP6456414B2 (ja) * | 2017-02-01 | 2019-01-23 | 日機装株式会社 | 半導体発光素子 |

| CN110462851B (zh) * | 2017-03-27 | 2022-07-19 | 同和电子科技有限公司 | Iii族氮化物半导体发光元件及其制造方法 |

| JP6379265B1 (ja) * | 2017-09-12 | 2018-08-22 | 日機装株式会社 | 窒化物半導体発光素子及び窒化物半導体発光素子の製造方法 |

-

2019

- 2019-10-31 CN CN201980072339.3A patent/CN112970124A/zh active Pending

- 2019-10-31 KR KR1020217010691A patent/KR20210083255A/ko not_active Application Discontinuation

- 2019-10-31 JP JP2019198185A patent/JP6766243B2/ja active Active

- 2019-10-31 EP EP19881858.5A patent/EP3879583A4/en active Pending

- 2019-11-04 TW TW108139844A patent/TWI734243B/zh active

Also Published As

| Publication number | Publication date |

|---|---|

| KR20210083255A (ko) | 2021-07-06 |

| CN112970124A (zh) | 2021-06-15 |

| EP3879583A1 (en) | 2021-09-15 |

| JP2020077874A (ja) | 2020-05-21 |

| TWI734243B (zh) | 2021-07-21 |

| TW202036930A (zh) | 2020-10-01 |

| EP3879583A4 (en) | 2022-08-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US11024769B2 (en) | Group III nitride semiconductor light-emitting element and method of manufacturing same | |

| TWI683448B (zh) | Iii族氮化物半導體發光元件及其製造方法 | |

| JP6001756B2 (ja) | Iii族窒化物半導体発光素子の製造方法およびiii族窒化物半導体発光素子 | |

| JP2016171127A (ja) | Iii族窒化物半導体発光素子およびその製造方法 | |

| JP6654731B1 (ja) | Iii族窒化物半導体発光素子およびその製造方法 | |

| JP6766243B2 (ja) | Iii族窒化物半導体発光素子およびその製造方法 | |

| JP6908422B2 (ja) | Iii族窒化物半導体発光素子およびその製造方法 | |

| TWI722718B (zh) | Iii族氮化物半導體發光元件及其製造方法 | |

| WO2016092804A1 (ja) | Iii族窒化物半導体発光素子の製造方法およびiii族窒化物半導体発光素子 | |

| WO2020095826A1 (ja) | Iii族窒化物半導体発光素子およびその製造方法 | |

| WO2020122137A1 (ja) | Iii族窒化物半導体発光素子及びその製造方法 | |

| JP6084196B2 (ja) | Iii族窒化物半導体発光素子の製造方法およびiii族窒化物半導体発光素子 | |

| US11984535B2 (en) | III-nitride semiconductor light-emitting device comprising barrier layers and well layers and method of producing the same | |

| WO2016092822A1 (ja) | Iii族窒化物半導体発光素子の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20191031 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20200128 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200326 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20200901 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20200916 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6766243 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |