JP6722980B2 - 表示装置および発光装置、並びに電子機器 - Google Patents

表示装置および発光装置、並びに電子機器 Download PDFInfo

- Publication number

- JP6722980B2 JP6722980B2 JP2015094500A JP2015094500A JP6722980B2 JP 6722980 B2 JP6722980 B2 JP 6722980B2 JP 2015094500 A JP2015094500 A JP 2015094500A JP 2015094500 A JP2015094500 A JP 2015094500A JP 6722980 B2 JP6722980 B2 JP 6722980B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- electrode

- display device

- substrate

- insulating film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/125—Active-matrix OLED [AMOLED] displays including organic TFTs [OTFT]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6755—Oxide semiconductors, e.g. zinc oxide, copper aluminium oxide or cadmium stannate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/80—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/421—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer

- H10D86/423—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer comprising semiconductor materials not belonging to the Group IV, e.g. InGaZnO

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K50/00—Organic light-emitting devices

- H10K50/80—Constructional details

- H10K50/84—Passivation; Containers; Encapsulations

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K50/00—Organic light-emitting devices

- H10K50/80—Constructional details

- H10K50/84—Passivation; Containers; Encapsulations

- H10K50/842—Containers

- H10K50/8426—Peripheral sealing arrangements, e.g. adhesives, sealants

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K50/00—Organic light-emitting devices

- H10K50/80—Constructional details

- H10K50/84—Passivation; Containers; Encapsulations

- H10K50/844—Encapsulations

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/121—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements

- H10K59/1213—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements the pixel elements being TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/123—Connection of the pixel electrodes to the thin film transistors [TFT]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/124—Insulating layers formed between TFT elements and OLED elements

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/131—Interconnections, e.g. wiring lines or terminals

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/80—Constructional details

- H10K59/87—Passivation; Containers; Encapsulations

- H10K59/871—Self-supporting sealing arrangements

- H10K59/8722—Peripheral sealing arrangements, e.g. adhesives, sealants

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/40—OLEDs integrated with touch screens

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/80—Constructional details

- H10K59/87—Passivation; Containers; Encapsulations

- H10K59/873—Encapsulations

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Optics & Photonics (AREA)

- Geometry (AREA)

- Electroluminescent Light Sources (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

Description

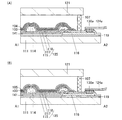

本発明の一態様の表示装置100の構成例および作製方法例について、図1乃至図24を用いて説明する。本実施の形態では、パッシブマトリクス型の表示装置100について説明する。図1(A)は外部電極124aが接続された表示装置100の斜視図である。また、図1(B)は、図1(A)にA1−A2の一点鎖線で示す部位の断面図である。なお、本明細書に開示する表示装置100は、表示素子として発光素子を用いた表示装置を例示している。また、本発明の一態様の表示装置100として、トップエミッション構造(上面射出構造)の表示装置を例示する。なお、表示装置100をボトムエミッション構造(下面射出構造)、またはデュアルエミッション構造(両面射出構造)の表示装置とすることも可能である。

本発明の一態様の表示装置100の構成例について、図1および図2を用いて説明する。本実施の形態に示す表示装置100は、表示領域131を有する。また、表示領域131は、複数の画素130を有する。一つの画素130は、少なくとも一つの発光素子125を有する。

基板111および基板121としては、特定のものに限定されることはない。その基板の一例としては、半導体基板(例えば単結晶基板またはシリコン基板)、SOI基板、ガラス基板、石英基板、有機樹脂基板、金属基板、可撓性を有する基板、貼り合わせフィルム、繊維状の材料を含む紙、または基材フィルムなどがある。または、有機樹脂材料や、可撓性を有する程度の厚さのガラス材料、または可撓性を有する程度の厚さの金属材料(合金材料を含む)などを用いることができる。

絶縁膜119、絶縁膜141は、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルなどの酸化物材料や、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウムなどの窒化物材料などを、単層または多層で形成することができる。例えば、絶縁膜119を、酸化シリコンと窒化シリコンを積層した2層構造としてもよいし、上記材料を組み合わせた5層構造としてもよい。絶縁膜119は、スパッタリング法やCVD法、熱酸化法、塗布法、印刷法等を用いて形成することが可能である。

電極116は、導電性を有する材料を用いて形成することができる。例えば、アルミニウム、クロム、銅、銀、金、白金、タンタル、ニッケル、チタン、モリブデン、タングステン、ハフニウム、バナジウム、ニオブ、マンガン、マグネシウム、ジルコニウム、ベリリウム等から選ばれた金属元素、上述した金属元素を成分とする合金、または上述した金属元素を組み合わせた合金などを用いることができる。また、リン等の不純物元素を含有させた多結晶シリコンに代表される半導体、ニッケルシリサイドなどのシリサイドを用いてもよい。導電膜の形成方法は特に限定されず、蒸着法、CVD法、スパッタリング法、スピンコート法などの各種形成方法を用いることができる。

電極115は、後に形成されるEL層117が発する光を効率よく反射する導電性材料を用いて形成することが好ましい。なお、電極115は単層に限らず、複数層の積層構造としてもよい。例えば、電極115を陽極として用いる場合、EL層117と接する膜を、インジウム錫酸化物などのEL層117よりも仕事関数が大きく透光性を有する膜とし、その膜に接して反射率の高い膜(アルミニウム、アルミニウムを含む合金、または銀など)を設けてもよい。

絶縁膜114は、隣接する電極118間の電気的ショートを防止するために設ける。また、後述するEL層117の形成にメタルマスクを用いる場合、メタルマスクが発光素子125を形成する領域に接触しないようにする機能も有する。絶縁膜114は、エポキシ樹脂、アクリル樹脂、イミド樹脂などの有機樹脂材料や、酸化シリコンなどの無機材料で形成することができる。絶縁膜114は、その側壁がテーパーまたは連続した曲率を持って形成される傾斜面となるように形成することが好ましい。絶縁膜114の側壁をこのような形状とすることで、後に形成されるEL層117や電極118の被覆性を良好なものとすることができる。なお、本明細書において、絶縁膜114の表面のうち、基板111の表面と平行でない面をすべて絶縁膜114の側面という。

EL層117の構成については、実施の形態7で説明する。

本実施の形態では電極118を陰極として用いる。電極118は、後述するEL層117に電子を注入できる仕事関数の小さい材料を用いて形成することが好ましい。また、仕事関数の小さい金属単体ではなく、仕事関数の小さいアルカリ金属、またはアルカリ土類金属を数nm形成した膜を緩衝膜として形成し、その上にアルミニウムなどの金属材料を用いて形成してもよい。また、緩衝膜として、アルカリ土類金属の酸化物、ハロゲン化物、または、マグネシウム−銀等の合金を用いることもできる。なお、ボトムエミッション構造の表示装置の場合、電極118は反射性を有することで、光取り出し効率を高めることができる。

保護膜103は透湿性の低い膜で形成される。保護膜103は、表示装置100の外部からEL層117への水の拡散を防ぐバリア膜としての機能を有する。また、保護膜103は、表示装置100内の構成部材からEL層117への水の拡散を防ぐバリア膜としての機能を有する。このため、水による発光素子125の劣化を防ぐことができる。

接着部120としては、光硬化型の接着剤、反応硬化型接着剤、熱硬化型接着剤、または嫌気型接着剤を用いることができる。例えば、エポキシ樹脂、アクリル樹脂、シリコーン樹脂、フェノール樹脂、イミド樹脂、PVC(ポリビニルクロライド)樹脂、PVB(ポリビニルブチラル)樹脂、EVA(エチレンビニルアセテート)樹脂等を用いることができる。特に、エポキシ樹脂等の透湿性が低い材料が好ましい。また、二液混合型の樹脂を用いてもよい。また、接着シート等を用いてもよい。

異方性導電接続部138aは、様々な異方性導電フィルム(ACF:Anisotropic Conductive Film)や、異方性導電ペースト(ACP:Anisotropic Conductive Paste)などを用いて形成することができる。

図3(A)は、表示装置100の斜視図である。また、図3(B)は、図3(A)にA1−A2の一点鎖線で示す部位の断面図である。本実施の形態に示す表示装置100は、表示領域131を有する。また、表示領域131の外側に閉ループ状のシール材107を有する。

シール材107としては、熱硬化樹脂、または光硬化樹脂などの有機樹脂や、低融点ガラス(フリットガラスともいう)などを用いることができる。また、シール材107に乾燥剤が含まれていても良い。例えば、アルカリ土類金属の酸化物(酸化カルシウムや酸化バリウム等)のように、化学吸着によって水分を吸着する物質を、シール材107に分散させることができる。その他の乾燥剤として、ゼオライトやシリカゲル等のように、物理吸着によって水分を吸着する物質を用いてもよい。乾燥剤が含まれていると、封止領域内の水などを低減し、発光素子125の信頼性が向上するため好ましい。シール材107として低融点ガラスを用いることで、表示装置100の外部に存在する水が、EL層117に拡散することを防ぐことが可能である。この結果、表示装置100の部分的な輝度の低下を防ぐことが可能である。また、表示装置100において、非発光領域が生じることを防ぐことができる。

本実施の形態に示す表示装置100は、基板121において着色膜を有してもよい。または、本実施の形態に示す表示装置100は、基板121においてタッチセンサを有してもよい。図5および図6は、基板121において、着色膜およびタッチセンサを有する表示装置100の断面図である。

ここで、カラー表示を実現するための画素構成の一例を、図7を用いて説明しておく。図7(A)、図7(B)、および図7(C)は、図1(A)の表示領域131中に示した領域170を拡大した平面図である。

図8(A)に示す表示装置100は、基板111および基板121がシール材107で固着されている点が、図5および図6に示す表示装置と異なる。また、表示装置100において、基板111、基板121、およびシール材107で囲まれる封止領域内が中空構造である。封止領域内には、希ガスまたは窒素ガスなどの不活性ガスが充填されていてもよい。または、封止領域内を、減圧雰囲気とすることができる。これらの結果、封止領域内における水などを低減することが可能であり、発光素子125の信頼性を高めることが可能である。

本実施の形態に示す表示装置100は、接着部120およびシール材107を用いて、基板111および基板121が固着されてもよい。図10に示す表示装置100は、接着部120およびシール材107を用いて、基板111および基板121が固着されている。

本実施の形態に示す表示装置100は、基板111の代わりに可撓性を有する基板を用いてもよい。また、本実施の形態に示す表示装置100は、基板121の代わりに可撓性を有する基板を用いてもよい。図11(A)に示す表示装置100は、接着部112によって、可撓性を有する基板111aが絶縁膜119に固着されている。また、接着部120によって、可撓性を有する基板121aが保護膜103に固着されている。また、図11(B)に示す表示装置100は、可撓性を有する基板121aにおいて、絶縁膜129、タッチセンサ271、絶縁膜275、遮光膜264、着色膜266、および保護膜267を有する。また、接着部122によって、可撓性を有する基板121aが絶縁膜129に固着されている。

可撓性を有する基板111a、121aの厚さは、10μm以上200μm以下が好ましく、20μm以上50μm以下がより好ましい。この結果、可撓性を有し、耐衝撃性に優れ、破損しにくい表示装置を作製することができる。

次に、図12乃至図16を用いて、表示装置100の作製方法を説明する。なお、図12乃至図16は、図1中のA1−A2の一点鎖線で示す部位の断面に相当する。はじめに、発光素子を有する素子層を備えた基板111の作製方法について説明する。

基板111上に絶縁膜119を形成する。絶縁膜119は、基板101などからの不純物元素の拡散を防止または低減することができる。絶縁膜119の厚さは、好ましくは30nm以上2μm以下、より好ましくは50nm以上1μm以下とすればよい。本実施の形態では、絶縁膜119として、基板101側から、厚さ600nmの酸化窒化シリコン、厚さ200nmの窒化シリコン、厚さ200nmの酸化窒化シリコン、厚さ140nmの窒化酸化シリコン、厚さ100nmの酸化窒化シリコンの積層膜をプラズマCVD法により形成する。

次に、絶縁膜119上に電極116を形成する(図12(A)参照)。まず、スパッタリング法により二層のモリブデンの間にアルミニウムを挟んだ三層の金属膜を形成する。続いて、金属膜上にレジストマスクを形成し、該レジストマスクを用いて、金属膜を所望の形状にエッチングして、電極116を形成することができる。レジストマスクの形成は、リソグラフィ法、印刷法、インクジェット法等を適宜用いて行うことができる。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

次に、絶縁膜119および電極116上に、開口128、132aを有する絶縁膜141を形成する(図12(B)参照)。まず、プラズマCVD法により酸化窒化シリコンで形成される絶縁膜を形成する。

次に、絶縁膜141上に電極115を形成する(図12(C)参照)。電極115は、電極116と同様の材料および方法で形成することができる。ここでは、電極115となる金属膜をスパッタリング法を用いて形成する。次に、金属膜上にレジストマスクを形成し、該レジストマスクを用いて、金属膜の一部を選択的に除去し、電極115を形成する。金属膜のエッチングは、ドライエッチング法でもウェットエッチング法でもよく、両方を用いてもよい。本実施の形態では、電極115と電極116は、開口128で電気的に接続される。

次に、絶縁膜114を形成する(図12(D)参照)。本実施の形態では、絶縁膜114を感光性の有機樹脂材料を用いて塗布法で形成し、所望の形状に加工することにより形成する。本実施の形態では、絶縁膜114を、感光性を有するポリイミド樹脂を用いて形成する。

次に、EL層117を電極115および絶縁膜114上に形成する。

次に、電極118をEL層117上に形成する。本実施の形態では、電極118としてマグネシウムと銀の合金を用いる。電極118は、蒸着法、スパッタリング法等で形成することができる(図12(E)参照)。

次に、保護膜103を、絶縁膜114、EL層117、および電極118の上に形成する(図13(A)参照)。この結果、絶縁膜114、EL層117、および電極118の露出部を覆う保護膜103を形成することができる。本実施の形態では、スパッタリングターゲットとして、In:Ga:Zn=1:4:5の原子数比のIn−Ga−Zn酸化物を用いたスパッタリング法を用いて、保護膜103として酸化物半導体膜を形成する。

次に、素子層171と基板121を、接着部120を介して貼り合せる(図13(B)参照。)。

次に、開口132aに異方性導電接続部138aを形成し、異方性導電接続部138a上に、表示装置100に電力や信号を入力するための外部電極124aを形成する(図13(C)参照。)。外部電極124aは複数の電極を有する。また、外部電極124aが有する少なくとも1つの電極が、異方性導電接続部138aを介して電極116と電気的に接続することで、表示装置100に電力や信号を入力することが可能となる。

次に、図5に示すような、タッチセンサおよび着色膜を有する表示装置100の作製方法について説明する。はじめに、タッチセンサおよび着色膜を有する素子層を備えた基板121の作製方法について説明する。

基板121上に絶縁膜129を形成する。絶縁膜129は、絶縁膜119と同様の材料および方法で形成することができる。本実施の形態では、絶縁膜129として、基板102側から、厚さ200nmの酸化窒化シリコン膜、厚さ140nmの窒化酸化シリコン膜、厚さ100nmの酸化窒化シリコン膜の積層膜をプラズマCVD法により形成する。

次に、電極272を絶縁膜129上に形成する。電極272は、絶縁膜129上に透光性を有する導電膜を形成し、該導電膜の一部を選択的にエッチングして形成することができる。透光性を有する導電膜は、例えば、前述の透光性を有する導電性材料用いて形成することができる。本実施の形態では、インジウム錫酸化物膜を用いて電極272を形成する。

次に、電極272上に、絶縁膜273を形成する(図14(A)参照)。本実施の形態では、絶縁膜273としてプラズマCVD法により酸化窒化シリコン膜を形成する。

次に、絶縁膜273上に電極274を形成する。電極274は、絶縁膜273上に透光性を有する導電膜を形成し、該導電膜の一部を選択的にエッチングして形成することができる。本実施の形態では、インジウム錫酸化物を用いて電極274を形成する。以上の工程により、タッチセンサ271を形成することができる。

次に、電極274上に、絶縁膜275を形成する(図14(B)参照)。本実施の形態では、絶縁膜275としてプラズマCVD法により酸化窒化シリコン膜を形成する。ただし、絶縁膜275は、必ずしも設ける必要はなく、絶縁膜275を形成しない構造としてもよい。

次に、絶縁膜275上に、遮光膜264を形成する。遮光膜264は隣接する表示素子からの光を遮光し、隣接する表示素子間における混色を抑制する。また、着色膜266の端部と遮光膜264の端部が重なるように設けることにより、光漏れを抑制することができる。遮光膜264は、単層構造であっても2層以上の積層構造であってもよい。遮光膜264に用いることができる材料として、例えば、クロム、チタン、またはニッケルなどを含む金属材料、例えば、クロム、チタン、またはニッケルなどを含む酸化物材料、金属材料や顔料や染料を含む樹脂材料などが挙げられる。

次に、絶縁膜275上に、着色膜266を形成する(図14(C)参照)。前述したように、着色膜は特定の波長帯域の光を透過する膜である。例えば、赤色の波長帯域の光を透過する赤色(R)のカラーフィルタ、緑色の波長帯域の光を透過する緑色(G)のカラーフィルタ、青色の波長帯域の光を透過する青色(B)のカラーフィルタなどを用いることができる。着色膜266は、様々な材料を用いて、印刷法、インクジェット法、フォトリソグラフィ法を用いて、それぞれ所望の位置に形成する。この時、着色膜266の一部が遮光膜264と重なるように設けることが好ましい。画素毎に着色膜266の色を変えることで、カラー表示を行うことができる。

次に、遮光膜264および着色膜266上に保護膜267を形成する(図14(D)参照)。

次に、素子層171が設けられた基板111と素子層181が設けられた基板121を、接着部120を介して貼り合せる。この時、素子層171に含まれる発光素子125と、素子層181に含まれる着色膜266が向かい合うように配置する。

次に、図11(B)に示すような、可撓性を有する基板を用い、且つタッチセンサおよび着色膜を有する表示装置100の作製方法について説明する。

まず、基板101(「素子形成基板」ともいう。)上に剥離膜113を形成する(図15(A)参照)。基板101としては、ガラス基板、石英基板、サファイア基板、セラミック基板、金属基板、半導体基板などを用いることができる。また、本実施の形態の処理温度に耐えうる耐熱性を有するプラスチック基板を用いてもよい。その基板の一例としては、半導体基板(例えば単結晶基板またはシリコン基板)、SOI基板、ガラス基板、石英基板、プラスチック基板、金属基板、ステンレス・スチル基板、ステンレス・スチル・ホイルを有する基板、タングステン基板、タングステン・ホイルを有する基板、などがある。ガラス基板の一例としては、バリウムホウケイ酸ガラス、アルミノホウケイ酸ガラス、またはソーダライムガラスなどがある。

次に、上記した<表示装置の作製方法2>と同様の工程を用いて、剥離膜123上に、素子層181を形成する(図15(D)参照。)。

次に、素子層171を有する基板101と素子層181を有する基板102を、接着部120を介して貼り合せる。この時、素子層171に含まれる発光素子125と、素子層181に含まれる着色膜266が向かい合うように配置する(図16(A)参照。)。

次に、素子層171が設けられた基板101を、剥離膜113とともに絶縁膜119から剥離する(図16(B)参照)。剥離方法としては、機械的な力を加えること(人間の手や治具で引き剥がす処理や、ローラーを回転させながら分離する処理、超音波等)を用いて行えばよい。たとえば、剥離膜113に鋭利な刃物またはレーザー光照射等で切り込みをいれ、その切り込みに水を注入する。毛細管現象により水が剥離膜113と基板101の間にしみこむことにより、基板101を容易に剥離することができる。

次に、接着部112を介して基板111aを絶縁膜119に貼り合わせる(図16(C)参照)。

次に、素子層181が設けられた基板102を、剥離膜123とともに絶縁膜129から剥離する(図17(A)参照)。

次に、接着部122を介して、基板121aを絶縁膜129に貼り合わせる(図17(B)参照)。

次に、開口132aに異方性導電接続部138aを形成し、異方性導電接続部138a上に、表示装置100に電力や信号を入力するための外部電極124aを形成する。

本実施の形態では、上記実施の形態に示した表示装置100と異なる構成を有する表示装置200について、図18を用いて説明する。本実施の形態では、アクティブマトリクス型の表示装置200について説明する。図18(A)は表示装置200の上面図であり、図18(B)は、図18(A)中にA3−A4の一点鎖線で示す部位の断面図である。

本実施の形態に示す表示装置200は、表示領域231と、駆動回路251を有する。また、表示装置200は、電極115、EL層117、電極118を含む発光素子125と、電極116を有する。発光素子125は、表示領域231中に複数形成されている。また、各発光素子125には、発光素子125の発光量を制御するトランジスタ232が接続されている。

図20(A)は、表示装置200の斜視図である。また、図20(B)は、図20(A)にA1−A2の一点鎖線で示す部位の断面図である。本実施の形態に示す表示装置200は、表示領域231および駆動回路251を有する。また、表示領域231の外側に閉ループ状のシール材107を有する。

本実施の形態に示す表示装置200は、基板121において着色膜を有してもよい。または、本実施の形態に示す表示装置200は、基板121においてタッチセンサを有してもよい。図22および図23は、基板121において、着色膜およびタッチセンサを有する表示装置200の断面図である。

図24(A)に示す表示装置200は、基板111および基板121がシール材107で固着されている点が、図22および図23に示す表示装置200と異なる。また、表示装置200において、基板111、基板121、およびシール材107で囲まれる封止領域内が中空構造である。封止領域内には、希ガスまたは窒素ガスなどの不活性ガスが充填されていてもよい。または、封止領域内を、減圧雰囲気とすることができる。これらの結果、封止領域内における水などを低減することが可能であり、発光素子125の信頼性を高めることが可能である。

本実施の形態に示す表示装置200は、接着部120およびシール材107を用いて、基板111および基板121が固着されていてもよい。図26に示す表示装置200は、接着部120およびシール材107を用いて、基板111および基板121が固着されている。

本実施の形態に示す表示装置200は、基板111の代わりに可撓性を有する基板を用いてもよい。また、本実施の形態に示す表示装置200は、基板121の代わりに可撓性を有する基板を用いてもよい。図27(A)に示す表示装置200は、接着部112によって、可撓性を有する基板111aが絶縁膜205に固着されている。また、接着部120によって、可撓性を有する基板121aが保護膜103に固着されている。また、図27(B)に示す表示装置200は、可撓性を有する基板121aにおいて、絶縁膜129、タッチセンサ271、絶縁膜275、遮光膜264、着色膜266、および保護膜267を有する。また、接着部122によって、可撓性を有する基板121aが絶縁膜129に固着されている。

本実施の形態では、表示装置200のより具体的な構成例について、図28を用いて説明する。図28(A)は、表示装置200の構成例を説明するためのブロック図である。

また、図28(B)に示す画素回路134は、トランジスタ431と、容量素子233と、トランジスタ232と、トランジスタ434と、を有する。また、画素回路134は、発光素子125と電気的に接続されている。

図28(C)に示す画素回路134は、トランジスタ431と、容量素子233と、を有する。また、画素回路134は、液晶素子432と電気的に接続されている。

本発明の一態様の表示装置は、様々な形態を用いること、または様々な表示素子を有することが出来る。表示素子としては、例えば、EL(エレクトロルミネッセンス)素子(有機物および無機物を含むEL素子、有機EL素子、無機EL素子)、LED(白色LED、赤色LED、緑色LED、青色LEDなど)、トランジスタ(電流に応じて発光するトランジスタ)、電子放出素子、液晶素子、電子インク、電気泳動素子、グレーティングライトバルブ(GLV)、プラズマディスプレイ(PDP)、MEMS(マイクロ・エレクトロ・メカニカル・システム)を用いた表示素子、デジタルマイクロミラーデバイス(DMD)、DMS(デジタル・マイクロ・シャッター)、MIRASOL(登録商標)、IMOD(インターフェアレンス・モジュレーション)素子、シャッター方式のMEMS表示素子、光干渉方式のMEMS表示素子、エレクトロウェッティング素子、圧電セラミックディスプレイ、カーボンナノチューブを用いた表示素子などの少なくとも一つを有している。これらの他にも、電気的または磁気的作用により、コントラスト、輝度、反射率、透過率などが変化する表示媒体を有していても良い。また、表示素子として量子ドットを用いてもよい。EL素子を用いた表示装置の一例としては、ELディスプレイなどがある。電子放出素子を用いた表示装置の一例としては、フィールドエミッションディスプレイ(FED)またはSED方式平面型ディスプレイ(SED:Surface−conduction Electron−emitter Display)などがある。量子ドットを用いた表示装置の一例としては、量子ドットディスプレイなどがある。液晶素子を用いた表示装置の一例としては、液晶ディスプレイ(透過型液晶ディスプレイ、半透過型液晶ディスプレイ、反射型液晶ディスプレイ、直視型液晶ディスプレイ、投射型液晶ディスプレイ)などがある。電子インク、電子粉流体(登録商標)、または電気泳動素子を用いた表示装置の一例としては、電子ペーパーなどがある。なお、半透過型液晶ディスプレイや反射型液晶ディスプレイを実現する場合には、画素電極の一部、または、全部が、反射電極としての機能を有するようにすればよい。例えば、画素電極の一部、または、全部が、アルミニウム、銀、などを有するようにすればよい。さらに、その場合、反射電極の下に、SRAMなどの記憶回路を設けることも可能である。これにより、さらに、消費電力を低減することができる。

本実施の形態では、上記実施の形態に示したトランジスタ232、および/またはトランジスタ252に置き換えて用いることができるトランジスタの一例について、図29乃至図31を用いて説明する。なお、本明細書等に開示するトランジスタは、トランジスタ431やトランジスタ434などにも用いることができる。

図29(A)、(B)に例示するトランジスタ400は、ボトムゲート型のトランジスタの1つであるチャネルエッチ型のトランジスタである。トランジスタ400は、絶縁膜211上に電極216を有する。電極216は、バックゲート電極としての機能を有する。電極216は、電極206または電極115と同様の材料および方法により形成することができる。

図31(A)に例示するトランジスタ430は、トップゲート型のトランジスタの1つである。トランジスタ430は、絶縁膜119の上に半導体膜208を有し、半導体膜208および絶縁膜119上に、半導体膜208の一部に接する電極214および半導体膜208の一部に接する電極215を有し、半導体膜208上に絶縁膜207を有し、絶縁膜207上に電極206を有する。また、電極206上に絶縁膜210と、絶縁膜212を有する。

以下では、酸化物半導体膜の構造について説明する。

上記実施の形態では、タッチセンサ271の一例として静電容量方式のタッチセンサを例示したが、本発明の一態様はこれに限定されない。タッチセンサ271として、抵抗膜方式のタッチセンサを用いてもよい。また、トランジスタなどの能動素子を用いたアクティブ方式のタッチセンサを用いることもできる。

図32に例示するタッチセンサ500は、マトリクス状に配置される複数の検知ユニット510と、行方向に配置される複数の検知ユニット510が電気的に接続される走査線G1と、列方向に配置される複数の検知ユニット510が電気的に接続される信号線DLと、を有する(図32(A)参照)。

図32(C)に例示する検知回路519は、トランジスタM1、トランジスタM2、トランジスタM3を有する。また、トランジスタM1は、ゲートがノードAと電気的に接続され、ソースまたはドレインの一方が接地電位を供給することができる配線VPIと電気的に接続され、ソースまたはドレインの他方がトランジスタM2のソースまたはドレインの一方と電気的に接続される。

変換器CONVは変換回路を備える。検知信号DATAを変換して端子OUTに供給することができるさまざまな回路を、変換器CONVに用いることができる。例えば、変換器CONVを検知回路519と電気的に接続することにより、ソースフォロワ回路またはカレントミラー回路などが構成されるようにしてもよい。

検知回路519の駆動方法について説明する。

《第1のステップ》

第1のステップにおいて、トランジスタM3を導通状態にした後に非導通状態にするリセット信号をゲートに供給し、ノードAの電位を所定の電位にする(図32(D−1)期間T1参照)。

第2のステップにおいて、トランジスタM2を導通状態にする選択信号を供給し、トランジスタM1のソースまたはドレインの他方を信号線DLに電気的に接続する。

第3のステップにおいて、制御信号を検知素子518の一方の電極に供給し、制御信号および検知素子518の静電容量に基づいて変化する電位をノードAを介してトランジスタM1のゲートに供給する。

第4のステップにおいて、トランジスタM1のゲートの電位の変化がもたらす信号を信号線DLに供給する。

第5のステップにおいて、トランジスタM2を非導通状態にする選択信号をゲートに供給する。

図33に例示するタッチセンサ500Bは、検知ユニット510に換えて検知ユニット510Bを備える点がタッチセンサ500と異なる。

図33(C)に例示する検知回路519Bは、トランジスタM1、トランジスタM3を有する。また、トランジスタM1は、ゲートがノードAと電気的に接続され、ソースまたはドレインの一方が接地電位を供給することができる配線VPIと電気的に接続され、ソースまたはドレインの他方が検知信号DATAを供給することができる信号線DLと電気的に接続される。

検知回路519Bの駆動方法について説明する。

《第1のステップ》

第1のステップにおいて、トランジスタM3を導通状態にした後に非導通状態にするリセット信号をゲートに供給し、検知素子518の第1の電極の電位を所定の電位にする(図33(D)期間T1参照)。

第2のステップにおいて、選択信号を検知素子518の一方の電極に供給し、選択信号および検知素子518の静電容量に基づいて変化する電位をノードAを介してトランジスタM1のゲートに供給する(図33(D)期間T2参照)。

第3のステップにおいて、トランジスタM1のゲートの電位の変化がもたらす信号を信号線DLに供給する。

本実施の形態では、発光素子125に用いることができる発光素子の構成例について説明する。なお、本実施の形態に示すEL層320が、他の実施の形態に示したEL層117に相当する。

図34(A)に示す発光素子330は、一対の電極(電極318、電極322)間にEL層320が挟まれた構造を有する。なお、以下の本実施の形態の説明においては、例として、電極318を陽極として用い、電極322を陰極として用いるものとする。

本実施の形態では、本発明の一態様の表示装置が適用された電子機器の例について、図面を参照して説明する。

101 基板

102 基板

103 保護膜

104 導電膜

105 絶縁膜

107 シール材

111 基板

111a 基板

112 接着部

113 剥離膜

114 絶縁膜

115 電極

116 電極

117 EL層

118 電極

119 絶縁膜

120 接着部

121 基板

121a 基板

122 接着部

123 剥離膜

124a 外部電極

125 発光素子

128 開口

129 絶縁膜

130 画素

130B 画素

130G 画素

130R 画素

130Y 画素

131 表示領域

132a 開口

133 駆動回路

134 画素回路

135 配線

136 配線

138a 異方性導電接続部

140 画素

141 絶縁膜

142a 駆動回路

142b 駆動回路

151 光

170 領域

171 素子層

181 素子層

200 表示装置

205 絶縁膜

206 電極

207 絶縁膜

208 半導体膜

209 絶縁膜

210 絶縁膜

211 絶縁膜

212 絶縁膜

213 電極

214 電極

215 電極

216 電極

217 絶縁膜

218 開口

219 電極

220 開口

231 表示領域

232 トランジスタ

233 容量素子

251 駆動回路

252 トランジスタ

264 遮光膜

266 着色膜

267 保護膜

271 タッチセンサ

272 電極

273 絶縁膜

274 電極

275 絶縁膜

318 電極

320 EL層

320a 電荷発生層

322 電極

330 発光素子

331 発光素子

400 トランジスタ

401 トランジスタ

410 トランジスタ

411 トランジスタ

420 トランジスタ

421 トランジスタ

430 トランジスタ

431 トランジスタ

432 液晶素子

434 トランジスタ

435 ノード

436 ノード

437 ノード

500 タッチセンサ

500B タッチセンサ

510 検知ユニット

510B 検知ユニット

518 検知素子

519 検知回路

519B 検知回路

7100 携帯表示装置

7101 筐体

7102 表示部

7103 操作ボタン

7104 送受信装置

7200 照明装置

7201 台部

7202 発光部

7203 操作スイッチ

7210 照明装置

7212 発光部

7220 照明装置

7222 発光部

7400 携帯電話機

7401 筐体

7402 表示部

7403 操作ボタン

7404 外部接続ポート

7405 スピーカ

7406 マイク

9310 携帯情報端末

9313 ヒンジ

9315 筐体

9316 表示パネル

9320 携帯情報端末

9322 表示部

9325 非表示部

9330 携帯情報端末

9333 表示部

9335 筐体

9336 筐体

9337 情報

9339 操作ボタン

9340 携帯情報端末

9345 携帯情報端末

9354 筐体

9355 情報

9356 情報

9357 情報

9358 表示部

Claims (12)

- 発光素子と、有機樹脂膜と、第1の酸化物膜とを有し、

前記有機樹脂膜は、前記発光素子に接する領域を有し、

前記発光素子は、第1の電極と、EL層と、第2の電極とを有し、

前記有機樹脂膜は、前記第1の電極上面と接し、

前記EL層は、前記有機樹脂膜上面及び前記第1の電極上面と接し、

前記第2の電極は、前記EL層上面と接し、

前記第1の酸化物膜は、前記第2の電極上面、前記有機樹脂膜側面及び前記第1の電極側面と接し、

前記第1の酸化物膜は、前記有機樹脂膜の側面と接する領域を有し、

前記第1の酸化物膜は、インジウムと、亜鉛及びガリウムを含む、表示装置。 - 請求項1において、

絶縁膜を有し、

前記絶縁膜は、前記第1の酸化物膜と接する領域を有する、表示装置。 - 発光素子と、有機樹脂膜と、第1の酸化物膜と、第2の酸化物膜とを有し、

前記有機樹脂膜は、前記発光素子に接する領域を有し、

前記発光素子は、第1の電極と、EL層と、第2の電極とを有し、

前記有機樹脂膜は、前記第1の電極上面と接し、

前記EL層は、前記有機樹脂膜上面及び前記第1の電極上面と接し、

前記第2の電極は、前記EL層上面と接し、

前記第1の酸化物膜は、前記第2の電極上面、前記有機樹脂膜側面及び前記第1の電極側面と接し、

前記第2の酸化物膜は、前記第1の酸化物膜上面と接し、

前記第1の酸化物膜は、インジウムと、亜鉛及びガリウムを含み、

前記第2の酸化物膜は、インジウムを含む、表示装置。 - 請求項1乃至3のいずれか一項において、

トランジスタを有し、

前記トランジスタは、前記発光素子に接続される、表示装置。 - 発光素子と、有機樹脂膜と、第1の酸化物膜とを有し、

前記有機樹脂膜は、前記発光素子に接する領域を有し、

前記発光素子は、第1の電極と、EL層と、第2の電極とを有し、

前記有機樹脂膜は、前記第1の電極上面と接し、

前記EL層は、前記有機樹脂膜上面及び前記第1の電極上面と接し、

前記第2の電極は、前記EL層上面と接し、

前記第1の酸化物膜は、前記第2の電極上面、前記有機樹脂膜側面及び前記第1の電極側面と接し、

前記第2の酸化物膜は、前記第1の酸化物膜上面と接し、

前記第1の酸化物膜は、インジウムと、亜鉛及びガリウムを含む、発光装置。 - 請求項5において、

絶縁膜を有し、

前記絶縁膜は、前記第1の酸化物膜と接する領域を有する、発光装置。 - 発光素子と、有機樹脂膜と、第1の酸化物膜と、第2の酸化物膜とを有し、

前記有機樹脂膜は、前記発光素子に接する領域を有し、

前記発光素子は、第1の電極と、EL層と、第2の電極とを有し、

前記有機樹脂膜は、前記第1の電極上面と接し、

前記EL層は、前記有機樹脂膜上面及び前記第1の電極上面と接し、

前記第2の電極は、前記EL層上面と接し、

前記第1の酸化物膜は、前記第2の電極上面、前記有機樹脂膜側面及び前記第1の電極側面と接し、

前記第2の酸化物膜は、前記第1の酸化物膜上面と接し、

前記第1の酸化物膜は、インジウムと、亜鉛及びガリウムを含み、

前記第2の酸化物膜は、インジウムを含む、発光装置。 - 発光素子と、有機樹脂膜と、第1の酸化物膜と、第2の酸化物膜とを有し、

前記有機樹脂膜は、前記発光素子に接する領域を有し、

前記発光素子は、第1の電極と、EL層と、第2の電極とを有し、

前記有機樹脂膜は、前記第1の電極上面と接し、

前記EL層は、前記有機樹脂膜上面及び前記第1の電極上面と接し、

前記第2の電極は、前記EL層上面と接し、

前記第1の酸化物膜は、前記第2の電極上面、前記有機樹脂膜側面及び前記第1の電極側面と接し、

前記第2の酸化物膜は、前記第1の酸化物膜上面と接し、

前記第1の酸化物膜は、インジウムと、亜鉛及びガリウムを含み、

前記第2の酸化物膜は、インジウムを含む、発光装置。 - 請求項5乃至8のいずれか一項において、

前記第1の酸化物膜は、インジウムと、M(MはAl、Ga、Y、Zr、Sn、La、Ce、またはNd)と、亜鉛と、を含み、

前記第1の酸化物膜におけるガリウムの原子数比は、インジウムの原子数比より大きい値を有し、

前記第1の酸化物膜における亜鉛の原子数比は、インジウムの原子数比より大きい値を有する、発光装置。 - 請求項5乃至9のいずれか一項において、

トランジスタを有し、

前記トランジスタは、前記発光素子に接続される、発光装置。 - 請求項1乃至4のいずれか一項に記載の表示装置と、

操作スイッチ、筐体、またはマイクと、を有する電子機器。 - 請求項5乃至10のいずれか一項に記載の発光装置と、筐体と、を有する電子機器。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015094500A JP6722980B2 (ja) | 2014-05-09 | 2015-05-05 | 表示装置および発光装置、並びに電子機器 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014097943 | 2014-05-09 | ||

| JP2014097943 | 2014-05-09 | ||

| JP2015094500A JP6722980B2 (ja) | 2014-05-09 | 2015-05-05 | 表示装置および発光装置、並びに電子機器 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2015228368A JP2015228368A (ja) | 2015-12-17 |

| JP2015228368A5 JP2015228368A5 (ja) | 2018-06-14 |

| JP6722980B2 true JP6722980B2 (ja) | 2020-07-15 |

Family

ID=54368542

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015094500A Active JP6722980B2 (ja) | 2014-05-09 | 2015-05-05 | 表示装置および発光装置、並びに電子機器 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US9876058B2 (ja) |

| JP (1) | JP6722980B2 (ja) |

| KR (2) | KR20150128609A (ja) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6722980B2 (ja) * | 2014-05-09 | 2020-07-15 | 株式会社半導体エネルギー研究所 | 表示装置および発光装置、並びに電子機器 |

| US10204535B2 (en) * | 2015-04-06 | 2019-02-12 | Semiconductor Energy Laboratory Co., Ltd. | Display device and electronic device |

| CN105552225B (zh) * | 2016-01-20 | 2020-04-17 | 京东方科技集团股份有限公司 | 用于制造柔性基板的方法、柔性基板和显示装置 |

| CN109121438B (zh) * | 2016-02-12 | 2022-02-18 | 株式会社半导体能源研究所 | 半导体装置以及包括该半导体装置的显示装置 |

| CN107579088B (zh) * | 2016-07-11 | 2021-02-26 | 京东方科技集团股份有限公司 | 一种柔性oled显示面板及其制备方法 |

| KR102517092B1 (ko) * | 2017-08-02 | 2023-04-04 | 삼성전자주식회사 | 가요성 디스플레이 패널을 포함하는 전자 장치 |

| CN109752421B (zh) * | 2019-01-31 | 2021-08-24 | 厦门天马微电子有限公司 | 显示面板和显示装置 |

| KR20220087606A (ko) * | 2020-12-17 | 2022-06-27 | 삼성디스플레이 주식회사 | 표시 장치 |

| CN113054077A (zh) * | 2021-03-16 | 2021-06-29 | 京东方科技集团股份有限公司 | 显示面板及其制备方法、显示装置及拼接显示装置 |

| US11296224B1 (en) * | 2021-06-16 | 2022-04-05 | Purdue Research Foundation | Non-volatile polarization induced strain coupled 2D FET memory |

Family Cites Families (42)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6717181B2 (en) * | 2001-02-22 | 2004-04-06 | Semiconductor Energy Laboratory Co., Ltd. | Luminescent device having thin film transistor |

| JP4027740B2 (ja) | 2001-07-16 | 2007-12-26 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US8415208B2 (en) | 2001-07-16 | 2013-04-09 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and peeling off method and method of manufacturing semiconductor device |

| JP4408127B2 (ja) * | 2003-01-24 | 2010-02-03 | 株式会社半導体エネルギー研究所 | 発光装置の作製方法 |

| JP2005292407A (ja) * | 2004-03-31 | 2005-10-20 | Nec Corp | 液晶パネルおよびその製造方法及び液晶パネルを搭載した電子機器 |

| US7298084B2 (en) | 2004-11-02 | 2007-11-20 | 3M Innovative Properties Company | Methods and displays utilizing integrated zinc oxide row and column drivers in conjunction with organic light emitting diodes |

| JPWO2006067952A1 (ja) * | 2004-12-20 | 2008-06-12 | コニカミノルタホールディングス株式会社 | ガスバリア性薄膜積層体、ガスバリア性樹脂基材、有機elデバイス |

| JPWO2006095612A1 (ja) * | 2005-03-10 | 2008-08-14 | コニカミノルタホールディングス株式会社 | 有機エレクトロルミネッセンス用樹脂フィルム基板および有機エレクトロルミネッセンスデバイス |

| JP4971703B2 (ja) * | 2005-07-04 | 2012-07-11 | 帝人デュポンフィルム株式会社 | 有機elディスプレイ基板用ポリエステルフィルム及びそれからなる有機elディスプレイ基板用ガスバリア性積層ポリエステルフィルム |

| KR101345376B1 (ko) | 2007-05-29 | 2013-12-24 | 삼성전자주식회사 | ZnO 계 박막 트랜지스터 및 그 제조방법 |

| EP2274163B1 (en) * | 2008-04-29 | 2019-12-18 | Agency for Science, Technology And Research | Inorganic graded barrier film and methods for their manufacture |

| TWI450399B (zh) | 2008-07-31 | 2014-08-21 | 半導體能源研究所股份有限公司 | 半導體裝置及其製造方法 |

| US8383470B2 (en) | 2008-12-25 | 2013-02-26 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor (TFT) having a protective layer and manufacturing method thereof |

| TWI474408B (zh) | 2008-12-26 | 2015-02-21 | 半導體能源研究所股份有限公司 | 半導體裝置及其製造方法 |

| US8450144B2 (en) | 2009-03-26 | 2013-05-28 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| WO2011013523A1 (en) * | 2009-07-31 | 2011-02-03 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| WO2011027661A1 (en) | 2009-09-04 | 2011-03-10 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device and method for manufacturing the same |

| WO2011027656A1 (en) * | 2009-09-04 | 2011-03-10 | Semiconductor Energy Laboratory Co., Ltd. | Transistor and display device |

| WO2011074407A1 (en) * | 2009-12-18 | 2011-06-23 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| CN105789321B (zh) | 2010-03-26 | 2019-08-20 | 株式会社半导体能源研究所 | 半导体装置的制造方法 |

| JP2012028169A (ja) * | 2010-07-23 | 2012-02-09 | Hitachi Displays Ltd | 有機エレクトロルミネッセンス表示装置 |

| US9443984B2 (en) | 2010-12-28 | 2016-09-13 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US9082860B2 (en) | 2011-03-31 | 2015-07-14 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP6109489B2 (ja) | 2011-05-13 | 2017-04-05 | 株式会社半導体エネルギー研究所 | El表示装置 |

| US10249848B2 (en) * | 2011-11-02 | 2019-04-02 | Joled Inc. | Organic light-emitting panel and method for producing same |

| JP5918509B2 (ja) * | 2011-11-15 | 2016-05-18 | 株式会社半導体エネルギー研究所 | 発光装置 |

| JP5907722B2 (ja) * | 2011-12-23 | 2016-04-26 | 株式会社半導体エネルギー研究所 | 発光装置の作製方法 |

| KR102412138B1 (ko) * | 2012-01-25 | 2022-06-22 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 반도체 장치의 제작 방법 |

| JP6059566B2 (ja) * | 2012-04-13 | 2017-01-11 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| CN104380366B (zh) * | 2012-06-19 | 2017-09-08 | 新日铁住金化学株式会社 | 显示装置及其制造方法、以及显示装置支撑基材用聚酰亚胺膜及其制造方法 |

| KR102173801B1 (ko) * | 2012-07-12 | 2020-11-04 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시 장치, 및 표시 장치의 제작 방법 |

| JP6142151B2 (ja) * | 2012-07-31 | 2017-06-07 | 株式会社Joled | 表示装置および電子機器 |

| US9018624B2 (en) * | 2012-09-13 | 2015-04-28 | Semiconductor Energy Laboratory Co., Ltd. | Display device and electronic appliance |

| TWI782259B (zh) * | 2012-10-24 | 2022-11-01 | 日商半導體能源研究所股份有限公司 | 半導體裝置及其製造方法 |

| KR102000043B1 (ko) * | 2012-10-31 | 2019-07-15 | 엘지디스플레이 주식회사 | 유기전계발광 표시소자 및 그 제조방법 |

| FR2997770B1 (fr) * | 2012-11-07 | 2015-11-20 | Saint Gobain | Support electroconducteur pour vitrage a diffusion variable par cristaux liquides, et un tel vitrage |

| JP5804162B2 (ja) * | 2013-08-30 | 2015-11-04 | 大日本印刷株式会社 | トップエミッション型有機エレクトロルミネッセンス表示装置の製造方法、およびトップエミッション型有機エレクトロルミネッセンス表示装置形成用蓋材 |

| US9349751B2 (en) * | 2013-12-12 | 2016-05-24 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| WO2015132694A1 (en) * | 2014-03-07 | 2015-09-11 | Semiconductor Energy Laboratory Co., Ltd. | Touch sensor, touch panel, and manufacturing method of touch panel |

| JP6722980B2 (ja) * | 2014-05-09 | 2020-07-15 | 株式会社半導体エネルギー研究所 | 表示装置および発光装置、並びに電子機器 |

| US10372274B2 (en) * | 2015-04-13 | 2019-08-06 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and touch panel |

| US20160299387A1 (en) * | 2015-04-13 | 2016-10-13 | Semiconductor Energy Laboratory Co., Ltd. | Display panel, data processor, and method for manufacturing display panel |

-

2015

- 2015-05-05 JP JP2015094500A patent/JP6722980B2/ja active Active

- 2015-05-06 US US14/705,774 patent/US9876058B2/en active Active

- 2015-05-08 KR KR1020150064438A patent/KR20150128609A/ko not_active Ceased

-

2022

- 2022-03-29 KR KR1020220038539A patent/KR102432641B1/ko active Active

Also Published As

| Publication number | Publication date |

|---|---|

| KR102432641B1 (ko) | 2022-08-16 |

| JP2015228368A (ja) | 2015-12-17 |

| US20150325631A1 (en) | 2015-11-12 |

| KR20150128609A (ko) | 2015-11-18 |

| US9876058B2 (en) | 2018-01-23 |

| KR20220044184A (ko) | 2022-04-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US11800747B2 (en) | Display device and electronic device | |

| US11669181B2 (en) | Display device and electronic device | |

| US10038171B2 (en) | Method for manufacturing display device and method for manufacturing electronic device | |

| JP6722980B2 (ja) | 表示装置および発光装置、並びに電子機器 | |

| US9917267B2 (en) | Electronic device comprising first opening and second opening with different widths | |

| US9843017B2 (en) | Display device, manufacturing method thereof, and electronic device | |

| US10522574B2 (en) | Manufacturing method of display device and manufacturing method of electronic device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180426 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20180426 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20190116 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20190226 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190423 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20191001 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20191127 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200129 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20200526 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20200623 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6722980 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |