JP6663209B2 - 撮像装置、撮像システム及び撮像装置の駆動方法 - Google Patents

撮像装置、撮像システム及び撮像装置の駆動方法 Download PDFInfo

- Publication number

- JP6663209B2 JP6663209B2 JP2015233675A JP2015233675A JP6663209B2 JP 6663209 B2 JP6663209 B2 JP 6663209B2 JP 2015233675 A JP2015233675 A JP 2015233675A JP 2015233675 A JP2015233675 A JP 2015233675A JP 6663209 B2 JP6663209 B2 JP 6663209B2

- Authority

- JP

- Japan

- Prior art keywords

- capacitance

- input node

- capacitance value

- unit

- control unit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000003384 imaging method Methods 0.000 title claims description 127

- 238000000034 method Methods 0.000 title claims description 36

- 238000006243 chemical reaction Methods 0.000 claims description 76

- 238000012546 transfer Methods 0.000 claims description 51

- 230000003321 amplification Effects 0.000 claims description 17

- 238000003199 nucleic acid amplification method Methods 0.000 claims description 17

- 238000012545 processing Methods 0.000 claims description 16

- 230000008569 process Effects 0.000 claims description 14

- 230000008859 change Effects 0.000 claims description 12

- 238000009792 diffusion process Methods 0.000 description 40

- 238000010586 diagram Methods 0.000 description 39

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 19

- 230000000052 comparative effect Effects 0.000 description 16

- 238000009825 accumulation Methods 0.000 description 12

- 230000006870 function Effects 0.000 description 11

- 230000001276 controlling effect Effects 0.000 description 10

- 239000003990 capacitor Substances 0.000 description 8

- 230000000875 corresponding effect Effects 0.000 description 7

- 238000004891 communication Methods 0.000 description 5

- 230000003287 optical effect Effects 0.000 description 5

- 230000004044 response Effects 0.000 description 5

- 230000003111 delayed effect Effects 0.000 description 4

- 230000007423 decrease Effects 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 239000004065 semiconductor Substances 0.000 description 3

- 230000007704 transition Effects 0.000 description 3

- 230000004888 barrier function Effects 0.000 description 2

- 230000003139 buffering effect Effects 0.000 description 2

- 230000015556 catabolic process Effects 0.000 description 2

- 238000012937 correction Methods 0.000 description 2

- 230000002596 correlated effect Effects 0.000 description 2

- 238000006731 degradation reaction Methods 0.000 description 2

- 230000001934 delay Effects 0.000 description 2

- 230000006866 deterioration Effects 0.000 description 2

- 239000012535 impurity Substances 0.000 description 2

- 238000005070 sampling Methods 0.000 description 2

- 239000000758 substrate Substances 0.000 description 2

- 230000005540 biological transmission Effects 0.000 description 1

- 238000013144 data compression Methods 0.000 description 1

- 238000006073 displacement reaction Methods 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 238000005096 rolling process Methods 0.000 description 1

- 230000035945 sensitivity Effects 0.000 description 1

- 230000001360 synchronised effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/50—Control of the SSIS exposure

- H04N25/57—Control of the dynamic range

- H04N25/59—Control of the dynamic range by controlling the amount of charge storable in the pixel, e.g. modification of the charge conversion ratio of the floating node capacitance

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/50—Control of the SSIS exposure

- H04N25/53—Control of the integration time

- H04N25/531—Control of the integration time by controlling rolling shutters in CMOS SSIS

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/50—Control of the SSIS exposure

- H04N25/57—Control of the dynamic range

- H04N25/58—Control of the dynamic range involving two or more exposures

- H04N25/587—Control of the dynamic range involving two or more exposures acquired sequentially, e.g. using the combination of odd and even image fields

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

- H04N25/779—Circuitry for scanning or addressing the pixel array

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

- H04N25/78—Readout circuits for addressed sensors, e.g. output amplifiers or A/D converters

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/803—Pixels having integrated switching, control, storage or amplification elements

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/805—Coatings

- H10F39/8057—Optical shielding

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/812—Arrangements for transferring the charges in the image sensor perpendicular to the imaging plane, e.g. buried regions used to transfer generated charges to circuitry under the photosensitive region

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

- H04N25/77—Pixel circuitry, e.g. memories, A/D converters, pixel amplifiers, shared circuits or shared components

- H04N25/778—Pixel circuitry, e.g. memories, A/D converters, pixel amplifiers, shared circuits or shared components comprising amplifiers shared between a plurality of pixels, i.e. at least one part of the amplifier must be on the sensor array itself

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

Description

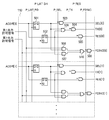

図1は、第1実施形態に係る撮像装置の構成を示すブロック図である。撮像装置は、画素アレイ100、垂直走査回路110(VSC)、列読み出し部120、メモリ部130、出力回路140、及び水平走査回路150を有する。撮像装置は、さらにこれらの各部に信号を供給して制御する、第1容量制御部160、第2容量制御部170、及びタイミング制御部180(TG)を有する。画素アレイ100は、複数の行及び複数の列をなすマトリクス状に配列された複数の画素101を含む。垂直走査回路110は、行ごとに複数の制御信号を画素アレイ100の各画素101に出力する。ここで、垂直走査回路から各画素に供給される制御信号は、RES[0]〜[n]、TX[0]〜[n]、FDINC[0]〜[n]、SEL[0]〜[n]である。なお、添字は画素アレイ100の行番号を示すものとするが、行番号を特定する必要がない場合には、添字を省略することもある。また、本明細書では行番号及び列番号は、いずれも0から始まるものとする。したがって、画素101の行数はn+1である。画素101は、垂直走査回路110からの制御信号SEL[0]〜[n]により行ごとに順次選択される(垂直走査)。選択された行の画素101から出力される信号が列ごとに共通に設けられた垂直出力線102を介して読み出される。

図10は、第2実施形態に係る画素アレイの配列図である。画素アレイ1000は、NULL画素(ダミー画素)が配列されたNULL画素領域1000aと、OB画素(遮光画素)が配列されたOB画素領域1000bと、第1実施形態で述べた画素101(有効画素)が配列された有効画素領域1000cとを有する。これらの画素領域は、画素アレイ1000の先頭行から順に、NULL画素領域1000a、OB画素領域1000b、有効画素領域1000cの順に並んでいる。NULL画素とは、光電変換部PDを有しない画素であり、暗電流の影響を含まない基準信号を取得可能な画素である。OB画素とは、光電変換部PDが可視光を透過しない金属等の遮光膜で覆われている画素であり、暗電流の影響を含む基準信号を得ることができる。これらの基準信号を用いて有効画素領域1000cから得られた信号を補正することにより、高精度な撮像が可能となる。

図13は、第3実施形態に係る撮像装置の構成を示すブロック図である。本実施形態では、第2容量制御部1370及び垂直走査回路1310の構成が第1、第2実施形態と異なる。第2容量制御部1370は、第2出力許可信号Aと第2出力許可信号Bの2つの信号を垂直走査回路1310に出力する。

図19は、第4実施形態に係る撮像装置の駆動方法を模式的に示す図である。本実施形態は第3実施形態の駆動方法に、撮像装置のリセット時のデフォルト設定(初期設定)をFD容量大としたものである。以下、撮像装置の電源がオンになった直後の駆動について説明する。

図20は、第5実施形態に係る撮像装置の駆動方法を模式的に示す図である。本実施形態の撮像装置は、第4実施形態の撮像装置において、さらに、メカニカルシャッタ(メカシャッタ)を備え、かつメカシャッタにより蓄積時間を制御する静止画撮影が可能となっている。メカシャッタによる露光時間制御が行われるため、本実施形態では、第1から第4の形態で述べたようなシャッタ走査は行われない。

図23は、第6実施形態に係る画素の構成を示す回路図である。本実施形態は、画素2301の構成が、第1乃至第5実施形態の画素101と異なる。本実施形態の画素2301は、2つの光電変換部PD_A、PD_Bと2つの転送トランジスタM1A、M1Bを有する。画素2301は半導体基板上に形成される。光電変換部PD_A、PD_Bが形成されている部分の上部には、入射光を光電変換部PD_A、PD_Bに導くための1つのマイクロレンズMLが形成されている。言い換えると、光電変換部PD_A、PD_Bは1つのマイクロレンズMLに共有されている。

第7実施形態に係る撮像システムについて説明する。撮像システムの例としては、デジタルスチルカメラ、デジタルカムコーダ、複写機、ファクシミリ、携帯電話、車載カメラ、観測衛星などがあげられる。また、レンズなどの光学系と撮像装置とを備えるカメラモジュールも、撮像システムに含まれる。図25に、撮像システムの一例としてデジタルスチルカメラのブロック図を示す。

101 画素

110 垂直走査回路

160 第1容量制御部

170 第2容量制御部

Claims (14)

- 入射光に応じた電荷を生成する光電変換部と、

入力ノードを有し、前記入力ノードの電荷に応じた信号を出力する増幅トランジスタと、

前記光電変換部で生成された電荷を前記入力ノードに転送する転送トランジスタと、

前記入力ノードを所定の電圧でリセットするリセットトランジスタと、

前記入力ノードの容量値を可変とする容量可変手段と、

をそれぞれが含む複数の画素が、複数の行をなすように配された画素アレイと、

前記転送トランジスタと前記リセットトランジスタとをオンにすることによって、前記光電変換部の電荷をリセットする処理を前記複数の画素のそれぞれの行に順次行うシャッタ走査と、前記転送トランジスタをオンにすることによって、前記光電変換部の電荷を前記入力ノードに転送する処理を前記複数の画素のそれぞれの行に順次行う読み出し走査と、のそれぞれを行う走査回路と、

前記読み出し走査において、前記容量可変手段を制御して前記入力ノードの容量値を設定する第1の制御部と、

前記シャッタ走査において、前記容量可変手段を制御して前記入力ノードの容量値を設定する第2の制御部と、

を有し、

前記第1の制御部は、前記走査回路が前記読み出し走査を開始するタイミングと同期して、前記容量可変手段が前記入力ノードの容量値を設定するように、前記容量可変手段を制御し、

前記第2の制御部は、前記走査回路が前記シャッタ走査を開始するタイミングと同期して、前記容量可変手段が前記入力ノードの容量値を設定するように、前記容量可変手段を制御する

ことを特徴とする撮像装置。 - 同一フレームの画像を取得するための一連の前記読み出し走査と前記シャッタ走査において、前記第1の制御部及び前記第2の制御部は、前記読み出し走査における前記入力ノードの容量値と、前記シャッタ走査における前記入力ノードの容量値とを同一の容量値に設定するように、前記容量可変手段を制御することを特徴とする請求項1に記載の撮像装置。

- 前記画素アレイは、複数の行をなすように配され、前記光電変換部を含まない複数のダミー画素と、複数の行をなすように配され、前記光電変換部が遮光された複数の遮光画素と、をさらに含み、

前記第2の制御部は、前記走査回路が前記ダミー画素及び前記遮光画素の前記読み出し走査を開始した後に、前記走査回路が前記シャッタ走査を開始するタイミングと同期して、前記容量可変手段が前記入力ノードの容量値を設定するように、前記容量可変手段を制御することを特徴とする請求項1又は2に記載の撮像装置。 - 入射光に応じた電荷を生成する光電変換部と、

入力ノードを有し、前記入力ノードの電荷に応じた信号を出力する増幅トランジスタと、

前記光電変換部で生成された電荷を前記入力ノードに転送する転送トランジスタと、

前記入力ノードを所定の電圧でリセットするリセットトランジスタと、

前記入力ノードの容量値を可変とする容量可変手段と、

をそれぞれが含む複数の画素が、複数の行をなすように配された画素アレイと、

前記転送トランジスタと前記リセットトランジスタとをオンにすることによって、前記光電変換部の電荷をリセットする処理を前記複数の画素のそれぞれの行に順次行うシャッタ走査と、前記転送トランジスタをオンにすることによって、前記光電変換部の電荷を前記入力ノードに転送する処理を前記複数の画素のそれぞれの行に順次行う読み出し走査と、のそれぞれを行う走査回路と、

前記読み出し走査において、前記容量可変手段を制御して前記入力ノードの容量値を設定する第1の制御部と、

前記シャッタ走査において、前記容量可変手段を制御して前記入力ノードの容量値を設定する第2の制御部と、

を有し、

同一フレームの画像を取得するための一連の前記読み出し走査と前記シャッタ走査において、前記第1の制御部及び前記第2の制御部は、前記読み出し走査における前記入力ノードの容量値と、前記シャッタ走査における前記入力ノードの容量値とを同一の容量値に設定するように、前記容量可変手段を制御する

ことを特徴とする撮像装置。 - 入射光に応じた電荷を生成する光電変換部と、

入力ノードを有し、前記入力ノードの電荷に応じた信号を出力する増幅トランジスタと、

前記光電変換部で生成された電荷を前記入力ノードに転送する転送トランジスタと、

前記入力ノードを所定の電圧でリセットするリセットトランジスタと、

前記入力ノードの容量値を可変とする容量可変手段と、

をそれぞれが含む複数の画素が、複数の行をなすように配された画素アレイと、

前記転送トランジスタと前記リセットトランジスタとをオンにすることによって、前記光電変換部の電荷をリセットする処理を前記複数の画素のそれぞれの行に順次行うシャッタ走査と、前記転送トランジスタをオンにすることによって、前記光電変換部の電荷を前記入力ノードに転送する処理を前記複数の画素のそれぞれの行に順次行う読み出し走査と、のそれぞれを行う走査回路と、

前記読み出し走査において、前記容量可変手段を制御して前記入力ノードの容量値を設定する第1の制御部と、

前記シャッタ走査において、前記容量可変手段を制御して前記入力ノードの容量値を設定する第2の制御部と、

を有し、

前記画素アレイは、複数の行をなすように配され、前記光電変換部を含まない複数のダミー画素と、複数の行をなすように配され、前記光電変換部が遮光された複数の遮光画素と、をさらに含み、

前記第2の制御部は、前記走査回路が前記ダミー画素及び前記遮光画素の前記読み出し走査を開始した後に、前記走査回路が前記シャッタ走査を開始するタイミングと同期して、前記容量可変手段が前記入力ノードの容量値を設定するように、前記容量可変手段を制御する

ことを特徴とする撮像装置。 - 入射光に応じた電荷を生成する光電変換部と、

入力ノードを有し、前記入力ノードの電荷に応じた信号を出力する増幅トランジスタと、

前記光電変換部で生成された電荷を前記入力ノードに転送する転送トランジスタと、

前記入力ノードを所定の電圧でリセットするリセットトランジスタと、

前記入力ノードの容量値を可変とする容量可変手段と、

をそれぞれが含む複数の画素が、複数の行をなすように配された画素アレイと、

前記転送トランジスタと前記リセットトランジスタとをオンにすることによって、前記光電変換部の電荷をリセットする処理を前記複数の画素のそれぞれの行に順次行うシャッタ走査と、前記転送トランジスタをオンにすることによって、前記光電変換部の電荷を前記入力ノードに転送する処理を前記複数の画素のそれぞれの行に順次行う読み出し走査と、のそれぞれを行う走査回路と、

前記読み出し走査において、前記容量可変手段を制御して前記入力ノードの容量値を設定する第1の制御部と、

前記シャッタ走査において、前記容量可変手段を制御して前記入力ノードの容量値を設定する第2の制御部と、

を有し、

前記第2の制御部は、前記画素アレイの2つの行の前記入力ノードに対し互いに異なる容量値を設定し得る

ことを特徴とする撮像装置。 - 入射光に応じた電荷を生成する光電変換部と、

入力ノードを有し、前記入力ノードの電荷に応じた信号を出力する増幅トランジスタと、

前記光電変換部で生成された電荷を前記入力ノードに転送する転送トランジスタと、

前記入力ノードを所定の電圧でリセットするリセットトランジスタと、

前記入力ノードの容量値を可変とする容量可変手段と、

をそれぞれが含む複数の画素が、複数の行をなすように配された画素アレイと、

前記転送トランジスタと前記リセットトランジスタとをオンにすることによって、前記光電変換部の電荷をリセットする処理を前記複数の画素のそれぞれの行に順次行うシャッタ走査と、前記転送トランジスタをオンにすることによって、前記光電変換部の電荷を前記入力ノードに転送する処理を前記複数の画素のそれぞれの行に順次行う読み出し走査と、のそれぞれを行う走査回路と、

前記読み出し走査において、前記容量可変手段を制御して前記入力ノードの容量値を設定する第1の制御部と、

前記シャッタ走査において、前記容量可変手段を制御して前記入力ノードの容量値を設定する第2の制御部と、

を有し、

前記容量可変手段は、前記入力ノードの容量値を、少なくとも第1の容量値と、前記第1の容量値よりも大きい第2の容量値とのいずれかに可変とする構成を有し、

撮像装置の初期設定において、前記第1の制御部及び前記第2の制御部は、いずれも前記容量可変手段を制御して前記入力ノードの容量値を前記第2の容量値に設定する

ことを特徴とする撮像装置。 - 一部の行の前記シャッタ走査と一部の行の前記読み出し走査は、同一の期間に並行して行われることを特徴とする請求項1乃至7のいずれか1項に記載の撮像装置。

- 前記走査回路が、前記複数の画素の全ての行の前記読み出し走査を行っている間に、前記第1の制御部は、前記容量可変手段が前記入力ノードの容量値を変更しないように前記容量可変手段を制御し、

前記走査回路が、前記複数の画素の全ての行の前記シャッタ走査を行っている間に、前記第2の制御部は、前記容量可変手段が前記入力ノードの容量値を変更しないように前記容量可変手段を制御する

ことを特徴とする請求項1乃至8のいずれか1項に記載の撮像装置。 - 前記容量可変手段は、前記入力ノードが有する所定の容量に対し付加される容量値を変化させることにより、前記入力ノードの容量値を可変とすることを特徴とする請求項1乃至9のいずれか1項に記載の撮像装置。

- 前記容量可変手段は、付加容量を含み、前記付加容量を前記入力ノードが有する所定の容量に対し接続又は非接続とすることにより、前記入力ノードの容量値を可変とすることを特徴とする請求項1乃至10のいずれか1項に記載の撮像装置。

- 前記容量可変手段は、前記入力ノードの容量値を、少なくとも第1の容量値と、前記第1の容量値よりも大きい第2の容量値とのいずれかに可変とする構成を有し、

メカニカルシャッタを用いた静止画撮影時において、前記第2の制御部は、前記容量可変手段を制御して前記入力ノードの容量値を常に前記第2の容量値に設定することを特徴とする請求項1乃至11のいずれか1項に記載の撮像装置。 - 前記複数の画素のそれぞれは、

1つのマイクロレンズによって導かれた光が入射される複数の前記光電変換部と、

前記複数の光電変換部のそれぞれで生成された電荷を前記入力ノードにそれぞれ転送する複数の前記転送トランジスタと、

を含むことを特徴とする請求項1乃至12のいずれか1項に記載の撮像装置。 - 請求項1乃至13のいずれか1項に記載の撮像装置と、

前記撮像装置から出力される信号を処理する信号処理部と

を有する撮像システム。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015233675A JP6663209B2 (ja) | 2015-11-30 | 2015-11-30 | 撮像装置、撮像システム及び撮像装置の駆動方法 |

| US15/360,833 US10432880B2 (en) | 2015-11-30 | 2016-11-23 | Imaging apparatus, imaging system, and driving method for imaging apparatus |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015233675A JP6663209B2 (ja) | 2015-11-30 | 2015-11-30 | 撮像装置、撮像システム及び撮像装置の駆動方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2017103537A JP2017103537A (ja) | 2017-06-08 |

| JP2017103537A5 JP2017103537A5 (ja) | 2019-01-17 |

| JP6663209B2 true JP6663209B2 (ja) | 2020-03-11 |

Family

ID=58778314

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015233675A Expired - Fee Related JP6663209B2 (ja) | 2015-11-30 | 2015-11-30 | 撮像装置、撮像システム及び撮像装置の駆動方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US10432880B2 (ja) |

| JP (1) | JP6663209B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2016012904A (ja) * | 2014-06-02 | 2016-01-21 | ソニー株式会社 | 撮像素子、撮像方法、および電子機器 |

| JP7587380B2 (ja) | 2020-09-18 | 2024-11-20 | キヤノン株式会社 | 光電変換装置、光電変換システム及び移動体 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6246436B1 (en) * | 1997-11-03 | 2001-06-12 | Agilent Technologies, Inc | Adjustable gain active pixel sensor |

| US6512544B1 (en) * | 1998-06-17 | 2003-01-28 | Foveon, Inc. | Storage pixel sensor and array with compression |

| US20030076431A1 (en) * | 2001-10-24 | 2003-04-24 | Krymski Alexander I. | Image sensor with pixels having multiple capacitive storage elements |

| US7075049B2 (en) * | 2003-06-11 | 2006-07-11 | Micron Technology, Inc. | Dual conversion gain imagers |

| JP4931232B2 (ja) * | 2007-07-04 | 2012-05-16 | キヤノン株式会社 | 撮像装置及びその処理方法 |

| US8077237B2 (en) | 2007-10-16 | 2011-12-13 | Aptina Imaging Corporation | Method and apparatus for controlling dual conversion gain signal in imaging devices |

| US8324550B2 (en) * | 2010-06-22 | 2012-12-04 | Aptina Imaging Corporation | High dynamic range imaging systems |

| TWI456990B (zh) * | 2011-04-08 | 2014-10-11 | Pixart Imaging Inc | 高動態範圍影像感測電路及高動態範圍影像讀取方法 |

| KR101241466B1 (ko) * | 2011-04-13 | 2013-03-11 | 엘지이노텍 주식회사 | 픽셀 어레이, 이를 포함하는 이미지센서 및 그 구동 방법 |

| US9628732B2 (en) * | 2013-08-23 | 2017-04-18 | Semiconductor Components Industries, Llc | Imaging systems and methods for performing column-based image sensor pixel gain adjustments |

| JP5623607B2 (ja) * | 2013-08-30 | 2014-11-12 | キヤノン株式会社 | 撮像装置及び撮像システム |

| US9929204B2 (en) * | 2014-03-13 | 2018-03-27 | Samsung Electronics Co., Ltd. | Unit pixel of image sensor, image sensor including the same and method of manufacturing image sensor |

| JP6075646B2 (ja) * | 2014-03-17 | 2017-02-08 | ソニー株式会社 | 固体撮像装置およびその駆動方法、並びに電子機器 |

| JP6339851B2 (ja) * | 2014-05-01 | 2018-06-06 | キヤノン株式会社 | 固体撮像装置及びその駆動方法 |

| JP5897752B1 (ja) * | 2015-05-14 | 2016-03-30 | ブリルニクスジャパン株式会社 | 固体撮像装置およびその駆動方法、電子機器 |

-

2015

- 2015-11-30 JP JP2015233675A patent/JP6663209B2/ja not_active Expired - Fee Related

-

2016

- 2016-11-23 US US15/360,833 patent/US10432880B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US10432880B2 (en) | 2019-10-01 |

| JP2017103537A (ja) | 2017-06-08 |

| US20170155857A1 (en) | 2017-06-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US20220329748A1 (en) | Comparator, ad converter, solid-state imaging device, electronic apparatus, and method of controlling comparator | |

| US10038868B2 (en) | Solid-state image sensing device and electronic device | |

| CN103139487B (zh) | 固态成像装置、成像系统和成像装置的驱动方法 | |

| KR101340112B1 (ko) | 고체 촬상 장치, 고체 촬상 장치의 구동 방법 및 촬상 장치 | |

| JP6776011B2 (ja) | 撮像装置及び撮像システム | |

| US9025064B2 (en) | Solid-state imaging device, imaging device, and signal readout method | |

| WO2016072289A1 (ja) | 撮像素子および駆動方法、並びに電子機器 | |

| JP5205155B2 (ja) | 固体撮像素子 | |

| US8004587B2 (en) | Solid-state imaging device, signal processing method for the same, and imaging apparatus | |

| CN102685405A (zh) | 固态成像器件及其驱动方法、成像装置以及电子设施 | |

| JP2015222885A (ja) | 撮像装置及びその駆動方法 | |

| JP5630991B2 (ja) | 撮像装置 | |

| JP6223000B2 (ja) | 撮像装置 | |

| JP2013051575A (ja) | 固体撮像装置、撮像装置および撮像方法 | |

| JP5475482B2 (ja) | 撮像素子及び撮像装置 | |

| JP6663209B2 (ja) | 撮像装置、撮像システム及び撮像装置の駆動方法 | |

| JP2012134666A (ja) | 固体撮像装置 | |

| CN103379292B (zh) | 信号处理设备及方法、成像设备和固态成像元件 | |

| JPH11261899A (ja) | 固体撮像装置 | |

| JP2006217421A (ja) | 固体撮像装置 | |

| US20210006742A1 (en) | Image sensor and timing controller thereof | |

| WO2012020520A1 (ja) | 固体撮像素子 | |

| JP2016092594A (ja) | 撮像装置及び固体撮像素子の駆動方法 | |

| JP2014064211A (ja) | 撮像素子及び撮像装置 | |

| JP2022170557A (ja) | Ad変換回路の駆動方法、ad変換回路、光電変換装置、機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD05 | Notification of revocation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7425 Effective date: 20171214 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20180126 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20181128 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20181128 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20190906 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20190919 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20191115 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20200116 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20200214 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 6663209 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| LAPS | Cancellation because of no payment of annual fees |