JP6602407B2 - 固体撮像装置及び撮像システム - Google Patents

固体撮像装置及び撮像システム Download PDFInfo

- Publication number

- JP6602407B2 JP6602407B2 JP2018002449A JP2018002449A JP6602407B2 JP 6602407 B2 JP6602407 B2 JP 6602407B2 JP 2018002449 A JP2018002449 A JP 2018002449A JP 2018002449 A JP2018002449 A JP 2018002449A JP 6602407 B2 JP6602407 B2 JP 6602407B2

- Authority

- JP

- Japan

- Prior art keywords

- pixel

- output line

- circuit

- selection circuit

- source follower

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Description

本発明の第1の実施形態について説明する。

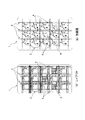

図1は、第1の実施形態による固体撮像装置の構成例を示す図である。固体撮像装置の画素アレイ(画素領域)1は、複数の画素回路2が2次元アレイ状(行列状)に配列されている。各画素回路2が設けられている領域を、単位画素領域とも称する。画素回路2は、例えばフォトダイオード(光電変換素子)PD、転送トランジスタTX、フローティングディフュージョン容量FD、ソースフォロワトランジスタ(増幅トランジスタ)SF、画素選択トランジスタSEL、及びリセットトランジスタRESを含む。

以上で説明したように、本実施例によれば、主垂直出力線3に接続される負荷容量を低減することが可能となり、高速な画素信号の読み出しが可能となる。

次に、本発明の第2の実施形態について説明する。

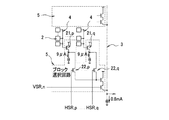

図3は、第2の実施形態による固体撮像装置の構成例を示す図である。図3において、図1に示した構成要素に対応する構成要素には同一の符号を付し、重複する説明は省略する。また、第2の実施形態による固体撮像装置の画素回路2及びブロック選択回路5の駆動方法は、第1の実施形態と同様であるので説明を省略する。

次に、本発明の第3の実施形態について説明する。

図4は、第3の実施形態による固体撮像装置の構成例を示す図である。図4において、図1に示した構成要素に対応する構成要素には同一の符号を付し、重複する説明は省略する。

次に、本発明の第4の実施形態について説明する。

図5は、第4の実施形態による固体撮像装置を説明するための図である。なお、図5においては、画像アレイ1内の主垂直出力線3、副垂直出力線4、及びブロック選択回路5と、垂直走査回路11のみを図示しているが、図示していない他の構成は第1の実施形態と同様である。

次に、本発明の第5の実施形態について説明する。

図7は、第5の実施形態による固体撮像装置を説明するための図である。なお、図7においては、画素アレイ1内の画素回路2、主垂直出力線3、副垂直出力線4、及びブロック選択回路5と、出力回路12を示している。また、第5の実施形態におけるブロック選択回路5の構成例を図8に示している。

次に、本発明の第6の実施形態について説明する。

図9は、第6の実施形態による固体撮像装置の構成例を示す図である。図9において、図1に示した構成要素に対応する構成要素には同一の符号を付し、重複する説明は省略する。

次に、本発明の第7の実施形態について説明する。

図10は、第7の実施形態による固体撮像装置の構成例を示す図である。図10において、図1、図9に示した構成要素に対応する構成要素には同一の符号を付し、重複する説明は省略する。

図11は、本発明の第8の実施形態による撮像システムの構成例を示す図である。撮像システム800は、例えば、光学部810、撮像素子100、映像信号処理回路部830、記録・通信部840、タイミング制御回路部850、システム制御部860、及び再生・表示部870を含む。撮像装置820は、撮像素子100及び映像信号処理回路部830を有する。撮像素子100は、前述の各実施形態で説明した撮像素子が用いられる。

Claims (9)

- 光電変換部と、前記光電変換部で生成した電荷に応じた信号を出力するソースフォロワ回路とが各々に設けられた複数の画素が行列状に配置された画素領域と、

第1の画素の前記ソースフォロワ回路に接続され、かつ、前記第1の画素と同じ列に配されている第2の画素の前記ソースフォロワ回路に接続された列方向に延在する第1の出力線と、

前記第2の画素と同じ列に配されている第3の画素の前記ソースフォロワ回路に接続され、かつ、前記第3の画素と同じ列に配されている第4の画素の前記ソースフォロワ回路に接続された前記列方向に延在する第2の出力線と、を有し、

前記第1の出力線は、第1の選択回路を介して、前記列方向に延在する第3の出力線と接続し、

前記第2の出力線は、第2の選択回路を介して、前記第3の出力線と接続し、

前記第1の選択回路および前記第2の選択回路は、平面視で前記画素領域に配されていることを特徴とする固体撮像装置。 - 光電変換部と、前記光電変換部で生成した電荷に応じた信号を出力するソースフォロワ回路とが各々に設けられた複数の画素が行列状に配置された画素領域と、

第1の画素の前記ソースフォロワ回路に接続され、かつ、前記第1の画素と同じ列に配されている第2の画素の前記ソースフォロワ回路に接続された第1の出力線と、

前記第2の画素と同じ列に配されている第3の画素の前記ソースフォロワ回路に接続され、かつ、前記第3の画素と同じ列に配されている第4の画素の前記ソースフォロワ回路に接続された第2の出力線と、

前記第1の出力線と前記第2の出力線の各々に設けられた複数の第1電流源と、

第3の出力線に設けられた第2電流源と、を有し、

前記第1の出力線は、第1の選択回路を介して、前記第3の出力線と接続し、

前記第2の出力線は、第2の選択回路を介して、前記第3の出力線と接続し、

前記第1の選択回路および前記第2の選択回路は、平面視で前記画素領域に配されていることを特徴とする固体撮像装置。 - 光電変換部と、前記光電変換部で生成した電荷に応じた信号を出力するソースフォロワ回路と、リセット部とが各々に設けられた複数の画素が行列状に配置された画素領域と、

第1の画素の前記ソースフォロワ回路に接続され、かつ、前記第1の画素と同じ列に配されている第2の画素の前記ソースフォロワ回路に接続された第1の出力線と、

前記第2の画素と同じ列に配されている第3の画素の前記ソースフォロワ回路に接続され、かつ、前記第3の画素と同じ列に配されている第4の画素の前記ソースフォロワ回路に接続された第2の出力線と、を有し、

前記第1の出力線は、第1の選択回路を介して、第3の出力線と接続し、

前記第2の出力線は、第2の選択回路を介して、前記第3の出力線と接続し、

前記第1の選択回路および前記第2の選択回路は、平面視で前記画素領域に配され、

前記ソースフォロワ回路は、前記光電変換部で生成した電荷を受ける制御ノードを備え、前記リセット部により前記制御ノードの電位を設定することにより、前記画素を選択状態又は非選択状態に切り替えることを特徴とする固体撮像装置。 - 前記第1の選択回路が、前記第1の画素に設けられ、かつ、前記第2の選択回路が、前記第3の画素に設けられることを特徴とする請求項1から3のいずれか1項に記載の固体撮像装置。

- 前記第1の選択回路は、前記第2の画素に設けられていないことを特徴とする請求項4に記載の固体撮像装置。

- 前記第2の画素内には、前記第1の出力線と前記第3の出力線とを接続していないダミーの選択回路が設けられることを特徴とする請求項5に記載の固体撮像装置。

- 前記第2の選択回路は、前記第4の画素に設けられておらず、前記第1の画素、前記第2の画素、前記第3の画素、前記第4の画素は、この順序で、列方向に配されていることを特徴とする請求項5に記載の固体撮像装置。

- 前記第1の選択回路又は前記第2の選択回路は、スイッチ回路又はバッファ回路を含むことを特徴とする請求項1から7のいずれか1項に記載の固体撮像装置。

- 請求項1から8のいずれか1項に記載の固体撮像装置と、

前記画素に光を集光させる光学部と、

前記固体撮像装置から出力された信号を処理する映像信号処理部とを有することを特徴とする撮像システム。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2018002449A JP6602407B2 (ja) | 2018-01-11 | 2018-01-11 | 固体撮像装置及び撮像システム |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2018002449A JP6602407B2 (ja) | 2018-01-11 | 2018-01-11 | 固体撮像装置及び撮像システム |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014033925A Division JP6274904B2 (ja) | 2014-02-25 | 2014-02-25 | 固体撮像装置及び撮像システム |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2018057048A JP2018057048A (ja) | 2018-04-05 |

| JP2018057048A5 JP2018057048A5 (ja) | 2019-01-24 |

| JP6602407B2 true JP6602407B2 (ja) | 2019-11-06 |

Family

ID=61837224

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018002449A Active JP6602407B2 (ja) | 2018-01-11 | 2018-01-11 | 固体撮像装置及び撮像システム |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6602407B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2020123795A (ja) * | 2019-01-30 | 2020-08-13 | ソニーセミコンダクタソリューションズ株式会社 | 固体撮像装置および電子機器 |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006345330A (ja) * | 2005-06-10 | 2006-12-21 | Hitachi Medical Corp | 撮像装置 |

| JP5500007B2 (ja) * | 2010-09-03 | 2014-05-21 | ソニー株式会社 | 固体撮像素子およびカメラシステム |

-

2018

- 2018-01-11 JP JP2018002449A patent/JP6602407B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2018057048A (ja) | 2018-04-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6274904B2 (ja) | 固体撮像装置及び撮像システム | |

| US9900482B2 (en) | Solid-state imaging element and camera system | |

| US8023025B2 (en) | Photoelectric conversion apparatus and image pickup system using the same | |

| JP4818018B2 (ja) | 光電変換装置及びそれを用いた撮像システム | |

| KR101204571B1 (ko) | 고체 촬상 장치, 고체 촬상 장치의 구동 방법 및 카메라 | |

| JP6946046B2 (ja) | 光電変換装置及びその駆動方法 | |

| KR102553988B1 (ko) | 고체 촬상 소자 및 촬상 장치 | |

| KR102389417B1 (ko) | 고체 촬상 소자 및 촬상 장치 | |

| JP5733536B2 (ja) | 固体撮像素子及びその駆動方法 | |

| JP6341675B2 (ja) | 固体撮像装置及びその駆動方法並びにそれを用いた撮像システム | |

| JP6445866B2 (ja) | 撮像装置、撮像システム、および撮像装置の駆動方法 | |

| WO2016052219A1 (ja) | 固体撮像装置、信号処理方法、及び、電子機器 | |

| JP6132500B2 (ja) | 撮像装置、撮像装置の駆動方法、および撮像システム。 | |

| JP4661212B2 (ja) | 物理情報取得方法および物理情報取得装置並びに半導体装置 | |

| JP6602407B2 (ja) | 固体撮像装置及び撮像システム | |

| JP2007166486A (ja) | 固体撮像装置 | |

| JP6532224B2 (ja) | 撮像装置、撮像システム、及び撮像装置の駆動方法 | |

| JP5177198B2 (ja) | 物理情報取得方法および物理情報取得装置 | |

| JP5523131B2 (ja) | 固体撮像装置 | |

| JP2020102816A (ja) | 撮像装置および撮像装置の制御方法 | |

| KR20060020230A (ko) | Cmos 이미지 센서 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180206 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20180206 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20181203 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20190222 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20190312 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190508 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20190910 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20191008 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 6602407 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |