JP6545902B2 - インダクタアセンブリおよびそれを用いる電力供給システム - Google Patents

インダクタアセンブリおよびそれを用いる電力供給システム Download PDFInfo

- Publication number

- JP6545902B2 JP6545902B2 JP2018515837A JP2018515837A JP6545902B2 JP 6545902 B2 JP6545902 B2 JP 6545902B2 JP 2018515837 A JP2018515837 A JP 2018515837A JP 2018515837 A JP2018515837 A JP 2018515837A JP 6545902 B2 JP6545902 B2 JP 6545902B2

- Authority

- JP

- Japan

- Prior art keywords

- phase

- terminal

- inductor

- inductor coil

- power supply

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 claims description 76

- 230000004907 flux Effects 0.000 claims description 65

- 230000010363 phase shift Effects 0.000 claims description 25

- 238000004804 winding Methods 0.000 claims description 22

- 230000007935 neutral effect Effects 0.000 claims description 14

- 230000001360 synchronised effect Effects 0.000 claims description 8

- 239000011888 foil Substances 0.000 claims description 4

- 238000009826 distribution Methods 0.000 description 11

- 230000008859 change Effects 0.000 description 9

- 239000000463 material Substances 0.000 description 9

- 238000010586 diagram Methods 0.000 description 7

- 230000008878 coupling Effects 0.000 description 6

- 238000010168 coupling process Methods 0.000 description 6

- 238000005859 coupling reaction Methods 0.000 description 6

- 230000001066 destructive effect Effects 0.000 description 6

- 239000003990 capacitor Substances 0.000 description 5

- 238000005259 measurement Methods 0.000 description 3

- 230000009467 reduction Effects 0.000 description 3

- 229910002601 GaN Inorganic materials 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 2

- 238000010276 construction Methods 0.000 description 2

- 238000011217 control strategy Methods 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- 238000001914 filtration Methods 0.000 description 2

- 230000014509 gene expression Effects 0.000 description 2

- 230000006698 induction Effects 0.000 description 2

- 238000009434 installation Methods 0.000 description 2

- 230000005415 magnetization Effects 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 2

- 229910010271 silicon carbide Inorganic materials 0.000 description 2

- 230000000087 stabilizing effect Effects 0.000 description 2

- 239000002028 Biomass Substances 0.000 description 1

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 230000002238 attenuated effect Effects 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000018109 developmental process Effects 0.000 description 1

- 239000003989 dielectric material Substances 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 239000000696 magnetic material Substances 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000000034 method Methods 0.000 description 1

- 229910003465 moissanite Inorganic materials 0.000 description 1

- 230000035699 permeability Effects 0.000 description 1

- 238000004382 potting Methods 0.000 description 1

- 238000010248 power generation Methods 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 230000006641 stabilisation Effects 0.000 description 1

- 238000011105 stabilization Methods 0.000 description 1

- 230000002123 temporal effect Effects 0.000 description 1

- 238000009827 uniform distribution Methods 0.000 description 1

- 238000011144 upstream manufacturing Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/14—Arrangements for reducing ripples from dc input or output

- H02M1/143—Arrangements for reducing ripples from dc input or output using compensating arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01F—MAGNETS; INDUCTANCES; TRANSFORMERS; SELECTION OF MATERIALS FOR THEIR MAGNETIC PROPERTIES

- H01F27/00—Details of transformers or inductances, in general

- H01F27/24—Magnetic cores

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01F—MAGNETS; INDUCTANCES; TRANSFORMERS; SELECTION OF MATERIALS FOR THEIR MAGNETIC PROPERTIES

- H01F27/00—Details of transformers or inductances, in general

- H01F27/28—Coils; Windings; Conductive connections

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01F—MAGNETS; INDUCTANCES; TRANSFORMERS; SELECTION OF MATERIALS FOR THEIR MAGNETIC PROPERTIES

- H01F37/00—Fixed inductances not covered by group H01F17/00

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M3/00—Conversion of dc power input into dc power output

- H02M3/02—Conversion of dc power input into dc power output without intermediate conversion into ac

- H02M3/04—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters

- H02M3/10—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M3/145—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal

- H02M3/155—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M7/00—Conversion of ac power input into dc power output; Conversion of dc power input into ac power output

- H02M7/42—Conversion of dc power input into ac power output without possibility of reversal

- H02M7/44—Conversion of dc power input into ac power output without possibility of reversal by static converters

- H02M7/48—Conversion of dc power input into ac power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M7/53—Conversion of dc power input into ac power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal

- H02M7/537—Conversion of dc power input into ac power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only, e.g. single switched pulse inverters

- H02M7/5387—Conversion of dc power input into ac power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only, e.g. single switched pulse inverters in a bridge configuration

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01F—MAGNETS; INDUCTANCES; TRANSFORMERS; SELECTION OF MATERIALS FOR THEIR MAGNETIC PROPERTIES

- H01F27/00—Details of transformers or inductances, in general

- H01F27/34—Special means for preventing or reducing unwanted electric or magnetic effects, e.g. no-load losses, reactive currents, harmonics, oscillations, leakage fields

- H01F27/38—Auxiliary core members; Auxiliary coils or windings

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Dc-Dc Converters (AREA)

- Inverter Devices (AREA)

Description

− 異なる相脚の上部磁気サブループおよび磁気メインループからの磁束が合流している中央脚の上方部分の上部、

− 異なる相脚の下部磁気サブループおよび磁気メインループからの磁束が合流している中央脚の下方部分の底部、および

− 異なる相脚の上部磁気サブループおよび下部磁気サブループからの磁束が合流している中央脚の中央点

である。

− DCリンクと、

− 電力供給システムの出力におけるn個の相端子であって、n個の相端子のそれぞれの1つは、DC/ACコンバータの対応する第1のハーフブリッジおよび対応する第2のハーフブリッジに接続される、n個の相端子と

をさらに含む。制御ユニットは、それぞれの相端子の対応する第1のハーフブリッジに対してインタリーブされた方式において、各相端子のための対応する第2のハーフブリッジを制御するように構成される。電力供給システムは、本発明によるインダクタアセンブリを含む出力フィルタをさらに含む。

− 入力電圧Vinを受け取るための入力と、

− 出力電圧Voutを供給するための出力と、

− 出力に並列に接続されたn個のスイッチングセルと

を含む。

− 互いに並列に接続された第1および第2のスイッチング経路であって、各スイッチング経路が第1の半導体スイッチおよび第2の半導体スイッチの直列接続ならびに第1の半導体スイッチと第2の半導体スイッチとの間の相互接続点を含む、第1および第2のスイッチング経路

を含む。電力供給システムは、

− 第2のスイッチング経路の第1の半導体スイッチに対してインタリーブされた方式で第1のスイッチング経路の第1の半導体スイッチを制御するように構成された制御ユニット

をさらに含む。電力供給システムは、

− n個のスイッチングセルのそれぞれの1つを入力に接続する、本発明によるインダクタアセンブリ

をさらに含み、n個のスイッチングセルのそれぞれの1つについて、

− 第1のスイッチング経路の相互接続点が上部インダクタコイルの第1の端子に接続され、および第2のスイッチング経路の相互接続点が下部インダクタコイルの第4の端子に接続されるように、

− n個のスイッチングセルのそれぞれの1つは、インダクタアセンブリの異なる対応する相脚と関連付けられ、かつその対応する相脚の上部コイルおよび下部コイルを介して入力に接続され、

− 上部インダクタコイルの第2の端子および下部インダクタコイルの第3の端子は、両方とも入力に接続される。

− 入力電圧Vinを受け取るための入力と、

− 出力電圧Voutを供給するための出力と、

− 入力に並列に接続されたn個のスイッチングセルと

を含む。

− 互いに並列に接続された第1および第2のスイッチング経路であって、各スイッチング経路は、第1の半導体スイッチおよび第2の半導体スイッチの直列接続ならびに第1の半導体スイッチと第2の半導体スイッチとの間の相互接続点を含む、第1および第2のスイッチング経路

を含む。電力供給システムは、

− 第2のスイッチング経路の第1の半導体スイッチに対してインタリーブされた方式で第1のスイッチング経路の第1の半導体スイッチを制御するように構成された制御ユニット

をさらに含む。電力供給システムは、

− n個のスイッチングセルのそれぞれの1つを出力に接続する、本発明によるインダクタアセンブリ

をさらに含み、n個のスイッチングセルのそれぞれの1つについて、

− 第1のスイッチング経路の相互接続点が上部インダクタコイルの第1の端子に接続され、および第2のスイッチング経路の相互接続点が下部インダクタコイルの第4の端子に接続されるように、

− n個のスイッチングセルのそれぞれの1つは、インダクタアセンブリの異なる対応する相脚と関連付けられ、かつその対応する相脚の上部コイルおよび下部コイルを介して出力に接続され、

− 上部インダクタコイルの第2の端子および下部インダクタコイルの第3の端子は、両方とも出力に接続される。

− 各スイッチングセルの第1の半導体スイッチは、制御ユニットによって実質的に同じクロック周波数で制御され、

− 同じスイッチングセルと関連付けられた第1の半導体スイッチは、互いに対して実質的に180°の位相シフトを含むインタリーブされた方式でクロックされ、

− 第1のスイッチングセルと関連付けられた任意の第1の半導体スイッチは、実質的に180/nまたは180°+180°/n(ここで、n=2またはn=3である)の位相シフトを含む第2のスイッチングセルの任意の第1の半導体スイッチに対してインタリーブされた方式でクロックされる。これは、すべての第1の半導体スイッチの位相シフトの均一な分布につながり、したがって電力供給システムの出力電圧Voutのリップルを最小化する。本発明の適用範囲内で、「実質的に」という副詞は、再び「実質的に」という副詞の後ろに述べた値の±5°の許容範囲に相当する。

− 第1のスイッチング経路65aの相互接続点68が上部インダクタコイル8の第1の端子20に接続され、および第2のスイッチング経路65bの相互接続点68が下部インダクタコイル9の第4の端子23に接続される

ように接続されている。加えて、上部インダクタコイル8の第2の端子21および下部インダクタコイル9の第3の端子22は、両方とも入力61に接続されている。

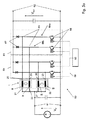

2 磁心

3 中央脚

4 相脚

5 中間点

6 シャント要素

7 ギャップ

8 上部インダクタコイル

9 下部インダクタコイル

10、11 相脚部

13 ブリッジ

15、16 ギャップ

20、21、22、23 端子

24、25、26、27 磁束

30 電力供給システム

31 DCリンク

32 出力

33 制御ユニット

34 出力フィルタ

35、37 出力

36、38 ハーフブリッジ

39、40、41 スイッチ

42、43、44 スイッチ

45 制御線

46 コンデンサ

47、48 電流センサ

50a、50b クロック信号

60 電力供給システム

61 入力

62 出力

63 制御ユニット

64 スイッチングセル

65a、65b スイッチング経路

66 半導体スイッチ

67 半導体スイッチ

68 相互接続点

69 制御線

Vin 入力電圧

Vout 出力電圧

I1、I2 電流

Φ、Φ1、Φ2 磁束

Claims (20)

- 中央脚(3)と、n個の相脚(4)(ここで、nは、整数かつn>1である)とを備えた磁心(2)を含むインダクタアセンブリ(1)において、

− 各相脚(4)は、上部ブリッジ(13)および下部ブリッジ(13)によって前記中央脚(3)に磁気的に接続されて磁気メインループを形成し、前記相脚(4)の中間点(5)は、ギャップ(7)を含むシャント要素(6)によって前記中央脚(3)の中央点に磁気的に接続され、

− 各相脚(4)は、前記中間点と前記上部ブリッジ(13)との間に位置している上部相脚部(10)に配設された上部インダクタコイル(8)と、前記中間点と前記下部ブリッジ(13)との間に位置している下部相脚部(11)に配設された下部インダクタコイル(9)とをさらに含み、または各相脚(4)は、前記上部ブリッジ(13)に配設された上部インダクタコイル(8)と、前記下部ブリッジ(13)に配設された下部インダクタコイル(9)とをさらに含み、

− 前記上部インダクタコイル(8)は、第1の端子(20)および第2の端子(21)を含み、前記下部インダクタコイル(9)は、第3の端子(22)および第4の端子(23)を含み、

− 前記上部インダクタコイル(8)の前記第2の端子(21)および前記下部インダクタコイル(9)の前記第3の端子(22)は、前記上部インダクタコイル(8)および前記下部インダクタコイル(9)の直列接続を形成するために互いに接続され、

− 前記下部インダクタコイル(9)の巻き方向に対する前記上部インダクタコイル(8)の巻き方向は、前記上部インダクタコイル(8)の前記第1の端子(20)から前記下部インダクタコイル(9)の前記第4の端子(23)へ流れる電流が、前記それぞれの相脚(4)内で建設的に重なり合っている、前記上部インダクタコイル(8)および前記下部インダクタコイル(9)のそれぞれの1つのための磁束(24、25)を発生させるようなものであることを特徴とするインダクタアセンブリ(1)。 - 請求項1に記載のインダクタアセンブリ(1)において、少なくとも1つの相脚(4)の前記上部相脚部(10)は、上部ギャップ(16)を含み、および前記少なくとも1つの相脚(4)の前記下部相脚部(11)は、下部ギャップ(15)を含むことを特徴とするインダクタアセンブリ(1)。

- 請求項2に記載のインダクタアセンブリ(1)において、前記上部ギャップ(16)の幅は、前記下部ギャップ(15)の幅と等しいことを特徴とするインダクタアセンブリ(1)。

- 請求項2または3に記載のインダクタアセンブリ(1)において、前記少なくとも1つの相脚(4)の前記シャント要素(6)に含まれるギャップ(7)の幅は、前記それぞれの相脚(4)の前記上部ギャップ(16)および/または前記下部ギャップ(15)の前記幅よりも少なくとも5倍大きいことを特徴とするインダクタアセンブリ(1)。

- 請求項1乃至4の何れか1項に記載のインダクタアセンブリ(1)において、nは、2または3に等しいことを特徴とするインダクタアセンブリ(1)。

- 請求項1乃至5の何れか1項に記載のインダクタアセンブリ(1)において、前記磁心(2)は、複数の磁心要素から組み立てられるように構成され、前記磁心要素の数および形状は、前記インダクタコイル(8、9)が、組立前に対応する相脚部(10、11)ならびに/または上部および下部ブリッジ(13)を形成する磁心要素上に設置可能であるように選択されることを特徴とするインダクタアセンブリ(1)。

- 請求項1乃至6の何れか1項に記載のインダクタアセンブリ(1)において、前記シャント要素(6)の前記ギャップ(7)は、前記中央脚(3)に隣接して配設されることを特徴とするインダクタアセンブリ(1)。

- 請求項1乃至6の何れか1項に記載のインダクタアセンブリ(1)において、前記シャント要素(6)の前記ギャップ(7)は、前記相脚(4)に隣接して配設されることを特徴とするインダクタアセンブリ(1)。

- 請求項1乃至8の何れか1項に記載のインダクタアセンブリ(1)において、前記中央脚(3)は、500μmより大きいギャップを含まないことを特徴とするインダクタアセンブリ(1)。

- 請求項1乃至9の何れか1項に記載のインダクタアセンブリ(1)において、前記インダクタコイル(8、9)の巻線は、ホイルベースの巻線およびワイヤベースの巻線の1つから選択されることを特徴とするインダクタアセンブリ(1)。

- DC/ACコンバータとして動作するように構成された電力供給システム(30)において、

− DCリンク(31)と、

− 出力(32)におけるn個の相端子(U、V、W)であって、前記n個の相端子(U、V、W)のそれぞれの1つは、前記DC/ACコンバータの対応する第1のハーフブリッジ(36)および対応する第2のハーフブリッジ(38)に接続される、n個の相端子(U、V、W)と、

− 前記対応する第1のハーフブリッジ(36)に対してインタリーブされた方式において、各相端子(U、V、W)のための前記対応する第2のハーフブリッジ(38)を制御するように構成された制御ユニット(33)と、

− 請求項1乃至10の何れか1項に記載のインダクタアセンブリ(1)を含む出力フィルタ(34)と

を含み、

− 各相端子(U、V、W)は、対応する相脚(4)の上部インダクタコイル(8)を介して前記対応する第1のハーフブリッジ(36)の出力(35)に接続され、かつ前記対応する相脚(4)の下部インダクタコイル(9)を介して前記対応する第2のハーフブリッジ(38)の出力(37)に接続され、

− 各相端子(U、V、W)について、前記対応する第1のハーフブリッジ(36)および前記対応する第2のハーフブリッジ(38)は、並列に前記DCリンク(31)に接続され、

− 前記インダクタアセンブリ(1)の各相脚(4)について、前記上部インダクタコイル(8)は、前記上部インダクタコイル(8)の第1の端子(20)で前記対応する第1のハーフブリッジ(36)の前記出力(35)に接続され、および前記下部インダクタコイル(9)は、前記下部インダクタコイル(9)の第4の端子(23)で前記対応する第2のハーフブリッジ(38)の前記出力(37)に接続され、

− 前記インダクタアセンブリ(1)の各相脚(4)について、前記上部インダクタコイル(8)の前記第2の端子(21)および前記下部インダクタコイル(9)の前記第3の端子(22)は、両方とも前記それぞれの相端子(U、V、W)に接続されることを特徴とする電力供給システム(30)。 - 請求項11に記載の電力供給システム(30)において、各相端子(U、V、W)について、前記対応する第2のハーフブリッジ(38)は、前記対応する第1のハーフブリッジ(36)に対してインタリーブされた方式でクロックされ、前記インタリーブされた方式は、180°±5°の位相差を含むことを特徴とする電力供給システム(30)。

- 請求項11または12に記載の電力供給システム(30)において、前記複数の第1および第2のハーフブリッジ(36、38)のそれぞれの1つは、単一のハイサイドスイッチ(39、42)および単一のローサイドスイッチ(40、43)を備えたトポロジを含むことを特徴とする電力供給システム(30)。

- 請求項11または12に記載の電力供給システム(30)において、前記複数の第1および第2のハーフブリッジ(36、38)のそれぞれの1つは、前記制御ユニット(33)によって実質的に同期した方式で制御される直列に接続された2つのハイサイドスイッチ(39、42)と、前記制御ユニット(33)によって実質的に同期した方式で制御される直列に接続された2つのローサイドスイッチ(40、43)とを備えたトポロジを含み、前記「実質的に同期した方式」は、0°±5°の位相差に相当することを特徴とする電力供給システム(30)。

- 請求項11乃至14の何れか1項に記載の電力供給システム(30)において、前記複数の第1および第2のハーフブリッジ(36、38)のすべては、中性点クランプ(NPC)および双方向スイッチ中性点クランプ(BSNPC)トポロジの1つである同一の回路トポロジを含むことを特徴とする電力供給システム(30)。

- 請求項11乃至15の何れか1項に記載の電力供給システム(30)において、前記電力供給システム(30)の出力(31)において2つの相端子(U、V)および中性端子(N)、または代替的に3つの相端子(U、V、W)および中性端子(N)を含むことを特徴とする電力供給システム(30)。

- 請求項11乃至16の何れか1項に記載の電力供給システム(30)において、前記複数の第1および第2のハーフブリッジ(36、38)のすべては、2レベル回路トポロジ、3レベル回路トポロジ、4レベル回路トポロジ、5レベル回路トポロジ、7レベル回路トポロジおよび9レベル回路トポロジの1つである同一の回路トポロジを含むことを特徴とする電力供給システム(30)。

- DC/DCコンバータとして動作するように構成された電力供給システム(60)において、

− 入力電圧Vinを受け取るための入力(61)と、

− 出力電圧Voutを供給するための出力(62)と、

− 前記出力(62)に並列に接続されたいくつかのn個のスイッチングセル(64)であって、前記n個のスイッチングセル(64)のそれぞれの1つは、

− 互いに並列に接続された第1および第2のスイッチング経路(65a、65b)であって、各スイッチング経路(65a、65b)が第1の半導体スイッチ(66)および第2の半導体スイッチ(67)の直列接続ならびに前記第1の半導体スイッチ(66)と前記第2の半導体スイッチ(67)との間の相互接続点(68)を含む、第1および第2のスイッチング経路(65a、65b)と、

− 前記第2のスイッチング経路(65b)の前記第1の半導体スイッチ(66)に対してインタリーブされた方式で前記第1のスイッチング経路(65a)の前記第1の半導体スイッチ(66)を制御するように構成された制御ユニット(63)と

を含む、いくつかのn個のスイッチングセル(64)と、

− 前記n個のスイッチングセル(64)のそれぞれの1つを前記入力(61)に接続する、請求項1乃至10の何れか1項に記載のインダクタアセンブリ(1)であって、前記n個のスイッチングセル(64)のそれぞれの1つについて、前記第1のスイッチング経路(65a)の前記相互接続点(68)が前記上部インダクタコイル(8)の前記第1の端子(20)に接続され、および前記第2のスイッチング経路(65b)の前記相互接続点(68)が前記下部インダクタコイル(9)の前記第4の端子(23)に接続されるように、前記n個のスイッチングセル(64)のそれぞれの1つは、前記インダクタアセンブリ(1)の異なる対応する相脚(4)に関連付けられ、かつ前記対応する相脚(4)の前記上部コイル(8)および前記下部コイル(9)を介して前記入力(61)に接続され、前記上部インダクタコイル(8)の前記第2の端子(21)および前記下部インダクタコイル(9)の前記第3の端子(22)は、両方とも前記入力(61)に接続される、インダクタアセンブリ(1)と

を含むことを特徴とする電力供給システム(60)。 - DC/DCコンバータとして動作するように構成された電力供給システム(60)において、

− 入力電圧Vinを受け取るための入力(61)と、

− 出力電圧Voutを供給するための出力(62)と、

− 前記入力(61)に並列に接続されたいくつかのn個のスイッチングセル(64)であって、前記n個のスイッチングセル(64)のそれぞれの1つは、

− 互いに並列に接続された第1および第2のスイッチング経路(65a、65b)であって、各スイッチング経路(65a、65b)は、第1の半導体スイッチ(66)および第2の半導体スイッチ(67)の直列接続ならびに前記第1の半導体スイッチ(66)と前記第2の半導体スイッチ(67)との間の相互接続点(68)を含む、第1および第2のスイッチング経路(65a、65b)と、

− 前記第2のスイッチング経路(65b)の前記第1の半導体スイッチ(66)に対してインタリーブされた方式で前記第1のスイッチング経路(65a)の前記第1の半導体スイッチ(66)を制御するように構成された制御ユニット(63)と

を含む、いくつかのn個のスイッチングセル(64)と、

− 前記n個のスイッチングセル(64)のそれぞれの1つを前記出力(62)に接続する、請求項1乃至10の何れか1項に記載のインダクタアセンブリ(1)であって、前記n個のスイッチングセル(64)のそれぞれの1つについて、前記第1のスイッチング経路(65a)の前記相互接続点(68)が前記上部インダクタコイル(8)の前記第1の端子(20)に接続され、および前記第2のスイッチング経路(65b)の前記相互接続点(68)が前記下部インダクタコイル(9)の前記第4の端子(23)に接続されるように、前記n個のスイッチングセル(64)のそれぞれの1つは、前記インダクタアセンブリ(1)の異なる対応する相脚(4)に関連付けられ、かつ前記対応する相脚(4)の前記上部コイル(8)および前記下部コイル(9)を介して前記出力(62)に接続され、前記上部インダクタコイル(8)の前記第2の端子(21)および前記下部インダクタコイル(9)の前記第3の端子(22)は、両方とも前記出力(62)に接続される、インダクタアセンブリ(1)と

を含むことを特徴とする電力供給システム(60)。 - 請求項18または19に記載の電力供給システム(60)において、2つまたは任意選択で3つのスイッチングセル(64)を含み、

− 各スイッチングセル(64)の前記第1の半導体スイッチ(66)は、前記制御ユニット(63)によって実質的に同じクロック周波数で制御され、

− 前記同じスイッチングセル(64)と関連付けられた前記第1の半導体スイッチ(66)は、互いに対して180°±5°の位相シフトを含むインタリーブされた方式でクロックされ、

− 第1のスイッチングセル(64)と関連付けられた任意の第1の半導体スイッチ(66)は、180°/n±5°または(180°+180°/n)±5°(ここで、n=2またはn=3である)の位相シフトを含む、第2のスイッチングセル(64)の任意の第1の半導体スイッチ(66)に対してさらにインタリーブされた方式でクロックされることを特徴とする電力供給システム(60)。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| EP15190215.2A EP3157022A1 (en) | 2015-10-16 | 2015-10-16 | Inductor assembly and power suppy system using the same |

| EP15190215.2 | 2015-10-16 | ||

| PCT/EP2016/073136 WO2017063889A1 (en) | 2015-10-16 | 2016-09-28 | Inductor assembly and power supply system using the same |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2018535540A JP2018535540A (ja) | 2018-11-29 |

| JP6545902B2 true JP6545902B2 (ja) | 2019-07-17 |

Family

ID=54359841

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018515837A Active JP6545902B2 (ja) | 2015-10-16 | 2016-09-28 | インダクタアセンブリおよびそれを用いる電力供給システム |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US10186950B2 (ja) |

| EP (2) | EP3157022A1 (ja) |

| JP (1) | JP6545902B2 (ja) |

| CN (1) | CN108140474B (ja) |

| PL (1) | PL3363031T3 (ja) |

| WO (1) | WO2017063889A1 (ja) |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2016098538A1 (ja) * | 2014-12-16 | 2016-06-23 | 三菱電機株式会社 | 絶縁型降圧コンバータ |

| US9923485B2 (en) * | 2015-11-05 | 2018-03-20 | Futurewei Technologies, Inc. | Multi-channel inverter systems |

| EP3562017B1 (en) * | 2016-12-22 | 2023-11-01 | Mitsubishi Electric Corporation | Power conversion device |

| CN108809079B (zh) * | 2017-05-05 | 2019-11-05 | 台达电子企业管理(上海)有限公司 | 功率变换器、电感元件以及电感切除控制方法 |

| CN107293389B (zh) * | 2017-07-03 | 2019-06-21 | 华为技术有限公司 | 集成电感 |

| JP6426796B1 (ja) * | 2017-07-07 | 2018-11-21 | ファナック株式会社 | 互いに嵌合する機構を備えた被覆部を有するリアクトル |

| JP6866324B2 (ja) * | 2018-03-01 | 2021-04-28 | 株式会社東芝 | インダクタユニット、非接触給電システムおよび電動車両 |

| JP6680820B2 (ja) * | 2018-03-20 | 2020-04-15 | ファナック株式会社 | 多段構造電磁機器 |

| US11676756B2 (en) | 2019-01-07 | 2023-06-13 | Delta Electronics (Shanghai) Co., Ltd. | Coupled inductor and power supply module |

| JP7126567B2 (ja) * | 2019-01-10 | 2022-08-26 | 三菱電機株式会社 | チョークコイルおよびそれを用いたノイズフィルタ |

| DE102019106472A1 (de) | 2019-03-14 | 2020-09-17 | Sma Solar Technology Ag | Wechselrichter mit mehreren DC/AC-Wandlern und einem gemeinsamen Sinusfilter und Energieerzeugungsanlage mit einem derartigen Wechselrichter |

| JP2022521856A (ja) * | 2019-03-27 | 2022-04-12 | エニュア,インコーポレイティド | 多相スイッチングレギュレータ |

| KR20210006640A (ko) | 2019-07-09 | 2021-01-19 | 엘지이노텍 주식회사 | 인덕터 및 이를 포함하는 직류 컨버터 |

| CN111711368B (zh) * | 2020-06-08 | 2023-06-20 | 北京达佳互联信息技术有限公司 | 电压变换装置和三相电压变换装置 |

| WO2022018098A2 (en) * | 2020-07-20 | 2022-01-27 | Eggtronic Engineering SpA | Improved performance of converter |

| CN114204836A (zh) * | 2021-10-11 | 2022-03-18 | 华为数字能源技术有限公司 | 一种逆变器和逆变装置 |

| KR102663472B1 (ko) * | 2021-10-26 | 2024-05-03 | 김상호 | 스위칭 손실 절감형 고승압 부스터 컨버터 |

Family Cites Families (52)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4122385A (en) * | 1975-11-28 | 1978-10-24 | The Charles Stark Draper Laboratory, Inc. | Saturable reactor current limiter |

| JPS54131055U (ja) * | 1978-03-03 | 1979-09-11 | ||

| JP2929694B2 (ja) * | 1990-10-02 | 1999-08-03 | 富士電機株式会社 | 三相多重電圧形pwmインバータ |

| US5485362A (en) * | 1993-09-08 | 1996-01-16 | Eos Corporation | Resonant power converter for changing the magnitude of a DC voltage |

| US5523673A (en) * | 1994-03-04 | 1996-06-04 | Marelco Power Systems, Inc. | Electrically controllable inductor |

| US6362986B1 (en) * | 2001-03-22 | 2002-03-26 | Volterra, Inc. | Voltage converter with coupled inductive windings, and associated methods |

| CN1257601C (zh) * | 2001-06-08 | 2006-05-24 | 台达电子工业股份有限公司 | 一种差模和共模集成滤波器 |

| US7034647B2 (en) * | 2001-10-12 | 2006-04-25 | Northeastern University | Integrated magnetics for a DC-DC converter with flexible output inductor |

| US7242275B2 (en) * | 2003-02-05 | 2007-07-10 | Paper Quality Management Associates | Variable inductor |

| US7479772B2 (en) * | 2005-02-25 | 2009-01-20 | The Regents Of The University Of Colorado | Active current sharing multiphase DC-DC converter |

| US20080074227A1 (en) * | 2006-09-21 | 2008-03-27 | Ford Global Technologies, Llc | Inductor topologies with substantial common-mode and differential-mode inductance |

| FI119491B (fi) * | 2006-10-20 | 2008-11-28 | Vacon Oyj | Taajuusmuuttajan suotokuristinjärjestely |

| US20080192960A1 (en) * | 2007-02-09 | 2008-08-14 | Nussbaum Michael B | Hybrid Filter for Audio Switching Amplifier |

| US7800924B2 (en) * | 2007-03-27 | 2010-09-21 | Eaton Corporation | Power converter apparatus and methods using neutral coupling circuits with interleaved operation |

| KR100983033B1 (ko) * | 2008-03-17 | 2010-09-17 | 삼성전기주식회사 | 집적화된 트랜스포머 및 이를 이용한 전원 장치 |

| EP2107672A1 (de) * | 2008-03-31 | 2009-10-07 | SMA Solar Technology AG | Dreiphasiger Wechselrichter ohne Verbindung zwischen dem Neutralleiter des Netzes und dem Mittelpunkt des Zwischenkreises |

| US7768373B2 (en) * | 2008-04-22 | 2010-08-03 | Cramer Coil & Transformer Co., Inc. | Common mode, differential mode three phase inductor |

| JP5081063B2 (ja) * | 2008-05-22 | 2012-11-21 | 本田技研工業株式会社 | 複合型変圧器、および電力変換回路 |

| GB2463503A (en) * | 2008-09-16 | 2010-03-17 | Cambridge Semiconductor Ltd | Crossed ridges in a gap of a ferrite core arrangement |

| US8648686B2 (en) * | 2009-11-05 | 2014-02-11 | Delta Electronics, Inc. | Resonant transformer and resonant converter employing same |

| CN101728968A (zh) * | 2010-01-19 | 2010-06-09 | 华为技术有限公司 | 一种磁集成双端变换器 |

| US20130200975A1 (en) * | 2010-02-12 | 2013-08-08 | Cramer Coil & Transformer Co. | Integrated common mode, differential mode audio filter inductor |

| US8610533B2 (en) * | 2011-03-31 | 2013-12-17 | Bose Corporation | Power converter using soft composite magnetic structure |

| EP2715922A2 (en) * | 2011-06-01 | 2014-04-09 | FH Joanneum GmbH | Inverter |

| DE102011051548A1 (de) * | 2011-07-04 | 2013-01-10 | Sma Solar Technology Ag | Betriebsverfahren für einen Wechselrichter und netzfehlertoleranter Wechselrichter |

| US20150003132A1 (en) * | 2012-01-12 | 2015-01-01 | Koninklijke Philips N.V. | Inverter with less snubber capacitors |

| TWI436380B (zh) * | 2012-02-01 | 2014-05-01 | Delta Electronics Inc | 磁性組件及其基座 |

| EP2624433A1 (en) * | 2012-02-03 | 2013-08-07 | ABB Research Ltd. | Non-isolated PV inverter system with ground current mitigation |

| JP5934001B2 (ja) * | 2012-03-16 | 2016-06-15 | サンケン電気株式会社 | Dc−dcコンバータ |

| US9093212B1 (en) * | 2012-05-01 | 2015-07-28 | Universal Lighting Technologies, Inc. | Stacked step gap core devices and methods |

| US20130301327A1 (en) * | 2012-05-14 | 2013-11-14 | General Electric Company | System and method of parallel converter current sharing |

| JP5885837B2 (ja) * | 2012-05-21 | 2016-03-16 | 株式会社テクノバ | 移動体用非接触給電トランス |

| US9472329B2 (en) * | 2012-08-15 | 2016-10-18 | Bruce W. Carsten | High leakage transformers with tape wound cores |

| KR101934446B1 (ko) * | 2012-09-10 | 2019-01-02 | 주식회사 솔루엠 | 자기 집적 회로 및 위상 천이에 의한 자속 밀도 감소 방법 |

| DE102012218512A1 (de) * | 2012-10-11 | 2014-04-17 | Robert Bosch Gmbh | Vorrichtung und Verfahren zum Laden eines elektrischen Energiespeichers aus einer dreiphasigen Wechselspannungsquelle |

| KR102098094B1 (ko) * | 2012-11-20 | 2020-05-29 | 엘지이노텍 주식회사 | 일체형 변압기 |

| US9281761B2 (en) * | 2013-01-18 | 2016-03-08 | General Electric Company | Control scheme for current balancing between parallel bridge circuits |

| US20140217827A1 (en) * | 2013-02-01 | 2014-08-07 | 3L Power Llc | Apparatus for and method of operation of a power inverter system |

| EP2773032A1 (en) * | 2013-03-01 | 2014-09-03 | GE Energy Power Conversion Technology Ltd | Current source converter with gate turn off semiconductor elements and a special commutation mode |

| US9252656B2 (en) * | 2013-03-12 | 2016-02-02 | XP Power Limited | Bridgeless interleaved power factor correction circuit using a PFC inductor with quad-winding on a single core |

| EP2959570B1 (en) | 2013-06-04 | 2021-02-03 | Huawei Technologies Co., Ltd. | Five-level pv inverter based on a multi-state switching cell |

| US9787217B2 (en) * | 2013-08-30 | 2017-10-10 | Huawei Technologies Co., Ltd. | Power conversion circuit and power conversion system |

| WO2015108613A1 (en) * | 2014-01-15 | 2015-07-23 | Abb Technology Ag | Interleaved multi-channel, multi-level, multi-quadrant dc-dc converters |

| JP5977773B2 (ja) * | 2014-02-24 | 2016-08-24 | 株式会社豊田中央研究所 | 複合磁気部品の使用方法および電源システム |

| TWI493579B (zh) * | 2014-04-16 | 2015-07-21 | Delta Electronics Inc | 具多氣隙之磁性組件 |

| US9876437B2 (en) * | 2014-09-26 | 2018-01-23 | Lenovo Enterprise Solutions (Singapore) Pte. Ltd. | Interleaved transformer/inductor |

| CN104967300B (zh) * | 2015-05-27 | 2018-04-10 | 阳光电源股份有限公司 | 一种预充电电路和光伏逆变器 |

| US20160352249A1 (en) * | 2015-06-01 | 2016-12-01 | Otis Elevator Company | Paralleled active front-end rectifiers with negligible common-mode |

| CN204808997U (zh) * | 2015-07-09 | 2015-11-25 | 台达电子企业管理(上海)有限公司 | 磁性组件及其适用的电源系统 |

| US10067175B2 (en) * | 2015-10-08 | 2018-09-04 | General Electric Company | Determining bond wire failures |

| US9874897B2 (en) * | 2016-05-03 | 2018-01-23 | Toyota Motor Engineering & Manufacturing North America, Inc. | Integrated inductor |

| US10110186B2 (en) * | 2016-05-04 | 2018-10-23 | Ut-Battelle, Llc | Harmonic filter for magnetic amplifier |

-

2015

- 2015-10-16 EP EP15190215.2A patent/EP3157022A1/en not_active Withdrawn

-

2016

- 2016-09-28 WO PCT/EP2016/073136 patent/WO2017063889A1/en active Application Filing

- 2016-09-28 CN CN201680060535.5A patent/CN108140474B/zh active Active

- 2016-09-28 PL PL16770963T patent/PL3363031T3/pl unknown

- 2016-09-28 EP EP16770963.3A patent/EP3363031B1/en active Active

- 2016-09-28 JP JP2018515837A patent/JP6545902B2/ja active Active

-

2018

- 2018-04-16 US US15/953,828 patent/US10186950B2/en active Active

- 2018-08-21 US US16/106,430 patent/US10326353B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| CN108140474B (zh) | 2020-02-07 |

| CN108140474A (zh) | 2018-06-08 |

| US10326353B2 (en) | 2019-06-18 |

| WO2017063889A1 (en) | 2017-04-20 |

| PL3363031T3 (pl) | 2019-10-31 |

| EP3157022A1 (en) | 2017-04-19 |

| JP2018535540A (ja) | 2018-11-29 |

| US20190006936A1 (en) | 2019-01-03 |

| US10186950B2 (en) | 2019-01-22 |

| US20180234008A1 (en) | 2018-08-16 |

| EP3363031B1 (en) | 2019-03-06 |

| EP3363031A1 (en) | 2018-08-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6545902B2 (ja) | インダクタアセンブリおよびそれを用いる電力供給システム | |

| JP4727882B2 (ja) | 電気エネルギーを変換するためのコンバータ | |

| US9728324B2 (en) | Transformer construction | |

| CN103782355B (zh) | 集成磁性元件 | |

| US7847535B2 (en) | Method and device for supply to a magnetic coupler | |

| JP5254337B2 (ja) | 電力変換装置 | |

| JP2009170620A (ja) | 多並列磁気相殺型変圧器及び電力変換回路 | |

| US8390414B2 (en) | Multi-phase transformer | |

| US8441150B2 (en) | Device for connection to an impedance having a mainly inductive character | |

| WO2021053166A1 (en) | Current balancing in power semiconductors of a dc/dc converter | |

| US20120075051A1 (en) | Magnetic Devices and Transformer Circuits Made Therewith | |

| JP7295914B2 (ja) | 一体型コア本体を有する三相磁気アセンブリ | |

| WO2010136033A1 (en) | Converter system for a wind turbine | |

| JP2004201360A (ja) | コンバータ装置 | |

| WO2012008889A1 (en) | A multiphase transformer rectifier unit | |

| ES2950832T3 (es) | Convertidor de potencia | |

| EP3672047A1 (en) | Coupled inductor component with integrated current balancing transformer | |

| Harasimczuk et al. | Common-leg Coupled Inductor Configuration in a Three-level Interleaved DC-DC Medium Voltage SiC-based Converter | |

| CN118116705A (zh) | 变压器组件和电力转换装置 | |

| CN117175946A (zh) | 电力转换装置的控制装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20190530 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20190611 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20190619 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6545902 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |