JP6518890B2 - 表示装置および電子機器 - Google Patents

表示装置および電子機器 Download PDFInfo

- Publication number

- JP6518890B2 JP6518890B2 JP2014071920A JP2014071920A JP6518890B2 JP 6518890 B2 JP6518890 B2 JP 6518890B2 JP 2014071920 A JP2014071920 A JP 2014071920A JP 2014071920 A JP2014071920 A JP 2014071920A JP 6518890 B2 JP6518890 B2 JP 6518890B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- transistor

- pixel

- display device

- display

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/131—Interconnections, e.g. wiring lines or terminals

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/481—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs integrated with passive devices, e.g. auxiliary capacitors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/123—Connection of the pixel electrodes to the thin film transistors [TFT]

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Electroluminescent Light Sources (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Control Of El Displays (AREA)

Description

本開示の第2の表示装置は、それぞれが表示素子を含み2次元配置された複数の画素を有する画素部と、複数の回路要素を有し、複数の画素を表示駆動する駆動回路部とを備え、基板上に、駆動回路部を含む第1層と、画素部を含む第2層とがこの順に積層され、複数の回路要素は、第1層内に分散して設けられ、第1層と第2層とは、互いに積層方向に沿って連通する光透過部を有し、第1層に形成されたトランジスタと、第2層に形成されたトランジスタとは、いずれも低温ポリシリコンを含むものである。

本開示の第3の表示装置は、それぞれが表示素子を含み2次元配置された複数の画素を有する画素部と、複数の画素を表示駆動する駆動回路部とを備え、基板上に、駆動回路部を含む第1層と、画素部を含む第2層とがこの順に積層され、第1層と第2層とは、互いに積層方向に沿って連通する光透過部を有し、第1層に形成されたトランジスタは、低温ポリシリコンを含み、第2層に形成されたトランジスタは、酸化物半導体を含み、画素部は、画素トランジスタとして、書き込みトランジスタと駆動トランジスタとを含み、書き込みトランジスタが第1層に形成され、駆動トランジスタが第2層に形成されているものである。

本開示の第4の表示装置は、それぞれが表示素子を含み2次元配置された複数の画素を有する画素部と、複数の画素を表示駆動する駆動回路部とを備え、基板上に、駆動回路部を含む第1層と、画素部を含む第2層とがこの順に積層され、第1層と第2層とは、互いに積層方向に沿って連通する光透過部を有し、第1層に形成されたトランジスタと、第2層に形成されたトランジスタとは、いずれも低温ポリシリコンを含み、画素部は、画素トランジスタとして、書き込みトランジスタと駆動トランジスタとを含み、書き込みトランジスタが第1層に形成され、駆動トランジスタが第2層に形成されているものである。

1.第1の実施の形態(回路部がパネルの3辺に対応する領域において画素部と積層して設けられた表示装置の例)

2.変形例1(回路部の構成要素が分散して設けられた例)

3.変形例2(走査線駆動回路がパネルの1辺に集約して設けられた例)

4.第2の実施の形態(透明ディスプレイに用いられる表示装置の例)

5.変形例3(他の発光方式(ボトムエミッション方式)の表示装置の例)

6.第3の実施の形態(書き込みトランジスタが回路部と同層に設けられた例)

7.変形例4(第1電極と駆動トランジスタとの接続層を省略した例)

8.変形例5(端面封止の好適例)

9.適用例(電子機器の例)

[構成]

図1は、本開示の第1の実施の形態に係る表示装置(表示装置1)の全体構成を表すものである。この表示装置1は、有機ELディスプレイなどとして用いられるものである。表示装置1は、例えば、マトリクス状に2次元配置された複数の画素PXLCを含む画素部(画素部110A)と、画素部110Aを表示駆動するための駆動回路部(回路部110B)とを備えている。画素PXLCは、例えば赤(R),緑(G),青(B),白(W)の4色のサブピクセルのいずれかに相当し、これらの4色の画素PXLCの組を1ピクセルとして画像が表示される。

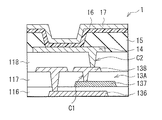

第1層F1は、回路部110Bとして複数の回路要素を含み、積層部B1には、各種素子(トランジスタおよび容量素子など)が形成される。但し、図4には、一例としてトランジスタ13Bのみを図示している。トランジスタ13Bは、駆動側基板11上に、ゲート電極131と、半導体層132と、電極層133とを有している。ゲート電極131と半導体層132の間には、ゲート絶縁膜111が、半導体層132と電極層133との間には、層間絶縁膜112が、それぞれ形成されている。電極層133上には層間絶縁膜113が形成されている。なお、本実施の形態では、第1層F1内の積層部B1以外の領域(図3A中の領域110C)には、電源線配線などの配線層134が配置されている。

第2層F2は、画素部110Aとして複数の画素PXLCを含み、第1層F1の全域にわたって、上述した構成要素(有機EL素子10,キャパシタCs,書き込みトランジスタWSTr,駆動トランジスタDRTr)が形成されている。但し、図4には、画素PXLCの一部の構成要素であるトランジスタ13A(上記の駆動トランジスタDRTrに相当)と、有機EL素子10のみを図示している。

本実施の形態の表示装置1では、第1電極14と第2電極17とを介して有機層16に駆動電流が供給されると、有機電界発光素子10において色光(例えば白色光)が発生する。この白色光が、第2電極17、樹脂層18、BM/CF層19および封止基板12を透過することにより、光LR,LG,LB,LWとして上方へ出射される。このようにして画像表示がなされる。

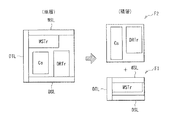

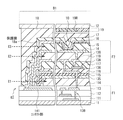

図6は、上記第1の実施の形態の変形例(変形例1)に係る表示装置(表示装置1A)の画素部110Aと回路部110Bとのレイアウトを説明するための平面模式図である。図7は、図6のIA−IA線における矢視断面図である。上記第1の実施の形態では、回路部110Bが第1層F1において、選択的な領域(矩形状の3辺に対応する領域)に偏って配置される場合について説明したが、回路部110Bのレイアウトはこれに限定されない。例えば、本変形例のように、回路部110Bを構成する複数の回路要素が第1層F1内に分散して配置されていてもよい。換言すると、第1層F1の全域にわたって回路部110Bが形成され、表示領域Aの全域が、画素部110Aと回路部110Bとが積層される積層部B2となっている。

図9は、上記第1の実施の形態の変形例(変形例2)に係る表示装置(表示装置1B)の画素部110Aと回路部110Bとのレイアウトを説明するための平面模式図である。図10は、図9のIB−IB線における矢視断面図である。上記第1の実施の形態では、回路部110Bが第1層F1において、選択的な領域(矩形状の3辺に対応する領域)に偏って配置される場合について説明したが、回路部110Bのレイアウトはこれに限定されない。例えば、本変形例のように、回路部110Bを構成する複数の回路要素が第1層F1において、矩形状の2辺に対応する領域に配置されていてもよい。具体的には、回路部110Bのうち走査線駆動回路130が、矩形状の1辺に集約して設けられている。この場合にも、第1層F1のうち、画素部110Aと回路部110Bとの積層部B1以外の領域110Cには、上記第1の実施の形態と同様、配線層134を形成することができる。その一例を、図11に示す。あるいは、領域110Cには、上述したような機能素子が形成されていてもよい。

上記第1の実施の形態において説明したように、画素部110Aと回路部110Bとの積層(第1層F1と第2層F2との積層)により、第1層F1におけるレイアウトの自由度が高まり、回路部110Bを分散して配置することが可能となる。このような回路部110Bの分散配置を利用して、例えば、光透過性を有し、背面側の景色が透けて見えるような透明ディスプレイを実現可能となる。

図18は、上記第1,第2の実施の形態の変形例(変形例3)に係る表示装置(表示装置2A)の断面構成を表したものである。上記実施の形態等では、トップエミッション方式の有機EL素子10を用いた表示装置を例に挙げて説明したが、本変形例のように、ボトムエミッション方式(下面発光方式)の有機EL素子(有機EL素子20)が用いられてもよい。本変形例の表示装置2Aでは、第1層F1において、上記変形例1および第2の実施の形態と同様、回路部110Bが分散配置され、回路要素同士の間隙を光(発光光、あるいは発光光および透過光)が通るように構成される。有機EL素子20は、第1電極22と第2電極23との間に有機層16を有している。有機EL素子20(発光部E2)が、トランジスタ13A,13Bに非重畳となるように形成されている。第1電極22は、ITOなどの透明導電膜により構成され、画素間絶縁膜15によって画素毎に電気的に分離されている。第2電極23は、反射電極であり、例えば上記第1の実施の形態の第1電極14と同様の材料により構成されている。カラーフィルタ(赤色フィルタ24R,緑色フィルタ24G,青色フィルタ24B)は、第1電極22よりも下層に形成され、いわゆるオンチップカラーフィルタ(OCCF)となっている。

図19は、本開示の第3の実施の形態の表示装置(表示装置3)の断面構成を表したものである。本実施の形態においても、上記第1の実施の形態と同様、回路部110Bを含む第1層F1と、画素部110Aを含む第2層F2とが積層されている。また、回路部110Bと画素部110Aとは、積層部B1において重畳する。但し、本実施の形態では、上記第1の実施の形態と異なり、画素PXLCのうちの一部が、第2層F2ではなく第1層F1に形成されている。例えば、書き込みトランジスタWsTrに相当するトランジスタ13Cが第1層F1に形成されている。第2層F2には、駆動トランジスタDRTrに相当するトランジスタ13Aが、トランジスタ13Cに平面視的に重畳するように形成されている。トランジスタ13Aとトランジスタ13Cとは、平坦化膜114等を介して層間接続されている。

図25は、上記第3の実施の形態の変形例(変形例4)に係る表示装置(表示装置3A)の断面構成を表したものである。本変形例では、画素部110Aにおいて、有機EL素子10の第1電極(第1電極14A)が、駆動トランジスタDRTrに相当するトランジスタ(トランジスタ13A1)のソース・ドレイン電極を兼ねている。換言すると、第1電極14Aとトランジスタ13A1との間の接続層(図4に示したソース・ドレイン電極138に相当)が省略されており、上記第1の実施の形態よりも簡易な層構造となっている。詳細には、本変形例では、上記第1の実施の形態における層間絶縁膜117とソース・ドレイン電極138とが省略され、半導体層137に第1電極14Aが直接に接続されることで、プロセス工程数が削減される。この理由について、以下に説明する。

図30は、上記実施の形態等の変形例(変形例5)に係る表示装置の端面付近の断面構成を表したものである。上記実施の形態等の表示装置は、第1層F1と第2層F2との積層構造を有するが、この積層構造は、本変形例のように、端面e1において無機絶縁膜あるいは金属膜などにより覆われていることが望ましい。具体的には、駆動側基板11上には、第1層F1、平坦化膜114、シールド層135、層間絶縁膜115および第2層F2がこの順に形成されている。第2層F2の上に、樹脂層18およびBM/CF層19を介して封止基板12が貼り合わせられている。

以下、上記実施の形態等で説明した表示装置の適用例について説明する。上記実施の形態の表示装置は、テレビジョン装置,デジタルカメラ,ノート型パーソナルコンピュータ、携帯電話等の携帯端末装置,ビデオカメラ,スマートフォン,タブレット型ディスプレイなど、外部から入力された映像信号あるいは内部で生成した映像信号を、画像あるいは映像として表示するあらゆる分野の電子機器の表示装置に適用することが可能である。特に、中小型のディスプレイあるいは透明ディスプレイに好適である。以下にその一例を示す。

(1)

それぞれが表示素子を含み2次元配置された複数の画素を有する画素部と、

前記複数の画素を表示駆動する駆動回路部と

を備え、

前記駆動回路部を含む第1層と、前記画素部を含む第2層とが積層されている

表示装置。

(2)

基板上に、前記第1層と前記第2層とがこの順に形成されている

上記(1)に記載の表示装置。

(3)

前記駆動回路部は、複数の回路要素を有し、

前記複数の回路要素は、前記第1層内に分散して設けられている

上記(1)または(2)に記載の表示装置。

(4)

前記第1層と前記第2層とは、互いに積層方向に沿って連通する光透過部を有する

上記(1)〜(3)のいずれかに記載の表示装置。

(5)

前記駆動回路部は、複数の回路要素を有し、

前記複数の回路要素は、前記第1層内に分散して設けられ、

前記光透過部は、前記複数の回路要素同士の間隙に形成されている

上記(4)に記載の表示装置。

(6)

前記駆動回路部は、複数の回路要素を有し、

前記複数の回路要素は、前記第1層のうちの選択的な第1の領域に設けられている

上記(1)〜(5)のいずれかに記載の表示装置。

(7)

前記第1層のうちの他の選択的な第2の領域に、配線層が形成されている

上記(6)に記載の表示装置。

(8)

前記第1層のうちの他の選択的な第2の領域に、機能素子が形成されている

上記(6)または(7)に記載の表示装置。

(9)

前記画素部は平面視的に矩形状を成し、

前記第1の領域は、前記矩形状の少なくとも1辺に対応する領域である

上記(6)〜(8)のいずれかに記載の表示装置。

(10)

前記画素部に形成されたトランジスタと、前記回路部に形成されたトランジスタとは、平面視的に重畳して形成されている

上記(1)〜(9)のいずれかに記載の表示装置。

(11)

前記画素部は複数の画素トランジスタを含み、

前記複数の画素トランジスタのうちの1つが、前記第1層に形成されている

上記(1)〜(10)のいずれかに記載の表示装置。

(12)

前記画素部は、前記画素トランジスタとして、書き込みトランジスタと駆動トランジスタとを含み、

前記書き込みトランジスタが前記第1層に形成され、前記駆動トランジスタが前記第2層に形成されている

上記(11)に記載の表示装置。

(13)

前記表示素子の電極は、前記駆動トランジスタのソース・ドレイン電極を兼ねている

上記(12)に記載の表示装置。

(14)

前記第1層に形成されたトランジスタは、低温ポリシリコンを含み、

前記第2層に形成されたトランジスタは、酸化物半導体を含む

上記(2)〜(13)のいずれかに記載の表示装置。

(15)

前記第1層に形成されたトランジスタと、前記第2層に形成されたトランジスタとは、いずれも酸化物半導体を含む

上記(2)〜(13)のいずれかに記載の表示装置。

(16)

前記第1層に形成されたトランジスタと、前記第2層に形成されたトランジスタとは、いずれも低温ポリシリコンを含む

上記(2)〜(13)のいずれかに記載の表示装置。

(17)

前記第1層に形成されたトランジスタは、酸化物半導体を含み、

前記第2層に形成されたトランジスタは、低温ポリシリコンを含む

上記(2)〜(13)のいずれかに記載の表示装置。

(18)

前記第1層と前記第2層との間に、シールド層が設けられている

上記(1)〜(17)のいずれかに記載の表示装置。

(19)

前記表示素子は有機電界発光素子である

上記(1)〜(18)のいずれかに記載の表示装置。

(20)

それぞれが表示素子を含み2次元配置された複数の画素を有する画素部と、

前記複数の画素を表示駆動する駆動回路部と

を備え、

前記駆動回路部を含む第1層と、前記画素部を含む第2層とが積層されている

表示装置を備えた電子機器。

Claims (8)

- それぞれが表示素子を含み2次元配置された複数の画素を有する画素部と、

前記複数の画素を表示駆動する駆動回路部と

を備え、

基板上に、前記駆動回路部を含む第1層と、前記画素部を含む第2層とがこの順に積層され、

前記第1層と前記第2層とは、互いに積層方向に沿って連通する光透過部を有し、

前記第1層に形成されたトランジスタは、低温ポリシリコンを含み、

前記第2層に形成されたトランジスタは、酸化物半導体を含み、

前記画素部は、画素トランジスタとして、書き込みトランジスタと駆動トランジスタとを含み、

前記書き込みトランジスタが前記第1層に形成され、前記駆動トランジスタが前記第2層に形成されている

表示装置。 - それぞれが表示素子を含み2次元配置された複数の画素を有する画素部と、

前記複数の画素を表示駆動する駆動回路部と

を備え、

基板上に、前記駆動回路部を含む第1層と、前記画素部を含む第2層とがこの順に積層され、

前記第1層と前記第2層とは、互いに積層方向に沿って連通する光透過部を有し、

前記第1層に形成されたトランジスタと、前記第2層に形成されたトランジスタとは、いずれも低温ポリシリコンを含み、

前記画素部は、画素トランジスタとして、書き込みトランジスタと駆動トランジスタとを含み、

前記書き込みトランジスタが前記第1層に形成され、前記駆動トランジスタが前記第2層に形成されている

表示装置。 - 前記表示素子の電極は、前記駆動トランジスタのソース・ドレイン電極を兼ねている

請求項1または請求項2に記載の表示装置。 - 前記第1層と前記第2層との間に、シールド層が設けられている

請求項1ないし請求項3のうちいずれか1項に記載の表示装置。 - 前記シールド層は、レーザ光遮蔽機能を有する

請求項4に記載の表示装置。 - 前記表示素子は有機電界発光素子である

請求項1ないし請求項5のうちいずれか1項に記載の表示装置。 - それぞれが表示素子を含み2次元配置された複数の画素を有する画素部と、

前記複数の画素を表示駆動する駆動回路部と

を備え、

基板上に、前記駆動回路部を含む第1層と、前記画素部を含む第2層とがこの順に積層され、

前記第1層と前記第2層とは、互いに積層方向に沿って連通する光透過部を有し、

前記第1層に形成されたトランジスタは、低温ポリシリコンを含み、

前記第2層に形成されたトランジスタは、酸化物半導体を含み、

前記画素部は、画素トランジスタとして、書き込みトランジスタと駆動トランジスタとを含み、

前記書き込みトランジスタが前記第1層に形成され、前記駆動トランジスタが前記第2層に形成されている

表示装置を備えた電子機器。 - それぞれが表示素子を含み2次元配置された複数の画素を有する画素部と、

複数の回路要素を有し、前記複数の画素を表示駆動する駆動回路部と

を備え、

基板上に、前記駆動回路部を含む第1層と、前記画素部を含む第2層とがこの順に積層され、

前記複数の回路要素は、前記第1層内に分散して設けられ、

前記第1層と前記第2層とは、互いに積層方向に沿って連通する光透過部を有し、

前記第1層に形成されたトランジスタと、前記第2層に形成されたトランジスタとは、いずれも低温ポリシリコンを含み、

前記画素部は、画素トランジスタとして、書き込みトランジスタと駆動トランジスタとを含み、

前記書き込みトランジスタが前記第1層に形成され、前記駆動トランジスタが前記第2層に形成されている

表示装置を備えた電子機器。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014071920A JP6518890B2 (ja) | 2014-03-31 | 2014-03-31 | 表示装置および電子機器 |

| US14/662,449 US9564482B2 (en) | 2014-03-31 | 2015-03-19 | Display device and electronic apparatus |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014071920A JP6518890B2 (ja) | 2014-03-31 | 2014-03-31 | 表示装置および電子機器 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2015194577A JP2015194577A (ja) | 2015-11-05 |

| JP2015194577A5 JP2015194577A5 (ja) | 2017-02-23 |

| JP6518890B2 true JP6518890B2 (ja) | 2019-05-29 |

Family

ID=54191507

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014071920A Active JP6518890B2 (ja) | 2014-03-31 | 2014-03-31 | 表示装置および電子機器 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9564482B2 (ja) |

| JP (1) | JP6518890B2 (ja) |

Families Citing this family (40)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102335214B1 (ko) * | 2014-11-18 | 2021-12-06 | 삼성디스플레이 주식회사 | 표시 패널 |

| KR102421010B1 (ko) * | 2015-01-09 | 2022-07-14 | 삼성디스플레이 주식회사 | 유기 발광 표시 장치 |

| CN104749850B (zh) * | 2015-04-17 | 2017-11-07 | 京东方科技集团股份有限公司 | 电致变色显示面板及其驱动方法、显示装置 |

| JP6815122B2 (ja) | 2015-08-07 | 2021-01-20 | 株式会社半導体エネルギー研究所 | 表示パネル |

| WO2017055971A1 (en) | 2015-10-01 | 2017-04-06 | Semiconductor Energy Laboratory Co., Ltd. | Display device and manufacturing method thereof |

| WO2017068454A1 (en) | 2015-10-23 | 2017-04-27 | Semiconductor Energy Laboratory Co., Ltd. | Display panel, input/output device, and data processing device |

| WO2017115214A1 (en) | 2015-12-28 | 2017-07-06 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and display device including the semiconductor device |

| US9905579B2 (en) * | 2016-03-18 | 2018-02-27 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and display device including the semiconductor device |

| JP6668455B2 (ja) | 2016-04-01 | 2020-03-18 | 株式会社半導体エネルギー研究所 | 酸化物半導体膜の作製方法 |

| CN113948560A (zh) | 2016-04-22 | 2022-01-18 | 索尼公司 | 显示装置与电子设备 |

| US10043858B2 (en) | 2016-04-27 | 2018-08-07 | Semiconductor Energy Laboratory Co., Ltd. | Display device and manufacturing method thereof |

| KR102632616B1 (ko) * | 2016-06-27 | 2024-02-02 | 삼성디스플레이 주식회사 | 디스플레이 장치 |

| KR102675912B1 (ko) * | 2016-06-30 | 2024-06-17 | 엘지디스플레이 주식회사 | 백플레인 기판과 이의 제조 방법 및 이를 적용한 유기 발광 표시 장치 |

| KR102655677B1 (ko) * | 2016-07-04 | 2024-04-11 | 티씨엘 차이나 스타 옵토일렉트로닉스 테크놀로지 컴퍼니 리미티드 | 표시 장치 |

| TWI709791B (zh) * | 2016-07-07 | 2020-11-11 | 日商半導體能源研究所股份有限公司 | 顯示裝置及電子裝置 |

| US10541375B2 (en) | 2016-07-21 | 2020-01-21 | Semiconductor Energy Laboratory Co., Ltd. | Display device and electronic device |

| US10586495B2 (en) * | 2016-07-22 | 2020-03-10 | Semiconductor Energy Laboratory Co., Ltd. | Display device and electronic device |

| KR102458660B1 (ko) | 2016-08-03 | 2022-10-26 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시 장치 및 전자 기기 |

| JP6916794B2 (ja) * | 2016-08-17 | 2021-08-11 | 株式会社半導体エネルギー研究所 | 表示装置 |

| US10475869B2 (en) * | 2016-08-23 | 2019-11-12 | Semiconductor Energy Laboratory Co., Ltd. | Display device including display element and transistor |

| US10163984B1 (en) * | 2016-09-12 | 2018-12-25 | Apple Inc. | Display with embedded components and subpixel windows |

| KR102467221B1 (ko) * | 2017-12-18 | 2022-11-14 | 엘지디스플레이 주식회사 | 멀티 뷰 디스플레이장치 |

| KR102630641B1 (ko) * | 2018-01-25 | 2024-01-30 | 삼성디스플레이 주식회사 | 표시장치 및 그의 제조방법 |

| JP7293589B2 (ja) * | 2018-08-29 | 2023-06-20 | 富士フイルムビジネスイノベーション株式会社 | 発光装置、光計測装置、画像形成装置及び発光デバイス |

| KR102539517B1 (ko) * | 2018-10-11 | 2023-06-02 | 엘지디스플레이 주식회사 | 센싱 구동 회로, 디스플레이 패널 및 디스플레이 장치 |

| KR102612390B1 (ko) * | 2018-12-19 | 2023-12-12 | 엘지디스플레이 주식회사 | 표시 패널 및 표시 장치 |

| US11228005B2 (en) * | 2019-01-11 | 2022-01-18 | Joled Inc. | Organic el display panel having dummy light emitting layers and method for manufacturing organic el display panel having dummy light emitting layers |

| KR20210130724A (ko) * | 2019-02-22 | 2021-11-01 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 안경형 전자 기기 |

| US11710760B2 (en) * | 2019-06-21 | 2023-07-25 | Semiconductor Energy Laboratory Co., Ltd. | Display device, display module, electronic device, and manufacturing method of display device |

| KR102805320B1 (ko) * | 2019-08-20 | 2025-05-13 | 삼성디스플레이 주식회사 | 표시 장치 및 그의 제조 방법 |

| KR20210052635A (ko) * | 2019-10-29 | 2021-05-11 | 삼성디스플레이 주식회사 | 디스플레이 장치 |

| CN113497093B (zh) * | 2020-04-02 | 2022-11-08 | 昆山国显光电有限公司 | 显示面板以及显示装置 |

| CN113871417B (zh) | 2020-06-30 | 2025-07-04 | 京东方科技集团股份有限公司 | 显示基板和显示装置 |

| KR102918335B1 (ko) * | 2020-12-22 | 2026-01-27 | 엘지디스플레이 주식회사 | 게이트 구동부 및 이를 포함하는 표시 장치 |

| US20240413141A1 (en) * | 2021-10-22 | 2024-12-12 | Semiconductor Energy Laboratory Co., Ltd. | Display apparatus and electronic device |

| US12525161B2 (en) | 2022-04-28 | 2026-01-13 | E Ink Holdings Inc. | Narrow border reflective display device |

| CN117012158B (zh) * | 2022-04-28 | 2026-03-20 | 川奇光电科技(扬州)有限公司 | 显示装置与驱动电路结构 |

| DE112023002742T5 (de) * | 2022-06-23 | 2025-04-03 | Sony Group Corporation | Anzeigeeinrichtung und elektronische Vorrichtung |

| KR20240083675A (ko) | 2022-12-05 | 2024-06-12 | 엘지디스플레이 주식회사 | 게이트 구동회로 및 표시장치 |

| KR20240176682A (ko) * | 2023-06-16 | 2024-12-24 | 엘지디스플레이 주식회사 | 표시 장치 및 표시 패널 |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6911675B2 (en) * | 2001-11-30 | 2005-06-28 | Semiconductor Energy Laboratory Co., Ltd. | Active matrix display device and manufacturing method thereof |

| JP4554152B2 (ja) * | 2002-12-19 | 2010-09-29 | 株式会社半導体エネルギー研究所 | 半導体チップの作製方法 |

| JP2004247373A (ja) * | 2003-02-12 | 2004-09-02 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| JP4573267B2 (ja) * | 2004-11-17 | 2010-11-04 | セイコーエプソン株式会社 | 薄膜デバイス、薄膜デバイスの製造方法、集積回路、マトリクス装置、電子機器 |

| JP4619186B2 (ja) * | 2005-04-19 | 2011-01-26 | 株式会社半導体エネルギー研究所 | 発光装置 |

| JP2010003910A (ja) * | 2008-06-20 | 2010-01-07 | Toshiba Mobile Display Co Ltd | 表示素子 |

| US8279145B2 (en) * | 2009-02-17 | 2012-10-02 | Global Oled Technology Llc | Chiplet driver pairs for two-dimensional display |

| US8125472B2 (en) * | 2009-06-09 | 2012-02-28 | Global Oled Technology Llc | Display device with parallel data distribution |

| KR101084198B1 (ko) * | 2010-02-24 | 2011-11-17 | 삼성모바일디스플레이주식회사 | 유기 발광 표시 장치 |

| JP5720222B2 (ja) | 2010-12-13 | 2015-05-20 | ソニー株式会社 | 表示装置及び電子機器 |

| SG10201605237SA (en) * | 2011-06-24 | 2016-08-30 | Sharp Kk | Display device and method for manufacturing same |

| US9721998B2 (en) * | 2011-11-04 | 2017-08-01 | Semiconductor Energy Laboratory Co., Ltd. | Display device and driving method thereof |

| JP5954651B2 (ja) * | 2011-12-09 | 2016-07-20 | 株式会社Joled | 表示装置および電子機器 |

| JP6034048B2 (ja) * | 2012-04-23 | 2016-11-30 | 株式会社半導体エネルギー研究所 | 表示装置、電子機器 |

-

2014

- 2014-03-31 JP JP2014071920A patent/JP6518890B2/ja active Active

-

2015

- 2015-03-19 US US14/662,449 patent/US9564482B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US9564482B2 (en) | 2017-02-07 |

| JP2015194577A (ja) | 2015-11-05 |

| US20150279918A1 (en) | 2015-10-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6518890B2 (ja) | 表示装置および電子機器 | |

| US11864407B2 (en) | Display device with structure for preventing organic material overflow | |

| US10580836B2 (en) | OLED touch display panel with baffles on a TFT back plate, method for manufacturing the same and touch display device | |

| US10930197B2 (en) | Display apparatus and tiled display apparatus | |

| CN103247692B (zh) | 薄膜晶体管、显示单元和电子设备 | |

| JP5899535B2 (ja) | El表示装置 | |

| KR102663140B1 (ko) | 디스플레이 장치 | |

| JP2014174319A (ja) | 表示装置および表示装置の製造方法ならびに電子機器 | |

| JP7274929B2 (ja) | 表示装置 | |

| WO2014046031A1 (ja) | 半導体装置及び表示装置 | |

| US12178079B2 (en) | Display device | |

| JP6258047B2 (ja) | 発光素子表示装置 | |

| KR20130020068A (ko) | 표시장치 및 그 제조방법 | |

| WO2014054558A1 (ja) | 半導体装置及び表示装置 | |

| CN118284128A (zh) | 显示装置 | |

| KR20240155408A (ko) | 표시 장치 및 이의 제조 방법 | |

| KR101932514B1 (ko) | 유기전계 발광소자 | |

| US20250143098A1 (en) | Display device and method of fabricating the same | |

| US20250143121A1 (en) | Display device | |

| EP3679422B1 (en) | Display substrate and display apparatus | |

| US20250126999A1 (en) | Display device and method for fabricating the same | |

| KR20240176117A (ko) | 표시 장치 및 표시 장치의 제조 방법 | |

| KR102029169B1 (ko) | 디스플레이 장치와 이의 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20151019 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170117 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20170117 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20171124 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20171205 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180131 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180313 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180510 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20181030 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20181129 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20190226 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20190313 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6518890 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S303 | Written request for registration of pledge or change of pledge |

Free format text: JAPANESE INTERMEDIATE CODE: R316303 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S803 | Written request for registration of cancellation of provisional registration |

Free format text: JAPANESE INTERMEDIATE CODE: R316803 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |