JP6301863B2 - Nitride semiconductor device and manufacturing method thereof - Google Patents

Nitride semiconductor device and manufacturing method thereof Download PDFInfo

- Publication number

- JP6301863B2 JP6301863B2 JP2015044710A JP2015044710A JP6301863B2 JP 6301863 B2 JP6301863 B2 JP 6301863B2 JP 2015044710 A JP2015044710 A JP 2015044710A JP 2015044710 A JP2015044710 A JP 2015044710A JP 6301863 B2 JP6301863 B2 JP 6301863B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- nitride semiconductor

- barrier layer

- semiconductor device

- insulating layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Junction Field-Effect Transistors (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Description

本発明は、窒化物半導体を用いて製造された窒化物半導体装置およびその製造方法に関する。 The present invention relates to a nitride semiconductor device manufactured using a nitride semiconductor and a manufacturing method thereof.

GaNをはじめとした窒化物半導体は、高い絶縁破壊電界強度、高い熱伝導率および高い電子飽和速度などの特性を有しており、高周波のハイパワーデバイス向けの材料として優れている。例えば、主表面をC面としたサファイア基板上に、主表面をIII族極性面(C面)としたGaNバッファ層を介して形成された、AlGaNバリア層を有するヘテロ接合構造は、分極効果によりヘテロ接合界面近傍に電子が高濃度に蓄積され、いわゆる2次元電子ガス(2DEG)を形成する(非特許文献1参照)。 Nitride semiconductors such as GaN have characteristics such as high breakdown field strength, high thermal conductivity, and high electron saturation speed, and are excellent as materials for high-frequency high-power devices. For example, a heterojunction structure having an AlGaN barrier layer formed on a sapphire substrate whose main surface is a C-plane via a GaN buffer layer whose main surface is a group III polar surface (C-plane) is Electrons are accumulated at a high concentration in the vicinity of the heterojunction interface to form a so-called two-dimensional electron gas (2DEG) (see Non-Patent Document 1).

この2次元電子ガスは、散乱要因となる導電性不純物が存在しないアンドープGaN層内に形成されるために高い電子移動度を示す。従って、2次元電子ガスをチャネルとして用いることで、いわゆる高電子移動度トランジスタ(HEMT)として動作させることが可能である。窒化物系HEMTにおいては、上記分極効果によって発生する2次元電子ガス濃度が非常に高いことから高電流密度でのトランジスタ動作が可能となり、この点でもハイパワーデバイス向けとして有利である。 This two-dimensional electron gas exhibits high electron mobility because it is formed in an undoped GaN layer that does not have conductive impurities that cause scattering. Therefore, by using a two-dimensional electron gas as a channel, it can be operated as a so-called high electron mobility transistor (HEMT). In the nitride-based HEMT, since the two-dimensional electron gas concentration generated by the polarization effect is very high, transistor operation at a high current density is possible, which is also advantageous for high power devices.

ところで、AlGaNとGaNのヘテロ構造を用いたHEMTを、例えばミリ波帯のパワーアンプ(PA)やモノリシックマイクロ波集積回路(MMIC)へ応用する場合、遮断周波数fTや最大発振周波数fmaxを数百GHzにする必要がある。GaNなどによるHEMTの高速性を向上させるためには、他のトランジスタと同様に、スケーリング則に則った微細化や寄生抵抗などの削減が有効である。 By the way, when a HEMT using a heterostructure of AlGaN and GaN is applied to, for example, a millimeter wave band power amplifier (PA) or a monolithic microwave integrated circuit (MMIC), the cutoff frequency f T and the maximum oscillation frequency f max are several. It is necessary to set it to 100 GHz. In order to improve the high-speed performance of the HEMT using GaN or the like, miniaturization according to the scaling law and reduction of parasitic resistance are effective as in other transistors.

非特許文献2には、ゲート長をより短くすることなどの微細化、および、オーミックアクセス領域への低抵抗n型層の再成長による寄生抵抗低減により、450GHzを超えるfTや、600GHz近いfmaxの値が報告されている。このHEMTは、図5に示すように、SiC基板501の上に、AlGaN層502が形成され、この上にGaN層503,AlN層504が積層され、この両脇をエッチング除去した後でn+−GaN層505を再成長させている。AlN層504の上には、断面T字のT型ゲート電極506が形成され、再成長させたn+−GaN層505には、ソース電極507およびドレイン電極508が形成されている。また、素子の表面は、窒化シリコン層509で保護されている。

Non-Patent Document 2 discloses that f T exceeding 450 GHz and f f close to 600 GHz due to miniaturization such as shorter gate length and reduction of parasitic resistance due to regrowth of the low resistance n-type layer in the ohmic access region. The value of max has been reported. In this HEMT, as shown in FIG. 5, an AlGaN

上記HEMTでは、T型ゲート電極506の採用により、短ゲート長化しつつゲート抵抗を低減している。また、ソース・ドレインのコンタクト領域では、エッチング除去した後再成長させた低抵抗なn+−GaN層505により、ソース電極507,ドレイン電極508と、2次元電子ガス521とのコンタクトを取り、アクセス抵抗を低減している。

In the HEMT, the gate resistance is reduced while the gate length is shortened by adopting the T-

しかしながら、上述したHEMTには、次に示す問題がある。T型ゲート電極は、短ゲートトランジスタにおいて広く用いられている技術ではあるが、T字の足の部分が頭部に比べて非常に細くなっているため、プロセス中にゲート電極が倒れやすく、歩留まりを低下させてしまうという問題がある。この問題は、ゲート寄生容量を低減させるために足の長さを長くし、かつ、ゲート長を極限的に短くするために半導体層と接する面積が小さくしようとすると、より顕著になる。 However, the HEMT described above has the following problems. Although the T-type gate electrode is a technology widely used in short gate transistors, the gate part of the T-shaped leg is very thin compared to the head, so that the gate electrode tends to fall down during the process, and the yield There is a problem of lowering. This problem becomes more prominent when the length of the foot is increased in order to reduce the gate parasitic capacitance and the area in contact with the semiconductor layer is decreased in order to extremely shorten the gate length.

本発明は、以上のような問題点を解消するためになされたものであり、プロセス歩留まりを低下させることなく、ゲート長をより短くできるようにすることを目的とする。 The present invention has been made to solve the above-described problems, and an object of the present invention is to make it possible to shorten the gate length without reducing the process yield.

本発明に係る窒化物半導体装置は、基板の上に形成された窒化物半導体からなる絶縁層と、アンドープの窒化物半導体から構成され、絶縁層の上のゲート領域のみに結晶成長することで形成されたチャネル層と、窒化物半導体から構成されてチャネル層の上のみに結晶成長することで形成されたバリア層と、n型の窒化物半導体から構成され、チャネル層およびバリア層の周囲の絶縁層の上に結晶成長することで形成されたコンタクト層と、バリア層の上に形成されたゲート電極と、ゲート電極を挟んで形成されて、コンタクト層に接続するソース電極およびドレイン電極とを備える。 The nitride semiconductor device according to the present invention includes an insulating layer made of a nitride semiconductor formed on a substrate and an undoped nitride semiconductor, and is formed by crystal growth only in a gate region on the insulating layer. A channel layer, a barrier layer formed by growing a crystal only on the channel layer, and an n-type nitride semiconductor, and insulating around the channel layer and the barrier layer. A contact layer formed by crystal growth on the layer; a gate electrode formed on the barrier layer; and a source electrode and a drain electrode formed on both sides of the gate electrode and connected to the contact layer .

上記窒化物半導体装置において、コンタクト層は、バリア層までの高さより厚く形成され、ゲート電極は、リセスゲート構造とされているようにしても良い。 In the nitride semiconductor device, the contact layer may be formed thicker than the barrier layer, and the gate electrode may have a recessed gate structure.

上記窒化物半導体装置において、チャネル層およびバリア層は、主表面をIII族極性面とされ、かつ成長側面が(1−101)面とされている。 In the nitride semiconductor device, the channel layer and the barrier layer have a main surface as a group III polar surface and a growth side surface as a (1-101) surface .

また、本発明に係る窒化物半導体装置の製造方法は、基板の上に窒化物半導体からなる絶縁層を結晶成長する第1工程と、絶縁層の上にゲート領域が開口した選択成長マスクを形成する第2工程と、選択成長マスクの開口部の絶縁層の上に選択的にアンドープの窒化物半導体を結晶成長して絶縁層の上のゲート領域のみにチャネル層を形成する第3工程と、チャネル層の上のみに窒化物半導体を結晶成長してバリア層を形成する第4工程と、選択成長マスクを除去してからチャネル層およびバリア層の周囲の絶縁層の上にn型の窒化物半導体を結晶成長してコンタクト層を形成する第5工程と、バリア層の上にゲート電極を形成する第6工程と、ゲート電極を挟んでコンタクト層に接続するソース電極およびドレイン電極を形成する第7工程とを備える。 The method for manufacturing a nitride semiconductor device according to the present invention includes a first step of crystal-growing an insulating layer made of a nitride semiconductor on a substrate, and a selective growth mask having an open gate region on the insulating layer. A second step of performing a crystal growth of an undoped nitride semiconductor selectively on the insulating layer in the opening of the selective growth mask to form a channel layer only in the gate region on the insulating layer; A fourth step of forming a barrier layer by crystal growth of a nitride semiconductor only on the channel layer; and removing the selective growth mask and then n-type nitride on the insulating layer around the channel layer and the barrier layer A fifth step of forming a contact layer by crystal growth of a semiconductor; a sixth step of forming a gate electrode on the barrier layer; and a fifth step of forming a source electrode and a drain electrode connected to the contact layer across the gate electrode. 7 steps Equipped with a.

上記窒化物半導体装置の製造方法において、第4工程では、コンタクト層をバリア層までの高さより厚く形成し、ゲート電極は、リセスゲート構造としてもよい。 In the method for manufacturing a nitride semiconductor device, in the fourth step, the contact layer may be formed to be thicker than the barrier layer, and the gate electrode may have a recessed gate structure.

上記窒化物半導体装置の製造方法において、第3工程および第4工程では、チャネル層およびバリア層を、主表面をIII族極性面とし、かつ成長側面を(1−101)面とした状態で結晶成長する。なお、第4工程では、絶縁層,チャネル層,バリア層に対して選択的に選択成長マスクをエッチングするウエットエッチングにより選択成長マスクを除去するとよい。 In the method for manufacturing a nitride semiconductor device, in the third step and the fourth step , the channel layer and the barrier layer are crystallized in a state where the main surface is a group III polar surface and the growth side surface is a (1-101) surface. you growth. In the fourth step, the selective growth mask may be removed by wet etching that selectively etches the selective growth mask with respect to the insulating layer, the channel layer, and the barrier layer.

以上説明したことにより、本発明によれば、プロセス歩留まりを低下させることなく、ゲート長をより短くできるという優れた効果が得られる。 As described above, according to the present invention, an excellent effect that the gate length can be shortened without reducing the process yield can be obtained.

以下、本発明の実施の形態について図を参照して説明する。 Hereinafter, embodiments of the present invention will be described with reference to the drawings.

[実施の形態1]

はじめに、本発明の実施の形態1について図1,図2A〜図2Hを用いて説明する。図1は、本発明の実施の形態1における窒化物半導体装置の構成を示す断面図である。図2A〜図2Hは、本発明の実施の形態1における窒化物半導体装置の製造方法を説明するための途中工程の状態を示す断面図である。

[Embodiment 1]

First, Embodiment 1 of the present invention will be described with reference to FIGS. 1 and 2A to 2H. FIG. 1 is a cross-sectional view showing the configuration of the nitride semiconductor device according to the first embodiment of the present invention. 2A to 2H are cross-sectional views illustrating a state of an intermediate process for explaining the method for manufacturing the nitride semiconductor device according to the first embodiment of the present invention.

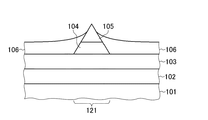

実施の形態1における窒化物半導体装置は、例えば、半絶縁性のSi−face (0001)SiCからなる基板101の上に形成された窒化物半導体からなるバッファ層102を備える。バッファ層102は、例えば、AlNまたはAlGaNから構成されていれば良い。また、バッファ層102の上に形成された窒化物半導体からなる絶縁層103を備える。絶縁層103は、FeあるいはCをドープしたGaNから構成すれば良い。また、ゲート長の短い電界効果トランジスタでしばしば観測される短チャネル効果を抑制させる目的で、後述するチャネル層104の材料よりもワイドバンドギャップな材料を用いてバックバリア構造としてもよい。例えば、チャネル層104をGaNから構成した場合、絶縁層103は、AlGaNなどから構成すればよい。

The nitride semiconductor device according to the first embodiment includes, for example, a

また、この窒化物半導体装置は、アンドープの窒化物半導体から構成され、絶縁層103の上のゲート領域121のみに結晶成長することで形成されたチャネル層104と、窒化物半導体から構成されてチャネル層104の上のみに結晶成長することで形成されたバリア層105とを備える。ゲート領域121は、例えば、図1の紙面手前より奥に向かって延在する短冊状の領域である。チャネル層104は、アンドープのGaNから構成し、バリア層105は、アンドープのAlGaNから構成すれば良い。

In addition, this nitride semiconductor device is composed of an undoped nitride semiconductor, and is composed of a

ここで、チャネル層104およびバリア層105は、主表面をIII族極性面とした状態で結晶成長(エピタキシャル成長)する、言い換えると、III族極性の(0001)面方向に結晶成長することで形成されていると良い。窒化物半導体は、主表面がIII族極性面(C+面)の上に、一般的に用いられる有機金属気相成長(MOVPE)法により結晶成長させると、III族極性で結晶成長する。この場合、成長側面が(1−101)となる条件で結晶成長させると、成長に伴い表面の面積が小さくなっていく。この結果、チャネル層104とバリア層105との界面の基板平面方向(ゲート長方向)の寸法を、チャネル層104の底面より小さくする状態に形成することが可能となる。

Here, the

また、実施の形態1における窒化物半導体装置は、n型の窒化物半導体から構成され、チャネル層104およびバリア層105の周囲の絶縁層103の上に結晶成長することで形成されたコンタクト層106と、バリア層105の上に絶縁層107を介して形成されたゲート電極108と、ゲート電極108を挟んで形成されて、コンタクト層106に接続するソース電極109およびドレイン電極110とを備える。コンタクト層106は、例えば、例えば、高濃度にSiをドープしたGaNから構成すれば良い。また、絶縁層107は、窒化シリコンから構成すれば良い。なお、ゲート電極108は、バリア層105にショットキー接続する構成としても良い。

The nitride semiconductor device according to the first embodiment is made of an n-type nitride semiconductor, and is formed by crystal growth on the insulating

次に、本発明の実施の形態1における窒化物半導体装置の製造方法について、図2A〜図2Hを用いて説明する。 Next, a method for manufacturing the nitride semiconductor device according to the first embodiment of the present invention will be described with reference to FIGS. 2A to 2H.

まず、図2Aに示すように、半絶縁性のSi−face (0001)SiCからなる基板101を用意し、図2Bに示すように、用意した基板101の上にAlNまたはAlGaNを堆積してバッファ層102を形成する。次に、図2Cに示すように、窒化物半導体である例えばFeあるいはCをドープしたGaNを結晶成長させて絶縁層103を形成する(第1工程)。この結晶成長では、MOVPE装置により、窒化物半導体をIII族極性の(0001)面方向に成長させる。

First, a

次に、図2Dに示すように、絶縁層103の上にゲート領域121に開口部151aを備える選択成長マスク151を形成する(第2工程)。例えば、前述した窒化物半導体の成長に用いたMOVPE装置より基板101を取り出し、絶縁層103の上に、プラズマ援用化学気相堆積(PE−CVD)装置やスパッタ装置などにより窒化シリコンを堆積して窒化シリコン膜を形成する。次いで、形成した窒化シリコン膜を公知のリソグラフィー技術およびエッチング技術によりパターニングし、開口部151aを備える選択成長マスク151を形成すればよい。

Next, as shown in FIG. 2D, a

次に、図2Eに示すように、選択成長マスク151の開口部151aの絶縁層103の上に選択的にアンドープの窒化物半導体を結晶成長し、絶縁層103の上のゲート領域121のみにチャネル層104を形成する(第3工程)。引き続いて、チャネル層104の上のみに窒化物半導体を結晶成長してバリア層105を形成する(第4工程)。例えば、絶縁層103までの形成に用いたMOVPE装置により、アンドープのGaNを所定の厚さにまで結晶成長させ、引き続いてアンドープのAlGaNを結晶成長させれば良い。

Next, as shown in FIG. 2E, an undoped nitride semiconductor is selectively grown on the insulating

ここで、チャネル層104およびバリア層105は、III族極性の(0001)面方向に結晶成長する。また、成長側面が(1−101)となる条件で結晶成長させる(非特許文献3参照)。この条件により、チャネル層104は、ゲート長方向の寸法が、成長とともに小さくなる。このように成長させたチャネル層104を所定の厚さにまで成長させると、形成されたチャネル層104の上面は、開口部151aの面積より小さくなり、チャネル層104のゲート両方向の断面は、台形となる。

Here, the

また、上述したように成長させたチャネル層104の上に、バリア層105を成長させると、同様に、ゲート長方向の寸法が、成長とともに小さくなる。この結果、バリア層105は、(0001)面である上面がこれ以上小さくなることができなくなるところまで成長すると、自動的に成長が停止する。結果として、バリア層105は、ゲート両方向の断面が三角形となる。

Further, when the

チャネル層104とバリア層105との界面がチャネル長となるため、上述したことより分かるように、チャネル長は、開口部151aのゲート長幅により規定され、開口部151aのゲート長幅より小さくすることができる。このように、実施の形態1によれば、後述するように形成するゲート電極108のゲート長寸法に依存せずに短チャネル化を図ることが可能となる。

Since the interface between the

次に、選択成長マスク151を除去してから、図2Fに示すように、チャネル層104およびバリア層105の周囲の絶縁層103の上にn型の窒化物半導体を結晶成長してコンタクト層106を形成する(第5工程)。例えば、バリア層105を形成した後、MOVPE装置より基板101を搬出し、フッ酸などを用いたウエットエッチングにより、選択成長マスク151のみを選択的にエッチング除去する。これは、絶縁層103,チャネル層104,バリア層105に対して選択的に選択成長マスク151をエッチングするウエットエッチングである。次いで、MOVPE装置に再度基板を搬入し、露出している絶縁層103の上に高濃度にSiをドープしたGaNを再成長させれば良い。

Next, after removing the

ところで、コンタクト層106の再成長時間を長くしすぎると、既に形成されているチャネル層104・バリア層105が完全にコンタクト層106で覆われてしまう。これを防ぐために、光学的手法を用い、成長しながら基板表面の反射率を測定するとよい。チャネル層104・バリア層105が成長層の表面に出現している間は、この凹凸によって反射率が低下するが、完全に覆われて表面が平坦化すると反射率が増大する。この反射率の変化を成長中にモニターすることで、コンタクト層106の埋め込み再成長時間を制御することができる。

By the way, if the regrowth time of the

次に、図2Gに示すように、コンタクト層106およびこの上に露出しているバリア層105を覆うように、絶縁層107を形成する。例えば、MOVPE装置より基板101を取り出し、PE−CVD装置やスパッタ装置などにより窒化シリコンを堆積すれば、絶縁層107が形成できる。

Next, as shown in FIG. 2G, an insulating

次に、図2Hに示すように、バリア層105の上にゲート電極108を形成し(第6工程)、ゲート電極108を挟んでコンタクト層106にオーミック接続するソース電極109およびドレイン電極110を形成する(第7工程)。例えば、よく知られたリフトオフ法などにより、各電極を形成すれば良い。また、ソース電極109およびドレイン電極110の形成では、リフトオフマスクを用いた選択的なエッチングにより、絶縁層107の電極形成箇所に開口部を形成した後、電極材料を堆積し、リフトオフマスクを除去することで、コンタクト層106に接続するソース電極109を形成すれば良い。

Next, as shown in FIG. 2H, the

以上に説明したように、実施の形態1によれば、ゲート領域121のみに成長させたチャネル層104とバリア層105との界面によりチャネル長が規定できるので、足の部分を非常に小さくした破損しやすいT型ゲート電極を用いる必要が無いので、プロセスも歩留まりを低下させることなく、ゲート長をより短くできるようになる。

As described above, according to the first embodiment, the channel length can be defined by the interface between the

また、コンタクト層106を再成長させるときに、選択成長マスク151をウエットエッチングにより除去できるので、ドライエッチングにより除去で発生するエッチングダメージが抑制できるようになる。この結果、チャネル層104に形成される2次元電子ガスと、コンタクト層106とのコンタクト寄生抵抗を増大させることがなく、十分にアクセス抵抗を下げることができる。

In addition, when the

[実施の形態2]

次に、本発明の実施の形態2について、図3,図4A〜図4Iを用いて説明する。図3は、本発明の実施の形態2における窒化物半導体装置の構成を示す断面図である。図4A〜図4Iは、本発明の実施の形態2における窒化物半導体装置の製造方法を説明するための途中工程の状態を示す断面図である。

[Embodiment 2]

Next, Embodiment 2 of the present invention will be described with reference to FIGS. 3 and 4A to 4I. FIG. 3 is a cross-sectional view showing a configuration of the nitride semiconductor device according to the second embodiment of the present invention. 4A to 4I are cross-sectional views showing a state of an intermediate step for explaining the method for manufacturing the nitride semiconductor device in the second embodiment of the present invention.

実施の形態2における窒化物半導体装置は、例えば、半絶縁性のSi−face (0001)SiCからなる基板201の上に形成された窒化物半導体からなるバッファ層202を備える。バッファ層202は、例えば、AlNまたはAlGaNから構成されていれば良い。また、バッファ層202の上に形成された窒化物半導体からなる絶縁層203を備える。絶縁層203は、FeあるいはCをドープしたGaNから構成すれば良い。また、ゲート長の短い電界効果トランジスタでしばしば観測される短チャネル効果を抑制させる目的で、後述するチャネル層204の材料よりもワイドバンドギャップな材料を用いてバックバリア構造としてもよい。例えば、チャネル層204をGaNから構成した場合、絶縁層203は、AlGaNなどから構成すればよい。

The nitride semiconductor device according to the second embodiment includes, for example, a

また、この窒化物半導体装置は、アンドープの窒化物半導体から構成され、絶縁層203の上のゲート領域221のみに結晶成長することで形成されたチャネル層204と、窒化物半導体から構成されてチャネル層204の上のみに結晶成長することで形成されたバリア層205とを備える。ゲート領域221は、例えば、図3の紙面手前より奥に向かって延在する短冊状の領域である。チャネル層204は、アンドープのGaNから構成し、バリア層205は、アンドープのAlGaNから構成すれば良い。上記構成は、前述した実施の形態1と同様である。

The nitride semiconductor device is composed of an undoped nitride semiconductor, and is formed of a

ここで、チャネル層204およびバリア層205は、主表面をIII族極性面とした状態で結晶成長(エピタキシャル成長)する、言い換えると、III族極性の(0001)面方向に結晶成長することで形成されていると良い。窒化物半導体は、主表面がIII族極性面(C+面)の上に、一般的に用いられる有機金属気相成長(MOVPE)法により結晶成長させると、III族極性で結晶成長する。この場合、成長側面が(1−101)となる条件で結晶成長させると、成長に伴い表面の面積が小さくなっていく。この結果、チャネル層204とバリア層205との界面の基板平面方向(ゲート長方向)の寸法を、チャネル層204の底面より小さくする状態に形成することが可能となる。

Here, the

また、実施の形態2における窒化物半導体装置は、n型の窒化物半導体から構成され、チャネル層204およびバリア層205の周囲の絶縁層203の上に結晶成長することで形成されたコンタクト層206と、バリア層205の上に絶縁層207を介して形成されたゲート電極208と、ゲート電極208を挟んで形成されて、コンタクト層206に接続するソース電極209およびドレイン電極210とを備える。コンタクト層206は、例えば、例えば、高濃度にSiをドープしたGaNから構成すれば良い。また、絶縁層207は、窒化シリコンから構成すれば良い。

The nitride semiconductor device according to the second embodiment is made of an n-type nitride semiconductor, and is formed by crystal growth on the insulating

ここで、実施の形態2では、コンタクト層206は、バリア層205までの高さより厚く形成され、ゲート電極208は、リセスゲート構造とされている。コンタクト層206は、チャネル層204,バリア層205を埋める状態に厚く形成されている。厚く形成したコンタクト層206のゲート領域221において、ゲート長方向に所定の溝幅としてバリア層205の上面にまで貫通する溝222が形成されている。また、側面や底面に絶縁層207が形成されている溝222の内部に充填するように、ゲート電極208が形成され、リセスゲート構造とされている。なお、ゲート電極208は、バリア層205にショットキー接続する構成としても良い。

Here, in the second embodiment, the

次に、本発明の実施の形態2における窒化物半導体装置の製造方法について、図4A〜図4Iを用いて説明する。 Next, a method for manufacturing the nitride semiconductor device according to the second embodiment of the present invention will be described with reference to FIGS. 4A to 4I.

まず、図4Aに示すように、半絶縁性のSi−face (0001)SiCからなる基板201を用意し、図4Bに示すように、用意した基板201の上にAlNまたはAlGaNを堆積してバッファ層202を形成する。次に、図4Cに示すように、窒化物半導体である例えばFeあるいはCをドープしたGaNを結晶成長させて絶縁層203を形成する(第1工程)。この結晶成長では、MOVPE装置により、窒化物半導体をIII族極性の(0001)面方向に成長させる。

First, a

次に、図4Dに示すように、絶縁層203の上にゲート領域221に開口部251aを備える選択成長マスク251を形成する(第2工程)。例えば、前述した窒化物半導体の成長に用いたMOVPE装置より基板201を取り出し、絶縁層203の上に、PE−CVD装置やスパッタ装置などにより窒化シリコンを堆積して窒化シリコン膜を形成する。次いで、形成した窒化シリコン膜を公知のリソグラフィー技術およびエッチング技術によりパターニングし、開口部251aを備える選択成長マスク251を形成すればよい。

Next, as shown in FIG. 4D, a

次に、図4Eに示すように、選択成長マスク251の開口部251aの絶縁層203の上に選択的にアンドープの窒化物半導体を結晶成長し、絶縁層203の上のゲート領域221のみにチャネル層204を形成する(第3工程)。引き続いて、チャネル層204の上のみに窒化物半導体を結晶成長してバリア層205を形成する(第4工程)。例えば、絶縁層203までの形成に用いたMOVPE装置により、アンドープのGaNを所定の厚さにまで結晶成長させ、引き続いてアンドープのAlGaNを結晶成長させれば良い。

Next, as shown in FIG. 4E, an undoped nitride semiconductor is selectively grown on the insulating

ここで、チャネル層204およびバリア層205は、III族極性の(0001)面方向に結晶成長する。また、成長側面が(1−101)となる条件で結晶成長させる(非特許文献3参照)。この条件により、チャネル層204は、ゲート長方向の寸法が、成長とともに小さくなる。このように成長させたチャネル層204を所定の厚さにまで成長させると、形成されたチャネル層204の上面は、開口部251aの面積より小さくなり、チャネル層204のゲート両方向の断面は、台形となる。

Here, the

また、上述したように成長させたチャネル層204の上に、バリア層205を成長させると、同様に、ゲート長方向の寸法が、成長とともに小さくなる。この結果、バリア層205は、(0001)面である上面がこれ以上小さくなることができなくなるところまで成長すると、自動的に成長が停止する。結果として、バリア層205は、ゲート両方向の断面が三角形となる。

Further, when the

次に、選択成長マスク251を除去してから、図4F,図4Gに示すように、チャネル層204およびバリア層205の周囲の絶縁層203の上にn型の窒化物半導体を結晶成長してコンタクト層206を形成する(第5工程)。コンタクト層206の再成長では、チャネル層204およびバリア層205を完全に埋め込み、図4Gに示すように、上面(表面)がほぼ平坦化されるまで厚く形成する。

Next, after removing the

例えば、バリア層205を形成した後、MOVPE装置より基板201を搬出し、フッ酸などを用いたウエットエッチングにより、選択成長マスク251のみを選択的にエッチング除去する。これは、絶縁層203,チャネル層204,バリア層205に対して選択的に選択成長マスク251をエッチングするウエットエッチングである。次いで、MOVPE装置に再度基板を搬入し、露出している絶縁層203の上に高濃度にSiをドープしたGaNを再成長させれば良い。チャネル層204周囲の絶縁層203表面より再成長するコンタクト層206は、成長の過程で、図4Fに示すようにバリア層205上部で一体となり、更に成長を続けることで、図4Gに示すように、やがて平坦化する。

For example, after the

チャネル層204・バリア層205を挟んで両側からコンタクト層206が会合するところは転位が発生し、コンタクト層206の表面部にはドットのような欠陥が観測されることになる。この位置が、ゲート領域221のゲート長方向の中心位置となる。平坦化するところまで成長した後、上記のドットを目印にゲート形成部を決定し、公知のリソグラフ工程によりマスクパターンを形成した後、ゲート形成部をエッチングすることで、図4Hに示すように、溝222を形成する。この時、バリア層205に達するまでエッチングし、バリア層205上面が出現する状態とする。このように、実施の形態2によれば、ゲート領域221の中心部が自動的に決定できるようになり、ゲート電極208の中心位置を、高い精度で決定することができる。

Dislocation occurs where the

なお、図4Hでは簡略化するため、バリア層205表面の(0001)面が出現するように示しているが、この面方位についてはどの面が出てもトランジスタ動作には大きな影響はない。次いで、溝222の側面,底面を含めてコンタクト層206の上に絶縁層207を形成する。例えば、MOVPE装置より基板201を取り出し、PE−CVD装置やスパッタ装置などにより窒化シリコンを堆積すれば、絶縁層207が形成できる。

In FIG. 4H, for the sake of simplification, the (0001) plane of the surface of the

次に、図4Iに示すように、絶縁層207が形成されている溝222内部に充填する状態で、バリア層205の上にゲート電極208を形成し(第6工程)、ゲート電極208を挟んでコンタクト層206にオーミック接続するソース電極209およびドレイン電極210を形成する(第7工程)。例えば、よく知られたリフトオフ法などにより、各電極を形成すれば良い。また、ソース電極209およびドレイン電極210の形成では、リフトオフマスクを用いた選択的なエッチングにより、絶縁層207の電極形成箇所に開口部を形成した後、電極材料を堆積し、リフトオフマスクを除去することで、コンタクト層206に接続するソース電極209を形成すれば良い。

Next, as shown in FIG. 4I, a

以上に説明した実施の形態2によれば、溝222のゲート長方向の幅によってゲート長が決定されるようになる。実施の形態2では、チャネル層204とバリア層205との界面のゲート長方向の長さより、ゲート長を小さくすることができる。また、非常に小さなゲート長としても、ゲート電極208のゲート長幅とされた細い足は、両脇が絶縁層207を介してコンタクト層206に支えられた状態となる。このため、一般的なT型ゲート電極構造のように倒れてしまうことはない。また、実施の形態2におけるゲート電極208は、T型として頭部をより大きくすることが可能であり、ゲート抵抗をきわめて小さくすることも可能である。

According to the second embodiment described above, the gate length is determined by the width of the

また、チャネル層204・バリア層205を挟んで両側からコンタクト層206が会合するところに発生する転位によるドット状の欠陥を基準としてゲート電極208の中心位置を決定できるので、非常に細い足の部分を、高い精度で位置決めして微細な幅としたバリア層205の上に配置させることができる。

Further, since the center position of the

このように、実施の形態2によれば、高周波動作に必要な短ゲート長を保持しつつ、十分に機械的強度を持った低抵抗なゲート電極を形成することが容易となる。一方、アクセス領域に関しては、実施の形態1と同様に、コンタクト層206を再成長させるときに、選択成長マスク251をウエットエッチングにより除去できるので、ドライエッチングにより除去で発生するエッチングダメージが抑制できるようになる。この結果、チャネル層204に形成される2次元電子ガスと、コンタクト層206とのコンタクト寄生抵抗を増大させることがなく、十分にアクセス抵抗を下げることができる。

Thus, according to the second embodiment, it becomes easy to form a low-resistance gate electrode having sufficient mechanical strength while maintaining a short gate length necessary for high-frequency operation. On the other hand, with respect to the access region, as in the first embodiment, when the

以上に説明したように、本発明によれば、ゲート領域のみに結晶成長することで、窒化物半導体からなるチャネル層およびバリア層を成長させるようにしたので、プロセス歩留まりを低下させることなく、ゲート長をより短くできるようになる。 As described above, according to the present invention, the channel layer and the barrier layer made of the nitride semiconductor are grown by crystal growth only in the gate region, so that the gate yield can be reduced without reducing the process yield. The length can be shortened.

なお、本発明は以上に説明した実施の形態に限定されるものではなく、本発明の技術的思想内で、当分野において通常の知識を有する者により、多くの変形および組み合わせが実施可能であることは明白である。 The present invention is not limited to the embodiment described above, and many modifications and combinations can be implemented by those having ordinary knowledge in the art within the technical idea of the present invention. It is obvious.

101…基板、102…バッファ層、103…絶縁層、104…チャネル層、105…バリア層、106…コンタクト層、107…絶縁層、108…ゲート電極、109…ソース電極、110…ドレイン電極、121…ゲート領域。

DESCRIPTION OF

Claims (5)

アンドープの窒化物半導体から構成され、前記絶縁層の上のゲート領域のみに結晶成長することで形成されたチャネル層と、

窒化物半導体から構成されて前記チャネル層の上のみに結晶成長することで形成されたバリア層と、

n型の窒化物半導体から構成され、前記チャネル層および前記バリア層の周囲の前記絶縁層の上に結晶成長することで形成されたコンタクト層と、

前記バリア層の上に形成されたゲート電極と、

前記ゲート電極を挟んで形成されて、前記コンタクト層に接続するソース電極およびドレイン電極と

を備え、

前記チャネル層および前記バリア層は、主表面をIII族極性面とされ、かつ成長側面が(1−101)面とされていることを特徴とする窒化物半導体装置。 An insulating layer made of a nitride semiconductor formed on the substrate;

A channel layer made of an undoped nitride semiconductor and formed by crystal growth only in the gate region on the insulating layer;

A barrier layer made of a nitride semiconductor and formed by crystal growth only on the channel layer;

a contact layer made of an n-type nitride semiconductor and formed by crystal growth on the insulating layer around the channel layer and the barrier layer;

A gate electrode formed on the barrier layer;

A source electrode and a drain electrode formed across the gate electrode and connected to the contact layer ;

It said channel layer and said barrier layer is a main surface and the group III-polar surface, and a nitride semiconductor device comprising grow sides that you have been the (1-101) plane.

前記コンタクト層は、前記バリア層までの高さより厚く形成され、

前記ゲート電極は、リセスゲート構造とされている

ことを特徴とする窒化物半導体装置。 The nitride semiconductor device according to claim 1,

The contact layer is formed thicker than the height to the barrier layer,

The nitride semiconductor device, wherein the gate electrode has a recess gate structure.

前記絶縁層の上にゲート領域が開口した選択成長マスクを形成する第2工程と、

前記選択成長マスクの開口部の前記絶縁層の上に選択的にアンドープの窒化物半導体を結晶成長して前記絶縁層の上のゲート領域のみにチャネル層を形成する第3工程と、

前記チャネル層の上のみに窒化物半導体を結晶成長してバリア層を形成する第4工程と、

前記選択成長マスクを除去してから前記チャネル層および前記バリア層の周囲の前記絶縁層の上にn型の窒化物半導体を結晶成長してコンタクト層を形成する第5工程と、

前記バリア層の上にゲート電極を形成する第6工程と、

前記ゲート電極を挟んで前記コンタクト層に接続するソース電極およびドレイン電極を形成する第7工程と

を備え、

前記第3工程および前記第4工程では、前記チャネル層および前記バリア層を、主表面をIII族極性面とし、かつ成長側面を(1−101)面とした状態で結晶成長して形成することを特徴とする窒化物半導体装置の製造方法。 A first step of crystal growing an insulating layer made of a nitride semiconductor on a substrate;

Forming a selective growth mask having a gate region opened on the insulating layer;

A third step of selectively growing an undoped nitride semiconductor on the insulating layer in the opening of the selective growth mask to form a channel layer only in the gate region on the insulating layer;

A fourth step of crystal-growing a nitride semiconductor only on the channel layer to form a barrier layer;

A fifth step of forming a contact layer by growing an n-type nitride semiconductor on the insulating layer around the channel layer and the barrier layer after removing the selective growth mask;

A sixth step of forming a gate electrode on the barrier layer;

And a seventh step of forming a source electrode and a drain electrode connected to the contact layer across the gate electrode ,

Wherein in the third step and the fourth step, the channel layer and the barrier layer, you formed by crystal growth in a state the main surface and the group III-polar surface, and that the growth side and (1-101) plane A method for manufacturing a nitride semiconductor device.

前記第4工程では、前記コンタクト層を前記バリア層までの高さより厚く形成し、

前記ゲート電極は、リセスゲート構造とする

ことを特徴とする窒化物半導体装置の製造方法。 In the manufacturing method of the nitride semiconductor device according to claim 3 ,

In the fourth step, the contact layer is formed thicker than the height to the barrier layer,

The method of manufacturing a nitride semiconductor device, wherein the gate electrode has a recessed gate structure.

前記第4工程では、前記絶縁層,チャネル層,バリア層に対して選択的に前記選択成長マスクをエッチングするウエットエッチングにより前記選択成長マスクを除去する

ことを特徴とする窒化物半導体装置の製造方法。 In the manufacturing method of the nitride semiconductor device according to claim 3 or 4 ,

In the fourth step, the selective growth mask is removed by wet etching that selectively etches the selective growth mask with respect to the insulating layer, the channel layer, and the barrier layer. .

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015044710A JP6301863B2 (en) | 2015-03-06 | 2015-03-06 | Nitride semiconductor device and manufacturing method thereof |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015044710A JP6301863B2 (en) | 2015-03-06 | 2015-03-06 | Nitride semiconductor device and manufacturing method thereof |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2016164926A JP2016164926A (en) | 2016-09-08 |

| JP6301863B2 true JP6301863B2 (en) | 2018-03-28 |

Family

ID=56876702

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015044710A Active JP6301863B2 (en) | 2015-03-06 | 2015-03-06 | Nitride semiconductor device and manufacturing method thereof |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6301863B2 (en) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN113013243B (en) * | 2021-02-02 | 2022-05-10 | 深圳大学 | Gallium nitride field effect transistor and preparation method thereof |

| CN113725288B (en) * | 2021-08-03 | 2024-07-26 | 中国科学院微电子研究所 | Gate structure of high electron mobility transistor and preparation method thereof |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02165679A (en) * | 1988-12-20 | 1990-06-26 | Sony Corp | Semiconductor device and manufacture thereof |

| JPH04199644A (en) * | 1990-11-29 | 1992-07-20 | Sony Corp | Semiconductor device |

| JPH06267992A (en) * | 1993-03-11 | 1994-09-22 | Hitachi Ltd | Semiconductor device and its manufacture |

| JP2007088185A (en) * | 2005-09-21 | 2007-04-05 | Toshiba Corp | Semiconductor device and its fabrication process |

-

2015

- 2015-03-06 JP JP2015044710A patent/JP6301863B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2016164926A (en) | 2016-09-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101108344B1 (en) | Methods of fabricating nitride-based transistors with a cap layer and a recessed gate | |

| EP1779437B1 (en) | Nitride-based transistors having laterally grown active region and methods of fabricating same | |

| KR101123459B1 (en) | Nitride-based transistors with a protective layer and a low-damage recess and methods of fabrication thereof | |

| JP5160225B2 (en) | Method for fabricating nitride-based transistor with regrowth ohmic contact region and nitride-based transistor with regrowth ohmic contact region | |

| US10026834B2 (en) | Method of manufacturing enhanced device and enhanced device | |

| US20060006435A1 (en) | Nitride-based transistors and methods of fabrication thereof using non-etched contact recesses | |

| KR101008272B1 (en) | Normally off nitride high electron mobility transistor and method for manufacturing thereof | |

| KR101285598B1 (en) | Nitride baced heterostructure semiconductor device and manufacturing method thereof | |

| JP2008124262A (en) | AlGaN/GaN-HEMT MANUFACTURING METHOD USING SELECTION-REGROWTH | |

| RU2686575C2 (en) | Field-effect transistor with heterojunction | |

| KR101103774B1 (en) | Nitride based semiconductor device employing recessed gate edge structure and method for fabricating the same | |

| JP6301863B2 (en) | Nitride semiconductor device and manufacturing method thereof | |

| JP2010098251A (en) | Semiconductor device and method of manufacturing the same | |

| JP2010165783A (en) | Field effect transistor, and method of manufacturing the same | |

| JP6984578B2 (en) | How to make a transistor | |

| JP2017152467A (en) | Field effect transistor and manufacturing method therefor | |

| KR101670238B1 (en) | Manufacturing method for semiconductor device | |

| JP2012204577A (en) | Nitride semiconductor device and method of manufacturing the same | |

| US20230106052A1 (en) | Semiconductor device and manufacturing method thereof | |

| KR101303592B1 (en) | Method for manufacturing nitride semiconductor device | |

| KR102261735B1 (en) | Hetero-junction transistor | |

| KR101439291B1 (en) | Semiconductor and methode of manufacturing thereof | |

| KR20140027698A (en) | Normally-off nitrede based transistor and method of fabricating the same | |

| KR20140110591A (en) | Heterojunction transistor and method of fabricating the same |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20170113 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20171025 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20171107 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20171220 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20180227 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20180301 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6301863 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |