JP6166101B2 - 光半導体素子収納用パッケージおよびこれを備えた実装構造体 - Google Patents

光半導体素子収納用パッケージおよびこれを備えた実装構造体 Download PDFInfo

- Publication number

- JP6166101B2 JP6166101B2 JP2013112981A JP2013112981A JP6166101B2 JP 6166101 B2 JP6166101 B2 JP 6166101B2 JP 2013112981 A JP2013112981 A JP 2013112981A JP 2013112981 A JP2013112981 A JP 2013112981A JP 6166101 B2 JP6166101 B2 JP 6166101B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor element

- optical semiconductor

- notch

- wiring board

- substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Semiconductor Lasers (AREA)

- Light Receiving Elements (AREA)

Description

され、貫通孔が形成された側部を有する枠体と、前記枠体の前記貫通孔を通って前記枠体の内側および外側に配置されたコネクタと、前記枠体の内側における前記基板の前記主面上に配置された台座部材と、前記台座部材上に配置された配線基板とを備え、前記台座部材は、上面に第1切欠き部を有しており、前記配線基板が、前記第1切欠き部内に配置され、接合部材を介して前記第1切欠き部の内面に接合されているとともに、前記コネクタに接続されており、前記台座部材の前記上面には、前記第1切欠き部に隣接して第2切欠き部が形成されているとともに、前記配線基板が幅狭部および幅広部を有し、前記幅狭部は前記第2切欠き部によって挟まれている。

信頼性の低下を抑制できる。

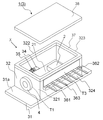

本発明の実施形態に係る光半導体素子収納用パッケージおよびこれを備えた実装構造体について、図1〜図8を参照しながら説明する。

側部322、第3側部323および第4側部324を有している。

るための第1貫通孔T1を有する部位である。第2側部322は、コネクタ33が挿通された

第2貫通孔T2を有する部位である。なお、本実施形態の第2側部322は第1側部321に隣接しているが、これには限られない。第3側部323は第1側部321と対向している部位である。第4側部324は、入出力端子36が挿通された第3貫通孔T3を有し、第1側部321に隣接している部位である。なお、第4側部324は第2側部322に対向している。

するための保持部材4がろう材などを介して接合されている。保持部材4によって保持された光ファイバやフェルールなどは、第1側部321の第1貫通孔T1に挿通され、枠体32

の内側に位置する光半導体素子2に光接続される。

を通過して枠体32の内側および外側に延在している。なお、中心導体331および外周導体332の間には、ガラスなどの誘電性材料は配置されている。

中心導体331を保持している。図3および図4に示すように、外周導体332は、枠体32の外側における第2側部322上に配置されている。外周導体332は、枠体32の外側における第2側部322の表面に銀ろうなどのろう材を介して接合されている。より具体的には、外周導

体332は、第2側部322における第2貫通孔T2の周囲の表面に接合されている。

導体332によって保持される。なお、図2に示すように、本実施形態の外周導体332は円筒状であるが、これに限定されない。

心導体331の他の一部は枠体32の内側に位置している。枠体32の外側に位置するコネクタ33の中心導体331には外部のケーブルが接続され、枠体32の内側に位置するコネクタ33の中心導体331には配線基板35が接続される。

おり、接合部材Bを介して第1切欠き部341の内面および配線基板35が接合されている。

接合部材Bとしては、半田または銀ろうなどのろう材などが挙げられる。

5および図6に示すように、本実施形態の第2切欠き部342は、第1切欠き部341における枠体32(第2側部322)側の端部に隣接している。また、本実施形態における第2切欠き

部342は、配線基板35を挟んで配線基板35の両側に位置している。

る。配線基板35は台座部材34の上面に配置されている。また、配線基板35は、台座部材34の第1切欠き部341内に配置されている。また、配線基板35は、第1切欠き部341の内面に接合部材Bを介して接合されている。すなわち、配線基板35および第1切欠き部341の間

には接合部材Bが介在している。なお、図7に示すように、本実施形態では、配線基板35の下面および配線基板35の側面の一部が、接合部材Bを介して第1切欠き部341の内面に

接合されている。

は幅狭部351aおよび幅狭部351aよりも幅の大きい幅広部351bを有している。

素質焼結体、窒化アルミニウム質焼結体または窒化珪素質焼結体などのセラミックスが挙げられる。

する。信号配線352は絶縁基板351の上面に配置されている。また、信号配線352は、半田

または銀ろうなどのろう材を介して枠体32の内側に位置するコネクタ33の中心導体331の

端部に接続されている。信号配線352は絶縁基板351の長手方向に延在している。

位置する導電膜353は、信号配線352の両側に位置しており、信号配線352に接触していな

い。また、絶縁基板351の上面および下面に位置する導電膜353は、絶縁基板351の長手方

向に延在している。なお、導電膜353は、例えばグランド電位など一定の電位に設定され

ている。

とで、コプレーナ線路が構成され、信号配線352を伝達する高周波信号を所定のインピー

ダンス値に整合させやすくなり、高周波信号に発生する伝送損失を抑制させ、高周波信号を効率良く入出力させることができる。

の第3貫通孔T3に挿通されている。また、入出力端子36は、基体361と、配線層362と、リード端子363とを有している。

枠体32の内側に位置する配線層362の部分は、ボンディングワイヤなどによって光半導体

素子2と電気的に接続される。一方、枠体32の外側に位置する配線層362の部分は、半田

またはろう材などによってリード端子363と電気的に接続される。配線層362の材料としては、例えば銅、銀、金、アルミニウム、ニッケル、モリブデン、タングステン、マンガンまたはクロムなどの金属材料、あるいはこれらの金属材料を含んだ合金が挙げられる。

材料、あるいはこれらの金属材料を含んだ合金からなる。

に配置されるとともに、第1切欠き部341の内面に接合されている。第1切欠き部341の内面を利用することによって、接合部材Bを介した配線基板35および台座部材34の接合面積を増加させることができるので、配線基板35および台座部材34を強固に接合できる。したがって、例えば光半導体素子2の駆動の熱による温度変化によって、台座部材34および配線基板35が熱膨張および熱収縮して、接合部材Bに応力が加わっても、配線基板35および台座部材34の位置がずれることを低減し、配線基板35およびコネクタ33の接続信頼性の低下を抑制できる。

した第2切欠き部342を有している。ここで、台座部材34は導電性材料で形成されている

ため、配線基板35および台座部材34の間で寄生容量が発生する。そのため、配線基板35の信号配線352に電気信号が伝達する際に、配線基板35および台座部材34の間の寄生容量に

よって、信号配線352の特性インピーダンスが変動してしまう可能性がある。また、例え

ば光半導体素子2の駆動の熱による温度変化によって、台座部材34および配線基板35が熱膨張および熱収縮すると、配線基板35の熱膨張係数および台座部材34の熱膨張係数の違いによって、配線基板35に応力が加わり、配線基板35にクラックが発生し、信号配線352が

断線する可能性がある。

に隣接した第2切欠き部342を有している。第2切欠き部342によって台座部材34が切欠かれた分、台座部材34および配線基板35の間で発生する寄生容量を小さくできるので、信号配線352の特性インピーダンスが変動することを低減できる。加えて、第2切欠き部342によって配線基板35および台座部材34の間で発生する応力を分散できるので、配線基板35にクラックが発生することを低減でき、信号配線352が断線することを低減できる。

材34の間で発生する寄生容量を小さくできる。したがって、信号配線352およびコネクタ33の特性インピーダンスの変動を抑制できる。加えて、第2切欠き部342がコネクタ33の中心導体331近傍に位置することで、コネクタ33(中心導体331)側の配線基板36の端部に生じる応力が低減されるので、コネクタ33(中心導体331)および信号配線352との接合部に加わる応力を低減でき、コネクタ33が信号配線352から剥がれることを抑制することがで

きる。

んで配線基板35の両側に位置している。両側に位置する第2切欠き部342によって、台座

部材34が切欠かれた分、台座部材34および配線基板35の間の寄生容量ならびに台座部材34および中心導体331の間の寄生容量をさらに小さくでき、信号配線352およびコネクタ33の特性インピーダンスの変動を低減できる。加えて、コネクタ33(中心導体331)側の配線

基板36の端部に生じる応力が低減されるので、コネクタ33および信号配線352との接合部

に加わる応力を低減でき、コネクタ33が信号配線352から剥がれることを抑制することが

できる。

子2の駆動の熱による温度変化によって、配線基板35および台座部材34が熱膨張し、第1切欠き部341に応力が加わった場合でも、配線基板35およびコネクタ33の両側に位置して

第1切欠き部341に隣接する第2切欠き部342の円弧状部分で応力を分散させることができるので、第2切欠き部342に応力を逃がすことができる。

低下を抑制できる。

熱膨張係数および配線基板35の熱膨張係数の差に起因する応力を低減することができるとともに、中心導体331と信号配線352との接合部に生じる応力を低減することができる。

量をさらに小さくでき、信号配線352およびコネクタ33の特性インピーダンスの変動を低

減できる。

コネクタ33の電気的な接続性の低下を抑制することができる。

以下、図1に示す光半導体素子収納用パッケージ3および実装構造体1の製造方法を説明する。なお、本発明は以下の実施形態に限定されるものではない。

部341および第2切欠き部342を有する台座部材34が形成される。

ず、例えば、酸化アルミニウム、窒化ホウ素、窒化アルミニウム、窒化ケイ素、炭化ケイ素または酸化ベリリウムなどのセラミック粉末に、有機バインダー、可塑剤または溶剤等を添加混合した混合物を所定形状に加工する。次いで、タングステンまたはモリブデンなどの高融点金属粉末を準備し、この粉末に有機バインダー、可塑剤または溶剤等を添加混合して金属ペーストを準備する。そして、所定形状に加工した混合物の表面に金属ペーストを所定のパターンに印刷する。そして、これを焼成することによって、金属ペーストを配線層362とし、所定形状に加工した混合物を基体361とする。そして、銀ろうを介して配線層372上にリード端子373を接合することで、入出力端子37が作製される。

貫通孔T1に重なるように配置するとともに、入出力端子37を第2貫通孔T2に挿入する。

基板35の所定の部分にコート部材Cを形成してもよい。

れた第1切欠き部341に配線基板35を配置する。そして、接合部材Bを溶融および固化す

ることによって、配線基板35を第1切欠き部341の内面に接合する。

制される。すなわち、第1切欠き部341によって、配線基板35の位置ずれを抑制すること

ができ、配線基板35を所望の位置に設けることができるので、中心導体331および信号配

線352の間の高周波信号の伝送特性が良好な光半導体素子収納用パッケージ3を製造でき

る。

号配線352と電気的に接続する。次いで、光半導体素子収納用パッケージ3を蓋体38にて

封止することで、実装構造体1を作製することができる。

2 光半導体素子

3 光半導体素子収納用パッケージ

31 基板

31a 主面

31b 素子搭載領域

32 枠体

321 第1側部

322 第2側部

323 第3側部

324 第4側部

33 コネクタ

331 中心導体

332 外周導体

33a 中心軸

34 台座部材

341 第1切欠き部

342 第2切欠き部

35 配線基板

351 絶縁基板

351a 幅狭部

351b 幅広部

352 信号配線

353 導電膜

36 入出力端子

361 基体

362 配線層

363 リード端子

37 シールリング

38 蓋体

4 保持部材

T1 第1貫通孔

T2 第2貫通孔

T3 第3貫通孔

B 接合部材

C コート材

Claims (5)

- 主面に光半導体素子を搭載する素子搭載領域を有する基板と、前記素子搭載領域を取り囲むように前記基板の前記主面上に配置され、貫通孔が形成された側部を有する枠体と、前記枠体の前記貫通孔を通って前記枠体の内側および外側に配置されたコネクタと、前記枠体の内側における前記基板の前記主面上に配置された台座部材と、前記台座部材上に配置された配線基板とを備え、

前記台座部材は、上面に第1切欠き部を有しており、

前記配線基板が、前記第1切欠き部内に配置され、接合部材を介して前記第1切欠き部の内面に接合されているとともに、前記コネクタに接続されており、

前記台座部材の前記上面には、前記第1切欠き部に隣接して第2切欠き部が形成されているとともに、前記配線基板が幅狭部および幅広部を有し、前記幅狭部は前記第2切欠き部によって挟まれている光半導体素子収納用パッケージ。 - 前記第2切欠き部は、前記第1切欠き部における前記貫通孔側の端部に隣接している請求項1に記載の光半導体素子収納用パッケージ。

- 前記第2切欠き部は、前記配線基板を挟んで前記配線基板の両側に位置している請求項1または2に記載の光半導体素子収納用パッケージ。

- 前記第2切欠き部は、平面視して円弧状である請求項1〜3のいずれか1つに記載の光半導体素子収納用パッケージ。

- 請求項1〜4のいずれかに記載の光半導体素子収納用パッケージと、

前記基板の前記主面の前記前記素子搭載領域に搭載された光半導体素子とを備える実装構造体。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013112981A JP6166101B2 (ja) | 2013-05-29 | 2013-05-29 | 光半導体素子収納用パッケージおよびこれを備えた実装構造体 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013112981A JP6166101B2 (ja) | 2013-05-29 | 2013-05-29 | 光半導体素子収納用パッケージおよびこれを備えた実装構造体 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2014232796A JP2014232796A (ja) | 2014-12-11 |

| JP6166101B2 true JP6166101B2 (ja) | 2017-07-19 |

Family

ID=52126015

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013112981A Active JP6166101B2 (ja) | 2013-05-29 | 2013-05-29 | 光半導体素子収納用パッケージおよびこれを備えた実装構造体 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6166101B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE102017123342A1 (de) * | 2017-10-09 | 2019-04-11 | Schott Ag | TO-Gehäuse mit hoher Reflexionsdämpfung |

| CN117767092B (zh) * | 2023-12-18 | 2024-06-28 | 武汉光至科技有限公司 | 一种缓解加工应力及螺纹应力的激光腔体结构 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002243992A (ja) * | 2001-02-20 | 2002-08-28 | Sumitomo Metal Electronics Devices Inc | パッケ−ジ、パッケ−ジの組付け方法、及び組付用治具 |

| JP3752473B2 (ja) * | 2002-06-19 | 2006-03-08 | 京セラ株式会社 | 半導体素子収納用パッケージおよび半導体装置 |

| JP2006128323A (ja) * | 2004-10-27 | 2006-05-18 | Kyocera Corp | 半導体素子収納用パッケージおよび半導体装置 |

| JP5225825B2 (ja) * | 2008-12-17 | 2013-07-03 | 新光電気工業株式会社 | 半導体素子収納用パッケージの製造方法及び半導体装置の製造方法 |

| JP5610892B2 (ja) * | 2010-07-22 | 2014-10-22 | 京セラ株式会社 | 素子収納用パッケージ、およびこれを備えた半導体装置 |

-

2013

- 2013-05-29 JP JP2013112981A patent/JP6166101B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2014232796A (ja) | 2014-12-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5981660B2 (ja) | 電子部品収納用パッケージおよび電子装置 | |

| EP2237316A1 (en) | Connection terminal, package using the same and electronic device | |

| JP6243510B2 (ja) | 電子部品収納用パッケージおよび電子装置 | |

| CN106415821B (zh) | 元件收纳用封装以及安装结构体 | |

| JP6166101B2 (ja) | 光半導体素子収納用パッケージおよびこれを備えた実装構造体 | |

| WO2015088028A1 (ja) | 素子収納用パッケージおよび実装構造体 | |

| JP5261104B2 (ja) | 回路基板および電子装置 | |

| JP6046822B2 (ja) | 素子収納用パッケージおよびこれを備えた実装構造体 | |

| JP5812671B2 (ja) | 素子収納用パッケージおよびこれを備えた半導体装置 | |

| JP2009283898A (ja) | 電子部品容器体およびそれを用いた電子部品収納用パッケージならびに電子装置 | |

| JP6829303B2 (ja) | 絶縁基体、半導体パッケージおよび半導体装置 | |

| JP5873167B2 (ja) | 半導体素子収納用パッケージおよび半導体装置 | |

| WO2015012405A1 (ja) | 素子収納用パッケージおよび実装構造体 | |

| JP5709427B2 (ja) | 素子収納用パッケージおよびこれを備えた半導体装置 | |

| JP6408661B2 (ja) | To−can型パッケージ用ヘッダーおよび半導体装置 | |

| WO2015029880A1 (ja) | 素子収納用パッケージおよび実装構造体 | |

| JP6051095B2 (ja) | 光半導体素子収納用パッケージおよびこれを備えた実装構造体 | |

| JP6162520B2 (ja) | 半導体素子収納用パッケージおよびこれを備えた実装構造体 | |

| JP5992785B2 (ja) | 半導体素子収納用パッケージおよび半導体装置 | |

| JP6239970B2 (ja) | To−can型パッケージ用ヘッダーおよび半導体装置 | |

| JP5791258B2 (ja) | 電子部品収納用パッケージおよび実装構造体 | |

| JP6219693B2 (ja) | 素子収納用パッケージおよびこれを備えた実装構造体 | |

| JP2012234880A (ja) | 素子収納用パッケージおよびこれを備えた半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160115 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20161018 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20161019 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161215 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170523 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170622 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6166101 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |