JP6166101B2 - Optical semiconductor element storage package and mounting structure including the same - Google Patents

Optical semiconductor element storage package and mounting structure including the same Download PDFInfo

- Publication number

- JP6166101B2 JP6166101B2 JP2013112981A JP2013112981A JP6166101B2 JP 6166101 B2 JP6166101 B2 JP 6166101B2 JP 2013112981 A JP2013112981 A JP 2013112981A JP 2013112981 A JP2013112981 A JP 2013112981A JP 6166101 B2 JP6166101 B2 JP 6166101B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor element

- optical semiconductor

- notch

- wiring board

- substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Description

本発明は、光半導体素子を収納するための光半導体素子収納用パッケージおよびこれを備えた実装構造体に関する。 The present invention relates to an optical semiconductor element housing package for housing an optical semiconductor element, and a mounting structure including the same.

光半導体素子を収納するための光半導体素子収納用パッケージは、主面を有する基板と、基板の主面上に配置され、貫通孔が形成された側部を有する枠体と、枠体の貫通孔を通って枠体の内側および外側に配置されたコネクタと、枠体の内側における基板の主面上に配置された台座部材と、コネクタに接続された配線基板とを備えている(例えば、特許文献1参照)。 An optical semiconductor element storage package for storing an optical semiconductor element includes a substrate having a main surface, a frame body disposed on the main surface of the substrate and having a side portion in which a through hole is formed, and through the frame body A connector disposed on the inside and outside of the frame body through the hole; a base member disposed on the main surface of the substrate on the inside of the frame body; and a wiring substrate connected to the connector (for example, Patent Document 1).

また、このような光半導体素子収納用パッケージでは、配線基板は台座部材上に配置されており、配線基板は接合部材を介して台座部材に接合されている。 In such an optical semiconductor element housing package, the wiring board is disposed on the pedestal member, and the wiring board is joined to the pedestal member via the joining member.

ここで、このような光半導体素子収納用パッケージでは、光半導体素子の駆動の際に光半導体素子から熱が発生し、この熱が台座部材および配線基板に伝わる。そのため、光半導体素子の駆動による温度変化によって、台座部材および配線基板が熱膨張および熱収縮する可能性がある。 Here, in such an optical semiconductor element housing package, heat is generated from the optical semiconductor element when the optical semiconductor element is driven, and this heat is transmitted to the base member and the wiring board. Therefore, the base member and the wiring board may be thermally expanded and contracted due to a temperature change caused by driving the optical semiconductor element.

このとき、台座部材の熱膨張係数および配線基板の熱膨張係数の違いによって、台座部材および配線基板を接合する接合部材に応力が加わり、接合部材の接合強度が低下する可能性があった。接合部材の接合強度が低下すると、配線基板および台座部材の位置がずれることで、配線基板およびコネクタの位置もずれ、配線基板およびコネクタの接続信頼性が低下する可能性があるという問題点あった。 At this time, due to the difference in the thermal expansion coefficient of the pedestal member and the thermal expansion coefficient of the wiring board, stress is applied to the joining member that joins the pedestal member and the wiring board, and the joining strength of the joining member may be reduced. When the bonding strength of the bonding member is lowered, the positions of the wiring board and the pedestal member are shifted, so that the positions of the wiring board and the connector are also shifted, and the connection reliability of the wiring board and the connector may be lowered. .

本発明は、上記の問題点に鑑みてなされたものであり、その目的は、配線基板およびコネクタの位置がずれることを低減し、配線基板およびコネクタの接続信頼性の低下を抑制できる光半導体素子収納用パッケージを提供することにある。 The present invention has been made in view of the above problems, and an object of the present invention is to reduce the displacement of the positions of the wiring board and the connector, and to suppress the decrease in the connection reliability of the wiring board and the connector. It is to provide a storage package.

本発明に係る光半導体素子収納用パッケージは、主面に光半導体素子を搭載する素子搭載領域を有する基板と、前記素子搭載領域を取り囲むように前記基板の前記主面上に配置

され、貫通孔が形成された側部を有する枠体と、前記枠体の前記貫通孔を通って前記枠体の内側および外側に配置されたコネクタと、前記枠体の内側における前記基板の前記主面上に配置された台座部材と、前記台座部材上に配置された配線基板とを備え、前記台座部材は、上面に第1切欠き部を有しており、前記配線基板が、前記第1切欠き部内に配置され、接合部材を介して前記第1切欠き部の内面に接合されているとともに、前記コネクタに接続されており、前記台座部材の前記上面には、前記第1切欠き部に隣接して第2切欠き部が形成されているとともに、前記配線基板が幅狭部および幅広部を有し、前記幅狭部は前記第2切欠き部によって挟まれている。

An optical semiconductor element storage package according to the present invention includes a substrate having an element mounting region for mounting an optical semiconductor element on a main surface, and a through hole disposed on the main surface of the substrate so as to surround the element mounting region. On the main surface of the substrate on the inner side of the frame body, a frame having a side portion formed with a connector, a connector disposed on the inner side and the outer side of the frame body through the through hole of the frame body, A pedestal member disposed on the pedestal member; the pedestal member having a first notch on an upper surface thereof; and the wiring substrate is disposed in the first notch. And is connected to the inner surface of the first cutout portion via a bonding member and connected to the connector, and the upper surface of the base member is adjacent to the first cutout portion. And a second notch is formed Having said wiring board narrow part and the wide part, the narrow portion is sandwiched by said second notch.

本発明に係る光半導体素子収納用パッケージによれば、配線基板およびコネクタの接続

信頼性の低下を抑制できる。

According to the package for housing an optical semiconductor element according to the present invention, it is possible to suppress a decrease in connection reliability between the wiring board and the connector.

本発明に係る実装構造体によれば、上記光半導体素子収納用パッケージを備えていることで、配線基板およびコネクタの接続信頼性の低下を抑制できる。 According to the mounting structure according to the present invention, it is possible to suppress a decrease in connection reliability between the wiring board and the connector by including the optical semiconductor element housing package.

[光半導体素子収納用パッケージおよび実装構造体]

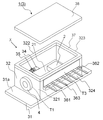

本発明の実施形態に係る光半導体素子収納用パッケージおよびこれを備えた実装構造体について、図1〜図8を参照しながら説明する。

[Optical Semiconductor Device Storage Package and Mounting Structure]

An optical semiconductor element housing package and a mounting structure including the same according to an embodiment of the present invention will be described with reference to FIGS.

実装構造体1は、光半導体素子2と、光半導体素子収納用パッケージ3とを備えている。

The

光半導体素子2は、光信号を電気信号に変換または電気信号を光信号に変換するなど光信号の処理を行なう機能を有する。図1に示すように、光半導体素子2は基板31の主面31a上に配置されている。より具体的には、図1に示すように、基板31の主面31a上には素子用台座部材21が配置されており、光半導体素子2は素子用台座部材21を介して基板31の主面31a上に配置されている。また、図1に示すように、光半導体素子2は光半導体素子収納用パッケージ3に収納されている。

The optical semiconductor element 2 has a function of processing an optical signal such as converting an optical signal into an electric signal or converting an electric signal into an optical signal. As shown in FIG. 1, the optical semiconductor element 2 is disposed on the

光半導体素子2としては、例えばレーザダイオードまたはフォトダイオードなどが挙げられる。光半導体素子2は、例えばヒ化ガリウム、ガリウム砒素リンまたは窒化ガリウムなどの半導体材料によって形成できる。 Examples of the optical semiconductor element 2 include a laser diode and a photodiode. The optical semiconductor element 2 can be formed of a semiconductor material such as gallium arsenide, phosphorus gallium arsenide, or gallium nitride.

光半導体素子収納用パッケージ3は光半導体素子2を保護する機能を有する。図1に示すように、光半導体素子収納用パッケージ3は光半導体素子2を収納している。また、光半導体素子収納用パッケージ3は、基板31と、枠体32と、コネクタ33と、台座部材34と、配線基板35と、入出力端子36と、シールリング37と、蓋体38とを備える。

The optical semiconductor

基板31は光半導体素子2を支持する機能を有する。基板31は主面31aを有している。また、基板31の主面31aは、光半導体素子2を搭載されるための素子搭載領域31bを有している。基板31は、1枚の金属板または複数の金属板を積層させた積層体からなる。基板の材料としては、例えば銅、鉄、タングステン、モリブデン、ニッケルまたはコバルトなどの金属、これらの金属を含んだ合金、セラミックス、ガラスあるいは樹脂等が挙げられる。なお、基板31の材料に金属材料を採用すれば、基板31を介して光半導体素子2から発生した熱を放熱できるので、半導体素子収納用パッケージ3の放熱性が向上する。

The

枠体32は、図1、図2および図3に示すように、光半導体素子2(素子搭載領域31b)を取り囲むように基板31の主面31a上に配置されている。枠体32は、第1側部321、第2

側部322、第3側部323および第4側部324を有している。

As shown in FIGS. 1, 2 and 3, the

It has a

第1側部321は、光ファイバやフェルールなどの光信号を入出力させる部品が挿通され

るための第1貫通孔T1を有する部位である。第2側部322は、コネクタ33が挿通された

第2貫通孔T2を有する部位である。なお、本実施形態の第2側部322は第1側部321に隣接しているが、これには限られない。第3側部323は第1側部321と対向している部位である。第4側部324は、入出力端子36が挿通された第3貫通孔T3を有し、第1側部321に隣接している部位である。なお、第4側部324は第2側部322に対向している。

The

また、図4に示すように、本実施形態では、枠体32および台座部材34が一体形成されている。なお、枠体32および台座部材34を一体形成せずに、それぞれ別体として形成してもよい。

Further, as shown in FIG. 4, in this embodiment, the

枠体32の材料としては、例えば銅、鉄、タングステン、モリブデン、ニッケルまたはコバルトなどの金属、これらの金属を含んだ合金、セラミックス、ガラスあるいは樹脂等が挙げられる。なお、本実施形態の枠体32では、金属または合金が採用されている。これによって、光半導体素子2の駆動の熱を枠体32で放熱しやすくなる。

Examples of the material of the

枠体32の外側における第1側部321上には、光ファイバやフェルールなどの部品を保持

するための保持部材4がろう材などを介して接合されている。保持部材4によって保持された光ファイバやフェルールなどは、第1側部321の第1貫通孔T1に挿通され、枠体32

の内側に位置する光半導体素子2に光接続される。

On the

Is optically connected to the optical semiconductor element 2 located inside the.

コネクタ33は、配線基板35および外部のケーブル(不図示)を接続する機能を有する。図4に示すように、コネクタ33は、第2貫通孔T2を通って枠体32の外側および内側に位置している。また、コネクタ33は、中心導体331および外周導体332を有している。

The

図4に示すように、中心導体331は枠体32の内側および外側に延在している。中心導体331は外周導体332によって取り囲まれている。中心導体331は、外周導体332の中心軸33a

を通過して枠体32の内側および外側に延在している。なお、中心導体331および外周導体332の間には、ガラスなどの誘電性材料は配置されている。

As shown in FIG. 4, the

And extends inside and outside the

外周導体332は、中心導体331の外周を取り囲むように配置されている。外周導体332は

中心導体331を保持している。図3および図4に示すように、外周導体332は、枠体32の外側における第2側部322上に配置されている。外周導体332は、枠体32の外側における第2側部322の表面に銀ろうなどのろう材を介して接合されている。より具体的には、外周導

体332は、第2側部322における第2貫通孔T2の周囲の表面に接合されている。

The outer

外周導体332は中心軸33aを有している。外周導体332の中心軸33aは第2貫通孔T2に重なっている。中心導体331は、中心軸33aに沿って配置され、誘電性材料を介して外周

導体332によって保持される。なお、図2に示すように、本実施形態の外周導体332は円筒状であるが、これに限定されない。

The outer

図4に示すように、コネクタ33では、中心導体331の一部は枠体32の外側に位置し、中

心導体331の他の一部は枠体32の内側に位置している。枠体32の外側に位置するコネクタ33の中心導体331には外部のケーブルが接続され、枠体32の内側に位置するコネクタ33の中心導体331には配線基板35が接続される。

As shown in FIG. 4, in the

本実施形態のコネクタ33は、同軸コネクタ構造を採用している。コネクタ33が同軸コネクタ構造である場合には、例えば、鉄−ニッケル−コバルト合金等の金属からなる外周導体332の中心軸33aに同じく鉄−ニッケル−コバルト合金等の金属からなる中心導体331がガラス材を介して固定されている。

The

中心導体331および外周導体332の材料は、例えば銅、鉄、タングステン、モリブデン、ニッケルまたはコバルトなどの金属、これらの金属を含んだ合金が挙げられる。

Examples of the material of the

台座部材34は配線基板35を支持する機能を有する。台座部材34は、枠体32の内側における基板31の主面31a上に配置されている。また、台座部材34は枠体32の第2貫通孔T2に隣り合っている。

The

また、図4に示すように、本実施形態の台座部材34は枠体32と一体形成されている。これによって、枠体32とは別の部材として台座部材34を備える必要がなくなるので、光半導体素子収納用パッケージ3の部品点数が少なくなる。なお、本実施形態の台座部材34は枠体32と一体形成されているが、これには限られない。すなわち、台座部材34を他の部材と一体形成してもよく、例えば台座部材34を外周導体332と一体形成してもよい。

As shown in FIG. 4, the

台座部材34は、上面に第1切欠き部341および第2切欠き部342を有している。第1切欠き部341は、基板31側に凹む凹部である。第1切欠き部341内には、配線基板35が配置されている。また、図7に示すように、第1切欠き部341の内面には接合部材Bが配置されて

おり、接合部材Bを介して第1切欠き部341の内面および配線基板35が接合されている。

接合部材Bとしては、半田または銀ろうなどのろう材などが挙げられる。

The

Examples of the bonding member B include a solder material such as solder or silver solder.

また、第2切欠き部342は基板31側に凹む凹部であり、第1切欠き部341に隣接して形成されている。また、本実施形態の第2切欠き部342は平面視して円弧状である。また、図

5および図6に示すように、本実施形態の第2切欠き部342は、第1切欠き部341における枠体32(第2側部322)側の端部に隣接している。また、本実施形態における第2切欠き

部342は、配線基板35を挟んで配線基板35の両側に位置している。

The

配線基板35は、光半導体素子2およびコネクタ33の中心導体331を接続する機能を有す

る。配線基板35は台座部材34の上面に配置されている。また、配線基板35は、台座部材34の第1切欠き部341内に配置されている。また、配線基板35は、第1切欠き部341の内面に接合部材Bを介して接合されている。すなわち、配線基板35および第1切欠き部341の間

には接合部材Bが介在している。なお、図7に示すように、本実施形態では、配線基板35の下面および配線基板35の側面の一部が、接合部材Bを介して第1切欠き部341の内面に

接合されている。

The

配線基板35は、絶縁基板351、信号配線352および導電膜353を有している。絶縁基板351は信号配線352および導電膜353を支持する機能を有している。本実施形態の絶縁基板351

は幅狭部351aおよび幅狭部351aよりも幅の大きい幅広部351bを有している。

The

Has a

絶縁基板351の材料は、例えば酸化アルミニウム質焼結体、ムライト質焼結体、炭化珪

素質焼結体、窒化アルミニウム質焼結体または窒化珪素質焼結体などのセラミックスが挙げられる。

Examples of the material of the insulating

信号配線352は、光半導体素子2およびコネクタ33の間で電気信号の伝送する機能を有

する。信号配線352は絶縁基板351の上面に配置されている。また、信号配線352は、半田

または銀ろうなどのろう材を介して枠体32の内側に位置するコネクタ33の中心導体331の

端部に接続されている。信号配線352は絶縁基板351の長手方向に延在している。

The

導電膜353は絶縁基板351の上面に配置されている。また、図7に示すように、本実施形態の導電膜353は、絶縁基板351の下面にも形成されている。また、絶縁基板351の上面に

位置する導電膜353は、信号配線352の両側に位置しており、信号配線352に接触していな

い。また、絶縁基板351の上面および下面に位置する導電膜353は、絶縁基板351の長手方

向に延在している。なお、導電膜353は、例えばグランド電位など一定の電位に設定され

ている。

The

また、信号配線352および導電膜353の一部にはアルミナ、クロムなどのコート材Cが形成されている。なお、図6では、コート材Cの形成領域が斜線で示されている。

In addition, a coating material C such as alumina or chromium is formed on part of the

配線基板35では、絶縁基板351の上面に信号配線352から離して導電膜353を形成するこ

とで、コプレーナ線路が構成され、信号配線352を伝達する高周波信号を所定のインピー

ダンス値に整合させやすくなり、高周波信号に発生する伝送損失を抑制させ、高周波信号を効率良く入出力させることができる。

In the

入出力端子36は、光半導体素子2および外部回路基板(不図示)の間で電気信号の伝送する機能を有する。図1および図2に示すように、入出力端子36は枠体32の第3側部323

の第3貫通孔T3に挿通されている。また、入出力端子36は、基体361と、配線層362と、リード端子363とを有している。

The input /

The third through hole T3 is inserted. The input /

基体361は、配線層362およびリード端子363を支持する機能を有する。基体361の材料としては、例えば、酸化アルミニウム質焼結体、ムライト質焼結体、炭化珪素質焼結体、窒化アルミニウム質焼結体または窒化珪素質焼結体などのセラミックスが挙げられる。

The

配線層362は、光半導体素子2が光信号から変換処理した電気信号をリード端子363まで伝送する機能を有する。図1に示すように、複数の配線層362が基体361上に配置されている。また、複数の配線層362は枠体32の外側から内側にかけて延在して配置されている。

枠体32の内側に位置する配線層362の部分は、ボンディングワイヤなどによって光半導体

素子2と電気的に接続される。一方、枠体32の外側に位置する配線層362の部分は、半田

またはろう材などによってリード端子363と電気的に接続される。配線層362の材料としては、例えば銅、銀、金、アルミニウム、ニッケル、モリブデン、タングステン、マンガンまたはクロムなどの金属材料、あるいはこれらの金属材料を含んだ合金が挙げられる。

The

A portion of the

リード端子363は、光半導体素子2から配線層362を介して伝送される電気信号を外部に伝送する機能を有する。リード端子363は配線層362に接続されている。また、リード端子363は、例えば銅、鉄、タングステン、モリブデン、ニッケルまたはコバルトなどの金属

材料、あるいはこれらの金属材料を含んだ合金からなる。

The

シールリング37は、枠体32および蓋体38を接合する機能を有する。図1に示すように、シールリング37は枠体32の第1側部321〜第4側部324の端面上に配置されており、平面視して光半導体素子2を取り囲んでいる。シールリング37の材料としては、例えば鉄、銅、銀、ニッケル、クロム、コバルト、モリブデンまたはタングステンなどの金属材料、あるいはこれらの金属材料を複数組み合わせた合金などが挙げられる。

The

蓋体38は、光半導体素子2を保護する機能を有する。また、図1に示すように、蓋体38は光半導体素子収納用パッケージ3の開口を封止している。蓋体38は、例えばシールリング37と同様の金属材料で形成することができる。

The

光半導体素子収納用パッケージ3では、配線基板35が台座部材34の第1切欠き部341内

に配置されるとともに、第1切欠き部341の内面に接合されている。第1切欠き部341の内面を利用することによって、接合部材Bを介した配線基板35および台座部材34の接合面積を増加させることができるので、配線基板35および台座部材34を強固に接合できる。したがって、例えば光半導体素子2の駆動の熱による温度変化によって、台座部材34および配線基板35が熱膨張および熱収縮して、接合部材Bに応力が加わっても、配線基板35および台座部材34の位置がずれることを低減し、配線基板35およびコネクタ33の接続信頼性の低下を抑制できる。

In the optical semiconductor

また、光半導体素子収納用パッケージ3では、台座部材34が、第1切欠き部341に隣接

した第2切欠き部342を有している。ここで、台座部材34は導電性材料で形成されている

ため、配線基板35および台座部材34の間で寄生容量が発生する。そのため、配線基板35の信号配線352に電気信号が伝達する際に、配線基板35および台座部材34の間の寄生容量に

よって、信号配線352の特性インピーダンスが変動してしまう可能性がある。また、例え

ば光半導体素子2の駆動の熱による温度変化によって、台座部材34および配線基板35が熱膨張および熱収縮すると、配線基板35の熱膨張係数および台座部材34の熱膨張係数の違いによって、配線基板35に応力が加わり、配線基板35にクラックが発生し、信号配線352が

断線する可能性がある。

In the optical semiconductor

これに対して、光半導体素子収納用パッケージ3では、台座部材34が第1切欠き部341

に隣接した第2切欠き部342を有している。第2切欠き部342によって台座部材34が切欠かれた分、台座部材34および配線基板35の間で発生する寄生容量を小さくできるので、信号配線352の特性インピーダンスが変動することを低減できる。加えて、第2切欠き部342によって配線基板35および台座部材34の間で発生する応力を分散できるので、配線基板35にクラックが発生することを低減でき、信号配線352が断線することを低減できる。

On the other hand, in the optical semiconductor

The

また、光半導体素子収納用パッケージ3では、第2切欠き部342が、第1切欠き部341における第2貫通孔T2側の端部に隣接している。すなわち、第2切欠き部342がコネクタ33の中心導体331近傍に位置している。これによって、配線基板35および台座部材34の間で発生する寄生容量を小さくできることに加え、コネクタ33(中心導体331)および台座部

材34の間で発生する寄生容量を小さくできる。したがって、信号配線352およびコネクタ33の特性インピーダンスの変動を抑制できる。加えて、第2切欠き部342がコネクタ33の中心導体331近傍に位置することで、コネクタ33(中心導体331)側の配線基板36の端部に生じる応力が低減されるので、コネクタ33(中心導体331)および信号配線352との接合部に加わる応力を低減でき、コネクタ33が信号配線352から剥がれることを抑制することがで

きる。

In the optical semiconductor

さらに、光半導体素子収納用パッケージ3では、第2切欠き部342が、配線基板35を挟

んで配線基板35の両側に位置している。両側に位置する第2切欠き部342によって、台座

部材34が切欠かれた分、台座部材34および配線基板35の間の寄生容量ならびに台座部材34および中心導体331の間の寄生容量をさらに小さくでき、信号配線352およびコネクタ33の特性インピーダンスの変動を低減できる。加えて、コネクタ33(中心導体331)側の配線

基板36の端部に生じる応力が低減されるので、コネクタ33および信号配線352との接合部

に加わる応力を低減でき、コネクタ33が信号配線352から剥がれることを抑制することが

できる。

Further, in the optical semiconductor

また、第2切欠き部342は平面視して円弧状である。これによって、例えば光半導体素

子2の駆動の熱による温度変化によって、配線基板35および台座部材34が熱膨張し、第1切欠き部341に応力が加わった場合でも、配線基板35およびコネクタ33の両側に位置して

第1切欠き部341に隣接する第2切欠き部342の円弧状部分で応力を分散させることができるので、第2切欠き部342に応力を逃がすことができる。

The

また、光半導体素子収納用パッケージ3では、配線基板35が幅狭部351aおよび幅広部351bを有し、幅狭部351aは第2切欠き部342によって挟まれている。強度の小さくなりやすい配線基板35の幅狭部351aを円弧状の第2切欠き部342で挟むことで、配線基板35の幅狭部351aに加わる応力を低減できるので、配線基板35およびコネクタ33の接続信頼性の

低下を抑制できる。

In the optical semiconductor

また、図6に示すように、本実施形態の幅狭部351aは、中心導体331および信号配線352の接合部に比べて枠体32のより内側まで形成されている。これによって、台座部材34の

熱膨張係数および配線基板35の熱膨張係数の差に起因する応力を低減することができるとともに、中心導体331と信号配線352との接合部に生じる応力を低減することができる。

Further, as shown in FIG. 6, the

また、図6に示すように、本実施形態の第2切欠き部342は、幅狭部351aに比べて枠体32のより内側まで形成されている。これによって、台座部材34が切欠かれた分、台座部材34および配線基板35の間の寄生容量ならびに台座部材34および中心導体331の間の寄生容

量をさらに小さくでき、信号配線352およびコネクタ33の特性インピーダンスの変動を低

減できる。

Further, as shown in FIG. 6, the

また、実装構造体1は、上記の光半導体素子収納用パッケージ3の内部に光半導体素子2を収納している。光半導体素子収納用パッケージ3では、配線基板35およびコネクタ33の中心導体331の接続信頼性の低下を抑制できる。これによって、光半導体素子2および

コネクタ33の電気的な接続性の低下を抑制することができる。

The mounting

本発明は上記実施形態に限定されるものではなく、本発明の要旨を逸脱しない範囲において種々の変更、改良などが可能である。 The present invention is not limited to the above-described embodiment, and various changes and improvements can be made without departing from the scope of the present invention.

[光半導体素子収納用パッケージおよび実装構造体の製造方法]

以下、図1に示す光半導体素子収納用パッケージ3および実装構造体1の製造方法を説明する。なお、本発明は以下の実施形態に限定されるものではない。

[Optical Semiconductor Device Storage Package and Mounting Structure Manufacturing Method]

A method for manufacturing the optical semiconductor

まず、基板31、枠体32および保持部材4を作製する。基板31、枠体32および保持部材4のそれぞれは、溶融した金属材料を型枠に鋳込んで固化させたインゴットを金属加工法を用いることによって所定形状に成形することで作製される。そして、枠体32には、第1貫通孔T1〜第3貫通孔T3が形成されるとともに、第2側部322と一体的に、第1切欠き

部341および第2切欠き部342を有する台座部材34が形成される。

First, the

次に、基体361、配線層362およびリード端子363を有する入出力端子36を作製する。ま

ず、例えば、酸化アルミニウム、窒化ホウ素、窒化アルミニウム、窒化ケイ素、炭化ケイ素または酸化ベリリウムなどのセラミック粉末に、有機バインダー、可塑剤または溶剤等を添加混合した混合物を所定形状に加工する。次いで、タングステンまたはモリブデンなどの高融点金属粉末を準備し、この粉末に有機バインダー、可塑剤または溶剤等を添加混合して金属ペーストを準備する。そして、所定形状に加工した混合物の表面に金属ペーストを所定のパターンに印刷する。そして、これを焼成することによって、金属ペーストを配線層362とし、所定形状に加工した混合物を基体361とする。そして、銀ろうを介して配線層372上にリード端子373を接合することで、入出力端子37が作製される。

Next, the input /

次に、枠体32を基板31の主面31aに配置し、保持部材4を枠体32の第1側部321の第1

貫通孔T1に重なるように配置するとともに、入出力端子37を第2貫通孔T2に挿入する。

Next, the

The input /

次に、配線基板35を作製する。基体361および配線層362で説明した作製方法と同様に、セラミック混合物を所定形状に加工し、金属ペーストをセラミック混合物の所定部分に印刷する。そして、これを焼成することによって、金属ペーストを信号配線352、導電膜353、所定形状に加工した混合物を絶縁基板351とする配線基板35が作製される。なお、配線

基板35の所定の部分にコート部材Cを形成してもよい。

Next, the

次に、台座部材34の第1切欠き部341に接合部材Bを配置し、この接合部材Bが配置さ

れた第1切欠き部341に配線基板35を配置する。そして、接合部材Bを溶融および固化す

ることによって、配線基板35を第1切欠き部341の内面に接合する。

Next, the joining member B is disposed in the

このとき、接合部材Bを介して配線基板35を台座部材34に接合する際に、配線基板35の位置が変動した場合でも、第1切欠き部341の内面によって配線基板35の位置の変動が抑

制される。すなわち、第1切欠き部341によって、配線基板35の位置ずれを抑制すること

ができ、配線基板35を所望の位置に設けることができるので、中心導体331および信号配

線352の間の高周波信号の伝送特性が良好な光半導体素子収納用パッケージ3を製造でき

る。

At this time, even when the position of the

次に、外周導体332の中心軸33aに中心導体331をガラスなどで接合固定させることで、コネクタ33を作製する。そして、コネクタ33を第2貫通孔T2に挿入するとともに、半田を溶融および固化させることによって、コネクタ33を枠体32に固定するとともに、中心導体331および配線基板35を接合する。

Next, the

最後に、光半導体素子2を素子用台座部材21を介して基板31の主面31aの素子搭載領域31b上に配置し、光半導体素子2をボンディングワイヤなどを介して配線層362および信

号配線352と電気的に接続する。次いで、光半導体素子収納用パッケージ3を蓋体38にて

封止することで、実装構造体1を作製することができる。

Finally, the optical semiconductor element 2 is disposed on the

1 実装構造体

2 光半導体素子

3 光半導体素子収納用パッケージ

31 基板

31a 主面

31b 素子搭載領域

32 枠体

321 第1側部

322 第2側部

323 第3側部

324 第4側部

33 コネクタ

331 中心導体

332 外周導体

33a 中心軸

34 台座部材

341 第1切欠き部

342 第2切欠き部

35 配線基板

351 絶縁基板

351a 幅狭部

351b 幅広部

352 信号配線

353 導電膜

36 入出力端子

361 基体

362 配線層

363 リード端子

37 シールリング

38 蓋体

4 保持部材

T1 第1貫通孔

T2 第2貫通孔

T3 第3貫通孔

B 接合部材

C コート材

DESCRIPTION OF

31 Board

31a Main surface

31b Device mounting area

32 frame

321 first side

322 Second side

323 3rd side

324 4th side

33 Connector

331 Center conductor

332 outer conductor

33a Center axis

34 Base member

341 1st notch

342 Second notch

35 Wiring board

351 Insulation substrate

351a Narrow part

351b Wide part

352 signal wiring

353 conductive film

36 I / O terminals

361 substrate

362 Wiring layer

363 Lead terminal

37 Seal ring

38

Claims (5)

前記台座部材は、上面に第1切欠き部を有しており、

前記配線基板が、前記第1切欠き部内に配置され、接合部材を介して前記第1切欠き部の内面に接合されているとともに、前記コネクタに接続されており、

前記台座部材の前記上面には、前記第1切欠き部に隣接して第2切欠き部が形成されているとともに、前記配線基板が幅狭部および幅広部を有し、前記幅狭部は前記第2切欠き部によって挟まれている光半導体素子収納用パッケージ。 A substrate having an element mounting region for mounting an optical semiconductor element on a main surface; and a frame having a side portion disposed on the main surface of the substrate so as to surround the element mounting region and having a through hole formed thereon; A connector disposed on the inside and outside of the frame through the through-hole of the frame, a pedestal member disposed on the main surface of the substrate on the inside of the frame, and on the pedestal member A wiring board arranged,

The pedestal member has a first notch on the upper surface,

The wiring board is disposed in the first cutout part, joined to the inner surface of the first cutout part via a joining member, and connected to the connector ,

On the upper surface of the pedestal member, a second notch is formed adjacent to the first notch, and the wiring board has a narrow part and a wide part, and the narrow part is An optical semiconductor element storage package sandwiched between the second cutout portions .

前記基板の前記主面の前記前記素子搭載領域に搭載された光半導体素子とを備える実装構造体。 The package for optical semiconductor element accommodation according to any one of claims 1 to 4 ,

A mounting structure comprising: an optical semiconductor element mounted on the element mounting region of the main surface of the substrate.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013112981A JP6166101B2 (en) | 2013-05-29 | 2013-05-29 | Optical semiconductor element storage package and mounting structure including the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013112981A JP6166101B2 (en) | 2013-05-29 | 2013-05-29 | Optical semiconductor element storage package and mounting structure including the same |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2014232796A JP2014232796A (en) | 2014-12-11 |

| JP6166101B2 true JP6166101B2 (en) | 2017-07-19 |

Family

ID=52126015

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013112981A Active JP6166101B2 (en) | 2013-05-29 | 2013-05-29 | Optical semiconductor element storage package and mounting structure including the same |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6166101B2 (en) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE102017123342A1 (en) * | 2017-10-09 | 2019-04-11 | Schott Ag | TO housing with high reflection loss |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002243992A (en) * | 2001-02-20 | 2002-08-28 | Sumitomo Metal Electronics Devices Inc | Package, method for attaching package, and tool for attachment |

| JP3752473B2 (en) * | 2002-06-19 | 2006-03-08 | 京セラ株式会社 | Semiconductor element storage package and semiconductor device |

| JP2006128323A (en) * | 2004-10-27 | 2006-05-18 | Kyocera Corp | Semiconductor device and storing package thereof |

| JP5225825B2 (en) * | 2008-12-17 | 2013-07-03 | 新光電気工業株式会社 | Manufacturing method of semiconductor element storage package and manufacturing method of semiconductor device |

| JP5610892B2 (en) * | 2010-07-22 | 2014-10-22 | 京セラ株式会社 | Element storage package and semiconductor device including the same |

-

2013

- 2013-05-29 JP JP2013112981A patent/JP6166101B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2014232796A (en) | 2014-12-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5981660B2 (en) | Electronic component storage package and electronic device | |

| EP2237316A1 (en) | Connection terminal, package using the same and electronic device | |

| JP6243510B2 (en) | Electronic component storage package and electronic device | |

| US9805995B2 (en) | Element-accommodating package and mounting structure | |

| JP6166101B2 (en) | Optical semiconductor element storage package and mounting structure including the same | |

| JP6082114B2 (en) | Device storage package and mounting structure | |

| JP6046822B2 (en) | Device storage package and mounting structure including the same | |

| JP5812671B2 (en) | Device storage package and semiconductor device including the same | |

| JP5873167B2 (en) | Semiconductor element storage package and semiconductor device | |

| JP5261104B2 (en) | Circuit board and electronic device | |

| JP6829303B2 (en) | Insulation substrates, semiconductor packages and semiconductor devices | |

| WO2015088028A1 (en) | Element housing package and mounting structure | |

| JP5709427B2 (en) | Device storage package and semiconductor device including the same | |

| JP6051095B2 (en) | Optical semiconductor element storage package and mounting structure including the same | |

| JP2009283898A (en) | Electronic part container, package for storing electronic part using the same and electronic device | |

| JP6162520B2 (en) | Package for housing semiconductor element and mounting structure including the same | |

| JP5992785B2 (en) | Semiconductor element storage package and semiconductor device | |

| JP6239970B2 (en) | TO-CAN type package header and semiconductor device | |

| JP5791258B2 (en) | Electronic component storage package and mounting structure | |

| JP6408661B2 (en) | TO-CAN type package header and semiconductor device | |

| JP6219693B2 (en) | Device storage package and mounting structure including the same | |

| WO2015029880A1 (en) | Package for housing elements and mounting structure | |

| JP5725900B2 (en) | Semiconductor element storage package and semiconductor device including the same | |

| JP2012234880A (en) | Package for housing element, and semiconductor device including the package | |

| JP2006093611A (en) | Electronic component accommodating package and electronic device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160115 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20161018 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20161019 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161215 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170523 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170622 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6166101 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |