JP6136430B2 - 設計支援装置、設計支援方法、および設計支援プログラム - Google Patents

設計支援装置、設計支援方法、および設計支援プログラム Download PDFInfo

- Publication number

- JP6136430B2 JP6136430B2 JP2013062350A JP2013062350A JP6136430B2 JP 6136430 B2 JP6136430 B2 JP 6136430B2 JP 2013062350 A JP2013062350 A JP 2013062350A JP 2013062350 A JP2013062350 A JP 2013062350A JP 6136430 B2 JP6136430 B2 JP 6136430B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- cells

- flip

- flop

- layout data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F30/00—Computer-aided design [CAD]

- G06F30/30—Circuit design

- G06F30/39—Circuit design at the physical level

- G06F30/392—Floor-planning or layout, e.g. partitioning or placement

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Architecture (AREA)

- Evolutionary Computation (AREA)

- Geometry (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

Description

図3は、設計支援装置のハードウェア構成例を示すブロック図である。図3において、設計支援装置100は、CPU301と、ROM302と、RAM303と、ディスクドライブ304と、ディスク305と、を有する。設計支援装置100は、I/F306と、入力装置307と、出力装置308と、を有する。また、各部はバス300によってそれぞれ接続される。

図4は、設計支援装置の機能的構成例を示すブロック図である。設計支援装置100は、領域サイズ算出部401と、領域情報生成部402と、第1データ生成部403と、第2データ生成部404と、を有する。さらに、設計支援装置100は、判断部405と、検出部406と、距離算出部407と、選択部408と、対応情報生成部409と、出力部410と、を有する。各部の処理は、たとえば、CPU301がアクセス可能な記憶装置に記憶された算出プログラムにコーディングされる。そして、CPU301が記憶装置から算出プログラムを読み出して、試験支援プログラムにコーディングされている処理を実行する。これにより、各部の処理が実現される。また、各部の処理結果は、たとえば、RAM303、ディスク305などの記憶装置に記憶される。

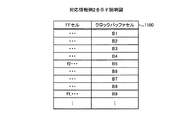

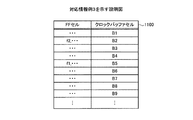

そして、対応情報生成部409は、第2レイアウトデータl2に基づいて、領域情報が示す複数の領域の各々について領域内のFFセルと、領域内のクロックバッファセルと、を対応付けた対応情報を生成する。

また、判断部405は、第2レイアウトデータl2に基づいて、複数の領域の各々について、領域内のフリップフロップセルの数が、領域内のバッファセルについての接続可能個数よりも多いか少ないかを判断する。

また、距離算出部407は、検出された領域内のバッファセルの各々について、検出された領域内のバッファセルと、対象領域内のフリップフロップセルの各々と、の距離を算出する。選択部408は、検出された領域内のバッファセルと、対象領域内のフリップフロップセルと、の組み合わせの中から、同一のフリップフロップセルを含む組み合わせを複数選択せず、算出された距離が短い順に、差分の組み合わせを選択する。ここでの差分は、対象領域内のフリップフロップセルの数と、接続可能個数と、の差分である。

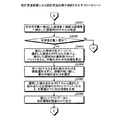

図20〜23は、設計支援装置による設計支援処理手順例1を示すフローチャートである。設計支援装置100は、クロックバッファの駆動可能個数を取得し(ステップS2001)、スキューの条件を保証可能な範囲(基準領域のサイズ)を算出する(ステップS2002)。ここでは、上述したように、基準領域の外周が算出される。設計支援装置100は、回路内のセル配置可能領域を一定間隔で区切った複数の領域を示す領域情報を生成する(ステップS2003)。一定間隔は、算出された基準領域の外周に基づく値である。

前記領域情報生成部によって生成された前記領域情報が示す前記複数の領域の各々に少なくとも1つ設けられる、他のセルにクロック信号を供給可能なバッファセルの配置を示す第1レイアウトデータを生成する第1データ生成部と、

前記第1データ生成部によって生成された前記第1レイアウトデータに基づいて、前記バッファセルの配置と、前記所定領域内に設けられるフリップフロップセルの配置と、を示す第2レイアウトデータを生成する第2データ生成部と、

前記第2データ生成部によって生成された前記第2レイアウトデータを出力する出力部と、

を有することを特徴とする設計支援装置。

前記出力部は、

前記第2レイアウトデータと、前記対応情報生成部によって生成された前記対応情報と、を関連付けて出力することを特徴とする付記1に記載の設計支援装置。

前記判断部によって前記フリップフロップセルの数が前記供給可能な数よりも多いと判断された前記領域内のフリップフロップセルのうち、前記供給可能な数のフリップフロップセル以外のフリップフロップセルを、前記判断部によって前記フリップフロップセルの数が前記供給可能な数よりも少ないと判断された前記領域内のバッファセルに対応付けた対応情報を生成する対応情報生成部と、

を有し、

前記出力部は、

前記第2レイアウトデータと、前記対応情報生成部によって生成された前記対応情報と、を関連付けて出力することを特徴とする付記1または2に記載の設計支援装置。

前記対応情報生成部は、

前記供給可能な数のフリップフロップセル以外のフリップフロップセルを、前記検出部によって検出された前記領域内のバッファセルに対応付けた対応情報を生成することを特徴とする付記3に記載の設計支援装置。

前記隣接する領域の中で、前記領域内のフリップフロップセルの数が最も少ない領域を検出することを特徴とする付記4に記載の設計支援装置。

前記供給可能な数よりも多いと判断された前記領域内のフリップフロップセルの中で、前記算出部によって算出された距離が短い順に、前記供給可能な数のフリップフロップセル以外のフリップフロップセルを選択する選択部と、

を有し、

前記対応情報生成部は、

前記選択部によって選択されたフリップフロップセルを、検出された前記領域内のバッファセルに対応付けた対応情報を生成することを特徴とする付記4または5に記載の設計支援装置。

検出された前記領域内のバッファセルと、前記供給可能な数よりも多いと判断された前記領域内のフリップフロップセルと、の組み合わせの中から、同一のフリップフロップセルを含む組み合わせを複数選択せず、前記算出部によって算出された距離が短い順に、前記供給可能な数よりも多いと判断された前記領域内のフリップフロップセルの数と、前記供給可能な数と、の差分の組み合わせを選択する選択部と、

を有し、

前記対応情報生成部は、

前記選択部によって選択された前記組み合わせに含まれるフリップフロップセルと、選択された前記組み合わせに含まれるバッファセルと、を対応付けた対応情報を生成することを特徴とする付記4に記載の設計支援装置。

前記検出部による検出によって前記隣接する領域が得られなかった場合、前記対応情報生成部による前記対応情報の生成を行わずに、前記供給可能な数よりも多いと判断された前記領域の周辺に前記フリップフロップセルの数が多いことを示す情報を出力することを特徴とする付記4〜6のいずれか一つに記載の設計支援装置。

回路内の所定領域を一定間隔で区切った複数の領域を示す領域情報を生成し、

生成した前記領域情報が示す前記複数の領域の各々に少なくとも1つ設けられる、他のセルにクロック信号を供給可能なバッファセルの配置を示す第1レイアウトデータを生成し、

生成した前記第1レイアウトデータに基づいて、前記バッファセルの配置と、前記所定領域内に設けられるフリップフロップセルの配置と、を示す第2レイアウトデータを生成する、

処理を実行することを特徴とする設計支援方法。

回路内の所定領域を一定間隔で区切った複数の領域を示す領域情報を生成し、

生成した前記領域情報が示す前記複数の領域の各々に少なくとも1つ設けられる、他のセルにクロック信号を供給可能なバッファセルの配置を示す第1レイアウトデータを生成し、

生成した前記第1レイアウトデータに基づいて、前記バッファセルの配置と、前記所定領域内に設けられるフリップフロップセルの配置と、を示す第2レイアウトデータを生成する、

処理を実行させることを特徴とする設計支援プログラム。

生成した前記領域情報が示す前記複数の領域の各々に少なくとも1つ設けられる、他のセルにクロック信号を供給可能なバッファセルの配置を示す第1レイアウトデータを生成し、

生成した前記第1レイアウトデータに基づいて、前記バッファセルの配置と、前記所定領域内に設けられるフリップフロップセルの配置と、を示す第2レイアウトデータを生成する、

処理をコンピュータに実行させる設計支援プログラムを記録したことを特徴とする記録媒体。

402 領域情報生成部

403 第1データ生成部

404 第2データ生成部

405 判断部

406 検出部

407 距離算出部

408 選択部

409 対応情報生成部

410 出力部

1100 対応情報

area 所定領域

a1〜a4,ar1〜ar9 領域

buf1〜buf4,B1〜B9 クロックバッファセル

l1 第1レイアウトデータ

l2 第2レイアウトデータ

Claims (8)

- 回路内の所定領域を一定間隔で区切った複数の領域を示す領域情報を生成する領域情報生成部と、

前記領域情報生成部によって生成された前記領域情報が示す前記複数の領域の各々に少なくとも1つ設けられる、他のセルにクロック信号を供給可能なバッファセルの配置を示す第1レイアウトデータを生成する第1データ生成部と、

前記第1データ生成部によって生成された前記第1レイアウトデータに基づいて、前記バッファセルの配置と、前記所定領域内に設けられるフリップフロップセルの配置と、を示す第2レイアウトデータを生成する第2データ生成部と、

前記第2レイアウトデータに基づいて、前記複数の領域の各々の領域について、前記領域内のフリップフロップセルの数が、前記領域内のバッファセルが前記クロック信号を供給可能な数よりも多いか少ないかを判断する判断部と、

前記判断部によって前記領域内のフリップフロップセルの数が前記供給可能な数よりも少ないと判断された領域のうち、前記供給可能な数よりも多いと判断された前記領域に隣接する領域を検出する検出部と、

前記供給可能な数よりも多いと判断された前記領域内のフリップフロップセルの各々と、前記検出部によって検出された前記領域内のバッファセルと、の距離を算出する算出部と、

前記供給可能な数よりも多いと判断された前記領域内のフリップフロップセルの中で、前記算出部によって算出された距離が短い順に、前記供給可能な数のフリップフロップセル以外のフリップフロップセルを選択する選択部と、

前記選択部によって選択されたフリップフロップセルを、前記検出部によって検出された前記領域内のバッファセルに対応付けた対応情報を生成する対応情報生成部と、

前記第2レイアウトデータと、前記対応情報生成部によって生成された前記対応情報と、を関連付けて出力する出力部と、

を有することを特徴とする設計支援装置。 - 前記検出部は、

前記隣接する領域の中で、前記領域内のフリップフロップセルの数が最も少ない領域を検出することを特徴とする請求項1に記載の設計支援装置。 - 前記出力部は、

前記検出部による検出によって前記隣接する領域が得られなかった場合、前記対応情報生成部による前記対応情報の生成を行わずに、前記供給可能な数よりも多いと判断された前記領域の周辺に前記フリップフロップセルの数が多いことを示す情報を出力することを特徴とする請求項1または2に記載の設計支援装置。 - 回路内の所定領域を一定間隔で区切った複数の領域を示す領域情報を生成する領域情報生成部と、

前記領域情報生成部によって生成された前記領域情報が示す前記複数の領域の各々に少なくとも1つ設けられる、他のセルにクロック信号を供給可能なバッファセルの配置を示す第1レイアウトデータを生成する第1データ生成部と、

前記第1データ生成部によって生成された前記第1レイアウトデータに基づいて、前記バッファセルの配置と、前記所定領域内に設けられるフリップフロップセルの配置と、を示す第2レイアウトデータを生成する第2データ生成部と、

前記第2レイアウトデータに基づいて、前記複数の領域の各々の領域について、前記領域内のフリップフロップセルの数が、前記領域内のバッファセルが前記クロック信号を供給可能な数よりも多いか少ないかを判断する判断部と、

前記判断部によって前記領域内のフリップフロップセルの数が前記供給可能な数よりも少ないと判断された領域のうち、前記供給可能な数よりも多いと判断された前記領域に隣接する領域を検出する検出部と、

前記検出部によって検出された前記領域の各々について、検出された前記領域内のバッファセルと、前記供給可能な数よりも多いと判断された前記領域内のフリップフロップセルの各々と、の距離を算出する算出部と、

検出された前記領域内のバッファセルと、前記供給可能な数よりも多いと判断された前記領域内のフリップフロップセルと、の組み合わせの中から、同一のフリップフロップセルを含む組み合わせを複数選択せず、前記算出部によって算出された距離が短い順に、前記供給可能な数よりも多いと判断された前記領域内のフリップフロップセルの数と、前記供給可能な数と、の差分の組み合わせを選択する選択部と、

前記選択部によって選択された前記組み合わせに含まれるフリップフロップセルと、選択された前記組み合わせに含まれるバッファセルと、を対応付けた対応情報を生成する対応情報生成部と、

前記第2レイアウトデータと、前記対応情報生成部によって生成された前記対応情報と、を関連付けて出力する出力部と、

を有することを特徴とする設計支援装置。 - コンピュータが、

回路内の所定領域を一定間隔で区切った複数の領域を示す領域情報を生成し、

生成した前記領域情報が示す前記複数の領域の各々に少なくとも1つ設けられる、他のセルにクロック信号を供給可能なバッファセルの配置を示す第1レイアウトデータを生成し、

生成した前記第1レイアウトデータに基づいて、前記バッファセルの配置と、前記所定領域内に設けられるフリップフロップセルの配置と、を示す第2レイアウトデータを生成し、

生成した前記第2レイアウトデータに基づいて、前記複数の領域の各々の領域について、前記領域内のフリップフロップセルの数が、前記領域内のバッファセルが前記クロック信号を供給可能な数よりも多いか少ないかを判断し、

前記領域内のフリップフロップセルの数が前記供給可能な数よりも少ないと判断した領域のうち、前記供給可能な数よりも多いと判断した前記領域に隣接する領域を検出し、

前記供給可能な数よりも多いと判断した前記領域内のフリップフロップセルの各々と、検出された前記領域内のバッファセルと、の距離を算出し、

前記供給可能な数よりも多いと判断した前記領域内のフリップフロップセルの中で、算出した前記距離が短い順に、前記供給可能な数のフリップフロップセル以外のフリップフロップセルを選択し、

選択した前記フリップフロップセルを、検出した前記領域内のバッファセルに対応付けた対応情報を生成し、

前記第2レイアウトデータと、生成した前記対応情報と、を関連付けて出力する、

処理を実行することを特徴とする設計支援方法。 - コンピュータが、

回路内の所定領域を一定間隔で区切った複数の領域を示す領域情報を生成し、

生成した前記領域情報が示す前記複数の領域の各々に少なくとも1つ設けられる、他のセルにクロック信号を供給可能なバッファセルの配置を示す第1レイアウトデータを生成し、

生成した前記第1レイアウトデータに基づいて、前記バッファセルの配置と、前記所定領域内に設けられるフリップフロップセルの配置と、を示す第2レイアウトデータを生成し、

前記第2レイアウトデータに基づいて、前記複数の領域の各々の領域について、前記領域内のフリップフロップセルの数が、前記領域内のバッファセルが前記クロック信号を供給可能な数よりも多いか少ないかを判断し、

前記領域内のフリップフロップセルの数が前記供給可能な数よりも少ないと判断した前記領域のうち、前記供給可能な数よりも多いと判断した前記領域に隣接する領域を検出し、

検出した前記領域の各々について、検出した前記領域内のバッファセルと、前記供給可能な数よりも多いと判断した前記領域内のフリップフロップセルの各々と、の距離を算出し、

検出した前記領域内のバッファセルと、前記供給可能な数よりも多いと判断した前記領域内のフリップフロップセルと、の組み合わせの中から、同一のフリップフロップセルを含む組み合わせを複数選択せず、算出した前記距離が短い順に、前記供給可能な数よりも多いと判断した前記領域内のフリップフロップセルの数と、前記供給可能な数と、の差分の組み合わせを選択し、

選択した前記組み合わせに含まれるフリップフロップセルと、選択した前記組み合わせに含まれるバッファセルと、を対応付けた対応情報を生成し、

前記第2レイアウトデータと、生成した前記対応情報と、を関連付けて出力する、

処理を実行することを特徴とする設計支援方法。 - コンピュータに、

回路内の所定領域を一定間隔で区切った複数の領域を示す領域情報を生成し、

生成した前記領域情報が示す前記複数の領域の各々に少なくとも1つ設けられる、他のセルにクロック信号を供給可能なバッファセルの配置を示す第1レイアウトデータを生成し、

生成した前記第1レイアウトデータに基づいて、前記バッファセルの配置と、前記所定領域内に設けられるフリップフロップセルの配置と、を示す第2レイアウトデータを生成し、

生成した前記第2レイアウトデータに基づいて、前記複数の領域の各々の領域について、前記領域内のフリップフロップセルの数が、前記領域内のバッファセルが前記クロック信号を供給可能な数よりも多いか少ないかを判断し、

前記領域内のフリップフロップセルの数が前記供給可能な数よりも少ないと判断した領域のうち、前記供給可能な数よりも多いと判断した前記領域に隣接する領域を検出し、

前記供給可能な数よりも多いと判断した前記領域内のフリップフロップセルの各々と、検出された前記領域内のバッファセルと、の距離を算出し、

前記供給可能な数よりも多いと判断した前記領域内のフリップフロップセルの中で、算出した前記距離が短い順に、前記供給可能な数のフリップフロップセル以外のフリップフロップセルを選択し、

選択した前記フリップフロップセルを、検出した前記領域内のバッファセルに対応付けた対応情報を生成し、

前記第2レイアウトデータと、生成した前記対応情報と、を関連付けて出力する、

処理を実行させることを特徴とする設計支援プログラム。 - コンピュータに、

回路内の所定領域を一定間隔で区切った複数の領域を示す領域情報を生成し、

生成した前記領域情報が示す前記複数の領域の各々に少なくとも1つ設けられる、他のセルにクロック信号を供給可能なバッファセルの配置を示す第1レイアウトデータを生成し、

生成した前記第1レイアウトデータに基づいて、前記バッファセルの配置と、前記所定領域内に設けられるフリップフロップセルの配置と、を示す第2レイアウトデータを生成し、

前記第2レイアウトデータに基づいて、前記複数の領域の各々の領域について、前記領域内のフリップフロップセルの数が、前記領域内のバッファセルが前記クロック信号を供給可能な数よりも多いか少ないかを判断し、

前記領域内のフリップフロップセルの数が前記供給可能な数よりも少ないと判断した前記領域のうち、前記供給可能な数よりも多いと判断した前記領域に隣接する領域を検出し、

検出した前記領域の各々について、検出した前記領域内のバッファセルと、前記供給可能な数よりも多いと判断した前記領域内のフリップフロップセルの各々と、の距離を算出し、

検出した前記領域内のバッファセルと、前記供給可能な数よりも多いと判断した前記領域内のフリップフロップセルと、の組み合わせの中から、同一のフリップフロップセルを含む組み合わせを複数選択せず、算出した前記距離が短い順に、前記供給可能な数よりも多いと判断した前記領域内のフリップフロップセルの数と、前記供給可能な数と、の差分の組み合わせを選択し、

選択した前記組み合わせに含まれるフリップフロップセルと、選択した前記組み合わせに含まれるバッファセルと、を対応付けた対応情報を生成し、

前記第2レイアウトデータと、生成した前記対応情報と、を関連付けて出力する、

処理を実行させることを特徴とする設計支援プログラム。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013062350A JP6136430B2 (ja) | 2013-03-25 | 2013-03-25 | 設計支援装置、設計支援方法、および設計支援プログラム |

| US14/156,501 US20140289691A1 (en) | 2013-03-25 | 2014-01-16 | Circuit design support apparatus, circuit design support method, and computer product |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013062350A JP6136430B2 (ja) | 2013-03-25 | 2013-03-25 | 設計支援装置、設計支援方法、および設計支援プログラム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2014186648A JP2014186648A (ja) | 2014-10-02 |

| JP6136430B2 true JP6136430B2 (ja) | 2017-05-31 |

Family

ID=51570116

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013062350A Active JP6136430B2 (ja) | 2013-03-25 | 2013-03-25 | 設計支援装置、設計支援方法、および設計支援プログラム |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US20140289691A1 (ja) |

| JP (1) | JP6136430B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN106960087B (zh) * | 2017-03-13 | 2020-05-19 | 上海华力微电子有限公司 | 一种时钟分布网络结构及其生成方法 |

| US10868524B2 (en) | 2018-12-13 | 2020-12-15 | Samsung Electronics Co., Ltd. | Semiconductor circuit and semiconductor circuit layout system |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3104678B2 (ja) * | 1998-05-20 | 2000-10-30 | 日本電気株式会社 | クロック信号分配設計回路及びその方法並びにその制御プログラムを記録した記録媒体 |

| JP3231728B2 (ja) * | 1999-02-24 | 2001-11-26 | エヌイーシーマイクロシステム株式会社 | 半導体集積回路のクロック分配レイアウト方法 |

| JP4218924B2 (ja) * | 2001-02-15 | 2009-02-04 | 株式会社日立製作所 | 半導体集積回路の設計システム |

| US6686785B2 (en) * | 2001-10-11 | 2004-02-03 | Sun Microsystems, Inc. | Deskewing global clock skew using localized DLLs |

| JP2004022864A (ja) * | 2002-06-18 | 2004-01-22 | Fujitsu Ltd | ツリー構造型回路生成方法およびツリー構造型回路生成プログラム |

| JP2005012045A (ja) * | 2003-06-20 | 2005-01-13 | Matsushita Electric Ind Co Ltd | 半導体集積回路のレイアウト方法及び半導体集積回路 |

| US20080209038A1 (en) * | 2007-02-23 | 2008-08-28 | Raza Microelectronics, Inc. | Methods and systems for optimizing placement on a clock signal distribution network |

| JP4966838B2 (ja) * | 2007-12-14 | 2012-07-04 | エヌイーシーコンピュータテクノ株式会社 | クロック配線処理装置、クロック配線処理方法、及びプログラム |

| JP5326471B2 (ja) * | 2008-09-30 | 2013-10-30 | 富士通株式会社 | クロック信号供給回路の設計方法、情報処理装置およびプログラム |

-

2013

- 2013-03-25 JP JP2013062350A patent/JP6136430B2/ja active Active

-

2014

- 2014-01-16 US US14/156,501 patent/US20140289691A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| US20140289691A1 (en) | 2014-09-25 |

| JP2014186648A (ja) | 2014-10-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN104573169B (zh) | 以自动流水线操作能力设计集成电路的方法和工具 | |

| US8607182B2 (en) | Method of fast analog layout migration | |

| Dolgov et al. | 2019 cad contest: Lef/def based global routing | |

| JP2008165750A (ja) | 回路設計支援装置、回路設計支援方法、回路設計支援プログラムおよびプリント基板の製造方法 | |

| JP2008165748A (ja) | 回路設計支援装置、回路設計支援方法、回路設計支援プログラムおよびプリント基板の製造方法 | |

| US8701059B2 (en) | Method and system for repartitioning a hierarchical circuit design | |

| JP2008165747A (ja) | 回路設計支援装置、回路設計支援方法、回路設計支援プログラムおよびプリント基板の製造方法 | |

| JP2007122589A (ja) | ミックスドシグナル回路シミュレータ | |

| JP2008250630A (ja) | デカップリングセル配置方法及びデカップリングセル配置装置 | |

| JP6136430B2 (ja) | 設計支援装置、設計支援方法、および設計支援プログラム | |

| CN1305127C (zh) | 用去耦合电容实现集成电路供电网络噪声优化的快速方法 | |

| JP5359655B2 (ja) | 生成方法 | |

| JP6024828B2 (ja) | 消費電力値が所定電力値以下である状態情報を、測定した処理性能値に基づいて選択する選択装置 | |

| JP2006085635A (ja) | タイミング解析装置、タイミング解析方法、タイミング解析プログラムおよび記録媒体 | |

| US10460063B1 (en) | Integrated circuit routing based on enhanced topology | |

| JP2005309624A (ja) | レイアウト設計装置、レイアウト設計方法、レイアウト設計プログラム、および記録媒体 | |

| JP4825905B2 (ja) | レイアウト設計装置、レイアウト設計プログラム、および記録媒体 | |

| JP2008186230A (ja) | 集積回路設計装置、集積回路設計方法及び集積回路設計プログラム | |

| JP4587754B2 (ja) | クロック合成方法、半導体装置及びプログラム | |

| Yu et al. | Multi-voltage and level-shifter assignment driven floorplanning | |

| US10929589B1 (en) | Generating routing structure for clock network based on edge intersection detection | |

| JPWO2010140216A1 (ja) | 設計支援方法、設計支援装置、設計支援プログラム、および半導体集積回路 | |

| Wang et al. | Post-floorplanning power optimization for MSV-driven application specific NoC design | |

| JP6428207B2 (ja) | 設計方法、設計装置及びプログラム | |

| JP2011107769A (ja) | 半導体集積回路のレイアウト装置及びクロックゲーティング方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20151106 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20160906 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160920 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161121 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170404 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170417 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6136430 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |