JP6126600B2 - 回路装置および信号を送信するための方法 - Google Patents

回路装置および信号を送信するための方法 Download PDFInfo

- Publication number

- JP6126600B2 JP6126600B2 JP2014525315A JP2014525315A JP6126600B2 JP 6126600 B2 JP6126600 B2 JP 6126600B2 JP 2014525315 A JP2014525315 A JP 2014525315A JP 2014525315 A JP2014525315 A JP 2014525315A JP 6126600 B2 JP6126600 B2 JP 6126600B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- signal

- clock

- differential

- downstream

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/0008—Synchronisation information channels, e.g. clock distribution lines

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/04—Speed or phase control by synchronisation signals

- H04L7/10—Arrangements for initial synchronisation

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/40—Bus structure

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B1/00—Details of transmission systems, not covered by a single one of groups H04B3/00 - H04B13/00; Details of transmission systems not characterised by the medium used for transmission

- H04B1/02—Transmitters

- H04B1/04—Circuits

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- General Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Dc Digital Transmission (AREA)

- Synchronisation In Digital Transmission Systems (AREA)

- Optical Communication System (AREA)

- Logic Circuits (AREA)

Description

論理レベルに基づく信号に対応するシングルエンド高速(High Speed:HS)データと、

特に、コモンモード信号に基づく信号に対応する差動低電力(Low Power:LP)データと、

がシリアル化されて、共通信号ストリームを形成する。

(発明を具体化するための最良の方法)

本発明による送信装置Sに関する図1Aに示す実施形態によって、および

本発明による受信装置Eに関する図2Aに示す実施形態によって、

ケーブルベースのリンクを実現するおよび作動させるための、本発明による回路装置A(図1A、図2Aを参照)が得られ(本発明に関しては、互いに無関係に、送信装置Sと受信装置Eを実現すること、作動させることが可能である)、

そのリンクは、光学的に、具体的には、少なくとも1つの光学媒体に基づいて、例えば、光導波路OM(図1A、図2Aの詳細図を参照)に基づいて、例えば、少なくとも1つのガラス繊維に基づいて、および/または少なくとも1つのプラスチック繊維に基づいて多重化され、およびシリアル化され、および/または

そのリンクは、電気的にまたはガルバニックに、具体的には、少なくとも1つの電気的またはガルバニックなリンクに基づいて、例えば、少なくとも1つの銅線に基づいて、および/または例えば、少なくともプリント回路基板上に配列された少なくとも1つの電気的ラインに基づいて多重化されていない

ことが可能である。

受信側Eで同期を実施するのに用いられる、最初の4ビット長の同期/スタートシーケンスと、

その後の、LPデータごとの3ビットと、

に分けられている。

S 送信装置

AE 受信装置Eの出力部

AP アプリケーションプロセッサ

AS 送信装置Sの出力部

AT 出力ドライバ、具体的には、レーザドライバ

CD クロックおよびデータリカバリユニット

CE 受信インタフェースロジックLEのクロックモジュール

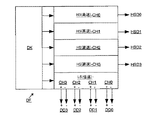

CH0± 第1のデータラインまたは第1のチャネル

CH1± 第2のデータラインまたは第2のチャネル

CH2± 第3のデータラインまたは第3のチャネル

CH3± 第4のデータラインまたは第4のチャネル

CLK± クロックラインまたはクロックチャネル

CS 送信インタフェースロジックLSのクロックモジュール

DD0± 第1のデータラインまたは第1のチャネルCH0±上の差動信号、具体的には、コモンモードベースのデータ信号

DD1± 第2のデータラインまたは第2のチャネルCH1±上の差動信号、具体的には、コモンモードベースのデータ信号

DD2± 第3のデータラインまたは第3のチャネルCH2±上の差動信号、具体的には、コモンモードベースのデータ信号

DD3± 第4のデータラインまたは第4のチャネルCH3±上の差動信号、具体的には、コモンモードベースのデータ信号

DF デフレーマ

DK デフレーマDFの復号器、具体的には、6b/5b復号器ブロック

DM デマルチプレクサ

DS デシリアライゼーション要素またはデシリアライザ

DU ディスプレイユニット

EE 受信装置Eの入力部

ES 送信装置Sの入力部

EV 入力増幅器、具体的には、トランスインピーダンス増幅器

FD フォトダイオード

FI フィルタ、具体的には、データフィルタ、例えば、LPデータフィルタ

FR フレーマ

HS 高速

HSD0 第1のデータラインまたは第1のチャネルCH0±上のシングルエンド論理レベルベースのデータ信号

HSD1 第2のデータラインまたは第2のチャネルCH1±上のシングルエンド論理レベルベースのデータ信号

HSD2 第3のデータラインまたは第3のチャネルCH2±上のシングルエンド論理レベルベースのデータ信号

HSD3 第4のデータラインまたは第4のチャネルCH3±上のシングルエンド論理レベルベースのデータ信号

IE データシンク関連のCSIおよび/またはCSI−2および/またはCSI−3および/またはDSIおよび/またはDSI−2インタフェース

IS データソース関連のCSIおよび/またはCSI−2および/またはCSI−3および/またはDSIおよび/またはDSI−2インタフェース

KA カメラ

KO フレーマFRの符号器、具体的には、5b/6b符号器ブロック

LA レーザ

LE 受信インタフェースロジック

LP 低電力

LS 送信インタフェースロジック

MU マルチプレクサ

MUZ マルチプレクサMUにおけるさらなるまたは追加的なマルチプレクサ

OM 光学媒体、具体的には、光導波路、例えば、ガラス繊維および/またはプラスチック繊維

PS クロック発振器、具体的には、位相ロックループ、例えば、クロックマルチプライヤユニット

SE シリアライゼーション要素またはシリアライザ

SI 共通信号ストリーム

TL クロックライン

Claims (17)

- シングルエンド論理レベルベースのデータ信号およびクロック信号(HS)と、

差動データ信号および差動クロック信号(LP)との両方を、

少なくとも1つのシリアル化された共通信号ストリーム(SI)の形態で、少なくとも1つのデータソースに割り当て可能な少なくとも1つの送信装置(S)と、少なくとも1つのデータシンクに割り当て可能な少なくとも1つの受信装置(E)との間で伝送するための回路装置(S,E)であって、前記差動データ信号および差動クロック信号(LP)のデータ転送速度は、前記シングルエンド論理レベルベースのデータ信号およびクロック信号(HS)のデータ転送速度よりも遅いことを特徴とする回路装置。 - 前記差動データ信号はコモンモードベースである請求項1に記載の回路装置。

- 前記送信装置(S)は、

前記データ信号およびクロック信号(HS;LP)のための少なくとも1つの入力部(ES)と、

入力部(ES)の下流の、前記データ信号およびクロック信号(HS;LP)を受け取るための少なくとも1つの送信インタフェースロジック(LS)と、

送信インタフェースロジック(LS)の下流の、前記共通信号ストリーム(SI)を生成するための少なくとも1つのシリアライザ(SE)と、

シリアライザ(SE)の上流で、送信インタフェースロジック(LS)の少なくとも1つのクロックモジュール(CS)の下流に設けられた、少なくとも1つの基準クロックを生成するための少なくとも1つのクロック発振器(PS)と、

シリアライザ(SE)の下流の少なくとも1つの出力ドライバ(AT)と、

出力ドライバ(AT)の下流の、前記共通信号ストリーム(SI)を前記受信装置(E)へ送信するための少なくとも1つの出力部(AS)と、

を備えることを特徴とする請求項1または2に記載の回路装置。 - 前記クロック発振器(PS)は、少なくとも位相ロックループとして構成されることを特徴とする請求項3に記載の回路装置。

- 前記クロック発振器(PS)は、少なくとも1つのクロックマルチプライヤユニットとして構成されることを特徴とする請求項4に記載の回路装置。

- 前記シリアライザ(SE)は、

前記送信インタフェースロジック(LS)の下流の、前記共通信号ストリーム(SI)のための、前記受信装置(E)で認識可能な少なくとも1つのフレームを生成するための少なくとも1つのフレーマ(FR)と、

前記フレーマ(FR)の下流の、前記共通信号ストリーム(SI)を生成するための少なくとも1つのマルチプレクサ(MU)と、

を備えることを特徴とする請求項3〜5のいずれか一項に記載の回路装置。 - 前記シングルエンド論理レベルベースのデータ信号(HSD0,HSD1,HSD2,HSD3)と前記差動データ信号(DD0+,DD0−,DD1+,DD1−,DD2+,DD2−,DD3+,DD3−)との両方を、前記フレーマ(FR)に印加することができること、および、前記フレーマは、少なくとも1つの符号器(KO)を用いて、前記差動データ信号(DD0+,DD0−,DD1+,DD1−,DD2+,DD2−,DD3+,DD3−)を、前記シングルエンド論理レベルベースのデータ信号(HSD0,HSD1,HSD2,HSD3)のストリームに埋め込むことを特徴とする請求項4又は5に記載の回路装置。

- 前記少なくとも1つの符号器は、少なくとも1つの5b/6b符号器ブロックである請求項7に記載の回路装置。

- 前記マルチプレクサ(MU)は、

前記差動データ信号および/または差動クロック信号(LP)と、前記シングルエンド論理レベルベースのデータ信号および/またはクロック信号(HS)を識別するための少なくとも1つのフィルタ(FI)と、

前記フィルタ(FI)から来る前記差動データ信号および/または差動クロック信号(LP)を追加的に印加することのできる少なくとも1つの追加的なマルチプレクサ(MUZ)と、

を備えることを特徴とする請求項6〜8のいずれか一項に記載の回路装置。 - 前記受信装置(E)は、

前記送信装置(S)によって送信された前記共通信号ストリーム(SI)のための少なくとも1つの入力部(EE)と、

前記共通信号ストリーム(SI)を受け取るための少なくとも1つの入力増幅器(EV)と、

前記データ信号およびクロック信号(HS,LP)を前記共通信号ストリーム(SI)から復元するための少なくとも1つのクロックおよびデータリカバリユニット(CD)と、

前記クロックおよびデータリカバリユニット(CD)の下流の、少なくとも1つの受信インタフェースロジック(LE)の少なくとも1つのクロックモジュール(CE)と、

前記クロックおよびデータリカバリユニット(CD)の下流の、前記データおよび/またはクロック信号(HS,LP)を再並列化するための、および再並列化された前記データおよび/またはクロック信号(HS,LP)を受信インタフェースロジック(LE)に割り当てるための少なくとも1つのデシリアライザ(DS)と、

前記受信インタフェースロジック(LE)の下流の、前記データ信号およびクロック信号(HS,LP)のための少なくとも1つの出力部(AE)と、

を備えることを特徴とする請求項1〜9のいずれか一項に記載の回路装置。 - 前記デシリアライザ(DS)は、

前記クロックおよびデータリカバリユニット(CD)の下流の、前記データおよび/またはクロック信号(HS,LP)を再並列化するための少なくとも1つのデマルチプレクサ(DM)と、

前記デマルチプレクサ(DM)の下流の、再並列化された前記データおよび/またはクロック信号(HS,LP)を、前記受信インタフェースロジック(LE)に割り当てるための少なくとも1つのデフレーマ(DF)と、

を備えることを特徴とする請求項10に記載の回路装置。 - 前記デフレーマ(DF)は、前記差動データ信号(DD0+,DD0−,DD1+,DD1−,DD2+,DD2−,DD3+,DD3−)を、少なくとも1つの復号器(DK)を用いて、前記シングルエンド論理レベルベースのデータ信号(HSD0,HSD1,HSD2,HSD3)と分けて、再並列化された前記データ信号を、それぞれのデータライン(CH0+,CH0−,CH1+,CH1−,CH2+,CH2−,CH3+,CH3−)に割り当てることを特徴とする請求項11に記載の回路装置。

- 前記少なくとも1つの復号器は、少なくとも1つの5b/6b復号器ブロックである請求項12に記載の回路装置。

- 前記共通信号ストリーム(SI)は、

少なくとも1つの光学媒体(OM)を介して、および/または

少なくとも1つの電気的またはガルバニックのリンク(GA)を介して、前記送信装置(S)と前記受信装置(E)との間で転送可能であることを特徴とする請求項1〜13のいずれか一項に記載の回路装置。 - シングルエンド論理レベルベースのデータ信号およびクロック信号(HS)と、

差動データ信号および差動クロック信号(LP)との両方を、

少なくとも1つのシリアル化された共通信号ストリーム(SI)の形態で、少なくとも1つのデータソースに割り当て可能な少なくとも1つの送信装置(S)と、少なくとも1つのデータシンクに割り当て可能な少なくとも1つの受信装置(E)との間で伝送するための方法であって、前記差動データ信号および差動クロック信号(LP)のデータ転送速度が、前記シングルエンド論理レベルベースのデータ信号およびクロック信号(HS)のデータ転送速度よりも遅いことを特徴とする方法。 - 前記差動データ信号はコモンモードベースである請求項15に記載の方法。

- 前記送信装置(S)と前記受信装置(E)との間の共通信号ストリーム(SI)は、

少なくとも1つの光学媒体(OM)を介して、および/または

少なくとも1つの電気的またはガルバニックのリンク(GA)を介して転送されることを特徴とする請求項15または16に記載の方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE102011052760.5 | 2011-08-16 | ||

| DE102011052760 | 2011-08-16 | ||

| PCT/DE2012/200051 WO2013023653A2 (de) | 2011-08-16 | 2012-08-16 | Schaltungsanordnung und verfahren zum uebertragen von signalen |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2014522204A JP2014522204A (ja) | 2014-08-28 |

| JP2014522204A5 JP2014522204A5 (ja) | 2015-10-08 |

| JP6126600B2 true JP6126600B2 (ja) | 2017-05-10 |

Family

ID=47556995

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014525315A Expired - Fee Related JP6126600B2 (ja) | 2011-08-16 | 2012-08-16 | 回路装置および信号を送信するための方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US9219598B2 (ja) |

| EP (1) | EP2745459B1 (ja) |

| JP (1) | JP6126600B2 (ja) |

| DE (1) | DE112012003372A5 (ja) |

| WO (1) | WO2013023653A2 (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI705666B (zh) * | 2015-06-15 | 2020-09-21 | 日商新力股份有限公司 | 傳送裝置、接收裝置、通信系統 |

| JP6763398B2 (ja) | 2015-12-11 | 2020-09-30 | ソニー株式会社 | 通信システムおよび通信方法 |

| JP6790435B2 (ja) | 2016-04-20 | 2020-11-25 | ソニー株式会社 | 受信装置、送信装置、および通信システム、ならびに、信号受信方法、信号送信方法、および通信方法 |

| JP2018164121A (ja) | 2017-03-24 | 2018-10-18 | ソニーセミコンダクタソリューションズ株式会社 | 通信装置および通信システム |

| US11108988B2 (en) | 2017-07-03 | 2021-08-31 | Sony Semiconductor Solutions Corporation | Transmitter and transmission method and receiver and reception method |

| US11509400B2 (en) | 2019-11-15 | 2022-11-22 | AuthenX Inc. | Image transmission system and image transmission method |

| US11927799B2 (en) | 2020-12-31 | 2024-03-12 | AuthenX Inc. | Data transmission system and data transmission method |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5968179A (en) | 1997-04-08 | 1999-10-19 | International Business Machines Corporation | Method for initializing a self-timed link |

| JP2001103028A (ja) * | 1999-10-01 | 2001-04-13 | Nippon Telegr & Teleph Corp <Ntt> | 信号多重方法 |

| US7496780B2 (en) * | 2003-02-11 | 2009-02-24 | Agere Systems Inc. | Reduction of data skew in parallel processing circuits |

| US7587537B1 (en) * | 2007-11-30 | 2009-09-08 | Altera Corporation | Serializer-deserializer circuits formed from input-output circuit registers |

| JP4633547B2 (ja) * | 2004-06-18 | 2011-02-16 | パナソニック株式会社 | 携帯情報端末機器およびその機器内相互通信方法 |

| JP5223183B2 (ja) * | 2006-10-31 | 2013-06-26 | 日立電線株式会社 | 光電気複合配線部品及びこれを用いた電子機器 |

| JP2008160370A (ja) * | 2006-12-22 | 2008-07-10 | Kddi Corp | データ伝送システム及び方法、データ送信装置並びにデータ受信装置 |

| JP4894917B2 (ja) * | 2007-04-05 | 2012-03-14 | オムロン株式会社 | 光伝送モジュール |

| PL2186242T3 (pl) * | 2007-09-10 | 2017-11-30 | Nokia Technologies Oy | Zmienianie ustawień sprzętowych na podstawie preambuły danych |

| JP4609552B2 (ja) * | 2008-08-22 | 2011-01-12 | オムロン株式会社 | 光伝送用並列直列変換器、光伝送システム、及び電子機器 |

| JP5187277B2 (ja) * | 2009-06-16 | 2013-04-24 | ソニー株式会社 | 情報処理装置、及びモード切り替え方法 |

-

2012

- 2012-08-16 JP JP2014525315A patent/JP6126600B2/ja not_active Expired - Fee Related

- 2012-08-16 EP EP12813747.8A patent/EP2745459B1/de active Active

- 2012-08-16 WO PCT/DE2012/200051 patent/WO2013023653A2/de active Application Filing

- 2012-08-16 DE DE112012003372.8T patent/DE112012003372A5/de not_active Withdrawn

-

2014

- 2014-02-14 US US14/181,414 patent/US9219598B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| WO2013023653A3 (de) | 2013-05-30 |

| WO2013023653A2 (de) | 2013-02-21 |

| JP2014522204A (ja) | 2014-08-28 |

| US20150043690A1 (en) | 2015-02-12 |

| EP2745459A2 (de) | 2014-06-25 |

| EP2745459B1 (de) | 2021-01-13 |

| DE112012003372A5 (de) | 2014-06-26 |

| US9219598B2 (en) | 2015-12-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6126600B2 (ja) | 回路装置および信号を送信するための方法 | |

| CA2450825C (en) | Protocol independent transmission using a 10 gigabit attachment unit interface | |

| US8873591B2 (en) | System and method for bit-multiplexed data streams over multirate gigabit Ethernet | |

| JP6126598B2 (ja) | 回路装置および信号を送信するための方法 | |

| EP2207315B1 (en) | Transmission of parallel data flows on a parallel bus | |

| US6915036B2 (en) | Field reconfigurable line cards for an optical transport system | |

| US20110123196A1 (en) | Method, device and system for sending and receiving client signals | |

| JP6126602B2 (ja) | 回路装置および信号を送信するための方法 | |

| JP6126601B2 (ja) | 回路装置および信号を送信するための方法 | |

| US20030219042A1 (en) | Time divison multiplexing and transport method, apparatus and system | |

| JP6126599B2 (ja) | 回路装置および信号を送信するための方法 | |

| JP2014524699A5 (ja) | ||

| JP6126604B2 (ja) | 送信装置および信号を送信するための方法 | |

| JP6126603B2 (ja) | 回路装置および信号を送信するための方法 | |

| KR20030061936A (ko) | 멀티미디어 다중 전송 시스템 | |

| KR100406490B1 (ko) | 라우터 시스템에서 버스구조에 대한 보드간의 인터페이스변환 장치 | |

| CN101707592B (zh) | Spi4接口数据包的处理方法 | |

| CN117749970A (zh) | 数据发送、接收装置、方法及芯片 | |

| WO2005011193A1 (en) | Device for implementing a rnc using lvds | |

| US20080225767A1 (en) | Device for Implementing a RNC Using LVDS | |

| JP2014529932A5 (ja) |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150817 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150817 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20160408 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160426 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20160726 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20160926 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161026 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20161206 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170228 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170314 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170407 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6126600 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |