JP6088521B2 - オンチップの中和キャパシタ及び線形作動を用いて自動キャリブレーションを行うことによる容量性変換器の線形性増大 - Google Patents

オンチップの中和キャパシタ及び線形作動を用いて自動キャリブレーションを行うことによる容量性変換器の線形性増大 Download PDFInfo

- Publication number

- JP6088521B2 JP6088521B2 JP2014530913A JP2014530913A JP6088521B2 JP 6088521 B2 JP6088521 B2 JP 6088521B2 JP 2014530913 A JP2014530913 A JP 2014530913A JP 2014530913 A JP2014530913 A JP 2014530913A JP 6088521 B2 JP6088521 B2 JP 6088521B2

- Authority

- JP

- Japan

- Prior art keywords

- phase

- automatic calibration

- calibration method

- proof mass

- neutralization capacity

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000006386 neutralization reaction Methods 0.000 title claims description 76

- 239000003990 capacitor Substances 0.000 title claims description 71

- 238000000034 method Methods 0.000 claims description 66

- 238000005259 measurement Methods 0.000 claims description 30

- 230000003247 decreasing effect Effects 0.000 claims description 7

- 230000003472 neutralizing effect Effects 0.000 claims description 6

- 238000007599 discharging Methods 0.000 claims description 4

- 230000003213 activating effect Effects 0.000 claims description 2

- 238000006073 displacement reaction Methods 0.000 description 24

- 238000010586 diagram Methods 0.000 description 23

- 230000001133 acceleration Effects 0.000 description 14

- 238000001514 detection method Methods 0.000 description 12

- 239000000758 substrate Substances 0.000 description 5

- 238000012886 linear function Methods 0.000 description 4

- 230000003071 parasitic effect Effects 0.000 description 4

- 230000008878 coupling Effects 0.000 description 2

- 238000010168 coupling process Methods 0.000 description 2

- 238000005859 coupling reaction Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000005484 gravity Effects 0.000 description 2

- 230000007935 neutral effect Effects 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 1

- 230000005284 excitation Effects 0.000 description 1

- 238000010998 test method Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01P—MEASURING LINEAR OR ANGULAR SPEED, ACCELERATION, DECELERATION, OR SHOCK; INDICATING PRESENCE, ABSENCE, OR DIRECTION, OF MOVEMENT

- G01P21/00—Testing or calibrating of apparatus or devices covered by the preceding groups

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01L—MEASURING FORCE, STRESS, TORQUE, WORK, MECHANICAL POWER, MECHANICAL EFFICIENCY, OR FLUID PRESSURE

- G01L25/00—Testing or calibrating of apparatus for measuring force, torque, work, mechanical power, or mechanical efficiency

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01L—MEASURING FORCE, STRESS, TORQUE, WORK, MECHANICAL POWER, MECHANICAL EFFICIENCY, OR FLUID PRESSURE

- G01L27/00—Testing or calibrating of apparatus for measuring fluid pressure

- G01L27/002—Calibrating, i.e. establishing true relation between transducer output value and value to be measured, zeroing, linearising or span error determination

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01D—MEASURING NOT SPECIALLY ADAPTED FOR A SPECIFIC VARIABLE; ARRANGEMENTS FOR MEASURING TWO OR MORE VARIABLES NOT COVERED IN A SINGLE OTHER SUBCLASS; TARIFF METERING APPARATUS; MEASURING OR TESTING NOT OTHERWISE PROVIDED FOR

- G01D18/00—Testing or calibrating apparatus or arrangements provided for in groups G01D1/00 - G01D15/00

- G01D18/002—Automatic recalibration

- G01D18/006—Intermittent recalibration

Description

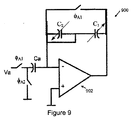

第1の容量性コアCAは、可変キャパシタC1A及びC2Aを含む。第2の容量性コアCBは、可変キャパシタC1B及びC2Bを含む。図3はまた、所望の検出キャパシタC1A、C2A、C1B、C2Bにそれぞれ並列な不要なフィードスルー容量Cft1、Cft2、Cft3、Cft4を示している。図4は、不要なフィードスルー容量を除去するために追加されたオンチップの中和キャパシタを備える図3の差動回路の一例を示す図である。中和キャパシタCn1、Cn2、Cn3、Cn4はそれぞれ、不要なフィードスルー容量Cft1、Cft2、Cft3、Cft4を除去するように追加される。

Claims (14)

- 中和容量のための初期値からスタートしてフィードスルー容量を中和するために容量性変換器を自動キャリブレーションする方法であって、

前記方法は、

静電力を前記容量性変換器のプルーフマスへ供給しないステップと、

静電力が前記プルーフマスに供給されていない間に前記容量性変換器の基本出力値を記録するステップと、

静電力F0を前記容量性変換器の前記プルーフマスに供給するステップと、

前記静電力F0が前記プルーフマスに供給されているときに、前記基本出力値と第1の出力値との間における前記容量性変換器の前記出力値の第1の変化を記録するステップと、

静電力n×F0を前記容量性変換器の前記プルーフマスに供給するステップであって、n>1である、ステップと、

前記静電力n×F0が前記プルーフマスに供給されているときに、前記第1の出力値と第2の出力値との間における前記容量性変換器の前記出力値の第2の変化を記録するステップと、

前記容量性変換器の前記出力値における前記記録された第1の変化及び第2の変化に基づいて、前記中和容量を増加する、減少する、又は維持するステップと、

前記中和容量のための最終値に到達するまで前記方法を繰り返すステップと、

を備える、自動キャリブレーション方法。 - 請求項1の自動キャリブレーション方法において、

前記増加する、減少する、又は維持するステップは、

前記出力値における前記第1の変化が前記出力値における前記第2の変化より大きい場合には前記中和容量を減少するステップと、

前記出力値における前記第1の変化が前記出力値における前記第2の変化より小さい場合には前記中和容量を増加するステップと、を含む

自動キャリブレーション方法。 - 請求項2の自動キャリブレーション方法において、

前記中和容量は、最小中和容量と最大中和容量との間で設定され、

前記増加する、減少する、又は維持するステップ、及び、前記繰り返しステップは、前記最小中和容量と前記最大中和容量との間で2分探索を実行するステップを含む、

自動キャリブレーション方法。 - 請求項3の自動キャリブレーション方法において、さらに、

前記中和容量のための前記最終値の線形性と線形性閾値とを比較するステップを含む、

自動キャリブレーション方法。 - 請求項3の自動キャリブレーション方法において、

前記静電力は、充電制御方法を用いて前記プルーフマスに供給される、

自動キャリブレーション方法。 - 請求項5の自動キャリブレーション方法において、

前記静電力F0を前記プルーフマスに供給するステップは、期間tの間前記プルーフマスを作動するステップを含み、

前記静電力n×F0を前記プルーフマスに供給するステップは、期間n×tの間前記プルーフマスを作動するステップを含む、

自動キャリブレーション方法。 - 請求項6の自動キャリブレーション方法において、

前記容量性変換器は、第1及び第2の可変キャパシタを含み、

前記静電力を供給するステップは、

前記第1及び第2の可変キャパシタから放電することによる第1の作動フェーズの間に、前記容量性変換器をリセットするステップと、

第2の作動フェーズの間に静電作動力を前記容量性変換器へ供給するステップであって、前記静電作動力は前記第2の作動フェーズの期間の機能であり、前記第2の作動フェーズは前記第1の作動フェーズに続くフェーズである、ステップと、

第1の測定フェーズの間に前記静電作動力に起因する前記容量性変換器の出力信号を読み出すステップであって、前記第1の測定フェーズは前記第2の作動フェーズに続くフェーズである、ステップと、

第2の測定フェーズの間に前記静電作動力を前記第1及び第2の可変キャパシタに供給しないステップであって、前記第2の測定フェーズは前記第1の測定フェーズに続き、前記第1の作動フェーズに先立つフェーズである、ステップと、を備える、

自動キャリブレーション方法。 - 請求項1の自動キャリブレーション方法において、

第1の中和容量が最初に最小中和容量に設定され、前記第1の中和容量より高い第2の中和容量が最初に最大中和容量に設定され、前記中和容量の初期値は前記最小中和容量と前記最大中和容量との平均であり、

前記増加する、減少する、又は維持するステップは、

前記出力値における前記第1の変化が前記出力値における前記第2の変化より大きい場合には、前記第2の中和容量を前記中和容量の現在値へ設定し、

前記出力値における前記第1の変化が前記出力値における前記第2の変化より小さい場合には、前記第1の中和容量を前記中和容量の現在値へ設定し、

前記出力値における前記第1の変化が前記出力値における前記第2の変化と等しい場合には、前記第1の中和容量と前記第2の中和容量とを維持し、

前記中和容量を前記第2の中和容量と前記第1の中和容量との平均に設定する、

自動キャリブレーション方法。 - 請求項8の自動キャリブレーション方法において、

前記方法をN回に至るまで繰り返し、

前記出力値における前記第1の変化と前記出力値における前記第2の変化とが等しくなった場合に、前記方法の繰り返しを停止する、

自動キャリブレーション方法。 - 請求項9の自動キャリブレーション方法において、

前記中和容量のための前記最終値の線形性と線形性閾値とを比較するステップを含む、

自動キャリブレーション方法。 - 請求項1の自動キャリブレーション方法において、

前記静電力は、充電制御方法を用いて前記プルーフマスに供給される、

自動キャリブレーション方法。 - 請求項11の自動キャリブレーション方法において、

静電力F0を前記プルーフマスに供給するステップは、期間tの間前記プルーフマスを作動させるステップを含み、

静電力n×F0を前記プルーフマスに供給するステップは、期間n×tの間前記プルーフマスを作動するステップを含む、

自動キャリブレーション方法。 - 請求項12の自動キャリブレーション方法において、

前記容量性変換器は、第1及び第2の可変キャパシタを含み、

前記静電力を供給するステップは、

前記第1及び第2の可変キャパシタから放電することによる第1の作動フェーズの間に、前記容量性変換器をリセットするステップと、

第2の作動フェーズの間に静電作動力を前記容量性変換器へ供給するステップであって、前記静電作動力は前記第2の作動フェーズの期間の機能であり、前記第2の作動フェーズは前記第1の作動フェーズに続くフェーズである、ステップと、

第1の測定フェーズの間に前記静電作動力に起因する前記容量性変換器の出力信号を読み出すステップであって、前記第1の測定フェーズは前記第2の作動フェーズに続くフェーズである、ステップと、

第2の測定フェーズの間に静電作動力を前記第1及び第2の可変キャパシタに供給しないステップであって、前記第2の測定フェーズは前記第1の測定フェーズに続き、前記第1の作動フェーズに先立つフェーズである、ステップと、を備える、

自動キャリブレーション方法。 - 請求項13の自動キャリブレーション方法において、

前記容量性変換器の前記第2の可変キャパシタは前記第2の作動フェーズの間ショートされる回路である、

自動キャリブレーション方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US13/235,334 | 2011-09-16 | ||

| US13/235,334 US9032777B2 (en) | 2011-09-16 | 2011-09-16 | Linearity enhancement of capacitive transducers by auto-calibration using on-chip neutralization capacitors and linear actuation |

| PCT/US2012/055645 WO2013040508A1 (en) | 2011-09-16 | 2012-09-14 | Linearity enhancement of capacitive transducers by auto-calibration using on-chip neutralization capacitors and linear actuation |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2014526701A JP2014526701A (ja) | 2014-10-06 |

| JP2014526701A5 JP2014526701A5 (ja) | 2015-11-05 |

| JP6088521B2 true JP6088521B2 (ja) | 2017-03-01 |

Family

ID=47016831

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014530913A Active JP6088521B2 (ja) | 2011-09-16 | 2012-09-14 | オンチップの中和キャパシタ及び線形作動を用いて自動キャリブレーションを行うことによる容量性変換器の線形性増大 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US9032777B2 (ja) |

| EP (1) | EP2756317B1 (ja) |

| JP (1) | JP6088521B2 (ja) |

| CN (1) | CN103890593B (ja) |

| WO (1) | WO2013040508A1 (ja) |

Families Citing this family (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9285207B2 (en) * | 2013-03-13 | 2016-03-15 | Invensense, Inc. | Linear capacitive displacement sensor |

| US9939290B1 (en) * | 2013-09-16 | 2018-04-10 | Panasonic Corporation | Method for calibration of a system with time-multiplexed sensors |

| US9435821B1 (en) | 2013-12-12 | 2016-09-06 | The United States Of America As Represented By The Administrator Of The National Aeronautics And Space Administration | Single-axis accelerometer |

| JP2015125088A (ja) * | 2013-12-27 | 2015-07-06 | 株式会社村田製作所 | 容量トリミング回路 |

| US10260983B2 (en) * | 2014-01-20 | 2019-04-16 | Lear Corporation | Apparatus and method for diagnostics of a capacitive sensor with plausibility check |

| GB201410038D0 (en) | 2014-06-06 | 2014-07-16 | Atlantic Inertial Systems Ltd | Accelerometers |

| JP6555869B2 (ja) * | 2014-10-17 | 2019-08-07 | キヤノン株式会社 | 静電容量型トランスデューサ |

| CN105259372B (zh) * | 2015-10-14 | 2018-07-10 | 华东光电集成器件研究所 | 晶圆级电容式加速度计自动测试系统 |

| CN105486450B (zh) * | 2015-12-10 | 2018-01-12 | 中国航空工业集团公司北京长城计量测试技术研究所 | 一种宽量程脉冲力校准装置 |

| US10198133B2 (en) | 2016-03-28 | 2019-02-05 | Synaptics Incorporated | Inflection based calibration method for force detector |

| EP3340021A4 (en) | 2016-10-31 | 2018-10-10 | Shenzhen Goodix Technology Co., Ltd. | Capacitance detection device and method, and pressure detection system |

| CN108008152B (zh) * | 2017-11-28 | 2020-04-03 | 中国电子产品可靠性与环境试验研究所 | 获取mems加速度计的寄生失配电容的方法及装置 |

| CN108195507A (zh) * | 2017-12-16 | 2018-06-22 | 芜湖致通汽车电子有限公司 | 用于传感器自动化批量检测系统 |

| JP2021071382A (ja) * | 2019-10-31 | 2021-05-06 | セイコーエプソン株式会社 | 物理量センサー、電子機器及び移動体 |

| US11268975B2 (en) * | 2019-12-19 | 2022-03-08 | Invensense, Inc. | Accelerometer sensitivity self-calibration with duty cycle control of drive signal |

| CN112125275B (zh) * | 2020-11-26 | 2021-04-06 | 南京高华科技股份有限公司 | 一种mems电容式传感器及其制备方法 |

| CN113203939B (zh) * | 2021-04-26 | 2022-03-18 | 中国科学院地质与地球物理研究所 | 一种mems加速度传感器芯片的检测方法及装置 |

| CN114414848B (zh) * | 2021-12-01 | 2022-10-25 | 西安电子科技大学 | 基于对称驱动的mems电容型传感器的馈通电容提取方法 |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5211051A (en) * | 1987-11-09 | 1993-05-18 | California Institute Of Technology | Methods and apparatus for improving sensor performance |

| JPH0623781B2 (ja) * | 1988-10-20 | 1994-03-30 | 株式会社日立製作所 | 加速度検出方法及び装置 |

| FR2700614B1 (fr) * | 1993-01-19 | 1995-04-14 | Sextant Avionique | Accéléromètre capacitif à circuit de correction de l'effet perturbateur de capacités parasites. |

| US5347867A (en) | 1993-02-03 | 1994-09-20 | Minnetonka Warehouse Supply, Inc | Accelerometer incorporating a driven shield |

| US6109114A (en) * | 1993-08-16 | 2000-08-29 | California Institute Of Technology | Caging, calibration, characterization and compensation of microstructural transducers |

| USD357807S (en) * | 1993-09-14 | 1995-05-02 | Kathy Meyer | Video tape fireproof storage box |

| US5770802A (en) | 1997-04-16 | 1998-06-23 | Texas Instruments Incorporated | Sensor with improved capacitive to voltage converter integrated circuit |

| US6718605B2 (en) | 1997-09-08 | 2004-04-13 | The Regents Of The University Of Michigan | Single-side microelectromechanical capacitive accelerometer and method of making same |

| JP2000074939A (ja) * | 1998-08-28 | 2000-03-14 | Denso Corp | 容量式加速度センサ |

| US6035694A (en) * | 1999-03-12 | 2000-03-14 | I/O Of Austin, Inc. | Method and apparatus for calibration of stray capacitance mismatch in a closed loop electro-mechanical accelerometer |

| US7712366B2 (en) * | 2004-06-09 | 2010-05-11 | Eth Zuerich | Multi-axis capacitive transducer and manufacturing method for producing it |

| US7121141B2 (en) * | 2005-01-28 | 2006-10-17 | Freescale Semiconductor, Inc. | Z-axis accelerometer with at least two gap sizes and travel stops disposed outside an active capacitor area |

| JP4719272B2 (ja) * | 2005-11-22 | 2011-07-06 | キオニクス,インコーポレイテッド | 三軸加速度計 |

| JP4931713B2 (ja) * | 2006-08-08 | 2012-05-16 | セイコーインスツル株式会社 | 力学量センサ |

| US8056415B2 (en) * | 2008-05-30 | 2011-11-15 | Freescale Semiconductor, Inc. | Semiconductor device with reduced sensitivity to package stress |

| US8220330B2 (en) * | 2009-03-24 | 2012-07-17 | Freescale Semiconductor, Inc. | Vertically integrated MEMS sensor device with multi-stimulus sensing |

| DE102009026496B4 (de) | 2009-05-27 | 2022-04-28 | Robert Bosch Gmbh | Kompensationskapazität für einen kapazitiven Sensor |

| JP5649810B2 (ja) * | 2009-10-29 | 2015-01-07 | 日立オートモティブシステムズ株式会社 | 静電容量式センサ |

| US8816703B2 (en) * | 2011-09-01 | 2014-08-26 | Robert Bosch Gmbh | Linear capacitance-to-voltage converter using a single amplifier for accelerometer front ends with cancellation of spurious forces contributed by sensor circuitry |

-

2011

- 2011-09-16 US US13/235,334 patent/US9032777B2/en active Active

-

2012

- 2012-07-17 US US13/551,408 patent/US9116166B2/en active Active

- 2012-09-14 CN CN201280050876.6A patent/CN103890593B/zh active Active

- 2012-09-14 WO PCT/US2012/055645 patent/WO2013040508A1/en active Application Filing

- 2012-09-14 JP JP2014530913A patent/JP6088521B2/ja active Active

- 2012-09-14 EP EP12772167.8A patent/EP2756317B1/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20130152663A1 (en) | 2013-06-20 |

| US9116166B2 (en) | 2015-08-25 |

| CN103890593B (zh) | 2016-10-26 |

| EP2756317A1 (en) | 2014-07-23 |

| EP2756317B1 (en) | 2015-09-09 |

| CN103890593A (zh) | 2014-06-25 |

| US20130067984A1 (en) | 2013-03-21 |

| US9032777B2 (en) | 2015-05-19 |

| WO2013040508A1 (en) | 2013-03-21 |

| JP2014526701A (ja) | 2014-10-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6088521B2 (ja) | オンチップの中和キャパシタ及び線形作動を用いて自動キャリブレーションを行うことによる容量性変換器の線形性増大 | |

| JP4178658B2 (ja) | 容量式物理量検出装置 | |

| JP6038152B2 (ja) | 物理量を検出する容量性変換器システム | |

| US7795881B2 (en) | Capacitive physical quantity detection device | |

| US7287429B2 (en) | Capacitive acceleration sensor system | |

| US8310248B2 (en) | Capacitive sensor device | |

| CN107231596B (zh) | 电容性传感器测试 | |

| JP2009097932A (ja) | 容量型検出装置 | |

| JP4508480B2 (ja) | 静電容量型センサのセンサ特性測定装置 | |

| JP2011107086A (ja) | 静電容量検出回路、圧力検出装置、加速度検出装置、および、マイクロフォン用トランスデューサ | |

| KR20170015891A (ko) | 가속도계 | |

| EP3404422B1 (en) | System including a capacitive transducer and an excitation circuit for such a transducer and a method for measuring acceleration with such a system | |

| JP6371984B2 (ja) | 容量式物理量検出装置 | |

| US7728603B2 (en) | Test method for a variable capacitance measuring system | |

| US10564176B2 (en) | Capacitive accelerometer | |

| JP5441027B2 (ja) | 静電容量型加速度センサの検査方法及びその検査装置 | |

| Depari et al. | Simple and robust microcontroller-based acquisition system for differential capacitive sensors | |

| JP4150292B2 (ja) | 異常検出機能を持つ静電容量式センサ装置 | |

| JP2012181143A (ja) | 容量検出装置、抵抗検出装置 | |

| Joshi et al. | Characterization of capacitive comb-finger MEMS accelerometers | |

| RU2244271C1 (ru) | Способ контроля качества изготовления микромеханических устройств | |

| JP2011247847A (ja) | 変位検出装置、及び、前置増幅器 | |

| RU2488785C1 (ru) | Способ измерения амплитудно-частотных характеристик подвижных элементов микромеханических устройств | |

| JP2019215189A (ja) | 容量式物理量検出装置 | |

| JP2008026177A (ja) | 容量型検出回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150911 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150911 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20160610 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160617 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160913 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170106 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170203 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6088521 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |