JP5761551B2 - 送信装置、送信方法、受信装置、受信方法、プログラム、および伝送システム - Google Patents

送信装置、送信方法、受信装置、受信方法、プログラム、および伝送システム Download PDFInfo

- Publication number

- JP5761551B2 JP5761551B2 JP2010258570A JP2010258570A JP5761551B2 JP 5761551 B2 JP5761551 B2 JP 5761551B2 JP 2010258570 A JP2010258570 A JP 2010258570A JP 2010258570 A JP2010258570 A JP 2010258570A JP 5761551 B2 JP5761551 B2 JP 5761551B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- unit

- transmission

- error correction

- bits

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/004—Arrangements for detecting or preventing errors in the information received by using forward error control

- H04L1/0056—Systems characterized by the type of code used

- H04L1/0057—Block codes

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/02—Details ; arrangements for supplying electrical power along data transmission lines

- H04L25/14—Channel dividing arrangements, i.e. in which a single bit stream is divided between several baseband channels and reassembled at the receiver

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L2001/0092—Error control systems characterised by the topology of the transmission link

- H04L2001/0096—Channel splitting in point-to-point links

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Power Engineering (AREA)

- Detection And Prevention Of Errors In Transmission (AREA)

- Error Detection And Correction (AREA)

Description

図1は、本発明の一実施形態に係る伝送システムの構成例を示す図である。

はじめに、送信側ブロック11の構成について説明する。送信側ブロック11は、信号処理部21、並べ替え処理部22、ECC処理部23、分割部24、および送信処理部25−1乃至25−4から構成される。

次に、受信側ブロック12の構成について説明する。受信側ブロック12は、受信処理部51−1乃至51−4、結合部52、ECC処理部53、並べ替え処理部54、および信号処理部55から構成される。

ここで、送信側ブロック11と受信側ブロック12の一連の処理について説明する。はじめに、図9のフローチャートを参照して送信側ブロック11の送信処理について説明する。

上述した一連の処理は、ハードウェアにより実行することもできるし、ソフトウェアにより実行することもできる。一連の処理をソフトウェアにより実行する場合には、そのソフトウェアを構成するプログラムが、専用のハードウェアに組み込まれているコンピュータ、または汎用のパーソナルコンピュータなどに、プログラム記録媒体からインストールされる。

Claims (8)

- 送信対象のデータである複数のシンボルを構成するビットを、所定の前記シンボルを構成するビット列の先頭から順に同じ単位に集めるようにして足りない場合に、次の前記シンボルを構成するビット列の先頭から集め、その次の前記単位は、それに続くビットから集めるように、先頭のビットから順に同じ前記単位毎に集め、前記単位のデータを出力する変換部と、

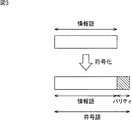

複数の前記単位のデータを情報語として誤り訂正符号を計算する誤り訂正符号計算部と、

前記誤り訂正符号計算部による計算によって求められた前記誤り訂正符号を前記情報語に付加して得られた符号語を、同じビット数の符号化データに分割し、前記符号化データを所定の数ずつ複数の伝送路に割り当て、他の前記伝送路より前記符号化データの割り当て数の少ない前記伝送路に対して、他の前記伝送路に割り当てた前記符号化データの量と同じ量のデータが割り当てられるように、前記符号化データと同じビット数の、所定の値を有するパディングデータを割り当てる分割部と、

前記分割部により割り当てられたデータをペイロードに格納し、ヘッダとフッタを付加したパケットを、前記パケット毎に開始コードと終了コードを付加して同じ装置内の受信装置に対して前記伝送路を介して送信する、複数の前記伝送路に対応して設けられる複数の送信部と

を備える送信装置。 - 前記分割部は、前記誤り訂正符号計算部から供給された順に、同じ前記符号語を構成する前記符号化データを異なる前記伝送路に割り当てる

請求項1に記載の送信装置。 - 送信対象のデータである複数のシンボルを構成するビットを、所定の前記シンボルを構成するビット列の先頭から順に同じ単位に集めるようにして足りない場合に、次の前記シンボルを構成するビット列の先頭から集め、その次の前記単位は、それに続くビットから集めるように、先頭のビットから順に同じ前記単位毎に集め、前記単位のデータを変換部から出力し、

複数の前記単位のデータを情報語として誤り訂正符号を誤り訂正符号計算部により計算し、

前記誤り訂正符号計算部による計算によって求められた前記誤り訂正符号を前記情報語に付加して得られた符号語を、同じビット数の符号化データに分割し、前記符号化データを所定の数ずつ分割部により複数の伝送路に割り当て、

他の前記伝送路より前記符号化データの割り当て数の少ない前記伝送路に対して、他の前記伝送路に割り当てた前記符号化データの量と同じ量のデータが割り当てられるように、前記符号化データと同じビット数の、所定の値を有するパディングデータを前記分割部により割り当て、

複数の前記伝送路に対応して設けられる複数の送信部により、前記分割部により割り当てられたデータをペイロードに格納し、ヘッダとフッタを付加したパケットを、前記パケット毎に開始コードと終了コードを付加して同じ装置内の受信装置に対して前記伝送路を介して送信する

ステップを含む送信方法。 - 送信対象のデータである複数のシンボルを構成するビットを、所定の前記シンボルを構成するビット列の先頭から順に同じ単位に集めるようにして足りない場合に、次の前記シンボルを構成するビット列の先頭から集め、その次の前記単位は、それに続くビットから集めるように、先頭のビットから順に同じ前記単位毎に集め、前記単位のデータを変換部から出力し、

複数の前記単位のデータを情報語として誤り訂正符号を誤り訂正符号計算部により計算し、

前記誤り訂正符号計算部による計算によって求められた前記誤り訂正符号を前記情報語に付加して得られた符号語を、同じビット数の符号化データに分割し、前記符号化データを所定の数ずつ分割部により複数の伝送路に割り当て、

他の前記伝送路より前記符号化データの割り当て数の少ない前記伝送路に対して、他の前記伝送路に割り当てた前記符号化データの量と同じ量のデータが割り当てられるように、前記符号化データと同じビット数の、所定の値を有するパディングデータを前記分割部により割り当て、

複数の前記伝送路に対応して設けられる複数の送信部により、前記分割部により割り当てられたデータをペイロードに格納し、ヘッダとフッタを付加したパケットを、前記パケット毎に開始コードと終了コードを付加して同じ装置内の受信装置に対して前記伝送路を介して送信する

ステップを含む処理をコンピュータに実行させるプログラム。 - 送信対象のデータである複数のシンボルを構成するビットを、所定の前記シンボルを構成するビット列の先頭から順に同じ単位に集めるようにして足りない場合に、次の前記シンボルを構成するビット列の先頭から集め、その次の前記単位は、それに続くビットから集めるように、先頭のビットから順に同じ前記単位毎に集め、複数の前記単位のデータを情報語として誤り訂正符号を計算し、計算によって求めた前記誤り訂正符号を前記情報語に付加して得られた符号語を、同じビット数の符号化データに分割し、前記符号化データを所定の数ずつ複数の伝送路に割り当て、他の前記伝送路より前記符号化データの割り当て数の少ない前記伝送路に対して、他の前記伝送路に割り当てた前記符号化データの量と同じ量のデータが割り当てられるように、前記符号化データと同じビット数の、所定の値を有するパディングデータを割り当て、複数の前記伝送路に割り当てられたデータをペイロードに格納し、ヘッダとフッタを付加したパケットを、前記パケット毎に開始コードと終了コードを付加して前記伝送路を介して送信する同じ装置内の送信装置から送信されたデータを受信し、前記開始コードから前記終了コードまでのデータを前記パケットのデータとして、前記ペイロードに格納されたデータを出力する、複数の前記伝送路に対応して設けられる複数の受信部と、

複数の前記受信部から出力されたデータのうち、前記パディングデータを除去し、前記符号化データに基づいて前記符号語を生成する結合部と、

前記結合部により生成された前記符号語に含まれる前記誤り訂正符号に基づいて前記情報語の誤り訂正を行う誤り訂正部と、

誤り訂正後の前記情報語を構成する、先頭のビットから順に並ぶ前記シンボルのビット数と同じビットを、前記シンボルのデータとして出力する変換部と

を備える受信装置。 - 送信対象のデータである複数のシンボルを構成するビットを、所定の前記シンボルを構成するビット列の先頭から順に同じ単位に集めるようにして足りない場合に、次の前記シンボルを構成するビット列の先頭から集め、その次の前記単位は、それに続くビットから集めるように、先頭のビットから順に同じ前記単位毎に集め、複数の前記単位のデータを情報語として誤り訂正符号を計算し、計算によって求めた前記誤り訂正符号を前記情報語に付加して得られた符号語を、同じビット数の符号化データに分割し、前記符号化データを所定の数ずつ複数の伝送路に割り当て、他の前記伝送路より前記符号化データの割り当て数の少ない前記伝送路に対して、他の前記伝送路に割り当てた前記符号化データの量と同じ量のデータが割り当てられるように、前記符号化データと同じビット数の、所定の値を有するパディングデータを割り当て、複数の前記伝送路に割り当てられたデータをペイロードに格納し、ヘッダとフッタを付加したパケットを、前記パケット毎に開始コードと終了コードを付加して前記伝送路を介して送信する同じ装置内の送信装置から送信されたデータを、複数の前記伝送路に対応して設けられる複数の受信部により受信し、前記開始コードから前記終了コードまでのデータを前記パケットのデータとして、前記ペイロードに格納されたデータを出力し、

複数の前記受信部から出力されたデータのうち、前記パディングデータを除去し、前記符号化データに基づいて前記符号語を結合部により生成し、

前記結合部により生成された前記符号語に含まれる前記誤り訂正符号に基づいて前記情報語の誤り訂正を誤り訂正部により行い、

誤り訂正後の前記情報語を構成する、先頭のビットから順に並ぶ前記シンボルのビット数と同じビットを、前記シンボルのデータとして変換部から出力する

ステップを含む受信方法。 - 送信対象のデータである複数のシンボルを構成するビットを、所定の前記シンボルを構成するビット列の先頭から順に同じ単位に集めるようにして足りない場合に、次の前記シンボルを構成するビット列の先頭から集め、その次の前記単位は、それに続くビットから集めるように、先頭のビットから順に同じ前記単位毎に集め、複数の前記単位のデータを情報語として誤り訂正符号を計算し、計算によって求めた前記誤り訂正符号を前記情報語に付加して得られた符号語を、同じビット数の符号化データに分割し、前記符号化データを所定の数ずつ複数の伝送路に割り当て、他の前記伝送路より前記符号化データの割り当て数の少ない前記伝送路に対して、他の前記伝送路に割り当てた前記符号化データの量と同じ量のデータが割り当てられるように、前記符号化データと同じビット数の、所定の値を有するパディングデータを割り当て、複数の前記伝送路に割り当てられたデータをペイロードに格納し、ヘッダとフッタを付加したパケットを、前記パケット毎に開始コードと終了コードを付加して前記伝送路を介して送信する同じ装置内の送信装置から送信されたデータを、複数の前記伝送路に対応して設けられる複数の受信部により受信し、前記開始コードから前記終了コードまでのデータを前記パケットのデータとして、前記ペイロードに格納されたデータを出力し、

複数の前記受信部から出力されたデータのうち、前記パディングデータを除去し、前記符号化データに基づいて前記符号語を結合部により生成し、

前記結合部により生成された前記符号語に含まれる前記誤り訂正符号に基づいて前記情報語の誤り訂正を誤り訂正部により行い、

誤り訂正後の前記情報語を構成する、先頭のビットから順に並ぶ前記シンボルのビット数と同じビットを、前記シンボルのデータとして変換部から出力する

ステップを含む処理をコンピュータに実行させるプログラム。 - 送信装置と受信装置からなる伝送システムにおいて、

前記送信装置は、

送信対象のデータである複数のシンボルを構成するビットを、所定の前記シンボルを構成するビット列の先頭から順に同じ単位に集めるようにして足りない場合に、次の前記シンボルを構成するビット列の先頭から集め、その次の前記単位は、それに続くビットから集めるように、先頭のビットから順に同じ前記単位毎に集め、前記単位のデータを出力する変換部と、

複数の前記単位のデータを情報語として誤り訂正符号を計算する誤り訂正符号計算部と、

前記誤り訂正符号計算部による計算によって求められた前記誤り訂正符号を前記情報語に付加して得られた符号語を、同じビット数の符号化データに分割し、前記符号化データを所定の数ずつ複数の伝送路に割り当て、他の前記伝送路より前記符号化データの割り当て数の少ない前記伝送路に対して、他の前記伝送路に割り当てた前記符号化データの量と同じ量のデータが割り当てられるように、前記符号化データと同じビット数の、所定の値を有するパディングデータを割り当てる分割部と、

前記分割部により割り当てられたデータをペイロードに格納し、ヘッダとフッタを付加したパケットを、前記パケット毎に開始コードと終了コードを付加して同じ装置内の前記受信装置に対して前記伝送路を介して送信する、複数の前記伝送路に対応して設けられる複数の送信部と

を備え、

前記受信装置は、

前記送信装置から送信されたデータを受信し、前記開始コードから前記終了コードまでのデータを前記パケットのデータとして、前記ペイロードに格納されたデータを出力する、複数の前記伝送路に対応して設けられる複数の受信部と、

複数の前記受信部から出力されたデータのうち、前記パディングデータを除去し、前記符号化データに基づいて符号語を生成する結合部と、

前記結合部により生成された前記符号語に含まれる前記誤り訂正符号に基づいて前記情報語の誤り訂正を行う誤り訂正部と、

誤り訂正後の前記情報語を構成する、先頭のビットから順に並ぶ前記シンボルのビット数と同じビットを、前記シンボルのデータとして出力する変換部と

を備える

伝送システム。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010258570A JP5761551B2 (ja) | 2010-11-19 | 2010-11-19 | 送信装置、送信方法、受信装置、受信方法、プログラム、および伝送システム |

| US13/253,464 US8583985B2 (en) | 2010-11-19 | 2011-10-05 | Transmission apparatus, transmission method, reception apparatus, reception method, program and transmission system |

| EP11187641.3A EP2456112B1 (en) | 2010-11-19 | 2011-11-03 | Error correction methods and apparatus |

| EP18195190.6A EP3451564B1 (en) | 2010-11-19 | 2011-11-03 | Error correction methods and apparatus |

| CN201110361134.2A CN102480340B (zh) | 2010-11-19 | 2011-11-15 | 发送设备、发送方法、接收设备、接收方法和传输系统 |

| CN2011204516069U CN202737883U (zh) | 2010-11-19 | 2011-11-15 | 发送设备、接收设备和传输系统 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010258570A JP5761551B2 (ja) | 2010-11-19 | 2010-11-19 | 送信装置、送信方法、受信装置、受信方法、プログラム、および伝送システム |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2012109890A JP2012109890A (ja) | 2012-06-07 |

| JP2012109890A5 JP2012109890A5 (ja) | 2013-12-19 |

| JP5761551B2 true JP5761551B2 (ja) | 2015-08-12 |

Family

ID=44992611

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010258570A Expired - Fee Related JP5761551B2 (ja) | 2010-11-19 | 2010-11-19 | 送信装置、送信方法、受信装置、受信方法、プログラム、および伝送システム |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US8583985B2 (ja) |

| EP (2) | EP2456112B1 (ja) |

| JP (1) | JP5761551B2 (ja) |

| CN (2) | CN102480340B (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5761551B2 (ja) * | 2010-11-19 | 2015-08-12 | ソニー株式会社 | 送信装置、送信方法、受信装置、受信方法、プログラム、および伝送システム |

| JP5583851B2 (ja) * | 2011-07-04 | 2014-09-03 | 日本電信電話株式会社 | 伝送システム及び伝送方法 |

| JP2013187606A (ja) | 2012-03-06 | 2013-09-19 | Sony Corp | 撮像装置および画像伝送方法 |

| JP2020167634A (ja) * | 2019-03-29 | 2020-10-08 | ソニーセミコンダクタソリューションズ株式会社 | 送信装置、受信装置、及び伝送システム |

| JP2024098810A (ja) * | 2023-01-11 | 2024-07-24 | 国立研究開発法人情報通信研究機構 | 通信ネットワークの制御装置 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3311878A (en) * | 1963-02-14 | 1967-03-28 | Ibm | Error checking system for binary parallel communications |

| JPH05304515A (ja) * | 1992-04-24 | 1993-11-16 | Rohm Co Ltd | デジタルデータ伝送方式 |

| JP3577717B2 (ja) * | 2001-05-18 | 2004-10-13 | 日本電気株式会社 | 通信装置、スクランブラ回路とデスクランブラ回路、そのスクランブル方法とデスクランブル方法 |

| JP3663151B2 (ja) * | 2001-06-07 | 2005-06-22 | 日本電信電話株式会社 | データ転送方法、データ転送システム、および受信装置 |

| JP3877576B2 (ja) * | 2001-11-07 | 2007-02-07 | 沖電気工業株式会社 | 並列送信装置及び並列伝送システム |

| JP2004088246A (ja) * | 2002-08-23 | 2004-03-18 | Toyota Industries Corp | 無線通信方法および無線通信装置 |

| US7978734B2 (en) * | 2004-03-18 | 2011-07-12 | Xocyst Transfer Ag L.L.C. | Multichannel MAC data stream for wireless communication |

| WO2006062552A1 (en) * | 2004-12-06 | 2006-06-15 | Thomson Licensing | Multiple flows for incremental forward error corection mechanisms |

| JP2008200344A (ja) * | 2007-02-21 | 2008-09-04 | Hoya Corp | 電子内視鏡および内視鏡プロセッサ |

| JP4774391B2 (ja) * | 2007-08-24 | 2011-09-14 | 株式会社日立製作所 | 光伝送システムおよび信号速度変換装置 |

| WO2009147735A1 (ja) * | 2008-06-04 | 2009-12-10 | 富士通株式会社 | 情報処理装置、データ送信装置およびデータ送信装置のデータ転送方法 |

| JP5388671B2 (ja) | 2009-04-22 | 2014-01-15 | キヤノン株式会社 | 撮像装置及び画像変換方法 |

| JP5761551B2 (ja) * | 2010-11-19 | 2015-08-12 | ソニー株式会社 | 送信装置、送信方法、受信装置、受信方法、プログラム、および伝送システム |

-

2010

- 2010-11-19 JP JP2010258570A patent/JP5761551B2/ja not_active Expired - Fee Related

-

2011

- 2011-10-05 US US13/253,464 patent/US8583985B2/en active Active

- 2011-11-03 EP EP11187641.3A patent/EP2456112B1/en active Active

- 2011-11-03 EP EP18195190.6A patent/EP3451564B1/en active Active

- 2011-11-15 CN CN201110361134.2A patent/CN102480340B/zh not_active Expired - Fee Related

- 2011-11-15 CN CN2011204516069U patent/CN202737883U/zh not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| EP2456112A2 (en) | 2012-05-23 |

| EP3451564B1 (en) | 2022-03-23 |

| US20120131412A1 (en) | 2012-05-24 |

| EP3451564A1 (en) | 2019-03-06 |

| CN102480340A (zh) | 2012-05-30 |

| CN102480340B (zh) | 2017-09-01 |

| EP2456112B1 (en) | 2019-01-02 |

| EP2456112A3 (en) | 2015-03-04 |

| US8583985B2 (en) | 2013-11-12 |

| JP2012109890A (ja) | 2012-06-07 |

| CN202737883U (zh) | 2013-02-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| TWI686085B (zh) | 攝像裝置及圖像感測器之資料傳送方法、資訊處理裝置及資訊處理方法以及程式 | |

| JP5233165B2 (ja) | データ伝送装置 | |

| EP1921754B1 (en) | Error correcting method and apparatus | |

| US8103942B2 (en) | Data transmission apparatus, data transmission device, data reception device and data transmission system | |

| JP5761551B2 (ja) | 送信装置、送信方法、受信装置、受信方法、プログラム、および伝送システム | |

| CN1323505C (zh) | 传输线路编码方法、传输线路解码方法及其设备 | |

| CN110769206B (zh) | 一种电子内窥镜信号传输方法、装置和系统及电子设备 | |

| WO1998058468A1 (fr) | Systeme de transmission avec multiplexage de donnees d'information, multiplexeur et demultiplexeur utilises a cet effet et codeur et decodeur pour correction d'erreurs | |

| CN1386017A (zh) | 用于处理辅助传输数据的残留边带传输系统 | |

| US20120131422A1 (en) | Transmitting device, transmitting method, receiving device, receiving method, program, and transmission system | |

| CN102469272A (zh) | 图像输出装置、图像处理装置及其方法和图像拾取装置 | |

| US20100262887A1 (en) | High Integrity Data Network System and Method | |

| KR20110066084A (ko) | 정보 객체의 인코딩을 위한 방법 및 이를 이용한 인코더 | |

| JP2009524335A (ja) | 非圧縮avデータを送受信する装置および方法 | |

| CN106571893B (zh) | 一种语音数据的编解码方法 | |

| US8812938B2 (en) | Coding apparatus, coding method, decoding apparatus, decoding method, program and transmission system | |

| KR101367216B1 (ko) | 디지털 방송 수신기 및 그 스트림 처리 방법 | |

| JP2011003975A (ja) | 誤り訂正符号化装置および誤り訂正復号装置 | |

| JP2017050734A (ja) | シリアル通信装置、通信システム及び通信方法 | |

| KR100740226B1 (ko) | 듀얼 전송 스트림 생성 장치 및 그 방법 | |

| JP5968577B2 (ja) | 通信装置、通信システムおよび誤り訂正フレーム生成方法 | |

| US8619895B2 (en) | Apparatus and method for transmitting/receiving broadcast data in digital broadcasting system | |

| US20220166598A1 (en) | Transmission apparatus, reception apparatus, and transmission system | |

| JP2004532459A (ja) | Ic間のリンク上の順方向誤り訂正(fec) | |

| CN117240401A (zh) | 编码传输方法、解码方法和通信装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131106 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20131106 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140704 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140708 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140822 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150217 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150417 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20150514 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20150527 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5761551 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |