JP5684076B2 - アナログデジタル変換器及び無線受信機 - Google Patents

アナログデジタル変換器及び無線受信機 Download PDFInfo

- Publication number

- JP5684076B2 JP5684076B2 JP2011193965A JP2011193965A JP5684076B2 JP 5684076 B2 JP5684076 B2 JP 5684076B2 JP 2011193965 A JP2011193965 A JP 2011193965A JP 2011193965 A JP2011193965 A JP 2011193965A JP 5684076 B2 JP5684076 B2 JP 5684076B2

- Authority

- JP

- Japan

- Prior art keywords

- analog

- digital

- digital converter

- sampling

- output

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/06—Continuously compensating for, or preventing, undesired influence of physical parameters

- H03M1/08—Continuously compensating for, or preventing, undesired influence of physical parameters of noise

- H03M1/0836—Continuously compensating for, or preventing, undesired influence of physical parameters of noise of phase error, e.g. jitter

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/12—Analogue/digital converters

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/12—Analogue/digital converters

- H03M1/1205—Multiplexed conversion systems

- H03M1/121—Interleaved, i.e. using multiple converters or converter parts for one channel

- H03M1/1215—Interleaved, i.e. using multiple converters or converter parts for one channel using time-division multiplexing

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Analogue/Digital Conversion (AREA)

- Stabilization Of Oscillater, Synchronisation, Frequency Synthesizers (AREA)

Description

(1) 基準クロックを源振とし、前記基準クロックより高周波数であり、かつ、前記基準クロックと同期したサンプリングクロックを生成する位相同期ループ

(2) 前記入力アナログ電圧を前記サンプリングクロックを用いてサンプリングし、デジタル値に変換するアナログデジタル変換部

(3) 前記基準クロックの電圧遷移タイミングに対する前記サンプリングクロックの時間遷移タイミングの時間差を検出し、前記時間差を差分デジタル値に変換する時間デジタル変換器

(4) 前記差分デジタル値を補間して各サンプリングタイミングに対応する補間値を求め、前記補間値により前記アナログデジタル変換部の生デジタル出力に含まれる前記サンプリングクロックのジッタの影響をデジタル補正するデジタル補正部

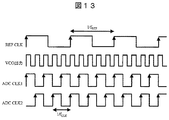

図2に、第一の実施例に係るアナログデジタル変換器の構成例を示す。本実施例の場合、アナログデジタル変換器で使用するサンプリングクロック(ADC CLK)は、基準クロック(REF CLK)を源振とする位相同期ループ(PLL)20において生成する。

V(nT+Δt)=V(nT)+Δt*dV/dt(nT)

このように、アナログデジタル変換部25の生デジタル出力には、理想的なタイミングでサンプリングされる電圧V(nT)に対し、Δt*dV/dt(nT)で表されるサンプリング電圧誤差が含くまれる。

以上説明したように、本実施例においては、サンプリングクロック(ADC CLK)を、より低速の基準クロック(REF CLK)を源振とする位相同期ループ20において生成する。このため、サンプリングクロック(ADC CLK)が超高速化する場合でも、低消費電力のまま、ジッタの影響をデジタル補正できるアナログデジタル変換器を実現することができる。すなわち、1GS/s以上の超高速で、10bit以上の高分解能を両立するアナログデジタル変換器を実現できる。

図8に、第二の実施例に係るアナログデジタル変換器の構成例を示す。本実施例は、実施例1の位相同期ループ20を後述する回路構成に置換している点を除き、実施例1と同一の回路構成を有するアナログデジタル変換器について説明する。具体的には、位相同期ループ20を、デューティ調整部(Duty)81と、その出力に接続されたバンドパスフィルタ(BPF)82と、その出力に接続されたバッファ83で構成される回路で置換する場合について説明する。従って、アナログデジタル変換部(ADC)25、デジタル補正部、時間デジタル変換器26、補間器27の構成や動作は、実施例1と同様である。

図10に、第三の実施例に係るアナログデジタル変換器の構成例を示す。本実施例でも、実施例1の位相同期ループ20を後述する回路構成に置換している点を除き、実施例1と同一の回路構成を有するアナログデジタル変換器について説明する。具体的には、位相同期ループ20を、デューティ調整部(Duty)81と、その出力に接続された注入同期型(Injection locking)発振器101と、その出力に接続されたバッファ83で構成される回路で置換する場合について説明する。従って、アナログデジタル変換部(ADC)25、デジタル補正部、時間デジタル変換器26、補間器27の構成や動作は、実施例1と同様である。

図12に、第四の実施例に係るアナログデジタル変換器の構成例を示す。本実施例は、タイムインターリーブ型のアナログデジタル変換器について説明する。タイムインターリーブ型のアナログデジタル変換器は、非特許文献3及び4などに記載されているように、複数(例えば、L個)の同一構成のアナログデジタル変換部により入力信号をアナログデジタル変換する。

V(nT+Δt1)=V(nT)+Δt1*dV/dt(nT)

V(nT+T/2+Δt2)=V(nT+T/2)+Δt2*dV/dt(nT+T/2)

このように、第二のアナログデジタル変換部127の生デジタル出力には、理想的なタイミングでサンプリングされる電圧V(nT+T/2)に対し、Δt2*dV/dt(nT+T/2)で表されるサンプリング電圧誤差が含まれる。

以上説明したように、タイムインターリーブ型アナログデジタル変換器を構成することにより、変換器全体としてのサンプリングクロックが超高速化する場合でも、低消費電力のまま、ジッタの影響をデジタル補正できるアナログデジタル変換器を実現することができる。

図14に、第五の実施例に係るアナログデジタル変換器の構成例を示す。本実施例も、タイムインターリーブ型アナログデジタル変換器について説明する。ただし、本実施例に係るアナログデジタル変換器は、各アナログデジタル変換部におけるサンプリングタイミングのスキューをデジタル補正するための機構を有する点において第四の実施例と異なっている。

以上説明したように、本実施例によれば、サンプリングクロックが超高速化する場合でも、低消費電力のまま、スキューとジッタの影響をデジタル補正できるアナログデジタル変換器を実現することができる。

図15に、第六の実施例を示す。本実施例は、実施例1で説明したアナログデジタル変換器を、一般の無線送受信機に適用した場合の例である。

以上説明したように、本実施例によれば、超高速のサンプリングクロックで動作するアナログデジタル変換器の無線送受信機への実装が実現される。しかも、本実施例で使用するアナログデジタル変換器は低消費電力である。このため、携帯型の無線送受信機に特に効果的である。

図16に、第七の実施例を示す。本実施例は、実施例1で説明したアナログデジタル変換器を、マイコンチップに適用した場合の例である。

以上説明したように、本実施例によれば、超高速のサンプリングクロックで動作するアナログデジタル変換器のマイコンチップへの実装が実現される。しかも、本実施例で使用するアナログデジタル変換器は低消費電力である。このため、携帯機器に搭載されるマイコンチップに特に効果的である。

図17に、各実施例で使用する時間デジタル変換器(TDC)の回路実装例を示す。すなわち、時間デジタル変換器26(図2、図8、図10、図15、図16)や時間デジタル変換器122、128(図12、図14)に用いて好適な回路実装例を示す。

以上から、チャージポンプ172の出力電圧VCは、次式となる。

11:位相同期ループ

12:分周器

13:アナログデジタル変換部

14:時間デジタル変換器

15:デジタル補正部

20:位相同期ループ

21:位相比較器

22:ループフィルタ

23:電圧制御発振器

24:分周器

25:アナログデジタル変換部

26:TDC(時間デジタル変換器)

27:補間器

28:微分器

29:乗算器

210:減算器

61〜65:遅延器

66〜611:定数倍器

612:加算器

71:遅延器

72:加算器

81:デューティ調整部

82:バンドパスフィルタ

83:バッファ

101:注入同期型発振器

120:1/2分周器

121、127:アナログデジタル変換部

122、128:TDC

123、129:補間器

124、1210:微分器

125、1211:乗算器

126、1212:減算器

141:参照アナログデジタル変換部

142:スキュー探索部

143、144:加算器

150:分周器

151:アンテナ

152:スイッチ

153:フロントエンドモジュール

154:低雑音増幅器

155:受信ミキサ

156:アナログフロントエンド部

157:デジタルベースバンド部

158:デジタルアナログ変換器

159:フィルタ

1510:送信ミキサ

1511:パワーアンプ

161:MPU(マイクロプロセッシングユニット)

162:RAM(ランダムアクセスメモリ)

163:ROM(リードオンリーメモリ)

171:位相周波数比較器

171A、171B:Dフリップフロップ

171C:遅延AND(アンド)ゲート

171D:反転(インバータ)ゲート

172:チャージポンプ

172A:PMOSスイッチ

172B:NMOSスイッチ

172C:PMOS電流源

172D:NMOS電流源

173:容量素子

174:リセットスイッチ

175:電圧源

176:抵抗ラダー

177:コンパレータ列

178:温度計コードTOバイナリコード変換部

179:クロック生成部

Claims (15)

- 入力アナログ電圧をサンプリングしてデジタル値に変換するアナログデジタル変換器において、

基準クロックを源振とし、前記基準クロックより高周波数であり、かつ、前記基準クロックと同期したサンプリングクロックを生成する位相同期ループと、

前記入力アナログ電圧を前記サンプリングクロックを用いてサンプリングし、デジタル値に変換するアナログデジタル変換部と、

前記基準クロックの電圧遷移タイミングに対する前記サンプリングクロックの時間遷移タイミングの時間差を検出し、前記時間差を差分デジタル値に変換する時間デジタル変換器と、

前記差分デジタル値を補間して各サンプリングタイミングに対応する補間値を求め、前記補間値により前記アナログデジタル変換部の生デジタル出力に含まれる前記サンプリングクロックのジッタの影響をデジタル補正するデジタル補正部と

を有することを特徴とするアナログデジタル変換器。 - 請求項1に記載のアナログデジタル変換器において、

前記デジタル補正部は、前記アナログデジタル変換部の生デジタル出力の微分値を求め、前記微分値と前記補間値に基づいて前記生デジタル出力をデジタル補正する

ことを特徴とするアナログデジタル変換器。 - 入力アナログ電圧をサンプリングしてデジタル値に変換するアナログデジタル変換器において、

それぞれが、対応する第1のサンプリングクロックを用いて前記入力アナログ電圧をサンプリングし、デジタル値に変換する複数のアナログデジタル変換部であって、複数の前記第1のサンプリングクロックは、周波数が互いに同一であり、かつ、位相が互いに異なる関係を有する、複数のアナログデジタル変換部と、

各アナログデジタル変換部に対応して設けられ、それぞれが、基準クロックの電圧遷移タイミングに対する前記第1のサンプリングクロックの時間遷移タイミングの時間差を検出し、前記時間差を差分デジタル値に変換する複数の時間デジタル変換器であり、前記第1のサンプリングクロックの周波数は、位相同期ループ用である前記基準クロックの周波数より低周波数である、複数の時間デジタル変換器と、

各アナログデジタル変換部に対応して設けられ、それぞれが、前記差分デジタル値を補間して各サンプリングタイミングに対応する補間値を求め、前記補間値により対応する前記アナログデジタル変換部の生デジタル出力に含まれる前記第1のサンプリングクロックのジッタの影響をデジタル補正する複数のデジタル補正部と

を有することを特徴とするアナログデジタル変換器。 - 請求項3に記載のアナログデジタル変換器において、

参照アナログデジタル変換器と

スキュー探索部とを有し、

前記参照アナログデジタル変換器は、各アナログデジタル変換部に対応する複数の第1のサンプリングクロックとサンプリングタイミングを順次同期できる周波数の第2のサンプリングクロックにより前記入力アナログ電圧をサンプリングして参照用デジタル値を生成し、

前記スキュー探索部は、前記参照用デジタル値を用いて、複数の前記第1のサンプリングクロックにそれぞれ含まれるサンプリングタイミングスキューを探索し、得られたサンプリングタイミングスキューをそれぞれ対応する前記デジタル補正部に与え、

前記複数のデジタル補正部は、それぞれが、対応する前記補間値と前記サンプリングタイミングスキューとに基づいて、対応する前記アナログデジタル変換部の生デジタル出力に含まれる前記第1のサンプリングクロックのジッタとスキューの影響をデジタル補正する

ことを特徴とするアナログデジタル変換器。 - 請求項3に記載のアナログデジタル変換器において、

複数の前記第1のサンプリングクロックは、前記第1のサンプリングクロックよりも低周波数である基準クロックを源振とする位相同期ループにより生成される前記基準クロックと同期した第3のサンプリングクロックを分周することにより生成する

ことを特徴とするアナログデジタル変換器。 - 請求項4に記載のアナログデジタル変換器において、

複数の前記第1のサンプリングクロックは、前記第1のサンプリングクロックよりも低周波数である基準クロックを源振とする位相同期ループにより生成される前記基準クロックと同期した第4のサンプリングクロックを分周することにより生成する

ことを特徴とするアナログデジタル変換器。 - 請求項3に記載のアナログデジタル変換器において、

複数の前記デジタル補正部のそれぞれは、対応する前記アナログデジタル変換部の生デジタル出力の微分値を求め、前記微分値と対応する前記補間値に基づいて前記生デジタル出力をデジタル補正する

ことを特徴とするアナログデジタル変換器。 - 請求項4に記載のアナログデジタル変換器において、

複数の前記デジタル補正部のそれぞれは、対応する前記アナログデジタル変換部の生デジタル出力の微分値を求め、前記微分値と対応する前記補間値に基づいて前記生デジタル出力をデジタル補正する

ことを特徴とするアナログデジタル変換器。 - 請求項5に記載のアナログデジタル変換器において、

複数の前記デジタル補正部のそれぞれは、対応する前記アナログデジタル変換部の生デジタル出力の微分値を求め、前記微分値と対応する前記補間値に基づいて前記生デジタル出力をデジタル補正する

ことを特徴とするアナログデジタル変換器。 - 請求項6に記載のアナログデジタル変換器において、

複数の前記デジタル補正部のそれぞれは、対応する前記アナログデジタル変換部の生デジタル出力の微分値を求め、前記微分値と対応する前記補間値に基づいて前記生デジタル出力をデジタル補正する

ことを特徴とするアナログデジタル変換器。 - 請求項3に記載のアナログデジタル変換器において、

前記基準クロック又はその分周出力に含まれる高調波をフィルタにより抽出し、さらに、抽出された前記高調波を分周することにより、複数の各アナログデジタル変換部に対応する前記第1のサンプリングクロックを生成する

ことを特徴とするアナログデジタル変換器。 - 請求項4に記載のアナログデジタル変換器において、

前記基準クロック又はその分周出力に含まれる高調波をフィルタにより抽出し、さらに、抽出された前記高調波を分周することにより、複数の各アナログデジタル変換部に対応する前記第1のサンプリングクロックを生成する

ことを特徴とするアナログデジタル変換器。 - 請求項3に記載のアナログデジタル変換器において、

前記基準クロック又はその分周出力を注入同期型発振器に注入し、前記注入同期型発振器の発振出力を分周し、得られた分周出力を用いて、複数の前記アナログデジタル変換部のそれぞれに対応する複数の前記第1のサンプリングクロックを生成する

ことを特徴とするアナログデジタル変換器。 - 請求項4に記載のアナログデジタル変換器において、

前記基準クロック又はその分周出力を注入同期型発振器に注入し、前記注入同期型発振器の発振出力を分周し、得られた分周出力を用いて、複数の前記アナログデジタル変換部のそれぞれに対応する複数の前記第1のサンプリングクロックを生成する

ことを特徴とするアナログデジタル変換器。 - 無線信号を受信する受信回路部であって、

基準クロックを源振とし、前記基準クロックより高周波数であり、かつ、前記基準クロックと同期したサンプリングクロックを生成する位相同期ループと、

前記入力アナログ電圧を前記サンプリングクロックを用いてサンプリングし、デジタル値に変換するアナログデジタル変換部と、

前記基準クロックの電圧遷移タイミングに対する前記サンプリングクロックの時間遷移タイミングの時間差を検出し、前記時間差を差分デジタル値に変換する時間デジタル変換器と、

前記差分デジタル値を補間して各サンプリングタイミングに対応する補間値を求め、前記補間値により前記アナログデジタル変換部の生デジタル出力に含まれる前記サンプリングクロックのジッタの影響をデジタル補正するデジタル補正部と

を有するアナログデジタル変換器を有する受信回路部と、

前記無線信号を周波数変換するための局部発振信号を生成する位相同期ループと

を有することを特徴とする無線受信機。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011193965A JP5684076B2 (ja) | 2011-09-06 | 2011-09-06 | アナログデジタル変換器及び無線受信機 |

| US13/570,228 US8933831B2 (en) | 2011-09-06 | 2012-08-08 | Analog-to-digital converter and wireless receiver |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011193965A JP5684076B2 (ja) | 2011-09-06 | 2011-09-06 | アナログデジタル変換器及び無線受信機 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2013055598A JP2013055598A (ja) | 2013-03-21 |

| JP5684076B2 true JP5684076B2 (ja) | 2015-03-11 |

Family

ID=47753175

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011193965A Expired - Fee Related JP5684076B2 (ja) | 2011-09-06 | 2011-09-06 | アナログデジタル変換器及び無線受信機 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8933831B2 (ja) |

| JP (1) | JP5684076B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20190143028A (ko) * | 2018-06-19 | 2019-12-30 | 세종대학교산학협력단 | 시간 디지털 변환 카운터 및 이를 포함하는 라이더 시스템 |

Families Citing this family (44)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8461886B1 (en) * | 2010-10-20 | 2013-06-11 | Marvell International Ltd. | Circuit and circuit method for reduction of PFD noise contribution for ADPLL |

| JP6192259B2 (ja) | 2011-04-21 | 2017-09-06 | 三星電子株式会社Samsung Electronics Co.,Ltd. | Dtvのアナログフロントエンド、それを含むデジタルtvシステム、及びこれらの動作方法 |

| US8669794B2 (en) * | 2012-02-21 | 2014-03-11 | Qualcomm Incorporated | Circuit for detecting a voltage change using a time-to-digital converter |

| US8922184B2 (en) * | 2012-03-22 | 2014-12-30 | Realtek Semiconductor Corp. | Integrated switch-capacitor DC-DC converter and method thereof |

| US8754797B2 (en) * | 2012-08-30 | 2014-06-17 | Texas Instruments Incorporated | Asynchronous analog-to-digital converter having rate control |

| US8830106B2 (en) * | 2012-08-30 | 2014-09-09 | Texas Instruments Incorporated | Asynchronous analog-to-digital converter having adapative reference control |

| US8878577B2 (en) * | 2012-09-05 | 2014-11-04 | IQ-Analog Corporation | System and method for frequency multiplier jitter correction |

| US9007105B2 (en) * | 2013-01-29 | 2015-04-14 | Perceptia Devices Australia Pty Ltd | Hitless switching phase-locked loop |

| JP6273931B2 (ja) * | 2014-03-14 | 2018-02-07 | シンフォニアテクノロジー株式会社 | 電力変換装置の信号変換装置 |

| KR101624507B1 (ko) | 2014-04-03 | 2016-05-26 | 한국과학기술원 | 클럭 신호 처리기, 수신기 및 송/수신 시스템 |

| KR101615435B1 (ko) * | 2014-06-09 | 2016-04-26 | 한국과학기술원 | 센서 저항을 이용한 온도 측정 장치 및 그 방법 |

| US9651646B2 (en) * | 2014-06-24 | 2017-05-16 | Tektronix, Inc. | Phase noise correction system for discrete time signal processing |

| US10009038B2 (en) * | 2014-09-03 | 2018-06-26 | University Of Southern California | Wideband Nyquist VCO-based analog-to-digital converter |

| US9231602B1 (en) * | 2014-09-18 | 2016-01-05 | Intel IP Corporation | A-priori-probability-phase-estimation for digital phase-locked loops |

| JP6416607B2 (ja) * | 2014-12-10 | 2018-10-31 | 日立オートモティブシステムズ株式会社 | 電子制御装置 |

| US9379880B1 (en) * | 2015-07-09 | 2016-06-28 | Xilinx, Inc. | Clock recovery circuit |

| JP6694728B2 (ja) * | 2016-02-18 | 2020-05-20 | 日本電波工業株式会社 | 信号処理装置 |

| US9588497B1 (en) * | 2016-07-27 | 2017-03-07 | Silicon Laboratories Inc. | Differential voltage-controlled oscillator analog-to-digital converter using input-referred offset |

| US10454483B2 (en) * | 2016-10-24 | 2019-10-22 | Analog Devices, Inc. | Open loop oscillator time-to-digital conversion |

| US9991898B1 (en) * | 2016-11-16 | 2018-06-05 | Perceptia Devices, Inc. | Fractional-N jitter attenuator |

| US10044383B2 (en) | 2016-12-30 | 2018-08-07 | Silicon Laboratories Inc. | Sinewave generation from multi-phase signals |

| US9979404B1 (en) | 2016-12-30 | 2018-05-22 | Silicon Laboratories Inc. | Multi-phase amplitude and phase modulation |

| EP3442129B1 (en) * | 2017-08-11 | 2020-06-03 | Samsung Electronics Co., Ltd. | Receiver and reception method based on pulse |

| KR102370285B1 (ko) * | 2017-08-11 | 2022-03-07 | 삼성전자주식회사 | 펄스를 이용한 수신기 및 수신 방법 |

| KR102452620B1 (ko) * | 2017-09-29 | 2022-10-07 | 삼성전자주식회사 | 터치 검출을 위한 장치 및 방법 |

| US10291247B1 (en) * | 2018-03-07 | 2019-05-14 | Xilinx, Inc. | Chopping switch time-skew calibration in time-interleaved analog-to-digital converters |

| US10483996B1 (en) * | 2018-05-29 | 2019-11-19 | Xilinx, Inc. | Time skew calibration of time-interleaved analog to digital converters |

| US10509104B1 (en) * | 2018-08-13 | 2019-12-17 | Analog Devices Global Unlimited Company | Apparatus and methods for synchronization of radar chips |

| US11231741B1 (en) * | 2018-10-11 | 2022-01-25 | Marvell Asia Pte, Ltd. | Systems and methods for generating clock signals |

| CN110069008B (zh) * | 2019-04-29 | 2020-05-22 | 复旦大学 | 一种时间数字转换器系统及包含该系统的倍数延迟锁相环 |

| CN110212912B (zh) * | 2019-06-06 | 2020-07-03 | 复旦大学 | 一种具有高精度时间数字转换器的倍数延迟锁相环 |

| KR102706475B1 (ko) * | 2019-06-26 | 2024-09-12 | 삼성전자주식회사 | 아날로그-디지털 컨버터 및 이를 포함하는 뉴로모픽 컴퓨팅 장치 |

| US11283437B2 (en) | 2019-12-17 | 2022-03-22 | Skyworks Solutions, Inc. | Measuring pin-to-pin delays between clock routes |

| US10958257B1 (en) * | 2020-04-28 | 2021-03-23 | Taiwan Semiconductor Manufacturing Company Limited | System and method for adjusting duty cycle of a signal |

| EP3996280B1 (en) * | 2020-11-05 | 2025-07-23 | Stichting IMEC Nederland | Circuit and method for random edge injection locking |

| CN112698363B (zh) * | 2020-12-29 | 2024-04-16 | 成都国星通信有限公司 | 一种北斗抗干扰天线高精度数据采集方法及采集电路 |

| JP2022146460A (ja) * | 2021-03-22 | 2022-10-05 | キオクシア株式会社 | 半導体回路、受信装置及びメモリシステム |

| EP4099608A4 (en) * | 2021-04-19 | 2023-01-11 | Tencent Technology (Shenzhen) Company Limited | CLOCK SYNCHRONIZATION SYSTEM, SIGNAL SYNCHRONIZATION CONTROL METHOD AND STORAGE MEDIA |

| JPWO2023112249A1 (ja) * | 2021-12-16 | 2023-06-22 | ||

| CN114564068B (zh) * | 2022-03-02 | 2023-07-14 | 重庆吉芯科技有限公司 | 应用于高速adc输入缓冲器的自适应电流产生电路及方法 |

| TWI793003B (zh) | 2022-05-05 | 2023-02-11 | 創意電子股份有限公司 | 消除相位雜訊之影響的校正系統與包含其的類比至數位轉換裝置 |

| CN115268355B (zh) * | 2022-07-29 | 2025-06-27 | 广东美的智能科技有限公司 | 数据处理方法、设备、输入输出扩展单元及控制器 |

| CN116015287B (zh) * | 2022-12-31 | 2024-03-19 | 成都电科星拓科技有限公司 | 一种基于频率转电压电路校正tdc步进的方法及装置 |

| CN116260959B (zh) * | 2023-03-08 | 2024-08-20 | 苏州欧谱曼迪科技有限公司 | 图像信号传输电路、图像采集传输系统及内窥镜 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE10007408A1 (de) * | 2000-02-18 | 2001-09-06 | Infineon Technologies Ag | Analog/Digital-Wandlerschaltungsanordnung |

| JP2003133954A (ja) | 2001-10-26 | 2003-05-09 | Agilent Technologies Japan Ltd | インターリーブa/d変換器の校正方法 |

| JP3692405B2 (ja) * | 2003-04-18 | 2005-09-07 | 独立行政法人情報通信研究機構 | アナログ/デジタル変換器の性能測定システム及び性能測定方法、並びに、デジタル/アナログ変換器の性能測定システム及び性能測定方法 |

| WO2004109927A1 (en) * | 2003-06-04 | 2004-12-16 | Koninklijke Philips Electronics N.V. | Bit-detection arrangement and apparatus for reproducing information |

| US7332973B2 (en) * | 2005-11-02 | 2008-02-19 | Skyworks Solutions, Inc. | Circuit and method for digital phase-frequency error detection |

| US7365607B2 (en) * | 2006-08-10 | 2008-04-29 | Newport Media, Inc. | Low-power, low-jitter, fractional-N all-digital phase-locked loop (PLL) |

| JPWO2008105183A1 (ja) * | 2007-02-28 | 2010-06-03 | パナソニック株式会社 | A/d変換器、及びa/d変換方法 |

| JP4271244B2 (ja) | 2007-03-26 | 2009-06-03 | 株式会社半導体理工学研究センター | アナログ・デジタル(ad)変換器及びアナログ・デジタル変換方法 |

| WO2008156401A1 (en) * | 2007-06-21 | 2008-12-24 | Signal Processing Devices Sweden Ab | Compensation of mismatch errors in a time-interleaved analog-to-digital converter |

| JP4977570B2 (ja) * | 2007-10-03 | 2012-07-18 | 株式会社日立製作所 | デジタルキャリブレーション型アナログデジタル変換器及びそれを用いた無線受信回路及び無線送受信回路 |

| JP2009117894A (ja) * | 2007-11-01 | 2009-05-28 | Univ Of Tokyo | 注入同期型発振器 |

| WO2011039859A1 (ja) * | 2009-09-30 | 2011-04-07 | 株式会社日立製作所 | アナログデジタル変換器およびそれを用いた半導体集積回路装置 |

| JP5458806B2 (ja) * | 2009-10-28 | 2014-04-02 | 日本電気株式会社 | A/d変換装置 |

-

2011

- 2011-09-06 JP JP2011193965A patent/JP5684076B2/ja not_active Expired - Fee Related

-

2012

- 2012-08-08 US US13/570,228 patent/US8933831B2/en not_active Expired - Fee Related

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20190143028A (ko) * | 2018-06-19 | 2019-12-30 | 세종대학교산학협력단 | 시간 디지털 변환 카운터 및 이를 포함하는 라이더 시스템 |

| KR102077626B1 (ko) * | 2018-06-19 | 2020-02-14 | 세종대학교산학협력단 | 시간 디지털 변환 카운터 및 이를 포함하는 라이더 시스템 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20130058437A1 (en) | 2013-03-07 |

| JP2013055598A (ja) | 2013-03-21 |

| US8933831B2 (en) | 2015-01-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5684076B2 (ja) | アナログデジタル変換器及び無線受信機 | |

| JP7655612B2 (ja) | 高線形性位相補間器 | |

| EP2711725B1 (en) | Phase noise tolerant sampling | |

| JP5673808B2 (ja) | クロック生成回路 | |

| Lee et al. | A low-noise wideband digital phase-locked loop based on a coarse–fine time-to-digital converter with subpicosecond resolution | |

| US10303124B2 (en) | Time-to-digital converter | |

| Gao et al. | Spur reduction techniques for phase-locked loops exploiting a sub-sampling phase detector | |

| US9941891B2 (en) | Adaptive spur cancellation techniques and multi-phase injection locked TDC for digital phase locked loop circuit | |

| JP5284131B2 (ja) | 位相同期回路及びこれを用いた受信機 | |

| CN102291126B (zh) | 对来自相位控制环路中的相位检测器的低频噪声的抑制 | |

| JP5347534B2 (ja) | 位相比較器、pll回路、及び位相比較器の制御方法 | |

| US9246670B2 (en) | Compact low-power fully digital CMOS clock generation apparatus for high-speed SerDes | |

| US20080238752A1 (en) | Analog-to-digital (AD) converter and analog-to-digital conversion method | |

| JP5609585B2 (ja) | Pll回路、pll回路の誤差補償方法及び通信装置 | |

| US7924191B2 (en) | Integrated poly-phase fir filter in double-sampled analog to digital converters | |

| Yu et al. | A 148fs rms integrated noise 4MHz bandwidth all-digital second-order ΔΣ time-to-digital converter using gated switched-ring oscillator | |

| Nagaraj et al. | Architectures and circuit techniques for multi-purpose digital phase lock loops | |

| GB2555413A (en) | Sampling circuitry | |

| Zhao et al. | A low-power digital design of all digital PLL for 2.4 G wireless communication applications | |

| CN110212912A (zh) | 一种具有高精度时间数字转换器的倍数延迟锁相环 | |

| CN116155268A (zh) | 任意频率时钟产生系统 | |

| Yang et al. | The Design and Analysis for Improving the Power-Efficiency of Ring-VCO Based PLL | |

| TW202535073A (zh) | 半導體裝置、該半導體裝置之控制方法、及控制程式 | |

| US10305493B2 (en) | Phase-locked loop and frequency synthesizer | |

| Hamouda et al. | A 20-Gbps low jitter analog clock recovery circuit for ultra-wide band Radio systems |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20131111 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140526 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140610 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140731 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20141216 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20150114 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5684076 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| LAPS | Cancellation because of no payment of annual fees |