JP5515216B2 - フィードフォワード分割器を有する適応帯域幅位相ロックループ - Google Patents

フィードフォワード分割器を有する適応帯域幅位相ロックループ Download PDFInfo

- Publication number

- JP5515216B2 JP5515216B2 JP2007341739A JP2007341739A JP5515216B2 JP 5515216 B2 JP5515216 B2 JP 5515216B2 JP 2007341739 A JP2007341739 A JP 2007341739A JP 2007341739 A JP2007341739 A JP 2007341739A JP 5515216 B2 JP5515216 B2 JP 5515216B2

- Authority

- JP

- Japan

- Prior art keywords

- sub

- pll

- division ratio

- clock signal

- output

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/16—Indirect frequency synthesis, i.e. generating a desired one of a number of predetermined frequencies using a frequency- or phase-locked loop

- H03L7/22—Indirect frequency synthesis, i.e. generating a desired one of a number of predetermined frequencies using a frequency- or phase-locked loop using more than one loop

- H03L7/23—Indirect frequency synthesis, i.e. generating a desired one of a number of predetermined frequencies using a frequency- or phase-locked loop using more than one loop with pulse counters or frequency dividers

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

- H03L7/089—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal the phase or frequency detector generating up-down pulses

- H03L7/0891—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal the phase or frequency detector generating up-down pulses the up-down pulses controlling source and sink current generators, e.g. a charge pump

- H03L7/0895—Details of the current generators

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

- H03L7/093—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal using special filtering or amplification characteristics in the loop

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/099—Details of the phase-locked loop concerning mainly the controlled oscillator of the loop

- H03L7/0995—Details of the phase-locked loop concerning mainly the controlled oscillator of the loop the oscillator comprising a ring oscillator

Landscapes

- Stabilization Of Oscillater, Synchronisation, Frequency Synthesizers (AREA)

Description

適応帯域幅PLLは、処理、電圧、及び温度(PVT)変動と殆ど無関係に作動周波数に比例してその力学をスケーリングするPLLの部類を意味する。

一部の実施形態では、方法は、第1及び第2サブ位相ロックループ(サブPLL)の第1及び第2電圧制御式発振器(VCO)に電圧制御信号を供給する段階を含む。更に、本方法は、第1及び第2VCOから第1及び第2VCO出力信号と第1及び第2フィードフォワード分割回路とを出力する段階と、第1及び第2VCO出力信号の第1及び第2周波数を第1及び第2分周率によって分割する段階と、第1及び第2分周率を選択する段階とを含む。

他の実施形態も説明して特許請求する。

本発明は、本発明の実施形態を示すために使用される以下の説明及び添付図面を参照することによって理解することができる。しかし、本発明は、これらの図面の詳細に限定されるものではない。

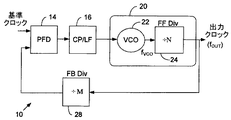

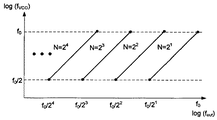

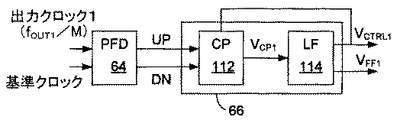

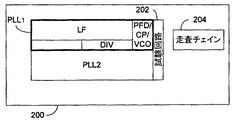

図1は、位相周波数検出器(PFD)10と、チャージポンプ(CP)/ループフィルタ(LF)16と、電圧制御式発振器(VCO)22及び分周率Nを有するフィードフォワード周波数分割器(FF Div)24を含む出力周波数制御回路20と、分周率Mを有するフィードバック周波数分割器(FB Div)28とを有するPLL10を示している。VCO22は、周波数fVCOを有するVCO信号を供給する。「FF Div」24は、周波数fOUTを有する出力クロック信号(out clk)を供給し、かつこの信号はまた、「FB Div」28に対しても供給される。「FB Div」28の出力は、PFD14への入力として供給される。CP/LF16のチャージポンプ及びループフィルタは、異なる回路であるが、図示を容易にするために結合されている。「FF Div」24の分周率(N)は、調節される。一部の実施形態では、VCOの調節領域が比較的狭い場合であっても、この調節によって「FF Div」24が広い領域の周波数を発生させることを可能にする。

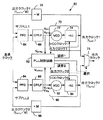

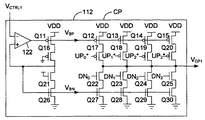

図6は、一部の実施形態によるチャージポンプ112及びそのバイアス回路の例を示すが、他の実施形態は、これらの詳細を含まない。適応式帯域幅に対してVBN(負バイアス)をVBNを通じてVCTRLに等しく設定することにより、チャージポンプ電流は、VCO電流に追従するようにバイアスされ、比較器122にフィードバック信号として供給される。また、このフィードバックは、VBP(正バイアス)を制御し、昇圧及び降圧電流が、例えば2%内に合わされて、静的位相オフセットを削減する。チャージポンプ112は、それぞれ、NMの1、2、及び4に対して、1倍、1/2倍、及び1/4倍の電流レベルをとるように区分される。Pチャンネル金属酸化膜半導体電界効果トランジスタ(PMOSFET)Q11、Q12、Q13、Q14、及びQ15のゲートは、比較器122の出力(VBP信号)を受け取ると共に、Nチャンネル金属酸化膜半導体電界効果トランジスタ(NMOSFET)Q26、Q27、Q28、Q29、及びQ30のゲートは、VBN信号を受け取る。「PMOSFET」Q17、Q18、Q19、及びQ20は、アップ信号UP0 *、UP1 *、UP2 *、及びUP2 *を受け取る。ここでUP0 *、UP1 *及びUP2 *は、UP0、UP1、及びUP2の論理的逆である。UP2は、UP0及びUP1の2倍の重みを有することに注意されたい。「NMOSFET」Q22、Q23、Q24、及びQ25は、ダウン信号DN0、DN1、DN2、及びDN3を受け取る。DN2は、DN0及びDN1の2倍の重みがあることに注意されたい。「PMOSFET」Q16及び「NMOSFET」Q21は、Q16及びQ21間にVBN信号を有してQ11及びQ26間で結合される。チャージポンプ電圧VCPは、「PMOSFET」Q17、Q18、Q19、及びQ20と「NMOSFET」Q22、Q23、Q24、及びQ25間に供給される。

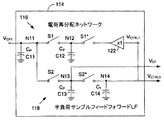

N15の電圧が引き下げられる時、「PMOSFET」Q71はONになり、VREGを昇圧してQ43をOFFにする。コンデンサC20は、電圧変動を平滑化する。電圧VREGは、インバータI1、I2、I3、I4、及びI5が振動する速度を制御し、その結果インバータI5から供給されるVCO1クロック信号の周波数を制御する。

処理技術:0.13μm、N−ウェル、1P6M CMOS

面積:1.1×0.46mm2

電源電圧:1.2V公称

ワット損:36mW

基準周波数範囲:2MHz〜1GHz

出力周波数範囲:2MHz〜1GHz

増倍率範囲:M=20〜9

ループ帯域幅:基準周波数の〜1/100

ジッタ(M=1、1.024GHz):13.10ps、pp、1.62ps、rms

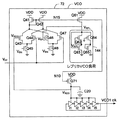

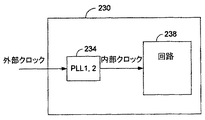

図10は、デュアルPLL234が外部クロック信号を受け取り、このデュアルPLLが回路238に内部クロック信号を供給するチップ230を示している。

図3では、分割Mは、回路78及び98に対して同じであるが、これらは異なっていてもよい。

本発明をいくつかの実施形態によって説明したが、本発明は、説明したそれらの実施形態に限定されるべきではなく、特許請求の範囲及び精神の範囲内で修正及び変更して実施することができる。以上の説明は、従って、限定的ではなく例示的であるとみなすものとする。

22 電圧制御式発振器

24 フィードフォワード周波数分割器

N、M 分周率

Claims (14)

- 第1及び第2のサブ位相ロックループ(サブPLL)であって、第1及び第2の電圧制御式発振器(VCO)出力信号を供給する第1及び第2のVCOと、該第1及び第2のVCO出力信号の第1及び第2の周波数を可変の第1及び第2の分周率によって分割し、前記第1のサブPLLから第1の出力クロック信号を生成し、前記第2のサブPLLから第2の出力クロック信号を生成する第1及び第2のフィードフォワード分割回路とを含む第1及び第2のサブ位相ロックループ(サブPLL)と、

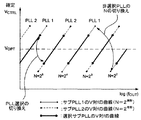

前記第1及び第2の分周率を選択し、前記第1のサブPLLからの前記第1の出力クロック信号又は前記第2のサブPLLからの前記第2の出力クロック信号のいずれかを出力信号として選択する位相ロックループ(PLL)制御回路であって、前記第1の出力クロック信号、前記第2の出力クロック信号、前記第1のサブPLLの前記第1のVCOによって受信される第1の制御電圧及び前記第2のサブPLLの前記第2のVCOによって受信される第2の制御電圧に基づいて、可変の分周率の選択と前記出力信号の選択をするPLL制御回路と、

を含み、

前記サブPLLの1つが、前記出力信号を提供するために前記位相ロックループ制御回路によって選択され、前記位相ロックループ制御回路が他のサブPLLに対する分周率を変更でき、

前記PLL制御回路による前記第1の分周率及び前記第2の分周率の選択は、前記第1の制御電圧及び前記第2の制御電圧が単一の最適電圧値に対してどの程度近いかに基づいていることを特徴とする位相ロックループ出力信号を生成するチップ。 - 前記第1の分周率は、前記第2の分周率と異なっていることを特徴とする請求項1に記載のチップ。

- 前記第1の分周率は、2の整数べき乗に等しく、前記第2の分周率も、2の整数べき乗に等しく、

前記第1の分周率に対する前記整数は、前記第2の分周率に対する前記整数と異なっている、

ことを特徴とする請求項1に記載のチップ。 - 前記第1のサブPLLの前記整数は、偶数整数であり、前記第2のサブPLLの前記整数は、奇数整数であることを特徴とする請求項3に記載のチップ。

- 前記第1及び第2のサブPLLは、

第1及び第2の位相周波数検出器、及び

前記第1及び第2の出力クロック信号の前記周波数を分割する第1及び第2のフィードバック分割回路であって、第1及び第2の分割回路の出力を前記第1及び第2の位相周波数検出器に供給する第1及び第2のフィードバック分割回路、

を含む、

ことを特徴とする請求項1に記載のチップ。 - 現在選択されていないサブPLLの変更される分周率が、選択されているサブPLLの分周率より良好である場合、前記PLL制御回路は、サブPLLの選択を選択されてないPLLに変更する請求項1に記載のチップ。

- 第1及び第2のサブ位相ロックループ(サブPLL)の第1及び第2の電圧制御式発振器(VCO)に第1及び第2の電圧制御信号を供給する段階と、

前記第1及び第2のVCOから第1及び第2のフィードフォワード分割回路に第1及び第2のVCO出力信号を出力する段階と、

前記第1のサブPLLから第1の出力クロック信号を生成すると共に前記第2のサブPLLから第2の出力クロック信号を生成するために、前記第1及び第2のフィードフォワード分割回路を用いて前記第1及び第2のVCO出力信号の第1及び第2の周波数を可変の第1及び第2の分周率によって分割する段階と、

前記第1及び第2分周率を選択する段階と、

記第1のサブPLLからの前記第1の出力クロック信号又は前記第2のサブPLLからの前記第2の出力クロック信号のいずれかを出力信号として選択する段階と、

を含み、

前記サブPLLの1つの前記出力クロック信号が、前記出力信号として選択され、他のサブPLLに対する分周率を変更でき、

前記可変の第1及び第2の分周率の選択と前記出力信号の選択は、前記第1の出力クロック信号、前記第2の出力クロック信号、前記第1のサブPLLの前記第1のVCOによって受信される第1の制御電圧及び前記第2のサブPLLの前記第2のVCOによって受信される第2の制御電圧に基づいてなされるものであり、前記PLL制御回路による前記第1の分周率及び前記第2の分周率の選択は、前記第1の制御電圧及び前記第2の制御電圧が単一の最適電圧値に対してどの程度近いかに基づいていることを特徴とする位相ロックループ出力信号を生成する方法。 - 前記第1の分周率は、前記第2の分周率と異なっていることを特徴とする請求項7に記載の方法。

- 選択されていないサブPLLの変更される分周率が、選択されているサブPLLの分周率より良好である場合、現在選択されているサブPLLから選択されていないサブPLLへ前記出力クロック信号の選択を変更することを更に含む請求項7に記載の方法。

- 入力クロック信号を搬送する少なくとも1つの導体と、

第1及び第2の電圧制御式発振器(VCO)出力信号を供給する第1及び第2のVCOと、該第1及び第2のVCO出力信号の第1及び第2の周波数を可変の第1及び第2の分周率によって分割する第1及び第2のフィードフォワード分割回路とを含む第1及び第2のサブ位相ロックループ(サブPLL)であって、前記第1のサブPLLから第1の出力クロック信号を生成し、前記第2のサブPLLから第2の出力クロック信号を生成する第1及び第2のサブPLL、及び

前記第1及び第2の分周率を選択し、記第1のサブPLLからの前記第1の出力クロック信号又は前記第2のサブPLLからの前記第2の出力クロック信号のいずれかを出力信号として選択する位相ロックループ(PLL)制御回路、

を含むデュアル位相ロックループ(デュアルPLL)と、

を含み、

前記サブPLLの1つが、前記出力信号を提供するために前記PLL制御回路によって選択される一方で、前記PLL制御回路が他のサブPLLに対する分周率を変更でき、

前記可変の第1及び第2の分周率の選択と前記出力信号の選択は、前記第1の出力クロック信号、前記第2の出力クロック信号、前記第1のサブPLLの前記第1のVCOによって受信される第1の制御電圧及び前記第2のサブPLLの前記第2のVCOによって受信される第2の制御電圧に基づいてなされるものであり、前記PLL制御回路による前記第1の分周率及び前記第2の分周率の選択は、前記第1の制御電圧及び前記第2の制御電圧が単一の最適電圧値に対してどの程度近いかに基づいていることを特徴とする位相ロックループ出力信号を生成するチップ。 - 前記第1の分周率は、前記第2の分周率と異なっていることを特徴とする請求項10に記載のチップ。

- 前記第1の分周率は、2の整数べき乗に等しく、前記第2の分周率も、2の整数べき乗に等しく、

前記第1の分周率に対する前記整数は、前記第2の分周率に対する前記整数と異なっている、

ことを特徴とする請求項10に記載のチップ。 - 前記第1のサブPLLの整数は、偶数の整数であり、前記第2のサブPLLの整数は、奇数の整数である請求項10に記載のチップ。

- 現在選択されていないサブPLLの変更される分周率が、選択されているサブPLLの分周率より良好である場合、前記PLL制御回路は、サブPLLの選択を選択されてないPLLに変更する請求項10に記載のチップ。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/637,254 | 2006-12-11 | ||

| US11/637,254 US7602253B2 (en) | 2006-12-11 | 2006-12-11 | Adaptive bandwidth phase locked loop with feedforward divider |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008148346A JP2008148346A (ja) | 2008-06-26 |

| JP5515216B2 true JP5515216B2 (ja) | 2014-06-11 |

Family

ID=38996611

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007341739A Active JP5515216B2 (ja) | 2006-12-11 | 2007-12-11 | フィードフォワード分割器を有する適応帯域幅位相ロックループ |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US7602253B2 (ja) |

| EP (1) | EP1933464B1 (ja) |

| JP (1) | JP5515216B2 (ja) |

| KR (1) | KR101470990B1 (ja) |

| CN (1) | CN101202546B (ja) |

| DE (1) | DE602007009176D1 (ja) |

| TW (1) | TWI356592B (ja) |

Families Citing this family (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7747237B2 (en) * | 2004-04-09 | 2010-06-29 | Skyworks Solutions, Inc. | High agility frequency synthesizer phase-locked loop |

| US20080317185A1 (en) * | 2007-06-25 | 2008-12-25 | Broadcom Corporation | Dual phase locked loop (pll) architecture for multi-mode operation in communication systems |

| US7821343B1 (en) * | 2008-08-27 | 2010-10-26 | Altera Corporation | Transmitter with multiple phase locked loops |

| TWI384761B (zh) * | 2009-02-20 | 2013-02-01 | Sunplus Technology Co Ltd | Low jitter, wide operating frequency band and frequency synthesis system suitable for low voltage operation |

| US8044726B2 (en) * | 2009-03-17 | 2011-10-25 | Qualcomm Incorporated | Systems and methods for self testing a voltage controlled oscillator |

| US7973612B2 (en) * | 2009-04-26 | 2011-07-05 | Qualcomm Incorporated | Supply-regulated phase-locked loop (PLL) and method of using |

| JP2011188077A (ja) * | 2010-03-05 | 2011-09-22 | Renesas Electronics Corp | 位相同期回路及びその制御方法 |

| US8415999B2 (en) | 2010-07-28 | 2013-04-09 | International Business Machines Corporation | High frequency quadrature PLL circuit and method |

| US8258835B1 (en) * | 2011-06-15 | 2012-09-04 | Asahi Kasei Microdevices Corporation | Cancellation system for phase jumps at loop gain changes in fractional-N frequency synthesizers |

| CN103269220A (zh) * | 2013-05-30 | 2013-08-28 | 上海坤锐电子科技有限公司 | 基于数字琐相环的nfc有源负载调制的时钟恢复电路 |

| CN103346784B (zh) * | 2013-06-18 | 2016-04-13 | 成都嘉纳海威科技有限责任公司 | 一种用于锁相环的匹配型电荷泵电路 |

| US9350362B2 (en) | 2013-10-08 | 2016-05-24 | Thomas & Betts International, Llc | Programmable slew rate phase locked loop |

| US9444473B2 (en) * | 2014-09-09 | 2016-09-13 | Qualcomm Incorporated | Increased synthesizer performance in carrier aggregation/multiple-input, multiple-output systems |

| JP6463467B2 (ja) | 2015-04-15 | 2019-02-06 | 三菱電機株式会社 | シンセサイザ |

| US10958278B2 (en) * | 2019-07-31 | 2021-03-23 | Intel Corporation | Techniques in phase-lock loop configuration in a computing device |

| JP7643994B2 (ja) * | 2021-12-22 | 2025-03-11 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| US12531564B2 (en) * | 2022-09-19 | 2026-01-20 | Qualcomm Incorporated | Synchronizing multiple phase-locked loop circuits |

| US12261609B1 (en) * | 2023-10-18 | 2025-03-25 | Shaoxing Yuanfang Semiconductor Co., Ltd. | Inter-PLL communication in a multi-PLL environment |

Family Cites Families (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60197015A (ja) | 1984-03-21 | 1985-10-05 | Nec Corp | 位相同期発振器 |

| JPS63305619A (ja) * | 1987-06-08 | 1988-12-13 | Mitsubishi Electric Corp | Pllシンセサイザ装置 |

| JPH01120133U (ja) * | 1988-02-06 | 1989-08-15 | ||

| JPH03190428A (ja) * | 1989-12-20 | 1991-08-20 | Matsushita Electric Ind Co Ltd | 位相同期回路 |

| JPH05145413A (ja) * | 1991-11-20 | 1993-06-11 | Nippon Denki Musen Denshi Kk | 位相同期回路 |

| JPH05199109A (ja) * | 1992-01-20 | 1993-08-06 | Ricoh Co Ltd | Pll回路 |

| JPH05227024A (ja) * | 1992-02-12 | 1993-09-03 | Sony Tektronix Corp | Pll発振装置 |

| US5483202A (en) * | 1994-08-31 | 1996-01-09 | Polaroid Corporation | Compensated phase locked loop for generating a controlled output clock signal |

| JPH08125529A (ja) * | 1994-10-20 | 1996-05-17 | Fujitsu General Ltd | Pll回路 |

| GB2295930B (en) | 1994-12-06 | 1999-11-24 | Motorola Ltd | Method and apparatus for implementing frequency hopping in a TDMA system |

| US5610558A (en) * | 1995-11-03 | 1997-03-11 | Motorola, Inc. | Controlled tracking of oscillators in a circuit with multiple frequency sensitive elements |

| JPH10271002A (ja) * | 1997-03-21 | 1998-10-09 | Sony Corp | 発振制御装置 |

| US6049254A (en) * | 1997-10-16 | 2000-04-11 | Oasis Design, Inc. | Phase-locked loop which can automatically adjust to and lock upon a variable input frequency |

| JPH11136124A (ja) * | 1997-10-27 | 1999-05-21 | Matsushita Electric Ind Co Ltd | Pll回路 |

| JPH11214992A (ja) * | 1998-01-23 | 1999-08-06 | Mitsubishi Electric Corp | 周波数シンセサイザ |

| US6111442A (en) * | 1998-03-09 | 2000-08-29 | International Business Machines Corporation | Phase-locked loop circuit with dynamic backup |

| JP2000252821A (ja) * | 1999-02-26 | 2000-09-14 | Ando Electric Co Ltd | 通信装置のクロック発生回路、および、通信装置のクロック発生方法 |

| KR20010059868A (ko) * | 1999-12-30 | 2001-07-06 | 윤종용 | 듀얼 위상동기루프의 주파수 발생 방법 |

| GB2363268B (en) * | 2000-06-08 | 2004-04-14 | Mitel Corp | Timing circuit with dual phase locked loops |

| JP2002064378A (ja) * | 2000-08-18 | 2002-02-28 | Advantest Corp | 信号発生器 |

| US6281727B1 (en) * | 2000-10-05 | 2001-08-28 | Pericom Semiconductor Corp. | Fine-tuning phase-locked loop PLL using variable resistor between dual PLL loops |

| US6670833B2 (en) * | 2002-01-23 | 2003-12-30 | Intel Corporation | Multiple VCO phase lock loop architecture |

| US7290156B2 (en) | 2003-12-17 | 2007-10-30 | Via Technologies, Inc. | Frequency-voltage mechanism for microprocessor power management |

| US7302599B2 (en) * | 2004-02-12 | 2007-11-27 | Via Technologies, Inc. | Instantaneous frequency-based microprocessor power management |

| US6812797B1 (en) * | 2003-05-30 | 2004-11-02 | Agere Systems Inc. | Phase-locked loop with loop select signal based switching between frequency detection and phase detection |

| US6762634B1 (en) * | 2003-08-13 | 2004-07-13 | Pericom Semiconductor Corp. | Dual-loop PLL with DAC offset for frequency shift while maintaining input tracking |

| US7630468B2 (en) * | 2003-12-19 | 2009-12-08 | Broadcom Corporation | Dual-PLL signaling for maintaining synchronization in a communications system |

-

2006

- 2006-12-11 US US11/637,254 patent/US7602253B2/en active Active

-

2007

- 2007-10-24 TW TW096139964A patent/TWI356592B/zh active

- 2007-10-31 EP EP07254315A patent/EP1933464B1/en active Active

- 2007-10-31 DE DE602007009176T patent/DE602007009176D1/de active Active

- 2007-12-10 KR KR1020070127886A patent/KR101470990B1/ko active Active

- 2007-12-10 CN CN2007101942310A patent/CN101202546B/zh active Active

- 2007-12-11 JP JP2007341739A patent/JP5515216B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| KR101470990B1 (ko) | 2014-12-12 |

| CN101202546B (zh) | 2012-12-26 |

| CN101202546A (zh) | 2008-06-18 |

| DE602007009176D1 (de) | 2010-10-28 |

| US20080136531A1 (en) | 2008-06-12 |

| KR20080053902A (ko) | 2008-06-16 |

| EP1933464A1 (en) | 2008-06-18 |

| TWI356592B (en) | 2012-01-11 |

| JP2008148346A (ja) | 2008-06-26 |

| US7602253B2 (en) | 2009-10-13 |

| EP1933464B1 (en) | 2010-09-15 |

| TW200830719A (en) | 2008-07-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5515216B2 (ja) | フィードフォワード分割器を有する適応帯域幅位相ロックループ | |

| US8040191B2 (en) | PLL circuit with VCO gain control | |

| US5781048A (en) | Synchronous circuit capable of properly removing in-phase noise | |

| US7696799B2 (en) | Delay cell of voltage controlled delay line using digital and analog control scheme | |

| US7379521B2 (en) | Delay circuit with timing adjustment function | |

| US5952892A (en) | Low-gain, low-jitter voltage controlled oscillator circuit | |

| US8264259B2 (en) | Phase-locked loop circuit and delay-locked loop circuit | |

| US7339438B2 (en) | Phase and delay locked loops and semiconductor memory device having the same | |

| US20090033429A1 (en) | Phase locked loop for stably operating in a matter that is insensitive to variation in process, voltage and temperature and method of operating the same | |

| US6624706B2 (en) | Automatic bias adjustment circuit for use in PLL circuit | |

| KR20000056764A (ko) | 아날로그 디엘엘회로 | |

| US7719331B2 (en) | PLL circuit | |

| US7375557B2 (en) | Phase-locked loop and method thereof and a phase-frequency detector and method thereof | |

| US7268633B2 (en) | Voltage-controlled oscillator for low-voltage, wide frequency range operation | |

| US8531218B1 (en) | Frequency generating system | |

| US8471613B2 (en) | Internal clock signal generator and operating method thereof | |

| JP7514162B2 (ja) | 間欠動作アンプを用いたpll回路 | |

| JP2000036741A (ja) | Pll回路 | |

| JP4534140B2 (ja) | Pll回路 | |

| US12500590B2 (en) | Phase-locked loop circuit | |

| US8373465B1 (en) | Electronic device and method for phase locked loop | |

| US20250125811A1 (en) | Initial control voltage generating circuit for voltage-controlled oscillator and phase-locked loop circuit with the initial control voltage generating circuit | |

| US20060140325A1 (en) | Integrated CMOS clock generator with a self-biased phase locked loop circuit | |

| KR20060103605A (ko) | 주파수 이득이 낮은 vco를 가지는 위상동조기 및 그의제어방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20101206 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120611 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120618 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20120918 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20120921 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121018 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130415 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20130716 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20130719 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20130814 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20130819 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130917 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140224 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20140228 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20140228 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140317 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5515216 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |