JP5407936B2 - 電磁ノイズ抑制体 - Google Patents

電磁ノイズ抑制体 Download PDFInfo

- Publication number

- JP5407936B2 JP5407936B2 JP2010045196A JP2010045196A JP5407936B2 JP 5407936 B2 JP5407936 B2 JP 5407936B2 JP 2010045196 A JP2010045196 A JP 2010045196A JP 2010045196 A JP2010045196 A JP 2010045196A JP 5407936 B2 JP5407936 B2 JP 5407936B2

- Authority

- JP

- Japan

- Prior art keywords

- magnetic

- electromagnetic noise

- magnetic flux

- ferromagnetic

- ferromagnetic body

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H10W74/00—

-

- H10W90/754—

Landscapes

- Shielding Devices Or Components To Electric Or Magnetic Fields (AREA)

Description

特許文献1に示される電磁波吸収体では、電磁波発生体である電子部品を覆うように配置されて、強磁性材料の磁化容易方向が発生磁界成分の方向と一致するように、該強磁性材料を配向した構成とされている。

また、非特許文献2では円形の磁性体を積層した例が報告されている。非特許文献2では円形の強磁性体が積層されたものであるが、角部が無い場合は磁極が生じにくいので強磁性体外部に形成される磁界は弱まる可能性がある。ただし、磁区の磁気モーメントの配列パターンによっては還流磁区構造にならないため、強い磁界を生じることがある。

すなわち、強磁性体がノイズ放射源から集めた磁気エネルギーが端部から漏洩し、隣接する回路に影響を与える可能性がある。強磁性体をLSIチップやLSIパッケージ上にシート状に形成する場合には強磁性体の厚みが10〜100マイクロメートル程度であり、強磁性体内部で生じる高周波損失、ヒステリシス損失などの損失が磁界を十分に減衰できる程度に大きいとは限らない。そのため、強磁性体に収束する磁界が強磁性体内部で減衰しないため端部から磁気エネルギーが漏洩し、強磁性体の近傍では磁界が強くなる場所が出現する可能性がある。

すなわち、本発明では、回路基板上に積層されたシート状の強磁性体により構成される電磁ノイズ抑制体であって、前記強磁性体は環状に形成されてその内部に収束した磁束を閉じ込めることにより、電磁ノイズを低減させることを特徴としている。

また、本発明では、回路基板上に積層されたシート状の強磁性体により構成される電磁ノイズ抑制体であって、前記強磁性体はその内部に収束した磁束を閉じ込め、電磁干渉が生じにくい所定領域まで該磁束を誘導しかつ漏洩させることにより、電磁ノイズを低減させることを特徴とする。

第2の発明では、強磁性体に収束した磁束を強磁性体内部に閉じ込めることにより、強磁性体がノイズ放射源から集めた磁気エネルギーを漏洩させず、隣接する回路に与える影響を排除することができる。このとき、電磁干渉が生じにくい所定領域まで前記磁束を誘導し、周辺の磁気ノイズに弱い回路に影響を与えにくい場所にてその前記磁束を漏洩させることにより、特に磁気ノイズに弱い回路に対して、電磁ノイズの影響を確実に抑制することができる。

そして、これらの発明により、電子機器から放射された電磁ノイズが、外部の電子機器や電子機器内部の隣接する回路の機能を低下させ、かつ誤動作を発生させる電磁障害(EMI)を防止する。また、外部から侵入しようとするノイズに対する電磁イミュニティを向上させ、かつLSI内部で扱う秘密情報が漏洩し、盗聴される可能性が低くなり、耐タンパー性能も向上させることも可能となる。

本実施例の電磁ノイズ抑制体はプリント配線板、セラミック基板、LSIチップなどの回路基板に適用されるシート状体である。

図1は本発明の実施例を説明するため一般的なICパッケージ1の実装状態を示す図であって、(A)はその上面図、(B)はその側面図である。図1に符号1で示される電子部品のICパッケージは、基板2上に接合ボール3を介して実装されている。

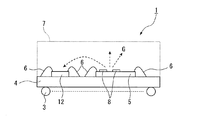

ここで、電子回路10はノイズ放射源であり、形成する磁束Gにより、周囲にある電磁ノイズに弱い電子回路11に電磁障害を発生させうるものとする。また、符号12は、インタポーザ基板4上に直接配置された電子回路である。

そして、このように本願の円環状の強磁性体8を採用しかつ配置することで、電磁障害を発生しにくい方向に磁束を誘導し、かつ強磁性体8の外部に磁界が発生しにくくなるという優れた特徴を有する。一般に棒状、あるいは角型の強磁性体を磁化すると棒の端面付近に磁極が発生し、強磁性体外部においてはその磁極から反対側の磁極に向けて磁界が発生し、強磁性体内部においては反磁界が発生する。これは磁気に関する基本的な現象であり、磁気工学の分野では良く知られている。強磁性体を環状にすると、磁束G2が始点に戻ってくるため強磁性体8の内部に磁極が発生しない。したがって、磁極による磁界が発生しにくくなり、言い換えれば磁束の漏洩が低減できる。

これまで述べた通り、強磁性体8を円環状にし、かつその一部をノイズの放射源である電子回路10上に積層し、磁路が電磁ノイズに弱い電子回路11から離れるように該強磁性体8を配置することにより、該強磁性体8に集められたノイズが再漏洩されることがなく、電磁障害を抑制することが可能となる。

ここで、電子回路10が発生する磁束(符号G1で示す)の向きと、前述の強磁性体8の軟磁性となる向きを合わせる。これにより、磁束G1が強磁性体8の内部で形成され、磁極を形成しない磁束G2の向きと同じであるので、強磁性体8の内部に磁束G2を取り込むことが容易となる。また、円周方向に一軸異方性であるとすれば、磁束G2を円周方向に誘導しやすくなる。従って、強磁性体外部への磁束の漏洩を抑制でき、結果として電子回路11などの電磁ノイズに弱い回路に対する電磁妨害を減らすことができる。

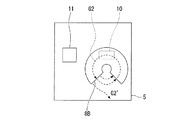

本実施例1では、図3では一例として円環状に強磁性体8が形成されているが、楕円状でも同様の効果が期待できる。長方形や正方形を使って環を形成し、その角部を面取りした形状でも同様の効果が期待できる。滑らかな形状となるように面取りを行うことが望ましいが、多角形の組み合わせでも効果が期待できる。

本実施例1では、図3に一例として示すように、円環状に強磁性体8が形成されているが、図4で示すようにその強磁性体8の一部を切り欠いて間隙部8Bを設けるようにしても良い。そして、このような強磁性体8の間隙部8Bを、電磁干渉が生じにくい位置に設ける配置とすることにより、電磁ノイズを強磁性体8の内部に収束する磁束として誘導することができ、電磁障害の発生に関係の無い場所で、間隙部8Bを通じて磁束(符号G2´で示す)を所定領域に漏洩させることができる。その結果、強磁性体8が持つ減衰量が小さい場合でも、磁束を誘導して運び間隙部8Bで漏洩させることで、高性能なノイズ抑制体を形成することができる。

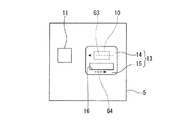

実施例2の電磁ノイズ抑制体が実施例1と異なる点は、実施例2の電磁ノイズ抑制体が、中央の開口部8Aが真円又は真円に近い円環状の強磁性体8からなるのに対して、実施例2の電磁ノイズ抑制体では、環の形状を変化させることでその磁気特性を部分的に変化させて、漏洩する磁束Gを低減させるようにしている。

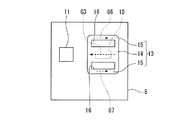

実施例2では、強磁性体13を構成するメインフィルム14とサブフィルム15は一体化して形成して良く、異なるプロセスで形成しても良い。

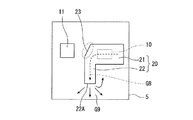

実施例2では、主磁路となりメインフィルム14と、副磁路となるサブフィルム15とにより段部を有する強磁性体13を構成するとともに、メインフィルム14を側方から迂回するようにサブフィルム15を連結した。しかし、これに限定されず、図6に示すように、主磁路となりメインフィルム14の図中下部位置に、副磁路となるサブフィルム15を連結することで、全体として段部が無く磁極を発生させない四角形状に強磁性体13を形成しても良い。そして、このような構成によっても、強磁性体13内部に収束した磁束は、開口出口の無い環状の強磁性体13によりその内部に閉じ込められるので、外部に漏れ出ることができず、強磁性体13の磁気損失によりその磁束を強磁性体13内部で減衰させることができる。

実施例2では、主磁路となりメインフィルム14と、副磁路となる1本のサブフィルム15とにより強磁性体13を全体として四角形状に形成したが、これに限定されず、図7に示すように、メインフィルム14の端部に2本のサブフィルム15を連結し、これらメインフィルム14及び2本のサブフィルム15により2つの磁気経路(符号G6・G7で示す)を形成しても良い。そして、このような構成によっても、強磁性体13内部に収束した磁束は、開口出口の無い強磁性体13によりその内部に閉じ込められているので、外部に漏れ出ることができず、強磁性体13の磁気損失によりその磁束を強磁性体13内部で減衰させることができる。

なお、このようなサブフィルム15は2本に限定されず、磁気特性に応じて2本以上の複数本設けても良く、その幅も適宜設定しても良い。また、強磁性体13のメインフィルム14とサブフィルム15との間には対称となる位置関係に孔16が形成されるが、この孔16の大きさは、周囲の電子部品12の配置に応じた電磁ノイズを低減度合いに応じて適宜、調整すると良い。

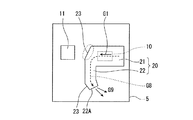

実施例3の電磁ノイズ抑制体が実施例1・2と異なるのは、実施例1・2の電磁ノイズ抑制体が環状の強磁性体8からなるのに対して、実施例3の電磁ノイズ抑制体では、図8に示されるように、L字状に曲がった形状の強磁性体20により構成される点である。

サブフィルム22の端部22Aには磁極が形成され、新たな磁束(符号G9で示す)が形成され、かつ端部22Aから磁束G9が漏洩する。磁束G9は通常、放射状に広がり、一部はメインフィルム21の別の磁極が形成されている部分に向かうなど、強磁性体20近傍にある分布を形成する。ここで、サブフィルム22の端部22Aが電子回路11に対向配置されていないので、電子回路11周辺には強い磁界が形成されることもない。従って、電子回路11に対する電磁干渉を低減することができる。また、メインフィルム21と幅狭のサブフィルム22とがL字をなすコーナー部23は面取りされたような鈍角になる形状になっている。

実施例3では、1つのコーナー部23でL字状に屈曲した強磁性体20を例に挙げたが、これに限定されず、図9に示すように、2つ以上のコーナー部23を設けることで、サブフィルム22の端部22Aを所望の箇所に位置させ、これにより電子回路に影響を与えず電磁ノイズを漏洩させるようにしても良い。強磁性体20の屈曲部23はL字状に限らず、C字状、J字状、T字状などの形状でも良く、いずれの側に屈曲させても良い。

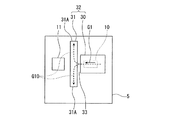

上記実施例3では、幅広のメインフィルム21と幅狭のサブフィルム22を一体に連結することで強磁性体20を形成したが、これに限定されず、図10に示すように幅広のメインフィルム30と幅狭のサブフィルム31を別体とすることで強磁性体32を構成しても良い。

このような強強磁性体32では、一定の長さを有するサブフィルム31の中間部近傍に、微小な間隙33を介在させてメインフィルム30が近接配置されており、サブフィルム31の端部31Aが図中上下方向に延伸するように配置となっている。そして、このような強強磁性体32では、幅広のメインフィルム30により磁束を集め、かつ幅狭のサブフィルム31により磁束G10を誘導するようにしているが、このときメインフィルム30とサブフィルム31との間には間隙33があるので、該磁束10Gは、メインフィルム30の端部30Aから漏洩することになる。しかし、サブフィルム31がメインフィルム30に近接配置されているため、磁束10Gは、サブフィルム31に吸引かつ誘導されて、該サブフィルム31に沿い下側又は上側の端部31Aに向かうようになる。

すなわち、上述したような屈曲部23を設けず、メインフィルム30とサブフィルム31の間に微小な間隙33を介在させることで強磁性体32を構成しても良い。そして、このように強磁性体32では、LSIチップ5上に半導体プロセスによりメインフィルム30、サブフィルム31が形成される場合は、間隙33の大きさを1マイクロメートル以下とすることで、良好な磁気的結合を得ることができる。

8B 間隙部

10 電子回路

11 電子回路

13 強磁性体

20 強磁性体

30 メインフィルム(強磁性体シート)

31 サブフィルム(強磁性体シート)

32 強磁性体

33 間隙

G1〜G10 磁束

Claims (8)

- 回路基板上に積層されたシート状の強磁性体により構成される電磁ノイズ抑制体であって、

前記強磁性体は環状に形成されてその内部に収束した磁束を閉じ込めることにより、電磁ノイズを低減させることを特徴とする電磁ノイズ抑制体。 - 環状に形成された前記強磁性体の孔が非対称に設けられていることを特徴とする請求項1の電磁ノイズ抑制体。

- 前記強磁性体の磁気特性を部分的に変化させたことを特徴とする請求項1または2のいずれか1項に記載の電磁ノイズ抑制体。

- 前記強磁性体の幅を変化させることにより前記磁気特性を部分的に変化させることを特徴とする請求項3の電磁ノイズ抑制体。

- 前記強磁性体の一部に、電磁干渉が生じにくい所定位置で切り欠きとなる間隙部を設けたことを特徴とする請求項1〜4のいずれか1項に記載の電磁ノイズ抑制体。

- 前記強磁性体の透磁率を変化させて構成したことを特徴とする請求項1〜5のいずれか1項に記載の電磁ノイズ抑制体。

- 前記強磁性体が、一軸異方性を有することを特徴とすることを特徴とする請求項1〜6のいずれか1項に記載の電磁ノイズ抑制体。

- 前記強磁性体の一部を少なくとも電磁ノイズの放射源である回路上に設置し、かつ、該強磁性体が電磁ノイズに弱い回路の近傍に設置されないように形成したことを特徴とする請求項1〜7のいずれか1項に記載の電磁ノイズ抑制体。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010045196A JP5407936B2 (ja) | 2010-03-02 | 2010-03-02 | 電磁ノイズ抑制体 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010045196A JP5407936B2 (ja) | 2010-03-02 | 2010-03-02 | 電磁ノイズ抑制体 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011181730A JP2011181730A (ja) | 2011-09-15 |

| JP5407936B2 true JP5407936B2 (ja) | 2014-02-05 |

Family

ID=44692935

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010045196A Expired - Fee Related JP5407936B2 (ja) | 2010-03-02 | 2010-03-02 | 電磁ノイズ抑制体 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5407936B2 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5670392B2 (ja) | 2012-07-27 | 2015-02-18 | 株式会社東芝 | 回路基板 |

| JP5904957B2 (ja) * | 2013-02-28 | 2016-04-20 | キヤノン株式会社 | 電子部品および電子機器。 |

| WO2014167871A1 (ja) * | 2013-04-10 | 2014-10-16 | 株式会社村田製作所 | 半導体装置 |

| JP7450457B2 (ja) * | 2020-05-22 | 2024-03-15 | 三菱電機株式会社 | 磁性体シートおよび該磁性体シートを備えた電子機器 |

| CN113625214B (zh) * | 2021-08-10 | 2023-08-29 | 广东工业大学 | 一种磁力计电磁干扰诊断滤波方法及系统 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001148596A (ja) * | 1999-11-22 | 2001-05-29 | Sony Corp | 電波吸収体 |

| JP2003115691A (ja) * | 2001-10-04 | 2003-04-18 | Tdk Corp | フィルム状emiフィルタ |

| JP2004146505A (ja) * | 2002-10-23 | 2004-05-20 | Kyocera Corp | 電磁波吸収部材とその製造方法、及びこれを用いた高周波回路パッケージ用蓋体並びに高周波回路パッケージ |

| JP4161911B2 (ja) * | 2004-01-30 | 2008-10-08 | ソニー株式会社 | 集積回路装置 |

-

2010

- 2010-03-02 JP JP2010045196A patent/JP5407936B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2011181730A (ja) | 2011-09-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5407936B2 (ja) | 電磁ノイズ抑制体 | |

| US20160164178A1 (en) | Antenna device and portable electronic device using the same | |

| KR102288244B1 (ko) | 전자파 감쇠체 및 전자 장치 | |

| JP2011054672A (ja) | 電気磁気素子およびその製造方法 | |

| CN209658154U (zh) | 电子元件 | |

| US10468354B2 (en) | Semiconductor device with magnetic layer and nonmagnetic layer | |

| US20150303573A1 (en) | Antenna device | |

| CN111491500B (zh) | 电磁波衰减体及电子装置 | |

| JP2009071604A (ja) | 平面アンテナ | |

| JPH1064714A (ja) | Emi対策部品及びそれを備えた能動素子 | |

| US8143696B2 (en) | Integrated circuit inductors with reduced magnetic coupling | |

| US10510680B2 (en) | Semiconductor device having electromagnetic wave attenuation layer | |

| TWI774013B (zh) | 具有磁屏蔽層的裝置及方法 | |

| Muroga et al. | Simultaneous evaluation of conductive/near-field noise suppression in Co-Zr-Nb film using magnetic circuit | |

| JP2011030106A (ja) | 非接触icカードリーダ・ライタのシールドアンテナ、そのアンテナ・シールド | |

| US8964400B2 (en) | Circuitry arrangement for reducing a tendency towards oscillations | |

| Yamaguchi et al. | On-chip integrated magnetic thin-film solution to countermeasure digital noise on RF IC | |

| Ma et al. | Analysis of multilayered Co-Zr-Nb film on-chip noise suppressor as a function of resistivity and permeability | |

| Ma et al. | Analysis of magnetic-film-type noise suppressor integrated on transmission lines for on-chip crosstalk evaluation | |

| JP5574281B2 (ja) | 磁性体装置 | |

| JP6048218B2 (ja) | Esd保護デバイス | |

| JP2010010635A (ja) | 電磁ノイズ対策部材及び電磁ノイズ対策方法 | |

| JP6044021B2 (ja) | ノイズ抑制部材 | |

| KR101011633B1 (ko) | 고인덕턴스를 제공하는 적층형 파워인덕터 | |

| JPH04164393A (ja) | 磁界スリット型シールド方式 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20130212 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130705 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130716 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130911 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20131008 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131021 |

|

| LAPS | Cancellation because of no payment of annual fees |