JP5368397B2 - 電界効果トランジスタおよびその製造方法 - Google Patents

電界効果トランジスタおよびその製造方法 Download PDFInfo

- Publication number

- JP5368397B2 JP5368397B2 JP2010200298A JP2010200298A JP5368397B2 JP 5368397 B2 JP5368397 B2 JP 5368397B2 JP 2010200298 A JP2010200298 A JP 2010200298A JP 2010200298 A JP2010200298 A JP 2010200298A JP 5368397 B2 JP5368397 B2 JP 5368397B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- aln

- doped

- concentration

- type

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Landscapes

- Electrodes Of Semiconductors (AREA)

- Junction Field-Effect Transistors (AREA)

Description

図3に、Siドープn型AlN層を用いたショットキーダイオードを示す。(a)は上面図、(b)は横断面図である。ショットキーダイオードは、半絶縁性基板であるAlN(0001)基板31上に、アンドープAlN層32、Siドープn型AlN層33が順に積層されている。さらに、Siドープn型AlN層33上に、ショットキー電極35と、高濃度Siドープn型AlN層34上に形成されたオーミック電極36とが積層されている。

図7に、Siドープn型AlN層のSi濃度と耐圧の関係を示す。実施例1では、Siドープn型AlN層33のSi濃度を1×1017cm−3とした。ここでは、図5に示した再成長による手法で、Si濃度を変えてショットキーダイオードを作製した。500V以上の耐圧は、Si濃度が5×1018cm−3以下において得られる。Si濃度が5×1016cm−3では、耐圧は1000Vまで増加する。ただし、5×1016cm−3以下では、ショットキーダイオードは動作しなくなる。これは、Si濃度が5×1016cm−3以下では、高い導電性を有するn型AlNが得られないからである。

実施例1では、オーミック電極36とSiドープn型AlN層33との間に、高濃度Siドープn型AlN層34が挿入されている。高出力電子デバイスでは、電力損失を下げるためには、オーミック電極36の接触抵抗を下げる必要がある。図8に、高濃度Siドープn型AlN層のSi濃度と接触抵抗の関係を示す。

図5を参照して述べたように、再成長によりショットキーダイオードを作製する場合、リフトオフによりSiO2マスク37およびSiO2マスク上の高濃度Siドープn型AlN層34を除去する(図5(c)〜(d))。従来のGaNを用いたショットキーダイオードの場合には、SiO2マスク上にGaNが堆積しないので、容易にGaNを除去することができる。しかし、Alが含まれるAlNやAlYGa1−YN(0<Y<1、以下、組成の範囲の表示は省略する)の場合には、SiO2マスク上にAlNやAlYGa1−YNが堆積するために、それらを除去することは困難になる。

実施例1では、絶縁性基板として半絶縁性AlN(0001)基板を用いている。基板材料と耐圧の関係について調べた結果を表1に示す。

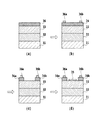

図14に、実施例4−1にかかる電界効果トランジスタを示す。ここでは、図5に示した(B)再成長により作製する方法と同様にして、(E)AlN/AlGaN/AlN電界効果トランジスタを作製する手順を示す。(1)MOCVD法により、AlN(0001)基板71上に、膜厚1μmのアンドープAlN層72と、膜厚0.5μm、Si濃度1×1018cm−3のSiドープn型AlN層73と、Al組成X=0.8、膜厚30nmのAlXGa1−XNチャネル層78と、膜厚5nmのAlNキャップ層79をエピタキシャル成長させる。(2)SiO2マスクをスパッタリング法により堆積する。(3)MOCVD法により、膜厚40nm、Si濃度5×1019cm−3の高濃度Siドープn型AlN層74を再成長させる。

図17に、AlN/AlXGa1−XN/AlN電界効果トランジスタのAlXGa1−XNチャネル層の膜厚とAl組成Xとの関係を示す。実施例4では、AlXGa1−XNチャネル層78,88のAl組成Xを0.8および膜厚を30nmとした。最大動作電圧が100V以上、最大相互コンタクタンスが500mS/mm以上、最大ドレイン電流が1A/mm以上と高出力特性が優れた電界効果トランジスタが得られる条件を〇、特性が劣化する条件を×で示す。

t<20+200×X、

の条件下においてのみ、高出力特性が優れた電界効果トランジスタが得られる。

図18に、Siドープn型AlN層のSi濃度と最大ドレイン電流の関係を示す。実施例4では、Siドープn型AlN層73,83のSi濃度を1×1018cm−3とした。1A/mm以上の最大ドレイン電流は、Si濃度が5×1016cm−3から5×1018cm−3の範囲においてのみ得られる。ただし、5×1016cm−3以下では、電界効果トランジスタは動作しなくなる。これは、Si濃度が5×1016cm−3以下では、高い導電性を有するn型AlNが得られないからである。従って、Siドープn型AlN層73,83のSi濃度を、5×1016cm−3から5×1018cm−3の範囲にすることで、最大ドレイン電流が高い電界効果トランジスタを作製することができる。

図19に、AlNキャップ層の膜厚と最大相互コンダクタンスの関係を示す。実施例4では、AlNキャップ層79,89の膜厚を5nmとした。500mS/mm以上の最大相互コンタクタンスは、AlNキャップ層79,89の膜厚が15nm以下においてのみ得られる。膜厚を3nmにおいては、最大相互コンタクタンスは900mS/mmまで増加する。MOCVD法によりAlNキャップ層79,89を成長させるため、AlNキャップ層79,89の膜厚は0.5nmの精度で制御できる。従って、AlNキャップ層の膜厚を15nm以下にすることで、最大相互コンタクタンスが高い電界効果トランジスタを作製することができる。

図20に、実施例5−1にかかるAlN/Si/AlN電界効果トランジスタを示す。(G)エッチングと再成長により作製したAlN/Si/AlN電界効果トランジスタの構造を示す。ここでは、図16に示した実施例4−2の手順と同様にして、電界効果トランジスタを作製する手順を示す。(1)MOCVD法により、AlN(0001)基板101上に、膜厚1μmのアンドープAlN層102と、0.1分子層のSi層103と、膜厚8nmのAlNキャップ層109とをエピタキシャル成長させる。(2)SiO2マスクをスパッタリング法により堆積する。(3)AlNキャップ層109とSi層103の一部をアンドープAlN層102が露出するまで、塩素ガスを用いたドライエッチング(反応性イオンエッチング)により取り除く。

図22に、Si層の堆積量と最大ドレイン電流の関係を示す。前述のように、実施例5では、Si層103,113の堆積量を0.1分子層とした。0.5A/mm以上の最大ドレイン電流は、Si層103,113の堆積量が1分子層以下においてのみ得られる。ただし、Si層を挿入しない場合には、電界効果トランジスタは動作しなくなる。従って、Si層103,113の堆積量を1分子層以下にすることで、最大ドレイン電流が高い電界効果トランジスタを作製することができる。

上述したように、ショットキーダイオードのオーミック電極、電界効果トランジスタのソース電極およびドレイン電極は、高濃度Siドープn型AlN層上に形成した。これらの電極には、低い接触抵抗を有するオーミック特性が求められる。オーミック電極を形成する構造とオーミック電極の接触抵抗の関係を調べた。接触抵抗は、伝送線路(TLM)法を用いて求めた。作製した構造は、次の4つである。

(B)AlN(0001)基板上にアンドープAlN層(膜厚0.5μm)、Siドープn型AlN層(膜厚4μm、Si濃度1×1017cm−3)、高濃度Siドープn型AlN層(膜厚10nm、Si濃度5×1019cm−3)をエピタキシャル成長した構造。

(C)AlN(0001)基板上にアンドープAlN層(膜厚0.5μm)、Siドープn型AlN層(膜厚4μm、Si濃度1×1017cm−3)、高濃度Siドープn型AlN層(膜厚3nm、Si濃度5×1019cm−3)、高濃度Siドープn型AlZGa1−ZN組成傾斜層(Al組成Zは1から0へと連続的に変化、膜厚3nm、Si濃度5×1019cm−3)、高濃度Siドープn型GaN層(膜厚3nm、Si濃度5×1019cm−3)をエピタキシャル成長した構造。

(D)AlN(0001)基板上にアンドープAlN層(膜厚0.5μm)、Siドープn型AlN層(膜厚4μm、Si濃度1×1017cm−3)、高濃度Siドープn型AlN層(膜厚3nm、Si濃度5×1019cm−3)、高濃度Siドープn型AlN層(膜厚3nm、Si濃度5×1019cm−3)と高濃度Siドープn型AlZGa1−ZN層(膜厚3nm、Al組成Z=0.2、Si濃度5×1019cm−3)とを交互に積層した超格子層(5周期)をエピタキシャル成長した構造。

上述したように、ショットキーダイオードのオーミック電極、電界効果トランジスタのソース電極およびドレイン電極には、Ti/Al/Ti/Auを用いた。これら電極には低い接触抵抗が求められる。これら電極に用いる材料と接触抵抗の関係を調べた結果を表7に示す。

12 Siドープn型GaN層

13,35,43,54 ショットキー電極

14,36,44,55 オーミック電極

21 基板

22 アンドープGaN層

23 SiドープAlGaNキャップ層

24,67,77,87,107,117 ソース電極

25,66,76,86,106,116 ゲート電極

26,65,75,85,105,115 ドレイン電極

31,41,61,71,81,101,111 AlN(0001)基板

32,62,72,82,102,112 アンドープAlN層

33,42,52,63,73,83 Siドープn型AlN層

34,53,64,74,84,104,114 高濃度Siドープn型AlN層

37,90 SiO2マスク

51 AlN(000−1)基板

78,88 AlXGa1−XNチャネル層

79,89,109,119 AlNキャップ層

103,113 Si層

Claims (14)

- 半絶縁性基板上に積層されたアンドープAlN層と、

該アンドープAlN層上に積層されたSiドープn型AlN層と、

該Siドープn型AlN層上に積層されたAlXGa1−XNチャネル層と、

該AlXGa1−XNチャネル層上に積層されたAlNキャップ層と、

該AlNキャップ層上に、高濃度Siドープn型AlN層を介して形成されたドレイン電極およびソース電極と、

前記AlNキャップ層上に形成されたゲート電極とを備え、

前記Siドープn型AlN層のSi濃度は、5×1016cm−3〜5×1018cm−3であり、前記AlXGa1−XNチャネル層のAl組成Xは、0.9以下であり、前記AlXGa1−XNチャネル層の膜厚t(nm)は、t<20+200×Xの関係を満たし、前記高濃度Siドープn型AlN層のSi濃度は、5×1019cm−3以上であり、

前記ゲート電極の材料は、Pd,Pt,Ni,Au,Mo,W,Ta,Nb,Al,Tiのいずれか1つが含まれ、前記AlNキャップ層の表面とPd,Pt,Ni,Au,Mo,W,Ta,Nb,Al,Tiのいずれか1つの材料が接触していることを特徴とする電界効果トランジスタ。 - 半絶縁性基板上に積層されたアンドープAlN層と、

該アンドープAlN層上に積層されたSiドープn型AlN層と、

該Siドープn型AlN層上に積層されたAlXGa1−XNチャネル層と、

該AlXGa1−XNチャネル層上に積層されたAlNキャップ層と、

該AlNキャップ層と前記AlXGa1−XNチャネル層の一部を除去した部分に、高濃度Siドープn型AlYGa1−YN層を介して形成されたドレイン電極およびソース電極と、

前記AlNキャップ層上に形成されたゲート電極とを備え、

前記Siドープn型AlN層のSi濃度は、5×1016cm−3〜5×1018cm−3であり、前記AlXGa1−XNチャネル層のAl組成Xは、0.9以下であり、前記AlXGa1−XNチャネル層の膜厚t(nm)は、t<20+200×Xの関係を満たし、前記高濃度Siドープn型AlYGa1−YN層のSi濃度は、5×1019cm−3以上であり、Al組成XとYとの関係は、Y≦Xであり、

前記ゲート電極の材料は、Pd,Pt,Ni,Au,Mo,W,Ta,Nb,Al,Tiのいずれか1つが含まれ、前記AlNキャップ層の表面とPd,Pt,Ni,Au,Mo,W,Ta,Nb,Al,Tiのいずれか1つの材料が接触していることを特徴とする電界効果トランジスタ。 - 半絶縁性基板上に積層されたアンドープAlN層と、

該アンドープAlN層上に積層され、膜厚が1分子層以下のSi層と、

該Si層上に積層され、膜厚が15nm以下のAlNキャップ層と、

該AlNキャップ層と前記Si層と前記アンドープAlN層の一部を除去した部分に、高濃度Siドープn型AlN層を介して形成されたドレイン電極およびソース電極と、

前記AlNキャップ層上に形成されたゲート電極とを備え、

前記高濃度Siドープn型AlN層のSi濃度は、1×1019cm−3以上であることを特徴とする電界効果トランジスタ。 - 半絶縁性基板上に積層されたアンドープAlN層と、

該アンドープAlN層上に積層され、膜厚が1分子層以下のSi層と、

該Si層上に積層され、膜厚が15nm以下のAlNキャップ層と、

該AlNキャップ層上に、高濃度Siドープn型AlN層を介して形成されたドレイン電極およびソース電極と、

前記AlNキャップ層上に形成されたゲート電極とを備え、

前記高濃度Siドープn型AlN層のSi濃度は、1×1019cm−3以上であることを特徴とする電界効果トランジスタ。 - 前記高濃度Siドープn型AlN層と前記ドレイン電極およびソース電極との間に、高濃度Siドープn型AlZGa1−ZN組成傾斜層と、高濃度Siドープn型GaN層とを形成し、前記高濃度Siドープn型AlZGa1−ZN組成傾斜層のAl組成Zを、前記高濃度Siドープn型AlN層から前記高濃度Siドープn型GaN層に向けて1から0へと連続的に変化させ、前記高濃度Siドープn型AlZGa1−ZN組成傾斜層および前記高濃度Siドープn型GaN層のSi濃度は、1×1019cm−3以上であることを特徴とする請求項1ないし4のいずれかに記載の電界効果トランジスタ。

- 前記高濃度Siドープn型AlN層と前記ドレイン電極およびソース電極との間に、高濃度Siドープn型AlN層と高濃度Siドープn型AlZGa1−ZN層とを交互に積層した超格子層を形成し、前記高濃度Siドープn型AlZGa1−ZN層のAl組成Zは、0〜0.9であり、前記高濃度Siドープn型AlN層および前記高濃度Siドープn型AlZGa1−ZN層の膜厚は、5nm以下であり、記高濃度Siドープn型AlN層および前記高濃度Siドープn型AlZGa1−ZN層のSi濃度は、1×1019cm−3以上であることを特徴とする請求項1ないし4のいずれかに記載の電界効果トランジスタ。

- 前記ドレイン電極およびソース電極は、Mo,W,Ta,Al,Tiのいずれか1つが含まれ、

前記高濃度Siドープn型AlN層、前記高濃度Siドープn型AlYGa1−YN層、前記高濃度Siドープn型GaN層または前記超格子層の表面とTi,Al,W,Mo,Taのいずれか1つの材料が接触していることを特徴とする請求項6に記載の電界効果トランジスタ。 - 前記ゲート電極の材料は、Pd,Pt,Ni,Au,Mo,W,Ta,Nb,Al,Tiのいずれか1つが含まれ、

前記AlNキャップ層の表面とPd,Pt,Ni,Au,Mo,W,Ta,Nb,Al,Tiのいずれか1つの材料が接触していることを特徴とする請求項3または4に記載の電界効果トランジスタ。 - 前記半絶縁性基板は、成長表面が(0001)面であるAlN基板、SiC基板、サファイア基板のいずれかであることを特徴とする請求項1ないし4のいずれかに記載の電界効果トランジスタ。

- 半絶縁性基板上にアンドープAlN層を積層し、Si濃度が5×1016cm−3〜5×1018cm−3であるSiドープn型AlN層を、前記アンドープAlN層上に積層し、Al組成Xが0.9以下であり、膜厚t(nm)がt<20+200×Xの関係を満たすAlXGa1−XNチャネル層を、前記Siドープn型AlN層上に積層し、膜厚が15nm以下のAlNキャップ層を、前記AlXGa1−XNチャネル層上に積層し、Al組成YがAl組成XとY≦Xの関係を満たし、Si濃度が1×1019cm−3以上である高濃度Siドープn型AlYGa1−YN層を積層する第1の工程と、

前記高濃度Siドープn型AlYGa1−YN層の一部を、前記AlNキャップ層が露出するまでエッチングにより取り除く第2の工程と、

露出した前記AlNキャップ層上にゲート電極を形成する工程であって、前記ゲート電極は、Pd,Pt,Ni,Au,Mo,W,Ta,Nb,Al,Tiのいずれか1つが含まれ、前記AlNキャップ層の表面とPd,Pt,Ni,Au,Mo,W,Ta,Nb,Al,Tiのいずれか1つの材料が接触している、第3の工程と、

前記高濃度Siドープn型AlYGa1−YN層上にソース電極およびドレイン電極を形成する第4の工程と

を備えたことを特徴とする電界効果トランジスタの製造方法。 - 半絶縁性基板上にアンドープAlN層を積層し、Si濃度が5×1016cm−3〜5×1018cm−3であるSiドープn型AlN層を、前記アンドープAlN層上に積層し、Al組成Xが0.9以下であり、膜厚t(nm)がt<20+200×Xの関係を満たすAlXGa1−XNチャネル層を、前記Siドープn型AlN層上に積層し、膜厚が15nm以下のAlNキャップ層を、前記AlXGa1−XNチャネル層上に積層する第1の工程と、

前記AlNキャップ層上に、Al組成YがAl組成XとY≦Xの関係を満たし、Si濃度が1×1019cm−3以上である高濃度Siドープn型AlYGa1−YN層を、再成長により選択的に形成する第2の工程と、

前記AlNキャップ層上にゲート電極を形成する工程であって、前記ゲート電極は、Pd,Pt,Ni,Au,Mo,W,Ta,Nb,Al,Tiのいずれか1つが含まれ、前記AlNキャップ層の表面とPd,Pt,Ni,Au,Mo,W,Ta,Nb,Al,Tiのいずれか1つの材料が接触している、第3の工程と、

再成長により形成した前記高濃度Siドープn型AlYGa1−YN層上にソース電極およびドレイン電極を形成する第4の工程と

を備えたことを特徴とする電界効果トランジスタの製造方法。 - 半絶縁性基板上にアンドープAlN層を積層し、Si濃度が5×1016cm−3〜5×1018cm−3であるSiドープn型AlN層を、前記アンドープAlN層上に積層し、Al組成Xが0.9以下であり、膜厚t(nm)がt<20+200×Xの関係を満たすAlXGa1−XNチャネル層を、前記Siドープn型AlN層上に積層し、膜厚が15nm以下のAlNキャップ層を、前記AlXGa1−XNチャネル層上に積層する第1の工程と、

前記AlNキャップ層と前記AlXGa1−XNチャネル層の一部を、前記Siドープn型AlN層の近傍までエッチングにより取り除く第2の工程と、

露出した前記Siドープn型AlN層上に、Al組成YがAl組成XとY≦Xの関係を満たし、Si濃度が1×1019cm−3以上である高濃度Siドープn型AlYGa1−YN層を、再成長により選択的に形成する第3の工程と、

前記AlNキャップ層上にゲート電極を形成する工程であって、前記ゲート電極は、Pd,Pt,Ni,Au,Mo,W,Ta,Nb,Al,Tiのいずれか1つが含まれ、前記AlNキャップ層の表面とPd,Pt,Ni,Au,Mo,W,Ta,Nb,Al,Tiのいずれか1つの材料が接触している、第4の工程と、

再成長により形成した前記高濃度Siドープn型AlYGa1−YN層上にソース電極およびドレイン電極を形成する第5の工程と

を備えたことを特徴とする電界効果トランジスタの製造方法。 - 半絶縁性基板上にアンドープAlN層を積層し、膜厚が1分子層以下のSi層を前記アンドープAlN層上に積層し、膜厚が15nm以下のAlNキャップ層を前記Si層上に積層する第1の工程と、

前記AlNキャップ層上に、Si濃度が1×1019cm−3以上である高濃度Siドープn型AlN層を、再成長により選択的に形成する第2の工程と、

前記AlNキャップ層上にゲート電極を形成する第3の工程と、

再成長により形成した前記高濃度Siドープn型AlN層上にソース電極およびドレイン電極を形成する第4の工程と

を備えたことを特徴とする電界効果トランジスタの製造方法。 - 半絶縁性基板上にアンドープAlN層を積層し、膜厚が1分子層以下のSi層を前記アンドープAlN層上に積層し、膜厚が15nm以下のAlNキャップ層を前記Si層上に積層する第1の工程と、

前記AlNキャップ層と前記Si層と前記アンドープAlN層の一部をエッチングにより取り除く第2の工程と、

露出した前記アンドープAlN層上に、Si濃度が1×1019cm−3以上である高濃度Siドープn型AlN層を、再成長により選択的に形成する第3の工程と、

前記AlNキャップ層上にゲート電極を形成する第4の工程と、

再成長により形成した前記高濃度Siドープn型AlN層上にソース電極およびドレイン電極を形成する第5の工程と

を備えたことを特徴とする電界効果トランジスタの製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010200298A JP5368397B2 (ja) | 2010-09-07 | 2010-09-07 | 電界効果トランジスタおよびその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010200298A JP5368397B2 (ja) | 2010-09-07 | 2010-09-07 | 電界効果トランジスタおよびその製造方法 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005093163A Division JP4895520B2 (ja) | 2005-03-28 | 2005-03-28 | ショットキーダイオードおよびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011029648A JP2011029648A (ja) | 2011-02-10 |

| JP5368397B2 true JP5368397B2 (ja) | 2013-12-18 |

Family

ID=43637958

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010200298A Expired - Lifetime JP5368397B2 (ja) | 2010-09-07 | 2010-09-07 | 電界効果トランジスタおよびその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5368397B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6161246B2 (ja) * | 2012-09-28 | 2017-07-12 | トランスフォーム・ジャパン株式会社 | 半導体装置及び半導体装置の製造方法 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2663641B2 (ja) * | 1989-07-18 | 1997-10-15 | 日立電線株式会社 | 電界効果トランジスタの製造方法 |

| JPH07283237A (ja) * | 1994-04-07 | 1995-10-27 | Toyota Central Res & Dev Lab Inc | 電界効果トランジスタ |

| JPH10223652A (ja) * | 1997-02-07 | 1998-08-21 | Murata Mfg Co Ltd | 電界効果型半導体素子 |

| JP3085376B2 (ja) * | 1998-10-30 | 2000-09-04 | 住友電気工業株式会社 | 電界効果トランジスタ |

| JP3423896B2 (ja) * | 1999-03-25 | 2003-07-07 | 科学技術振興事業団 | 半導体デバイス |

| JP2001326232A (ja) * | 2000-05-12 | 2001-11-22 | Nippon Telegr & Teleph Corp <Ntt> | 半導体装置 |

| JP2003243423A (ja) * | 2002-02-19 | 2003-08-29 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| JP2003273398A (ja) * | 2002-03-20 | 2003-09-26 | Nippon Telegr & Teleph Corp <Ntt> | 半導体材料およびそれを用いた半導体装置 |

-

2010

- 2010-09-07 JP JP2010200298A patent/JP5368397B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2011029648A (ja) | 2011-02-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4895520B2 (ja) | ショットキーダイオードおよびその製造方法 | |

| JP5813279B2 (ja) | 窒化物ベースのトランジスタのための窒化アルミニウムを含むキャップ層およびその作製方法 | |

| KR101124937B1 (ko) | 질화물계 트랜지스터를 위한 캡층 및/또는 패시베이션층,트랜지스터 구조 및 그 제조방법 | |

| JP6174874B2 (ja) | 半導体装置 | |

| JP5634681B2 (ja) | 半導体素子 | |

| CN101689561B (zh) | 高压GaN基异质结晶体管的终止结构和接触结构 | |

| JP5891650B2 (ja) | 化合物半導体装置及びその製造方法 | |

| US8653561B2 (en) | III-nitride semiconductor electronic device, and method of fabricating III-nitride semiconductor electronic device | |

| US8330187B2 (en) | GaN-based field effect transistor | |

| CN101022128A (zh) | 氮化物半导体装置及其制作方法 | |

| CN111540781A (zh) | 在异质基底上的第III族氮化物缓冲层结构的p型掺杂 | |

| CN101027780A (zh) | Ⅲ-v族高电子迁移率晶体管器件 | |

| US20150123139A1 (en) | High electron mobility transistor and method of manufacturing the same | |

| JP2011166067A (ja) | 窒化物半導体装置 | |

| JP2005085852A (ja) | 半導体電子デバイス | |

| JP2009260296A (ja) | 窒化物半導体エピタキシャルウエハ及び窒化物半導体素子 | |

| JP6225584B2 (ja) | 半導体装置の評価方法、並びに半導体装置およびその製造方法 | |

| JP2006261642A (ja) | 電界効果トランジスタおよびその製造方法 | |

| JP6142893B2 (ja) | 化合物半導体装置及びその製造方法 | |

| US20150129889A1 (en) | Semiconductor device and semiconductor substrate | |

| JP2012230991A (ja) | 半導体装置 | |

| JP5368397B2 (ja) | 電界効果トランジスタおよびその製造方法 | |

| CN117199124A (zh) | 功率器件外延结构及其制备方法、功率器件 | |

| JP2012064977A (ja) | Iii族窒化物半導体積層ウェハ及びiii族窒化物半導体デバイス | |

| JP7069486B2 (ja) | 高電子移動度トランジスタ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130325 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130402 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130530 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130910 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130912 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5368397 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| EXPY | Cancellation because of completion of term |