JP5284487B2 - 表示装置 - Google Patents

表示装置 Download PDFInfo

- Publication number

- JP5284487B2 JP5284487B2 JP2011543359A JP2011543359A JP5284487B2 JP 5284487 B2 JP5284487 B2 JP 5284487B2 JP 2011543359 A JP2011543359 A JP 2011543359A JP 2011543359 A JP2011543359 A JP 2011543359A JP 5284487 B2 JP5284487 B2 JP 5284487B2

- Authority

- JP

- Japan

- Prior art keywords

- potential

- display device

- light

- photosensor

- wiring

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/01—Input arrangements or combined input and output arrangements for interaction between user and computer

- G06F3/03—Arrangements for converting the position or the displacement of a member into a coded form

- G06F3/041—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means

- G06F3/0412—Digitisers structurally integrated in a display

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/13624—Active matrix addressed cells having more than one switching element per pixel

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/01—Input arrangements or combined input and output arrangements for interaction between user and computer

- G06F3/03—Arrangements for converting the position or the displacement of a member into a coded form

- G06F3/041—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means

- G06F3/042—Digitisers, e.g. for touch screens or touch pads, characterised by the transducing means by opto-electronic means

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/13306—Circuit arrangements or driving methods for the control of single liquid crystal cells

- G02F1/13312—Circuits comprising photodetectors for purposes other than feedback

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0421—Structural details of the set of electrodes

- G09G2300/0426—Layout of electrodes and connections

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2360/00—Aspects of the architecture of display systems

- G09G2360/14—Detecting light within display terminals, e.g. using a single or a plurality of photosensors

- G09G2360/144—Detecting light within display terminals, e.g. using a single or a plurality of photosensors the light being ambient light

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Human Computer Interaction (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Nonlinear Science (AREA)

- Optics & Photonics (AREA)

- Mathematical Physics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Liquid Crystal (AREA)

- Position Input By Displaying (AREA)

- Solid State Image Pick-Up Elements (AREA)

- Light Receiving Elements (AREA)

Description

本発明は、フォトダイオードまたはフォトトランジスタ等の光検出素子を有する光センサ付きの表示装置に関し、特に、画素領域内に光センサを備えた表示装置に関する。

従来、例えばフォトダイオード等の光検出素子を画素内に備えたことにより、外光の明るさを検出したり、ディスプレイに近接した物体の画像を取り込んだりすることが可能な、光センサ付き表示装置が提案されている。

このような光センサ付き表示装置は、双方向通信用表示装置や、タッチパネル機能付き表示装置としての利用が想定されている。従来の光センサ付き表示装置では、アクティブマトリクス基板において、信号線および走査線、TFT(Thin Film Transistor)、画素電極等の周知の構成要素を半導体プロセスによって形成する際に、同時に、アクティブマトリクス基板上にフォトダイオード等を作り込む(特開2006−3857号公報参照)。

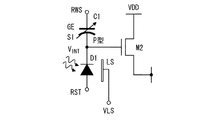

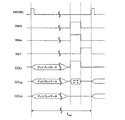

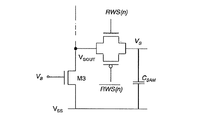

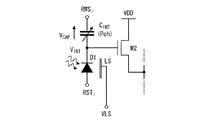

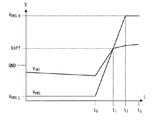

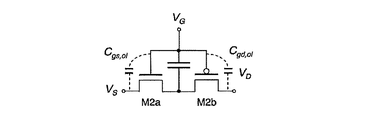

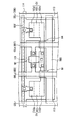

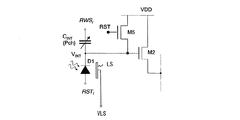

アクティブマトリクス基板上に形成される従来の光センサとして、国際公開第2007/145346号および国際公開第2007/145347号に開示された構成の一例を、図62に示す。図62に示す従来の光センサは、主として、フォトダイオードD1、コンデンサC2、トランジスタM2から構成される。フォトダイオードD1のアノードには、リセット信号を供給するための配線RSTが接続されている。フォトダイオードD1のカソードには、コンデンサC2の電極の一方と、トランジスタM2のゲートが接続されている。トランジスタM2のドレインは配線VDDに接続され、ソースは配線OUTに接続されている。コンデンサC2の電極の他方は、読み出し信号を供給するための配線RWSに接続されている。

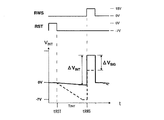

この構成において、配線RSTへリセット信号、配線RWSへ読み出し信号を、それぞれ所定のタイミングで供給することにより、フォトダイオードD1で受光した光の量に応じたセンサ出力VPIXを得ることができる。ここで、図63を参照し、図62に示したような従来の光センサの動作について説明する。なお、図63においては、リセット信号のローレベル(例えば−7V)をVRST.L、リセット信号のハイレベル(例えば0V)をVRST.H、読み出し信号のローレベル(例えば0V)をVRWS.L、読み出し信号のハイレベル(例えば15V)をVRWS.H、とそれぞれ表す。

まず、配線RSTへハイレベルのリセット信号VRST.Hが供給されると、フォトダイオードD1は順方向バイアスとなり、トランジスタM2のゲートの電位VINTは、下記の式(1)で表される。

VINT = VRST.H−VF ・・・(1)

式(1)において、VFはフォトダイオードD1の順方向電圧である。このときのVINTはトランジスタM2の閾値電圧より低いので、トランジスタM2はリセット期間において非導通状態となっている。

式(1)において、VFはフォトダイオードD1の順方向電圧である。このときのVINTはトランジスタM2の閾値電圧より低いので、トランジスタM2はリセット期間において非導通状態となっている。

次に、リセット信号がローレベル電位VRST.Lに戻る(図63においてtRSTのタイミング)ことにより、光電流の積分期間(センシング期間、図63に示すTINTの期間)が始まる。積分期間においては、フォトダイオードD1への入射光量に比例した光電流がコンデンサC2から流れ出し、コンデンサC2を放電させる。これにより、積分期間の終了時におけるトランジスタM2のゲートの電位VINTは、下記の式(2)で表される。

VINT=VRST.H−VF−ΔVRST・CPD/CTOTAL

−IPHOTO・TINT/CTOTAL …(2)

式(2)において、ΔVRSTは、リセット信号のパルスの高さ(VRST.H−VRST.L)であり、IPHOTOは、フォトダイオードD1の光電流、TINTは、積分期間の長さである。CPDは、フォトダイオードD1の容量である。CTOTALは、コンデンサC2の容量、フォトダイオードD1の容量CPDと、トランジスタM2の容量CTFTとの総和である。積分期間においても、VINTがトランジスタM2の閾値電圧より低いので、トランジスタM2は非導通状態となっている。

−IPHOTO・TINT/CTOTAL …(2)

式(2)において、ΔVRSTは、リセット信号のパルスの高さ(VRST.H−VRST.L)であり、IPHOTOは、フォトダイオードD1の光電流、TINTは、積分期間の長さである。CPDは、フォトダイオードD1の容量である。CTOTALは、コンデンサC2の容量、フォトダイオードD1の容量CPDと、トランジスタM2の容量CTFTとの総和である。積分期間においても、VINTがトランジスタM2の閾値電圧より低いので、トランジスタM2は非導通状態となっている。

積分期間が終わると、図63に示すtRWSのタイミングで読み出し信号RWSが立ち上がることにより、読み出し期間が始まる。なお、読み出し期間は、読み出し信号RWSがハイレベルの間、継続する。ここで、コンデンサC2に対して電荷注入が起こる。この結果、トランジスタM2のゲートの電位VINTは、下記の式(3)で表される。

VINT=VRST.H−VF−ΔVRST・CPD/CTOTAL−IPHOTO・TINT/CTOTAL

+ΔVRWS・CINT/CTOTAL…(3)

ΔVRWSは、読み出し信号のパルスの高さ(VRWS.H−VRWS.L)である。これにより、トランジスタM2のゲートの電位VINTが閾値電圧よりも高くなるので、トランジスタM2は導通状態となり、各列において配線OUTの端部に設けられているバイアストランジスタM3と共に、ソースフォロアアンプとして機能する。すなわち、トランジスタM2からのセンサ出力電圧VPIXは、積分期間におけるフォトダイオードD1の光電流の積分値に比例する。

+ΔVRWS・CINT/CTOTAL…(3)

ΔVRWSは、読み出し信号のパルスの高さ(VRWS.H−VRWS.L)である。これにより、トランジスタM2のゲートの電位VINTが閾値電圧よりも高くなるので、トランジスタM2は導通状態となり、各列において配線OUTの端部に設けられているバイアストランジスタM3と共に、ソースフォロアアンプとして機能する。すなわち、トランジスタM2からのセンサ出力電圧VPIXは、積分期間におけるフォトダイオードD1の光電流の積分値に比例する。

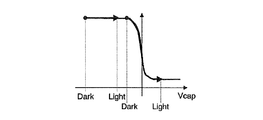

なお、図63において、実線で示した波形は、フォトダイオードD1に光の入射が少ない場合の電位VINTの変化を表し、破線で示した波形は、フォトダイオードD1に飽和レベルの光が入射した場合の電位VINTの変化を表している。図63のΔVSIGが、フォトダイオードD1へ入射した光の量に比例した電位差である。図63のΔVINTが、読み出し期間において、光センサに配線RWSから読み出し信号が印加されることによる、電位VINTの突き上げ量である。

上述のような、画素内に光センサを備えた表示装置においては、照度が異なる場合(例えば、暗状態の場合と飽和レベルの光が入射した場合)の蓄積期間終了時の蓄積ノードの電位の差が、それぞれの場合において読み出し期間に突き上げられた後の蓄積ノードの電位の差と等しい。つまり、暗状態の場合の蓄積期間終了時点の蓄積ノードの電位(ここではVINT1と称する)と、飽和レベルの光が入射した場合の蓄積期間終了時点の蓄積ノードの電位(ここではVINT2と称する)との電位差が、前記暗状態の場合の読み出し期間における突き上げ後の蓄積ノードの電位(ここではVINT3と称する)と、飽和レベルの光が入射した場合の読み出し期間における突き上げ後の蓄積ノードの電位(ここではVINT4と称する)との電位差に等しい。

しかし、上記のVINT3とVINT4との差が大きいほど、感度が高く、S/N比の高い、優れた特性の光センサを得ることができる。したがって、本発明は、積分期間終了時点における受光面の照度の差による蓄積ノードの電位差(VINT1−VINT2)よりも、突き上げ後の電位差(VINT3−VINT4)の方が大きくなるようにすることにより、感度が高い光センサを有する表示装置を提供することを目的とする。

上記の課題を解決するために、ここに開示する表示装置は、アクティブマトリクス基板の画素領域に光センサを備えた表示装置であって、前記光センサが、入射光を受光する光検出素子と、当該光センサへリセット信号を供給するリセット信号配線と、当該光センサへ読み出し信号を供給する読み出し信号配線と、前記リセット信号が供給されてから前記読み出し信号が供給されるまでの間をセンシング期間とし、センシング期間に前記光検出素子で受光された光量にしたがって電位が変化する蓄積ノードと、前記読み出し信号に応じて、前記蓄積ノードの電位を増幅する増幅素子と、前記増幅素子で増幅された電位をセンサ回路出力として出力配線へ読み出すためのセンサスイッチング素子とを備え、前記光検出素子に対してその受光面とは反対側に遮光膜が設けられ、前記遮光膜が、当該遮光膜を定電位に固定する電圧を供給する電源に接続され、前記定電位をVLS、前記リセット信号のハイレベル電位をVRST.Hとすると、

VLS ≧ VRST.H

が成り立つ構成である。

VLS ≧ VRST.H

が成り立つ構成である。

上記の構成によれば、読み出し信号に応じて蓄積ノードの電位を増幅する増幅素子を備えたことにより、積分期間終了時点における受光面の照度の差による蓄積ノードの電位差よりも、突き上げ後の電位差の方が大きくなる。例えば、暗状態の場合の蓄積期間終了時点の蓄積ノードの電位と、飽和レベルの光が入射した場合の蓄積期間終了時点の蓄積ノードの電位との電位差よりも、前記暗状態の場合の読み出し期間における突き上げ後の蓄積ノードの電位と、飽和レベルの光が入射した場合の読み出し期間における突き上げ後の蓄積ノードの電位との電位差の方が大きくなる。これにより、感度が高い光センサを有する表示装置を提供することができる。また、遮光膜の電位をリセット信号のハイレベル電位VRST.H以上の定電位に固定すれば、入射光量に対して線形性の高いセンサ出力を得ることが可能となる。

本発明の一実施形態にかかる表示装置は、アクティブマトリクス基板の画素領域に光センサを備えた表示装置であって、前記光センサが、入射光を受光する光検出素子と、当該光センサへリセット信号を供給するリセット信号配線と、当該光センサへ読み出し信号を供給する読み出し信号配線と、前記リセット信号が供給されてから前記読み出し信号が供給されるまでの間をセンシング期間とし、センシング期間に前記光検出素子で受光された光量にしたがって電位が変化する蓄積ノードと、前記読み出し信号に応じて、前記蓄積ノードの電位を増幅する増幅素子と、前記増幅素子で増幅された電位をセンサ回路出力として出力配線へ読み出すためのセンサスイッチング素子とを備えた構成である。

この構成によれば、読み出し信号に応じて蓄積ノードの電位を増幅する増幅素子を備えたことにより、積分期間終了時点における受光面の照度の差による蓄積ノードの電位差よりも、突き上げ後の電位差の方が大きくなる。例えば、暗状態の場合の蓄積期間終了時点の蓄積ノードの電位と、飽和レベルの光が入射した場合の蓄積期間終了時点の蓄積ノードの電位との電位差よりも、前記暗状態の場合の読み出し期間における突き上げ後の蓄積ノードの電位と、飽和レベルの光が入射した場合の読み出し期間における突き上げ後の蓄積ノードの電位との電位差の方が大きくなる。なお、この電位差の増幅機能は、暗状態の場合と飽和レベルの光が入射した場合とに限らず、任意の照度間で成立する。これにより、感度が高い光センサを有する表示装置を提供することができる。

また、上記の構成において、光検出素子に対してその受光面とは反対側に遮光膜が設けられ、前記遮光膜が、当該遮光膜を定電位に固定する電圧を供給する電源に接続され、前記定電位をVLS、前記リセット信号のハイレベル電位をVRST.Hとすると、

VLS ≧ VRST.H

が成り立つ構成であることが好ましい。この好ましい構成によれば、遮光膜の電位変動をなくすことができ、ダイオードD1の特性の劣化を抑制することができる。

VLS ≧ VRST.H

が成り立つ構成であることが好ましい。この好ましい構成によれば、遮光膜の電位変動をなくすことができ、ダイオードD1の特性の劣化を抑制することができる。

また、光検出素子としてPINダイオードを用いる場合、前記PINダイオードのpチャネル閾値電圧をVth_pとすると、

VLS ≧ VRST.H + Vth_p

が成り立つ構成とすることがさらに好ましい。この好ましい構成によれば、PINダイオードを、そのi層におけるp層側およびn層側の両方の界面において自由電子および正孔の移動が生じやすい状態で動作させることができるので、明電流(光電流)が大きく、かつ、照度変化に対する明電流(光電流)の変化の線形性を向上させることができる。

VLS ≧ VRST.H + Vth_p

が成り立つ構成とすることがさらに好ましい。この好ましい構成によれば、PINダイオードを、そのi層におけるp層側およびn層側の両方の界面において自由電子および正孔の移動が生じやすい状態で動作させることができるので、明電流(光電流)が大きく、かつ、照度変化に対する明電流(光電流)の変化の線形性を向上させることができる。

上記の表示装置において、前記増幅素子としては、例えば可変コンデンサを用いることができる。この場合、前記可変コンデンサとしては、例えば、前記読み出し信号配線と、絶縁膜と、シリコン膜に形成されたp型半導体領域とを含むMOSコンデンサを用いることができる。あるいは、前記可変コンデンサとしては、前記センサスイッチング素子のゲート電極と、絶縁膜と、シリコン膜に形成されたn型半導体領域とを含むMOSコンデンサを用いることができる。前者の構成によれば、前記読み出し信号配線を、当該可変コンデンサのゲート電極として用いることができるので、読み出し信号配線とゲート電極とを接続するための配線やコンタクトを設ける必要がないといった利点がある。

また、上記の表示装置において、前記増幅素子として、例えばpチャネル薄膜トランジスタを用いることもできる。この場合、pチャネル薄膜トランジスタにおいて、前記光検出素子と前記蓄積ノードとを接続するシリコン膜の幅広部にチャネル領域が形成され、前記幅広部にオーバーラップするように当該pチャネル薄膜トランジスタのゲート電極が設けられた構成とすることが好ましい。この構成によれば、境界長を短くすることができ、寄生容量やリーク電流によるダイナミックレンジの減少を防止できるからである。あるいは、上記の表示装置において、前記増幅素子として、nチャネル薄膜トランジスタを用いても良い。

あるいは、上記の表示装置において、前記増幅素子としてチャネル上にゲート電極を備えたダイオードを用いた構成とすることもできる。この構成によれば、境界長を短くすることができる。

また、上記の表示装置において、前記遮光膜と前記光検出素子との寄生容量に対して直列容量を形成するように、前記遮光膜に対向して設けられた電極とを備え、前記電極が前記読み出し配線に電気的に接続された構成とすることも好ましい。この構成によれば、遮光膜と光検出素子との間の寄生容量が積分期間における蓄積ノードの電位変化に与える影響を軽減することができるという効果がある。

また、上記の表示装置において、前記画素領域に複数の前記光検出素子を備え、前記複数の光検出素子が並列に接続され、前記複数の光検出素子の末端の光検出素子に前記増幅素子が接続された構成とすることが好ましい。このように、複数の光検出素子を並列に接続することにより、光電流を増加させることができ、感度を向上させることができる。

上記の表示装置において、前記センサスイッチング素子が三端子スイッチング素子であり、前記三端子のうちのゲート電極が前記蓄積ノードに接続され、前記三端子のうちの残りの二端子の一方が前記出力配線へ接続された構成とすることが好ましい。この構成によれば、センサスイッチング素子の数が一つで足りるので、光センサの回路構成を簡略化することができる。なお、上記の表示装置において、前記センサスイッチング素子のリセット用スイッチング素子をさらに備えた構成としても良い。

上記の表示装置において、前記増幅素子が、前記読み出し信号のローレベル電位とハイレベル電位との間に、当該増幅素子のオン/オフが切り替わる閾値電位を有することが好ましい。

また、上記の表示装置は、前記アクティブマトリクス基板に対向する対向基板と、前記アクティブマトリクス基板と対向基板との間に挟持された液晶とをさらに備えた液晶表示装置として実施することも可能である。

以下、本発明のより具体的な実施形態について、図面を参照しながら説明する。なお、以下の実施形態は、本発明にかかる表示装置を液晶表示装置として実施する場合の構成例を示したものであるが、本発明にかかる表示装置は液晶表示装置に限定されず、アクティブマトリクス基板を用いる任意の表示装置に適用可能である。なお、本発明にかかる表示装置は、光センサを有することにより、画面に近接する物体を検知して入力操作を行うタッチパネル付き表示装置や、表示機能と撮像機能とを具備した双方向通信用表示装置等としての利用が想定される。

また、以下で参照する各図は、説明の便宜上、本発明の実施形態の構成部材のうち、本発明を説明するために必要な主要部材のみを簡略化して示したものである。従って、本発明にかかる表示装置は、本明細書が参照する各図に示されていない任意の構成部材を備え得る。また、各図中の部材の寸法は、実際の構成部材の寸法および各部材の寸法比率等を忠実に表したものではない。

[第1の実施形態]

最初に、図1および図2を参照しながら、本発明の第1の実施形態にかかる液晶表示装置が備えるアクティブマトリクス基板の構成について説明する。

最初に、図1および図2を参照しながら、本発明の第1の実施形態にかかる液晶表示装置が備えるアクティブマトリクス基板の構成について説明する。

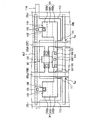

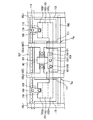

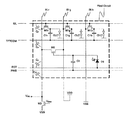

図1は、本発明の一実施形態にかかる液晶表示装置が備えるアクティブマトリクス基板100の概略構成を示すブロック図である。図1に示すように、アクティブマトリクス基板100は、ガラス基板上に、画素領域1、ディスプレイゲートドライバ2、ディスプレイソースドライバ3、センサカラム(column)ドライバ4、センサロウ(row)ドライバ5、バッファアンプ6、FPCコネクタ7を少なくとも備えている。また、画素領域1内の光検出素子(後述)で取り込まれた画像信号を処理するための信号処理回路8が、前記FPCコネクタ7とFPC9とを介して、アクティブマトリクス基板100に接続されている。

なお、アクティブマトリクス基板100上の上記の構成部材は、半導体プロセスによってガラス基板上にモノリシックに形成することも可能である。あるいは、上記の構成部材のうちのアンプやドライバ類を、例えばCOG(Chip On Glass)技術等によってガラス基板上に実装した構成としても良い。あるいは、図1においてアクティブマトリクス基板100上に示した上記の構成部材の少なくとも一部が、FPC9上に実装されることも考えられる。アクティブマトリクス基板100は、全面に対向電極が形成された対向基板(図示せず)と貼り合わされ、その間隙に液晶材料が封入される。

画素領域1は、画像を表示するために、複数の画素が形成された領域である。本実施形態では、画素領域1における各画素内には、画像を取り込むための光センサが設けられている。図2は、アクティブマトリクス基板100の画素領域1における画素と光センサとの配置を示す等価回路図である。図2の例では、1つの画素が、R(赤)、G(緑)、B(青)の3色の絵素によって形成され、この3絵素で構成される1つの画素内に、1つの光センサが設けられている。画素領域1は、M行×N列のマトリクス状に配置された画素と、同じくM行×N列のマトリクス状に配置された光センサとを有する。なお、上述のとおり、絵素数は、M×3Nである。

このため、図2に示すように、画素領域1は、画素用の配線として、マトリクス状に配置されたゲート線GLおよびソース線COLを有している。ゲート線GLは、ディスプレイゲートドライバ2に接続されている。ソース線COLは、ディスプレイソースドライバ3に接続されている。なお、ゲート線GLは、画素領域1内にM行設けられている。以下、個々のゲート線GLを区別して説明する必要がある場合は、GLi(i=1〜M)のように表記する。一方、ソース線COLは、上述のとおり、1つの画素内の3絵素にそれぞれ画像データを供給するために、1画素につき3本ずつ設けられている。ソース線COLを個々に区別して説明する必要がある場合は、COLrj,COLgj,COLbj(j=1〜N)のように表記する。

ゲート線GLとソース線COLとの交点には、画素用のスイッチング素子として、薄膜トランジスタ(TFT)M1が設けられている。なお、図2では、赤色、緑色、青色のそれぞれの絵素に設けられている薄膜トランジスタM1を、M1r,M1g,M1bと表記している。薄膜トランジスタM1のゲート電極はゲート線GLへ、ソース電極はソース線COLへ、ドレイン電極は図示しない画素電極へ、それぞれ接続されている。これにより、図2に示すように、薄膜トランジスタM1のドレイン電極と対向電極(VCOM)との間に液晶容量CLCが形成される。また、ドレイン電極とTFTCOMとの間に補助容量CLSが形成されている。

図2において、1本のゲート線GLiと1本のソース線COLrjとの交点に接続された薄膜トランジスタM1rによって駆動される絵素は、この絵素に対応するように赤色のカラーフィルタが設けられ、ソース線COLrjを介してディスプレイソースドライバ3から赤色の画像データが供給されることにより、赤色の絵素として機能する。また、ゲート線GLiとソース線COLgjとの交点に接続された薄膜トランジスタM1gによって駆動される絵素は、この絵素に対応するように緑色のカラーフィルタが設けられ、ソース線COLgjを介してディスプレイソースドライバ3から緑色の画像データが供給されることにより、緑色の絵素として機能する。さらに、ゲート線GLiとソース線COLbjとの交点に接続された薄膜トランジスタM1bによって駆動される絵素は、この絵素に対応するように青色のカラーフィルタが設けられ、ソース線COLbjを介してディスプレイソースドライバ3から青色の画像データが供給されることにより、青色の絵素として機能する。

なお、図2の例では、光センサは、画素領域1において、1画素(3絵素)に1つの割合で設けられている。ただし、画素と光センサの配置割合は、この例のみに限定されず、任意である。例えば、1絵素につき1つの光センサが配置されていても良いし、複数画素に対して1つの光センサが配置された構成であっても良い。

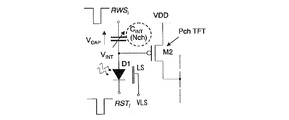

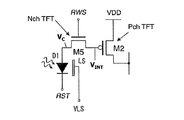

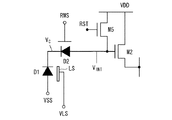

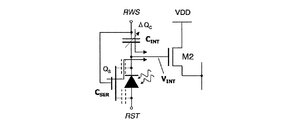

光センサは、図2に示すように、光検出素子としてのフォトダイオードD1、コンデンサC1(増幅素子)、トランジスタM2から構成される。本実施形態において増幅素子として機能するコンデンサC1は、可変コンデンサである。

図2の例では、ソース線COLrが、センサカラムドライバ4から定電圧VDDを光センサへ供給するための配線VDDを兼ねている。また、ソース線COLgが、センサ出力用の配線OUTを兼ねている。

フォトダイオードD1のアノードには、リセット信号を供給するための配線RSTが接続されている。フォトダイオードD1のカソードには、コンデンサC1の電極の一方と、トランジスタM2のゲートが接続されている。トランジスタM2のドレインは配線VDDに接続され、ソースは配線OUTに接続されている。図2において、フォトダイオードD1のカソードと、コンデンサC1の電極の一方と、トランジスタM2のゲートとの接続点(蓄積ノード)をINTと表記した。コンデンサC1の電極の他方は、読み出し信号を供給するための配線RWSに接続されている。配線RST,RWSは、センサロウドライバ5に接続されている。これらの配線RST,RWSは1行毎に設けられているので、以降、各配線を区別する必要がある場合は、RSTi,RWSi(i=1〜M)のように表記する。

センサロウドライバ5は、所定の時間間隔trowで、図2に示した配線RSTiとRWSiとの組を順次選択していく。これにより、画素領域1において信号電荷を読み出すべき光センサの行(row)が順次選択される。

なお、図2に示すように、配線OUTの端部には、絶縁ゲート型電界効果トランジスタM3のドレインが接続されている。また、このトランジスタM3のドレインには、出力配線SOUTが接続され、トランジスタM3のドレインの電位VSOUTが、光センサからの出力信号としてセンサカラムドライバ4へ出力される。トランジスタM3のソースは、配線VSSに接続されている。トランジスタM3のゲートは、参照電圧配線VBを介して、参照電圧電源(図示せず)に接続されている。

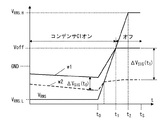

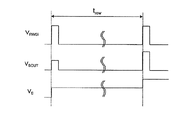

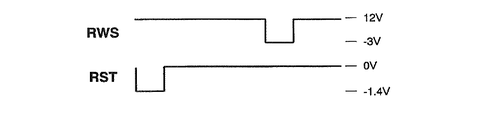

図3は、コンデンサC1のCV特性図である。図3において、横軸はコンデンサC1の電極間電圧VCAP、縦軸は静電容量を表す。図3に示すように、コンデンサC1は、電極間電圧VCAPが小さい間は一定の静電容量を有するが、電極間電圧VCAPの閾値の前後で静電容量が急峻に変化する特性を有する。したがって、配線RWSからの読み出し信号の電位によって、コンデンサC1の特性を動的に変化させることができる。このような特性を有するコンデンサC1を用いることにより、本実施形態にかかる光センサは、図4に示すように、積分期間TINTにおける蓄積ノードの電位変化を増幅して読み出すことができる。図4の例は、あくまでも一実施形態であるが、リセット信号のローレベル電位VRST.Lが−1.4Vであり、リセット信号のハイレベル電位VRST.Hが0Vである。また、読み出し信号のローレベル電位VRWS.Lが−3V、読み出し信号のハイレベル電位VRWS.Hが12Vである。図4においても、実線で示した波形は、フォトダイオードD1に光の入射が少ない場合の電位VINTの変化を表し、破線で示した波形は、フォトダイオードD1に飽和レベルの光が入射した場合の電位VINTの変化を表し、ΔVSIGがフォトダイオードD1へ入射した光の量に比例した電位差である。図63に示した従来例と、図4とを比較することから明らかなように、本実施形態にかかる光センサでは、飽和レベルの光が入射した場合の積分期間TINTにおける蓄積ノードの電位変化が、従来の光センサよりも小さいが、読み出し期間において(読み出し信号の電位がハイレベル電位VRWS.Hである間)、この蓄積ノードの電位が増幅して読み出されている。

ここで、図4を参照し、画素領域1からのセンサ出力の読み出しについて説明する。まず、センサロウドライバ5から配線RSTへ供給されるリセット信号がローレベル(VRST.L)から立ち上がってハイレベル(VRST.H)になると、フォトダイオードD1は順方向バイアスとなり、接続点INTの電位VINTは、下記の式(4)で表される。

VINT = VRST.H−VF ・・・(4)

式(4)において、VFはフォトダイオードD1の順方向電圧である。このときのVINTはトランジスタM2の閾値電圧より低いので、トランジスタM2はリセット期間において非導通状態となっている。

式(4)において、VFはフォトダイオードD1の順方向電圧である。このときのVINTはトランジスタM2の閾値電圧より低いので、トランジスタM2はリセット期間において非導通状態となっている。

次に、リセット信号がローレベル電位VRST.Lに戻ると、光電流の積分期間(TINT)が始まる。積分期間TINTにおいては、フォトダイオードD1への入射光量に比例した光電流がコンデンサC1に流れ込み、コンデンサC1を放電させる。これにより、積分期間TINTの終了時における接続点INTの電位VINTは、下記の式(5)で表される。

VINT=VRST.H−VF−ΔVRST・CPD/CTOTAL

−IPHOTO・tINT/CTOTAL …(5)

式(5)において、ΔVRSTは、リセット信号のパルスの高さ(VRST.H−VRST.L)であり、IPHOTOは、フォトダイオードD1の光電流、tINTは、積分期間の長さである。CPDはフォトダイオードD1の容量である。CTOTALは、光センサ回路全体の容量、すなわち、接続点INTの総容量であり、コンデンサC1の容量CINTと、フォトダイオードD1の容量CPDと、トランジスタM2の容量CTFTとの総和である。積分期間においても、VINTがトランジスタM2の閾値電圧より低いので、トランジスタM2は非導通状態となっている。

−IPHOTO・tINT/CTOTAL …(5)

式(5)において、ΔVRSTは、リセット信号のパルスの高さ(VRST.H−VRST.L)であり、IPHOTOは、フォトダイオードD1の光電流、tINTは、積分期間の長さである。CPDはフォトダイオードD1の容量である。CTOTALは、光センサ回路全体の容量、すなわち、接続点INTの総容量であり、コンデンサC1の容量CINTと、フォトダイオードD1の容量CPDと、トランジスタM2の容量CTFTとの総和である。積分期間においても、VINTがトランジスタM2の閾値電圧より低いので、トランジスタM2は非導通状態となっている。

積分期間が終わると、配線RWSへ供給される読み出し信号が立ち上がることにより、読み出し期間が始まる。ここで、コンデンサC1に対して電荷注入が起こる。そして、接続点INTの電位VINTがトランジスタM2の閾値電圧よりも高くなったとき、トランジスタM2は導通状態となり、各列において配線OUTの端部に設けられているバイアストランジスタM3と共に、ソースフォロアアンプとして機能する。本実施形態にかかる光センサにおいては、トランジスタM3のドレインからの出力配線SOUTからの出力信号電圧は、積分期間におけるフォトダイオードD1の光電流の積分値を増幅したものに相当する。その原理については、後述する。

以上のとおり、本実施形態においては、リセットパルスによる初期化と、積分期間における光電流の積分と、読み出し期間におけるセンサ出力の読み出しとを1サイクルとして周期的に行う。

以下、本実施形態にかかる光センサの具体的な構造について、図面を参照しながら説明する。図5は、本実施形態にかかる光センサの等価回路図である。図6は、本実施形態にかかる光センサの平面構造の一例を示す平面図である。図7は、コンデンサC1が形成されている領域の拡大図である。図8は、本実施形態にかかる光センサにおける各領域の接続関係を示した断面模式図である。

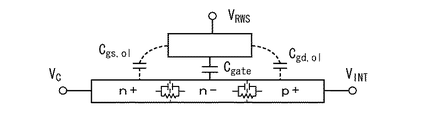

図5に示すように、本実施形態にかかる光センサは、可変コンデンサであるコンデンサC1を増幅素子として備えている。本実施形態においては、コンデンサC1は、pチャネルMOSコンデンサである。なお、図6においては、ソース線COLgとCOLbとの間の領域にトランジスタM2を設け、その両側に、コンデンサC1とダイオードD1の組を1つずつ設けているが、コンデンサC1とダイオードD1とが1組だけ設けられた構成であっても良い。ダイオードD1の背面には、バックライト光が入射することを防止するための遮光膜LSが設けられている。遮光膜LSは、少なくとも光センサの動作中、定電位VLSに固定される。

このように、遮光膜LSを定電位VLSに固定することにより、フォトダイオードの信頼性を向上させることができる。遮光膜LSの電位がフローティングである場合、キャリアの移動や注入などにより、遮光膜LSが初期の電位から変動し、ダイオードD1の特性が変動劣化する可能性があるが、遮光膜LSを定電位VLSに固定することにより、この問題を解決することができる。

また、複数のダイオードD1間での特性のばらつきを低減することができる。なぜなら、遮光膜LSの電位がフローティングである場合、プロセス工程でのプラズマイオンなどのチャージアップが均一でないことにより、遮光膜LSのフローティング電位にばらつきが発生する可能性がある。これに対して、遮光膜LSを定電位VLSに固定することにより、この問題を解決することができる。

また、表示用の各種信号との干渉ノイズを低減することができる。なぜなら、遮光膜LSはソース線COLや画素電極と容量結合しているので、遮光膜LSの電位がフローティングの場合、表示用の各種信号の電位変動(ソース線電位や画素電極電位)により、遮光膜LSの電位が影響を受ける。この遮光膜LSの電位の変動が、さらに、光センサにノイズを与えることになる。これに対して、遮光膜LSを定電位VLSに固定することにより、遮光膜LSの電位変動をなくすことができ、この問題を解決することができる。

なお、遮光膜LSの定電位をVLS、リセット信号のハイレベル電位をVRST.Hとすると、

VLS ≧ VRST.H

の関係が成り立つことが好ましい。また、ダイオードD1のpチャネル閾値電圧をVth_pとすると、

VLS ≧ VRST.H + Vth_p

の関係が成り立つことがさらに好ましい。この理由については、後に詳しく説明する。

VLS ≧ VRST.H

の関係が成り立つことが好ましい。また、ダイオードD1のpチャネル閾値電圧をVth_pとすると、

VLS ≧ VRST.H + Vth_p

の関係が成り立つことがさらに好ましい。この理由については、後に詳しく説明する。

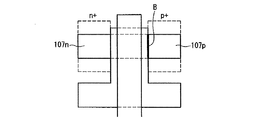

図6に示すように、本実施形態にかかる光センサは、ソース線COLgとCOLbとの間の領域にトランジスタM2を備えている。ダイオードD1は、ベースとなるシリコン膜に、p型半導体領域102pと、i型半導体領域102iと、n型半導体領域102nとが直列に形成された、ラテラル構造のPINダイオードである。p型半導体領域102pは、ダイオードD1のアノードとなり、配線108およびコンタクト109,110を介して配線RSTに接続される。n型半導体領域102nは、ダイオードD1のカソードとなり、シリコン膜の延設部107,コンタクト105,106、および配線104を介して、トランジスタM2のゲート電極101に接続される。

この構成において、配線RST,RWSは、トランジスタM2のゲート電極101と同じ金属により同じ工程で形成されている。また、配線104,108は、ソース線COLと同じ金属により同じ工程で形成されている。ダイオードD1の背面には、遮光膜LS(図5参照)として機能する金属膜113が設けられている。前述のとおり、遮光膜LSとしての金属膜113の電位は定電位VLSに固定される。このため、金属膜113は、配線114に接続されている。配線114は、画素領域1の外部において、定電圧電源(図示せず)に接続されている。なお、図6においては、遮光膜LSとして機能する金属膜113へ定電位VLSを供給するための配線114が、リセット配線RSTに平行に設けられている構成を例示したが、配線114の態様はこの具体例のみに限定されない。

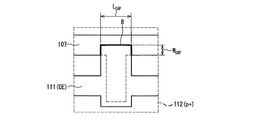

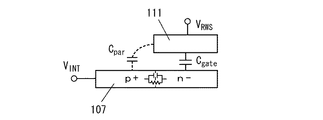

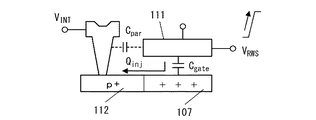

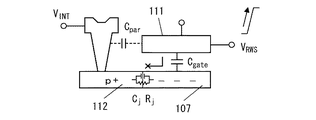

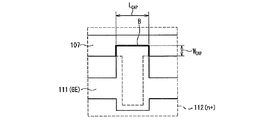

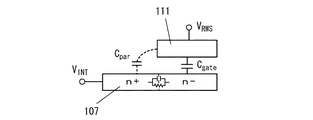

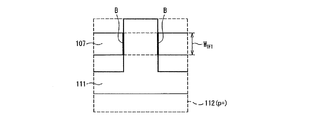

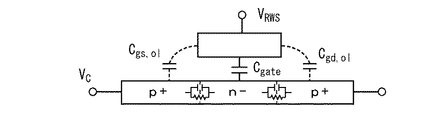

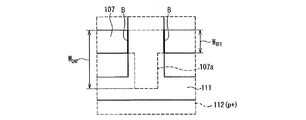

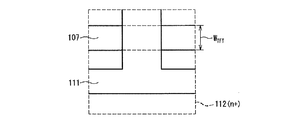

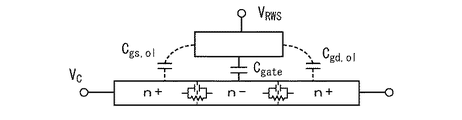

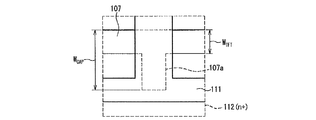

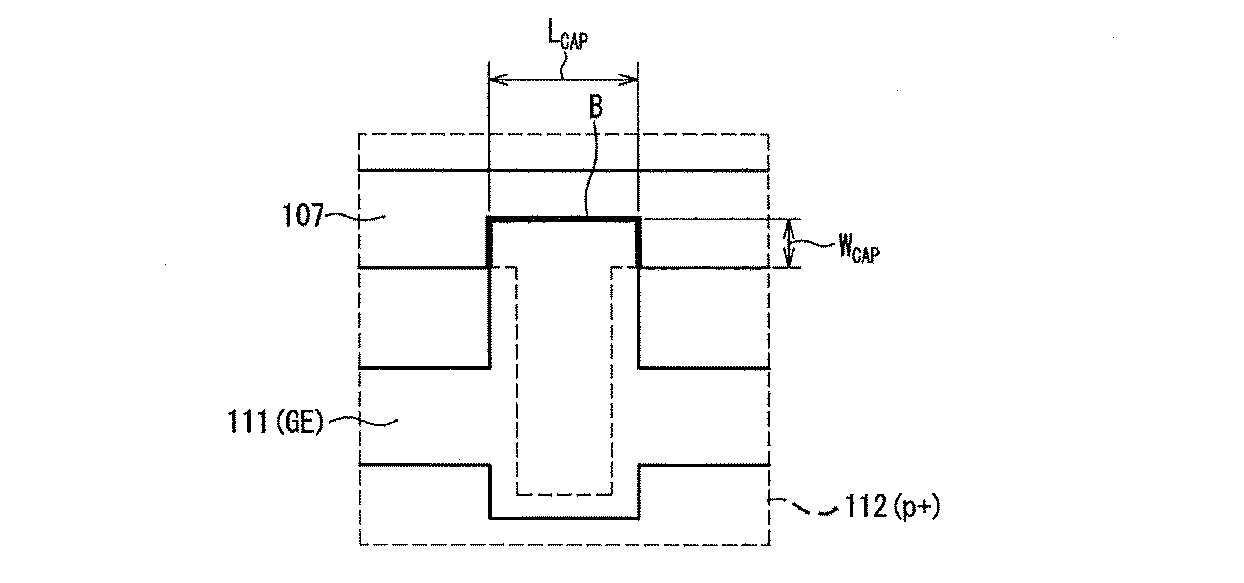

また、図6〜図8に示すように、配線RWSに形成された幅広部111と、シリコン膜の延設部107と、その間に配置された絶縁膜(図示せず)とによって、コンデンサC1が形成されている。つまり、配線RWSと同電位である幅広部111が、コンデンサC1のゲート電極として機能する。図7に示す領域112は、n型シリコン膜に対して例えばボロン等のp型不純物をドープして形成されたp+領域である。なお、p型不純物のドープの際に幅広部111がマスクとして機能するので、図8に示すように、延設部107はp+領域となり、幅広部111の下方にあるシリコン膜はn−領域を形成する。

ここで、本実施形態にかかる光センサの読み出し動作について説明する。図9は、積分期間の最後から読み出し期間にかけての蓄積ノードの電位VINTの変化を示す波形図である。図9において、実線で示した波形w1は、フォトダイオードD1に光の入射が少ない場合の電位VINTの変化を表し、破線で示した波形w2は、フォトダイオードD1に光が入射した場合の電位VINTの変化を表している。また、時刻t0は、配線RWSから供給される読み出し信号がローレベル電位VRWS.Lからの立ち上がりを開始する時刻であり、時刻t2は、読み出し信号がハイレベル電位VRWS.Hへ到達する時刻である。時刻tSは、トランジスタM2がオンになってセンサ出力のサンプリングが行われる時刻である。時刻t1は、読み出し信号がコンデンサC1の閾値電圧Voffに到達する時刻である。すなわち、コンデンサC1は、読み出し配線RWSから幅広部111へ供給される電位と閾値電圧Voffとの大小関係によって、その動作特性が変わる。

図10Aおよび図10Bは、コンデンサC1におけるゲート電極(幅広部111)の電位による電荷の移動の違いを示す断面模式図である。図9、図10A、および図10Bに示すように、時刻t1よりも前の時刻においては、コンデンサC1は常にオン状態であり、時刻t1以降はオフ状態となる。すなわち、配線RWSの電位が閾値電圧Voff以下の間は、図10Aに示すようにゲート電極(幅広部111)下の電荷Qinjの移動が生じるが、配線RWSの電位が閾値電圧Voffを超えると、図10Bに示すようにゲート電極(幅広部111)下の電荷Qinjの移動がなくなる。以上より、読み出し配線RWSから供給される読み出し信号の電位がハイレベル電位VRWS.Hへ到達した後のサンプル時刻tSにおける蓄積ノードの電位VINT(tS)は、下記の式(6)に示すとおりである。なお、図4に示したΔVINTは、VINT(t0)とVINT(tS)との差分に相当し、Qinj/CINTに等しい。

図9に示したように、本実施形態にかかる光センサによれば、積分期間の終期におけるける受光面の照度の差による蓄積ノードの電位差よりも、突き上げ後の電位差の方が大きくなる。例えば、暗状態の場合の蓄積期間終了時点の蓄積ノードの電位と、飽和レベルの光が入射した場合の蓄積期間終了時点の蓄積ノードの電位との電位差よりも、前記暗状態の場合の読み出し期間における突き上げ後の蓄積ノードの電位と、飽和レベルの光が入射した場合の読み出し期間における突き上げ後の蓄積ノードの電位との電位差の方が大きくなる。したがって、感度が高く、かつS/N比も高い光センサを実現することができる。

ここで、図11〜図13を参照しながら、本実施形態にかかる光センサの利点について説明する。前述のように、本実施形態にかかる光センサでは、フォトダイオードD1の受光面の反対側に、バックライト光の入射を防止する遮光膜LS(図5参照)が設けられ、その電位が定電位VLSに固定されている。また、定電位VLSは、リセット信号のハイレベル電位をVRST.Hと、ダイオードD1のpチャネル閾値電圧をVth_pとの間で、

VLS ≧ VRST.H + Vth_p

との関係を満たす。遮光膜LSの定電位VLSをこのように設定することにより、低照度領域におけるフォトダイオードD1の線形性を向上させることができる。その理論を以下に説明する。

VLS ≧ VRST.H + Vth_p

との関係を満たす。遮光膜LSの定電位VLSをこのように設定することにより、低照度領域におけるフォトダイオードD1の線形性を向上させることができる。その理論を以下に説明する。

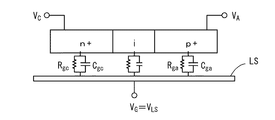

図11は、ラテラル構造のPINダイオードの断面模式図である。図11に示すとおり、本実施形態にかかる光センサのように、ラテラル構造のPINダイオードの近傍に遮光膜LSが設けられた場合、この遮光膜LSとの間に生ずる寄生容量により、ダイオードは三端子素子として機能する。すなわち、遮光膜LSがゲート、p層がアノード、n層がカソードとなり、ゲートすなわち遮光膜LSの電位VLSと、アノード電位VAと、カソード電位VCとの関係によって、互いに異なる3つの動作モードを呈する。

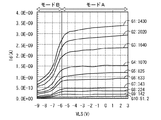

図12Aおよび図12Bは、上記の3つの動作モードの違いを表すId−VLS特性図である。なお、Idは、ダイオードの明電流である。なお、明電流は、ダイオードに光が入射した際に光量に応じて生じる電流であり、光電流とも呼ばれる。図12Aは、アノード電位VAを−7V、カソード電位VCを0Vとした場合の、遮光膜LSの電位VLSと明電流Idとの関係を示すグラフである。図12Aの例では、VLSの値がVA+Vth_pの点を境界として、遮光膜LSの電位VLSに対する明電流Idのふるまいが変化する。ここで、VLS≦VA+Vth_pの領域における動作モードを「モードB」、VLS≧VA+Vth_pの領域における動作モードを「モードA」と称することとする。

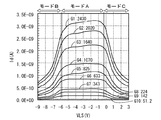

また、図12Bは、アノード電位VAを−7V、カソード電位VCを−3Vとした場合の、遮光膜LSの電位VLSと明電流Idとの関係を示すグラフである。図12Bの例では、VLSの値がVA+Vth_pの点を境界として、遮光膜LSの電位VLSに対する明電流Idのふるまいが変化すると共に、VLSの値がVC+Vth_nの点を境界として、遮光膜LSの電位VLSに対する明電流Idのふるまいが変化する。ここで、上記と同様に、VLS≦VA+Vth_pの領域における動作モードを「モードB」と称し、VA+Vth_p≦VLS≦VC+Vth_nの領域における動作モードを「モードA」、VC+Vth_n≦VLSの領域における動作モードを「モードC」と称することとする。

図12Aおよび図12Bから明らかなように、モードAにおいては、高い明電流Idが安定して得られ、かつ、照度に対する明電流値の線形性が良い。したがって、本実施形態においても、ダイオードD1はモードAで動作することが好ましい。すなわち、VA+Vth_p≦VLS≦VC+Vth_nの場合(モードA)においては、ダイオードのi層におけるp層側およびn層側の両方の界面において、自由電子および正孔の移動が生じやすい状態となる。これにより、モードAにおいては、フォト電流がダイオード内をスムーズに流れ、かつ、暗電流は低下する傾向があるので、良好なS/N比が得られると共に、照度に対する明電流の線形性が向上する。

一方、VLS≦VA+Vth_pの場合(モードB)においては、ダイオードのi層におけるn層側の界面では自由電子および正孔の移動が生じやすい状態となっているが、p層側の界面では電流の流れがi層によって妨げられる。その逆に、VC+Vth_n≦VLSの場合(モードC)においては、ダイオードのi層におけるp層側の界面では自由電子および正孔の移動が生じやすい状態となっているが、n層側の界面では電流の流れがi層によって妨げられる。したがって、モードB,Cの場合は、フォト電流がダイオード内をスムーズに流れることができず、また、暗電流が増加する傾向があるので、良好なS/N比が得られない。

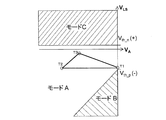

ここで、モードA,B,Cの分布を、アノード電位VAと遮光膜LSの電位VLSとの関係で表すと、図13のようになる。図13において、ハッチングが付されていない領域がモードA、右下がりのハッチングが付された領域がモードB、左下がりのハッチングが付された領域がモードCである。上述のとおり、モードAの領域は、

VA+Vth_p≦VLS≦VC+Vth_n

モードBの領域は、

VLS≦VA+Vth_p

モードCの領域は、

VC+Vth_n≦VLS

と表すことができる。

VA+Vth_p≦VLS≦VC+Vth_n

モードBの領域は、

VLS≦VA+Vth_p

モードCの領域は、

VC+Vth_n≦VLS

と表すことができる。

図13中に示されたT1,T2,T3のうち、T1は、図4に示したリセット信号がハイレベルとなった時刻のVLSとVAとを表す座標である。T2は、図4に示した時刻tRST(すなわちリセット信号がハイレベルからローレベルへ切り替わった時刻)に対応し、T3は、図4に示した時刻tRWS(すなわち読み出し信号がローレベルからハイレベルへ切り替わった時刻)に対応する。

ここで、T1,T2,T3を結ぶ線で形成される三角形が、モードAの領域に収まっていることが好ましい。したがって、まず、T1におけるVLSの値がモードBの領域に入らず、モードAの領域内にあるための条件として、

VLS≧VA+Vth_p

が満たされていることが好ましい。なお、リセット開始時のアノード電位VAはリセット信号のハイレベル電位VRST.Hに等しいので、上記の式は、

VLS≧VRST.H+Vth_p

と表現することができる。

VLS≧VA+Vth_p

が満たされていることが好ましい。なお、リセット開始時のアノード電位VAはリセット信号のハイレベル電位VRST.Hに等しいので、上記の式は、

VLS≧VRST.H+Vth_p

と表現することができる。

なお、T1〜T2の間はVLSの値は変化しない。そして、図4に示した時刻tRSTにおいてリセット信号がローレベルへ切り替わった時点から、蓄積期間が始まる(図13のT2)。そして、図4に示した時刻tRWSにおいて読み出し信号がハイレベルへ切り替わった時点(図13のT3)まで、受光した光量に応じたフォト電流が流れ続け、VLSの値は上昇する。T3において読み出し信号がハイレベルへ切り替わった後は、VLSの値は初期状態(T1)へ戻る。

なお、本実施形態においては、コンデンサC1として可変コンデンサを用いていることにより、通常の(可変でない)コンデンサを使用する場合と比較して、蓄積期間中のカソード電位VCの変動が抑制されている。したがって、蓄積期間(図13のT2〜T3)においてVLSがあまり上昇せず、モードAの領域内で動作させることが可能となる。

なお、T3においてダイオードD1がモードCの領域で動作しないようにするためには、コンデンサC1の増幅率AACが、

AAC≧VDD/(Vth_n−Vth_p)

の関係を満たすことが望ましい。ここで、VDDは、出力トランジスタM2の電源電圧である。この関係が満たされれば、蓄積ノード電位Vintの可動範囲であるΔVth=Vth_n−Vth_pを、出力電圧範囲0V〜VDDに対応させることができる。

AAC≧VDD/(Vth_n−Vth_p)

の関係を満たすことが望ましい。ここで、VDDは、出力トランジスタM2の電源電圧である。この関係が満たされれば、蓄積ノード電位Vintの可動範囲であるΔVth=Vth_n−Vth_pを、出力電圧範囲0V〜VDDに対応させることができる。

以上のとおり、遮光膜LSの電位VLSの値を、

VLS≧VRST.H+Vth_p

が満たされるように定電位に設定することにより、リセット開始から蓄積期間の少なくとも初期において、フォトダイオードD1をモードAで動作させることができる。なお、仮に、リセット開始近傍においてダイオードがモードBで動作した場合には、図12Aおよび図12Bに示したように、特に低照度領域における線形性が劣化するという現象が見られる。しかし、ここで説明したように、リセット開始後からダイオードをモードAで動作させることにより、リセット開始後から蓄積期間の初期においても、S/N比が高く、かつ、照度変化に対する線形性が高い、センサ出力値を得ることができる。

VLS≧VRST.H+Vth_p

が満たされるように定電位に設定することにより、リセット開始から蓄積期間の少なくとも初期において、フォトダイオードD1をモードAで動作させることができる。なお、仮に、リセット開始近傍においてダイオードがモードBで動作した場合には、図12Aおよび図12Bに示したように、特に低照度領域における線形性が劣化するという現象が見られる。しかし、ここで説明したように、リセット開始後からダイオードをモードAで動作させることにより、リセット開始後から蓄積期間の初期においても、S/N比が高く、かつ、照度変化に対する線形性が高い、センサ出力値を得ることができる。

なお、遮光膜LSの電位を、

VLS≧VRST.H+Vth_p

を満たす定電位VLSに設定することが最も好ましいが、定電位VLSが、

VLS≧VRST.H

を満たす値であっても、ダイオードD1の特性を改善する上では効果が得られる。また、仮に定電位VLSが、

VLS≧VRST.H

を満たさない値であっても、遮光膜LSの電位がフローティングである場合よりは、ダイオードD1の特性を改善する上では効果が得られる。

VLS≧VRST.H+Vth_p

を満たす定電位VLSに設定することが最も好ましいが、定電位VLSが、

VLS≧VRST.H

を満たす値であっても、ダイオードD1の特性を改善する上では効果が得られる。また、仮に定電位VLSが、

VLS≧VRST.H

を満たさない値であっても、遮光膜LSの電位がフローティングである場合よりは、ダイオードD1の特性を改善する上では効果が得られる。

なお、本実施形態では、前述したように、ソース線COLr,COLg,COLbを光センサ用の配線VDD,OUT,VSSとして共用しているので、図14に示すように、ソース線COLr,COLg,COLbを介して表示用の画像データ信号を入力するタイミングと、センサ出力を読み出すタイミングとを区別する必要がある。図14の例では、水平走査期間において表示用画像データ信号の入力が終わった後に、水平ブランキング期間等を利用して、センサ出力の読み出しが行われる。

センサカラムドライバ4は、図1に示したように、センサ画素読み出し回路41と、センサカラムアンプ42と、センサカラム走査回路43とを含む。センサ画素読み出し回路41には、画素領域1からセンサ出力VSOUTを出力する配線SOUT(図2参照)が接続されている。図1において、配線SOUTj(j=1〜N)により出力されるセンサ出力を、VSOUTjと表記している。センサ画素読み出し回路41は、センサ出力VSOUTjのピークホールド電圧VSjを、センサカラムアンプ42へ出力する。センサカラムアンプ42は、画素領域1のN列の光センサにそれぞれ対応するN個のカラムアンプを内蔵しており、個々のカラムアンプでピークホールド電圧VSj(j=1〜N)を増幅し、VCOUTとしてバッファアンプ6へ出力する。センサカラム走査回路43は、センサカラムアンプ42のカラムアンプをバッファアンプ6への出力へ順次接続するために、カラムセレクト信号CSj(j=1〜N)を、センサカラムアンプ42へ出力する。

ここで、図15および図16を参照し、画素領域1からセンサ出力VSOUTが読み出された後のセンサカラムドライバ4およびバッファアンプ6の動作について説明する。図15は、センサ画素読み出し回路41の内部構成を示す回路図である。図16は、読み出し信号VRWSと、センサ出力VSOUTと、センサ画素読み出し回路の出力VSとの関係を示す波形図である。前述のように、読み出し信号がハイレベル電位VRWS.Hになったとき、トランジスタM2が導通することにより、トランジスタM2,M3によりソースフォロアアンプが形成され、センサ出力VSOUTがセンサ画素読み出し回路41のサンプルキャパシタCSAMに蓄積される。これにより、読み出し信号がローレベル電位VRWS.Lになった後も、その行の選択期間(trow)中、センサ画素読み出し回路41からセンサカラムアンプ42への出力電圧VSは、図16に示すように、センサ出力VSOUTのピーク値と等しいレベルに保持される。

次に、センサカラムアンプ42の動作について、図17を参照しながら説明する。図17に示すように、センサ画素読み出し回路41から、各列の出力電圧VSj(j=1〜N)が、センサカラムアンプ42のN個のカラムアンプへ入力される。図17に示すように、各カラムアンプは、トランジスタM6,M7から構成されている。センサカラム走査回路43によって生成されるカラムセレクト信号CSjが、1つの行の選択期間(trow)中に、N列のカラムのそれぞれに対して順次ONとなることにより、センサカラムアンプ42中のN個のカラムアンプのうちいずれか1つのみのトランジスタM6がONとなり、そのトランジスタM6を介して、各列の出力電圧VSj(j=1〜N)のいずれかのみが、センサカラムアンプ42からの出力VCOUTとして出力される。バッファアンプ6は、センサカラムアンプ42から出力されたVCOUTをさらに増幅し、パネル出力(光センサ信号)VOUTとして信号処理回路8へ出力する。

なお、センサカラム走査回路43は、上述のように光センサの列を1列ずつ走査するようにしても良いが、これに限定されず、光センサの列をインタレース走査する構成としても良い。また、センサカラム走査回路43が、例えば4相等の多相駆動走査回路として形成されていても良い。

以上の構成により、本実施形態にかかる表示装置は、画素領域1において画素毎に形成されたフォトダイオードD1の受光量に応じたパネル出力VOUTを得る。パネル出力VOUTは、信号処理回路8に送られてA/D変換され、パネル出力データとしてメモリ(図示せず)に蓄積される。つまり、このメモリには、画素領域1の画素数(光センサ数)と同数のパネル出力データが蓄積されることとなる。信号処理回路8では、メモリに蓄積されたパネル出力データを用いて、画像取り込みやタッチ領域の検出等の各種信号処理を行う。なお、本実施形態では、信号処理回路8のメモリに、画素領域1の画素数(光センサ数)と同数のパネル出力データを蓄積するものとしたが、メモリ容量等の制約により、必ずしも画素数と同数のパネル出力データを蓄積することを要しない。

なお、第1の実施形態にかかる構成は、配線RWSの幅広部111がコンデンサC1のゲート電極を兼ねているので、例えば後述する第3の実施形態よりもコンタクト(第3の実施形態において図24に示すコンタクト118,119)が少なくて済み、光センサ回路を小型化できるという利点がある。また、第1の実施形態にかかる構成では、配線RWSの幅広部111が、蓄積ノードINTをソース線COLからシールドする配置となっている。したがって、例えば後述する第3の実施形態のように、蓄積ノードINTの上層にソース線COLが配置される構成と比較して、蓄積ノードINTに対するソース線COLからのノイズ干渉を抑制できるという利点もある。

[第2の実施形態]

以下、本発明の第2の実施形態について説明する。第1の実施形態において説明した構成と同様の機能を有する構成については、第1の実施形態と同じ参照符号を付記し、その詳細な説明を省略する。

以下、本発明の第2の実施形態について説明する。第1の実施形態において説明した構成と同様の機能を有する構成については、第1の実施形態と同じ参照符号を付記し、その詳細な説明を省略する。

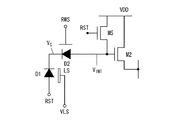

図18は、本実施形態にかかる光センサの等価回路図である。図19は、本実施形態にかかる光センサに供給されるリセット信号と読み出し信号の波形図である。図20は、本実施形態にかかる光センサの平面構造の一例を示す平面図である。図21は、コンデンサC1が形成されている領域の拡大図である。図22は、本実施形態にかかる光センサにおける各領域の接続関係を示した断面模式図である。

図18に示すように、本実施形態にかかる光センサは、コンデンサC1がnチャネルMOSコンデンサである点において、第1の実施形態と異なっている。また、ダイオードD1が第1の実施形態とは逆向きに接続されている。すなわち、ダイオードD1のカソードが配線RSTに接続され、アノードが蓄積ノードINTに接続されている。さらに、読み出し用のトランジスタM2が、pチャネルTFTである。また、図19に示すように、リセット信号と読み出し信号のハイレベルとローレベルの電位が、第1の実施形態とは逆である。

図20に示すように、ダイオードD1は、第1の実施形態と同様に、ベースとなるシリコン膜に、p型半導体領域102pと、i型半導体領域102iと、n型半導体領域102nとが直列に形成された、ラテラル構造のPINダイオードである。ただし、n型半導体領域102n(カソード)が、配線108およびコンタクト109,110を介して配線RSTに接続される。また、p型半導体領域102p(アノード)が、シリコン膜の延設部107,コンタクト105,106、および配線104を介して、トランジスタM2のゲート電極101に接続される。

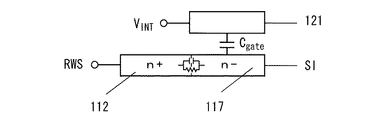

図21および図22に示すように、配線RWSに形成された幅広部111と、シリコン膜の延設部107と、その間に配置された絶縁膜(図示せず)とによって、コンデンサC1が形成されている。つまり、配線RWSと同電位である幅広部111が、コンデンサC1のゲート電極として機能する。本実施形態においては、図21に示す領域112は、n型シリコン膜に対して例えばリン等のn型不純物をドープして形成されたn+領域である。なお、n型不純物のドープの際に幅広部111がマスクとして機能するので、図22に示すように、延設部107はn+領域となり、幅広部111の下方にあるシリコン膜はn−領域を形成する。

以上の構成にかかる本実施形態の光センサにおいては、第1の実施形態と電位関係が逆になるので、積分期間および読み出し期間における蓄積ノードINTの電位変化は、第1の実施形態で示した図9を上下方向に逆にしたとおりとなる。したがって、本実施形態の光センサによっても、積分期間終了時点における受光面の照度の差による蓄積ノードの電位差よりも、突き上げ後の電位差の方が大きくなる。例えば、暗状態の場合の蓄積期間終了時点の蓄積ノードの電位と、飽和レベルの光が入射した場合の蓄積期間終了時点の蓄積ノードの電位との電位差よりも、前記暗状態の場合の読み出し期間における突き上げ後の蓄積ノードの電位と、飽和レベルの光が入射した場合の読み出し期間における突き上げ後の蓄積ノードの電位との電位差の方が大きくなる。この結果、感度が高く、かつS/N比も高い光センサを実現することができる。

また、本実施形態の光センサにおいても、ダイオードD1の遮光膜LSの電位が、定電位VLSに固定され、このVLSの値が、

VLS≧VRST.H、

より好ましくは、

VLS≧VRST.H+Vth_p

を満たすことにより、第1の実施形態と同様に、照度変化に対する線形性の良い光センサ出力を得ることができる。

VLS≧VRST.H、

より好ましくは、

VLS≧VRST.H+Vth_p

を満たすことにより、第1の実施形態と同様に、照度変化に対する線形性の良い光センサ出力を得ることができる。

[第3の実施形態]

以下、本発明の第3の実施形態について説明する。前述の各実施形態において説明した構成と同様の機能を有する構成については、前述の実施形態と同じ参照符号を付記し、その詳細な説明を省略する。

以下、本発明の第3の実施形態について説明する。前述の各実施形態において説明した構成と同様の機能を有する構成については、前述の実施形態と同じ参照符号を付記し、その詳細な説明を省略する。

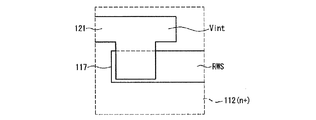

図23は、本実施形態にかかる光センサの等価回路図である。図24は、本実施形態にかかる光センサの平面構造の一例を示す平面図である。図25は、コンデンサC1が形成されている領域の拡大図である。図26は、本実施形態にかかる光センサにおける各領域の接続関係を示した断面模式図である。

図23に示すように、本実施形態にかかる光センサの等価回路図は、第1の実施形態と同じである。ただし、図24〜図26に示すように、コンデンサC1の構造等が異なっている。

図24に示すように、本実施形態の光センサにおいては、トランジスタM2のゲート電極101からの配線が、ダイオードD1のn型半導体領域102nの上方まで延設され、コンタクト115,116を介してn型半導体領域102nに接続されている。トランジスタM2のゲート電極101からの配線は、コンデンサC1の上層にも延設され、コンデンサC1のゲート電極121として機能する。

図25および図26に示すように、ゲート電極121と、シリコン膜117と、その間に配置された絶縁膜(図示せず)とによって、コンデンサC1が形成されている。ゲート電極121は、蓄積ノードINTと同電位(VINT)である。本実施形態においては、図25に示す領域112は、n型シリコン膜に対して例えばリン等のn型不純物をドープして形成されたn+領域である。なお、n型不純物のドープの際にゲート電極121がマスクとして機能するので、図26に示すように、ゲート電極121の下方にあるシリコン膜はn−領域を形成する。

本実施形態の光センサは、第1の実施形態において図4に示したリセット信号と読み出し信号によって駆動され、積分期間および読み出し期間における蓄積ノードINTの電位変化は、第1の実施形態において図9に示したとおりである。したがって、本実施形態の光センサによっても、積分期間終了時点における受光面の照度の差による蓄積ノードの電位差よりも、突き上げ後の電位差の方が大きくなる。例えば、暗状態の場合の蓄積期間終了時点の蓄積ノードの電位と、飽和レベルの光が入射した場合の蓄積期間終了時点の蓄積ノードの電位との電位差よりも、前記暗状態の場合の読み出し期間における突き上げ後の蓄積ノードの電位と、飽和レベルの光が入射した場合の読み出し期間における突き上げ後の蓄積ノードの電位との電位差の方が大きくなる。この結果、感度が高く、かつS/N比も高い光センサを実現することができる。

また、本実施形態の光センサにおいても、ダイオードD1の遮光膜LSの電位が、定電位VLSに固定され、このVLSの値が、

VLS≧VRST.H、

より好ましくは、

VLS≧VRST.H+Vth_p

を満たすことにより、第1の実施形態と同様に、照度変化に対する線形性の良い光センサ出力を得ることができる。

VLS≧VRST.H、

より好ましくは、

VLS≧VRST.H+Vth_p

を満たすことにより、第1の実施形態と同様に、照度変化に対する線形性の良い光センサ出力を得ることができる。

[第4の実施形態]

以下、本発明の第4の実施形態について説明する。前述の各実施形態において説明した構成と同様の機能を有する構成については、前述の実施形態と同じ参照符号を付記し、その詳細な説明を省略する。

以下、本発明の第4の実施形態について説明する。前述の各実施形態において説明した構成と同様の機能を有する構成については、前述の実施形態と同じ参照符号を付記し、その詳細な説明を省略する。

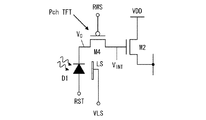

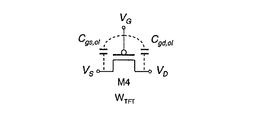

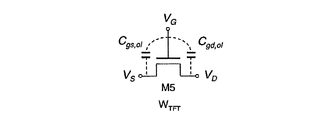

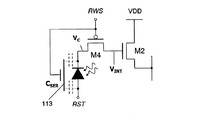

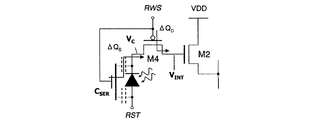

図27は、本実施形態にかかる光センサの等価回路図である。図28は、本実施形態にかかる光センサの平面構造の一例を示す平面図である。図29は、増幅素子(pチャネルTFT)が形成されている領域の拡大図である。図30は、本実施形態にかかる光センサにおける各領域の接続関係を示した断面模式図である。図31は、増幅素子としてのpチャネルTFTの等価回路図である。

本実施形態にかかる光センサは、図27〜図31に示すように、増幅素子として、第1〜第3の実施形態において説明した可変コンデンサC1の代わりに、pチャネルTFT(トランジスタM4)を用いたものである。なお、トランジスタM4を増幅素子として用いた本実施形態の光センサの駆動信号および動作は、第1の実施形態において図4および図9を参照して説明したものと同じである。したがって、本実施形態にかかる光センサによっても、蓄積ノードの電位VINTを増幅して読み出すことができる。

また、図28および図29に示すように、本実施形態にかかる光センサは、配線RWSの幅広部111が、配線107の幅全体を覆う位置まで延設されている点においても、第1の実施形態と異なっている。この構成により、本実施形態にかかる光センサは、第1の実施形態にかかる光センサよりも境界長が短いという利点を有する。

以下、境界長について説明する。境界長とは、増幅素子と蓄積ノードINTとの境界の長さを意味する。例えば、第1の実施形態においては、図6および図7に示すように、シリコン膜の延設部107と配線RWSの幅広部111との重なりによってコンデンサC1が形成されている。したがって、第1の実施形態においては、図7に示すように、増幅素子と蓄積ノードINTとの境界は太線Bで示されるとおり、配線RWSの幅広部111の外縁がシリコン膜の延設部107に重なっている部分である。すなわち、第1の実施形態においては、図7に示したLCAPの長さと、2×WCAPの値との和が、境界長となる。また、本実施形態にかかる光センサにおいては、図29に示すように、配線RWSの幅広部111とシリコン膜の延設部107とが重なっている部分が増幅素子として機能するので、この増幅素子の幅WTFT(すなわち延設部107の幅)の2倍が、境界長である。

第1の実施形態においては、境界長を短くしようとすると、LCAPの長さを小さくしなければならず、コンデンサC1の容量を確保するためには、コンデンサC1のレイアウト面積が増加してしまう。しかし、第4の実施形態においては、境界長はシリコン膜の延設部107の幅WTFTであるため、レイアウト面積を増加させることなく境界長を短くすることができる。

なお、境界長が短い方が良い理由について、図9および図32を参照しながら以下に説明する。第1の実施形態において図9を参照しながら説明したように、配線RWSから供給される読み出し信号がローレベル電位VRWS.Lからハイレベル電位VRWS.Hへ立ち上がる途中に、閾値電圧Voffが存在する。ここで、時刻t1において配線RWSの読み出し信号が閾値電圧Voffに到達した後は、サンプリング時刻tSまで、蓄積ノードの電位VINTは一定であることが好ましい。しかし、図32に示すように、読み出し信号が上昇する時刻t1〜t2の間には、増幅素子と蓄積ノードとの間の寄生容量に起因して、蓄積ノードの電位VINTは上昇し続ける。また、読み出し信号の電位がハイレベル電位VRWS.Hへ到達した時刻t2からサンプリング時刻tSの間にも、リーク電流に起因して、蓄積ノードの電位VINTは上昇し続ける。このように、時刻t1以降に蓄積ノードの電位VINTが上昇が生じることは、電位の増幅効果が小さくなるために好ましくない。時刻t1以降の寄生容量およびリーク電流に起因する電位VINTの上昇を抑制するためには、増幅素子の境界長が短いことが好ましい。

したがって、第4の実施形態にかかる光センサは、増幅素子の境界長が短い点において、時刻t1以降の寄生容量およびリーク電流に起因する電位VINTの上昇を抑制することができ、第1の実施形態にかかる光センサよりも有利である。

また、第4の実施形態にかかる光センサの変形例として、図33および図34に示すように、シリコン膜の延設部107の幅を狭くし、かつ、延設部107に、増幅素子の幅WCAPを確保するための幅広部107aを設けた構成とすることにより、増幅素子の有効面積を確保しつつ、境界長WTFTをさらに短くした構成とすることも可能である。この場合、増幅素子としてのpチャネルTFTの等価回路図は、図35に示すとおりとなる。この変形例にかかる構成によれば、図27〜図31に示した構成と比較して、境界長をさらに短くできるので、時刻t1以降の寄生容量およびリーク電流に起因する電位VINTの上昇をさらに小さく抑制することができる。これにより、さらにダイナミックレンジの広い光センサを実現できる。

また、本実施形態の光センサにおいても、ダイオードD1の遮光膜LSの電位が、定電位VLSに固定され、このVLSの値が、

VLS≧VRST.H、

より好ましくは、

VLS≧VRST.H+Vth_p

を満たすことにより、第1の実施形態と同様に、照度変化に対する線形性の良い光センサ出力を得ることができる。

VLS≧VRST.H、

より好ましくは、

VLS≧VRST.H+Vth_p

を満たすことにより、第1の実施形態と同様に、照度変化に対する線形性の良い光センサ出力を得ることができる。

[第5の実施形態]

以下、本発明の第5の実施形態について説明する。前述の各実施形態において説明した構成と同様の機能を有する構成については、前述の実施形態と同じ参照符号を付記し、その詳細な説明を省略する。

以下、本発明の第5の実施形態について説明する。前述の各実施形態において説明した構成と同様の機能を有する構成については、前述の実施形態と同じ参照符号を付記し、その詳細な説明を省略する。

図36は、本実施形態にかかる光センサの等価回路図である。図37は、本実施形態にかかる光センサの平面構造の一例を示す平面図である。図38は、増幅素子(nチャネルTFT)が形成されている領域の拡大図である。図39は、本実施形態にかかる光センサにおける各領域の接続関係を示した断面模式図である。図40は、増幅素子としてのnチャネルTFTの等価回路図である。

本実施形態の光センサは、増幅素子として、第2の実施形態において説明したnチャネルMOSコンデンサの代わりに、nチャネルTFT(トランジスタM4)を用いたものである。なお、nチャネルTFTを増幅素子として用いた本実施形態の光センサの駆動信号は、第2の実施形態において図19を参照して説明したとおり、nチャネルTFTを増幅素子として用いた第4の実施形態の駆動信号とは、ハイレベルとローレベルの電位が逆である。その駆動信号によれば、本実施形態の光センサは、第1の実施形態において図9を参照して説明したとおり、蓄積ノードの電位VINTを増幅して読み出すことができる。

図36および図37に示すとおり、本実施形態にかかる光センサにおいては、ダイオードD1が第4の実施形態とは逆向きに接続されている。すなわち、ダイオードD1のカソードが配線RSTに接続され、nチャネルTFTに接続されている。さらに、読み出し用のトランジスタM2が、pチャネルTFTである。

図37および図38に示すように、本実施形態にかかる光センサは、配線RWSの幅広部111が、配線107の幅全体を覆う位置まで延設されている点において、第2の実施形態と異なっている。本実施形態にかかる光センサは、前述の第4の実施形態において第1の実施形態と対比しながら説明したとおり、第2の実施形態にかかる光センサよりも境界長が短いという利点を有する。すなわち、第2の実施形態にかかる光センサの境界長は、図21に示すように、LCAP+2×WCAPである。一方、本実施形態にかかる光センサの境界長は、図38に示すように、延設部107の幅WTFTである。

第2の実施形態においては、境界長を短くしようとすると、LCAPの長さを小さくしなければならず、コンデンサC1の容量を確保するためには、コンデンサC1のレイアウト面積が増加してしまう。しかし、本実施形態においては、境界長はシリコン膜の延設部107の幅WTFTの2倍であるため、レイアウト面積を増加させることなく境界長を短くすることができる。これにより、本実施形態にかかる光センサは、増幅素子の境界長が短い点において、時刻t1以降の寄生容量およびリーク電流に起因する電位VINTの上昇を抑制することができ、第2の実施形態にかかる光センサよりも有利である。

また、第5の実施形態にかかる光センサの変形例として、図41および図42に示すように、シリコン膜の延設部107の幅を狭くし、かつ、延設部107に幅広部107aを設けた構成とすることにより、増幅素子の有効面積を確保しつつ、レイアウト面積を増加させることなく、WTFTをさらに短くした構成とすることも可能である。この場合、増幅素子としてのnチャネルTFTの等価回路図は、図43に示すとおりとなる。この変形例にかかる構成によれば、図36〜図40に示した構成と比較して、境界長をさらに短くできるので、時刻t1以降の寄生容量およびリーク電流に起因する電位VINTの上昇をさらに小さく抑制することができる。これにより、さらにダイナミックレンジの広い光センサを実現できる。

また、本実施形態の光センサにおいても、ダイオードD1の遮光膜LSの電位が、定電位VLSに固定され、このVLSの値が、

VLS≧VRST.H、

より好ましくは、

VLS≧VRST.H+Vth_p

を満たすことにより、第1の実施形態と同様に、照度変化に対する線形性の良い光センサ出力を得ることができる。

VLS≧VRST.H、

より好ましくは、

VLS≧VRST.H+Vth_p

を満たすことにより、第1の実施形態と同様に、照度変化に対する線形性の良い光センサ出力を得ることができる。

[第6の実施形態]

以下、本発明の第6の実施形態について説明する。前述の各実施形態において説明した構成と同様の機能を有する構成については、前述の実施形態と同じ参照符号を付記し、その詳細な説明を省略する。

以下、本発明の第6の実施形態について説明する。前述の各実施形態において説明した構成と同様の機能を有する構成については、前述の実施形態と同じ参照符号を付記し、その詳細な説明を省略する。

図44は、本実施形態にかかる光センサの等価回路図である。図45は、本実施形態にかかる光センサの平面構造の一例を示す平面図である。図46は、増幅素子(ダイオードD2)が形成されている領域の拡大図である。図47は、本実施形態にかかる光センサにおける各領域の接続関係を示した断面模式図である。図48は、増幅素子としてのダイオードの等価回路図である。

本実施形態にかかる光センサは、増幅素子としてダイオードD2を用いた点において、前述の各実施形態と異なる。なお、ここで用いるダイオードD2は、チャネル上にゲート電極を備えたダイオードである。ダイオードD2は、チャネル領域上にゲート電極を設けたことにより、ゲート−ダイオード間の容量によって読み出し期間の突き上げを行う。図44に示すように、本実施形態にかかる光センサは、増幅素子として機能するダイオードD2を有する。図44〜図46に示すように、ダイオードD2のカソード(n型半導体領域107n)は、ダイオードD1のカソード(n型半導体領域102n)に接続され、ダイオードD2のアノード(p型半導体領域107p)は、蓄積ノードINTに接続されている。

この構成においても、第1の実施形態において図4に示したリセット信号および読み出し信号によって、第1の実施形態で図9に示したとおり、蓄積ノードの電位VINTを増幅して読み出すことができる。

また、本実施形態にかかる構成は、第4の実施形態のように増幅素子としてpチャネルTFTを用いた構成と比較して、以下の二つの利点を有する。

第1の利点は、境界長がさらに短いという点である。つまり、本実施形態にかかる光センサにおいては、図46に示すように、境界Bがp+領域側にしか存在しないので、境界長はシリコン膜の延設部107の幅WTFTである。したがって、時刻t1以降の寄生容量およびリーク電流に起因する電位VINTの上昇をさらに抑制することができる点で、第4の実施形態にかかる光センサよりも有利である。

第2の利点は、ダイオードD1のカソード(n型半導体領域102n)と、ダイオードD2のカソード(n型半導体領域107n)とが接続されるので、ダイオードD1のカソード(n型半導体領域102n)をp型半導体領域に接続する第4の実施形態と比較して、接続が容易であるという点である。

なお、図44および図45に示した構成の変形例として、図49および図50に示すような構成を採用しても良い。図49は、本実施形態の第1の変形例にかかる光センサの等価回路図である。図50は、前記第1の変形例にかかる光センサの平面構造の一例を示す平面図である。図49および図50に示すように、本実施形態の第1の変形例にかかる光センサは、リセット用トランジスタM5が追加された構成である。

ダイオードD1のアノード(p型半導体領域102p)は、配線108およびコンタクト109,110を介して、所定のDC電位を供給する配線VSSに接続されている。リセット用トランジスタM3のゲート電極131は、配線RSTから延設されている。この第1の変形例にかかる構成によれば、図44および図45に示したようにダイオードD2を介してリセットを行う構成と比較して、蓄積ノードINTに接続されたリセット用のトランジスタM3によって、蓄積ノードをより確実にリセットすることができるという利点がある。

また、第2の変形例として、図51および図52に示すような構成も可能である。図51は、本実施形態の第2の変形例にかかる光センサの等価回路図である。図52は、前記第2の変形例にかかる光センサの平面構造の一例を示す平面図である。図51および図52に示す構成においては、ダイオードD1のアノード(p型半導体領域102p)が、リセット信号を供給する配線RSTに接続されている点において、前記の第1の変形例と異なっている。この構成によれば、配線VSSを別個に設ける必要がないので、前記の第1の変形例と比較して、光センサのレイアウト面積を小さくすることができるという利点がある。

また、本実施形態の光センサにおいても、ダイオードD1の遮光膜LSの電位が、定電位VLSに固定され、このVLSの値が、

VLS≧VRST.H、

より好ましくは、

VLS≧VRST.H+Vth_p

を満たすことにより、第1の実施形態と同様に、照度変化に対する線形性の良い光センサ出力を得ることができる。

VLS≧VRST.H、

より好ましくは、

VLS≧VRST.H+Vth_p

を満たすことにより、第1の実施形態と同様に、照度変化に対する線形性の良い光センサ出力を得ることができる。

[第7の実施形態]

以下、本発明の第7の実施形態について説明する。前述の各実施形態において説明した構成と同様の機能を有する構成については、前述の実施形態と同じ参照符号を付記し、その詳細な説明を省略する。

以下、本発明の第7の実施形態について説明する。前述の各実施形態において説明した構成と同様の機能を有する構成については、前述の実施形態と同じ参照符号を付記し、その詳細な説明を省略する。

図53は、本実施形態にかかる光センサの等価回路図である。図54は、本実施形態にかかる光センサの平面構造の一例を示す平面図である。

本実施形態にかかる光センサは、第4の実施形態において、図33〜図35に示した構成において、図53および図54に示すように、ダイオードD1の背面に設けられた遮光膜LSとしての金属膜113を、配線RWSと対向する位置まで延設し、この金属膜113と配線RWSとその間の絶縁膜(図示せず)により、コンデンサCSERを形成したものである。つまり、本実施形態にかかる光センサは、第4の実施形態と同様に、増幅素子としてpチャネルTFT(トランジスタM4)を用いている。

図53に示す構成において、コンデンサCSERは、金属膜113とダイオードD1との間の容量Cc、Caに対する直列コンデンサとして機能する。このため、第1の実施形態において説明した式(6)中のCINT’を増加させずに、CINTだけを増加させることができ、読み出し時の増幅効果を向上させることができる。

なお、このようにコンデンサCSERを備えたことにより、読み出し時の増幅効果を向上させる効果は、増幅素子として可変コンデンサを用いる構成よりも、本実施形態のように増幅素子としてpチャネルTFTを用いる構成において顕著である。

すなわち、図55Aに示すように、増幅素子として可変コンデンサC1が用いられている構成(第1の実施形態)にコンデンサCSERを組み合わせた場合、読み出し時に、蓄積ノードの電位VINTは、コンデンサC1からの電荷ΔQCだけでなく、コンデンサCSERから注入される電荷QSによっても影響を受ける。したがって、この構成においては、コンデンサCSERの存在は、読み出し時の増幅効果を低減させることとなる。

一方、図55Bに示すように、本実施形態のように、増幅素子としてpチャネルTFT(トランジスタM4)が用いられている構成にコンデンサCSERを組み合わせた場合、読み出し時には、コンデンサCSERから注入される電荷もトランジスタM4を通過しなければならない。したがって、コンデンサCSERから注入される電荷(ΔQS)も、電荷ΔQCと共に、増幅効果を向上させるよう作用する。

したがって、本実施形態のように、増幅素子としてpチャネルTFTを用いた構成にコンデンサCSERを組み合わせた光センサは、高い増幅効果を得る上で効果的である。

なお、上記の説明においては、第4の実施形態において図33〜図35に示した構成にコンデンサCSERを組み合わせた例を示したが、第4および第5の実施形態において説明した他の構成についても、コンデンサCSERを組み合わせることにより、同様の効果を得ることができる。

[第8の実施形態]

以下、本発明の第8の実施形態について説明する。前述の各実施形態において説明した構成と同様の機能を有する構成については、前述の実施形態と同じ参照符号を付記し、その詳細な説明を省略する。

以下、本発明の第8の実施形態について説明する。前述の各実施形態において説明した構成と同様の機能を有する構成については、前述の実施形態と同じ参照符号を付記し、その詳細な説明を省略する。

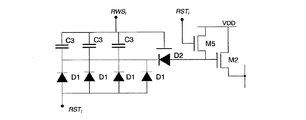

図56は、本実施形態にかかる光センサの等価回路図である。図57は、本実施形態にかかる光センサの平面構造の一例を示す平面図である。図56および図57に示すように、本実施形態にかかる光センサでは、複数の画素領域にわたって、ダイオードD1およびコンデンサC3がそれぞれ並列に形成されている。コンデンサC3は、通常の(可変ではない)コンデンサである。なお、図56および図57の例では、1つの読み出し用トランジスタM2により、4個のダイオードD1から読み出しを行う構成としたが、読み出し対象とするダイオードD1の個数はこれに限定されない。

図56および図57に示す例では、読み出し用トランジスタM2に最も近い画素領域にpチャネルTFT(トランジスタM4)を増幅素子として形成し、他の画素領域には通常の(可変でない)コンデンサC3が形成されている。

この構成によれば、ダイオードD1を複数並列に接続したことにより、光電流を増加させることができる。また、複数のダイオードD1において読み出しトランジスタM2に最も近いところに増幅素子を配置したことにより、蓄積ノードの電位を増幅して読み出すことができる。これにより、S/N比を劣化させることなく、感度が高い光センサを実現することができる。また、増幅素子としてpチャネルTFTを用いることにより、前述したように、可変コンデンサを用いる場合と比較して、境界長を短くすることができる。これにより、増幅効果をさらに向上させることができる。

また、本実施形態の光センサにおいても、ダイオードD1の遮光膜LS(図示省略)の電位が、定電位VLSに固定され、このVLSの値が、

VLS≧VRST.H、

より好ましくは、

VLS≧VRST.H+Vth_p

を満たすことにより、第1の実施形態と同様に、照度変化に対する線形性の良い光センサ出力を得ることができる。

VLS≧VRST.H、

より好ましくは、

VLS≧VRST.H+Vth_p

を満たすことにより、第1の実施形態と同様に、照度変化に対する線形性の良い光センサ出力を得ることができる。

[第9の実施形態]

以下、本発明の第9の実施形態について説明する。前述の各実施形態において説明した構成と同様の機能を有する構成については、前述の実施形態と同じ参照符号を付記し、その詳細な説明を省略する。

以下、本発明の第9の実施形態について説明する。前述の各実施形態において説明した構成と同様の機能を有する構成については、前述の実施形態と同じ参照符号を付記し、その詳細な説明を省略する。

図58は、本実施形態にかかる光センサの等価回路図である。図59は、本実施形態にかかる光センサの平面構造の一例を示す平面図である。図58および図59に示すように、本実施形態にかかる光センサでは、複数の画素領域にわたって、ダイオードD1およびコンデンサC3がそれぞれ並列に形成されている。コンデンサC3は、通常の(可変ではない)コンデンサである。なお、図58および図59の例では、1つの読み出し用トランジスタM2により、4個のダイオードD1から読み出しを行う構成としたが、読み出し対象とするダイオードD1の個数はこれに限定されない。

図58および図59に示す例では、4個のダイオードD1のうち、読み出し用トランジスタM2に最も近い画素領域に、増幅素子としてのダイオードD2が設けられ、他の画素領域には通常の(可変でない)コンデンサC3が形成されている。また、読み出し用トランジスタM2の隣の画素領域に、リセット用トランジスタM5が形成されている。

この構成によれば、ダイオードD1を複数並列に接続したことにより、光電流を増加させることができる。また、複数のダイオードD1において読み出しトランジスタM2に最も近いところに増幅素子(ダイオードD2)を配置したことにより、蓄積ノードの電位を増幅して読み出すことができる。これにより、S/N比を劣化させることなく、感度が高い光センサを実現することができる。また、増幅素子としてダイオードD2を用いることにより、前述したように、可変コンデンサを用いる場合と比較して、境界長を短くすることができる。これにより、増幅効果をさらに向上させることができる。

また、本実施形態の光センサにおいても、ダイオードD1の遮光膜LS(図示省略)の電位が、定電位VLSに固定され、このVLSの値が、

VLS≧VRST.H、

より好ましくは、

VLS≧VRST.H+Vth_p

を満たすことにより、第1の実施形態と同様に、照度変化に対する線形性の良い光センサ出力を得ることができる。

VLS≧VRST.H、

より好ましくは、

VLS≧VRST.H+Vth_p

を満たすことにより、第1の実施形態と同様に、照度変化に対する線形性の良い光センサ出力を得ることができる。

[第10の実施形態]

以下、本発明の第10の実施形態について説明する。前述の各実施形態において説明した構成と同様の機能を有する構成については、前述の実施形態と同じ参照符号を付記し、その詳細な説明を省略する。

以下、本発明の第10の実施形態について説明する。前述の各実施形態において説明した構成と同様の機能を有する構成については、前述の実施形態と同じ参照符号を付記し、その詳細な説明を省略する。

図60は、本実施形態にかかる光センサの等価回路図である。図61は、本実施形態にかかる光センサの平面構造の一例を示す平面図である。図60および図61に示すように、本実施形態にかかる光センサは、第1の実施形態にかかる光センサに対して、リセットトランジスタM5を追加した構成である。リセットトランジスタM5のゲート電極131は、配線RSTから延設されている。

この構成においても、第1の実施形態にかかる光センサと同様に、蓄積ノードの電位を増幅して読み出すことができる。これにより、S/N比を劣化させることなく、感度が高い光センサを実現することができる。

また、本実施形態の光センサにおいても、ダイオードD1の遮光膜LSの電位が、定電位VLSに固定され、このVLSの値が、

VLS≧VRST.H、

より好ましくは、

VLS≧VRST.H+Vth_p

を満たすことにより、第1の実施形態と同様に、照度変化に対する線形性の良い光センサ出力を得ることができる。

VLS≧VRST.H、

より好ましくは、

VLS≧VRST.H+Vth_p

を満たすことにより、第1の実施形態と同様に、照度変化に対する線形性の良い光センサ出力を得ることができる。

また、このようにリセットトランジスタM5を設ける構成は、第1の実施形態の他に、第2の実施形態、第3の実施形態、第4の実施形態、第5の実施形態、第7の実施形態、および、第8の実施形態にも適用することができ、それぞれの実施形態で説明したとおりの効果を奏する。

以上、本発明についての第1〜第10の実施形態を説明したが、本発明は上述の各実施形態にのみ限定されず、発明の範囲内で種々の変更が可能である。

例えば、上述の実施形態では、光センサに接続された配線VDD,VSSおよびOUTが、ソース線COLと共用されている構成を例示した。この構成によれば、画素開口率が高いという利点がある。しかしながら、この構成は、光センサ用の配線がソース線COLを共用しているので、画素表示のための映像信号がソース線COLに印加されている間は、センサ回路出力データの読み出しができない。そのため、図14に示したように、帰線期間にセンサ回路出力データの読み出し信号を印加することが必要となる。そこで、光センサ用の配線VDD,VSSおよびOUTをソース線COLとは別個に設けた構成としても良い。この構成によれば、画素開口率は低くなるが、光センサ用の配線をソース線COLとは別個に駆動することができるので、画素表示のタイミングと関係なく、センサ回路出力データの読み出しを行うことができるという利点がある。

本発明は、アクティブマトリクス基板の画素領域内に光センサを有する表示装置として、産業上の利用が可能である。

Claims (17)

- アクティブマトリクス基板の画素領域に光センサを備えた表示装置であって、

前記光センサが、

入射光を受光する光検出素子と、

当該光センサへリセット信号を供給するリセット信号配線と、

当該光センサへ読み出し信号を供給する読み出し信号配線と、

前記リセット信号が供給されてから前記読み出し信号が供給されるまでの間をセンシング期間とし、センシング期間に前記光検出素子で受光された光量にしたがって電位が変化する蓄積ノードと、

前記読み出し信号に応じて、前記蓄積ノードの電位を増幅する増幅素子と、

前記増幅素子で増幅された電位をセンサ回路出力として出力配線へ読み出すためのセンサスイッチング素子とを備え、

前記光検出素子に対してその受光面とは反対側に遮光膜が設けられ、

前記遮光膜が、当該遮光膜を定電位に固定する電圧を供給する電源に接続され、

前記定電位をVLS、前記リセット信号のハイレベル電位をVRST.Hとすると、

VLS ≧ VRST.H

である表示装置。 - 前記光検出素子がPINダイオードであり、

前記PINダイオードのpチャネル閾値電圧をVth_pとすると、

VLS ≧ VRST.H + Vth_p

である、請求項1に記載の表示装置。 - 前記増幅素子が可変コンデンサである、請求項1または2に記載の表示装置。

- 前記可変コンデンサが、前記読み出し信号配線と、絶縁膜と、シリコン膜に形成されたp型半導体領域とを含むMOSコンデンサである、請求項3に記載の表示装置。

- 前記可変コンデンサが、前記センサスイッチング素子のゲート電極と、絶縁膜と、シリコン膜に形成されたn型半導体領域とを含むMOSコンデンサである、請求項3に記載の表示装置。

- 前記増幅素子がpチャネル薄膜トランジスタである、請求項1〜5のいずれか一項に記載の表示装置。

- 前記pチャネル薄膜トランジスタにおいて、前記光検出素子と前記蓄積ノードとを接続するシリコン膜の幅広部にチャネル領域が形成され、前記幅広部にオーバーラップするように当該pチャネル薄膜トランジスタのゲート電極が設けられている、請求項6に記載の表示装置。

- 前記増幅素子がnチャネル薄膜トランジスタである、請求項1〜5のいずれか一項に記載の表示装置。

- 前記増幅素子が、チャネル上にゲート電極を備えたダイオードである、請求項1〜5のいずれか一項に記載の表示装置。

- 前記遮光膜と前記光検出素子との寄生容量に対して直列容量を形成するように、前記遮光膜に対向して設けられた電極とを備え、

前記電極が前記読み出し配線に電気的に接続されている、請求項1〜9のいずれか一項に記載の表示装置。 - 前記画素領域に複数の前記光検出素子を備え、

前記複数の光検出素子が並列に接続され、

前記複数の光検出素子の末端の光検出素子に前記増幅素子が接続された、請求項1〜10のいずれか一項に記載の表示装置。 - 前記センサスイッチング素子が三端子スイッチング素子であり、

前記三端子のうちのゲート電極が前記蓄積ノードに接続され、

前記三端子のうちの残りの二端子の一方が、前記出力配線へ接続された、請求項1〜11のいずれか一項に記載の表示装置。 - 前記センサスイッチング素子のリセット用スイッチング素子をさらに備えた、請求項1〜12のいずれか一項に記載の表示装置。

- 前記増幅素子が、前記読み出し信号のローレベル電位とハイレベル電位との間に、当該増幅素子のオン/オフが切り替わる閾値電位を有する、請求項1〜13のいずれか一項に記載の表示装置。

- 前記アクティブマトリクス基板に対向する対向基板と、

前記アクティブマトリクス基板と対向基板との間に挟持された液晶とをさらに備えた、請求項1〜14のいずれか一項に記載の表示装置。 - アクティブマトリクス基板の画素領域に光センサを備えた表示装置であって、

前記光センサが、

入射光を受光する光検出素子と、

当該光センサへリセット信号を供給するリセット信号配線と、

当該光センサへ読み出し信号を供給する読み出し信号配線と、

前記リセット信号が供給されてから前記読み出し信号が供給されるまでの間をセンシング期間とし、センシング期間に前記光検出素子で受光された光量にしたがって電位が変化する蓄積ノードと、

前記読み出し信号に応じて、前記蓄積ノードの電位を増幅する増幅素子と、

前記増幅素子で増幅された電位をセンサ回路出力として出力配線へ読み出すためのセンサスイッチング素子とを備え、

前記光検出素子に対してその受光面とは反対側に遮光膜が設けられ、

前記遮光膜が、当該遮光膜を定電位に固定する電圧を供給する電源に接続された、表示装置。 - 前記光検出素子がPINダイオードである、請求項16に記載の表示装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011543359A JP5284487B2 (ja) | 2009-11-30 | 2010-11-30 | 表示装置 |

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009272671 | 2009-11-30 | ||

| JP2009272671 | 2009-11-30 | ||

| PCT/JP2010/071327 WO2011065558A1 (ja) | 2009-11-30 | 2010-11-30 | 表示装置 |

| JP2011543359A JP5284487B2 (ja) | 2009-11-30 | 2010-11-30 | 表示装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2011065558A1 JPWO2011065558A1 (ja) | 2013-04-18 |

| JP5284487B2 true JP5284487B2 (ja) | 2013-09-11 |

Family

ID=44066662

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011543359A Expired - Fee Related JP5284487B2 (ja) | 2009-11-30 | 2010-11-30 | 表示装置 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US8803791B2 (ja) |

| EP (1) | EP2492781A4 (ja) |

| JP (1) | JP5284487B2 (ja) |

| CN (1) | CN102630313B (ja) |

| BR (1) | BR112012012809A2 (ja) |

| RU (1) | RU2510931C2 (ja) |

| WO (1) | WO2011065558A1 (ja) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5745369B2 (ja) | 2010-09-06 | 2015-07-08 | 株式会社半導体エネルギー研究所 | 電子機器 |

| JP6017214B2 (ja) * | 2012-07-23 | 2016-10-26 | ソニーセミコンダクタソリューションズ株式会社 | 撮像装置、撮像装置の駆動方法、および撮像表示システム |

| JP6132283B2 (ja) * | 2013-05-17 | 2017-05-24 | Nltテクノロジー株式会社 | 増幅回路および増幅回路を用いたイメージセンサ |

| JP2015187854A (ja) | 2014-03-13 | 2015-10-29 | 株式会社半導体エネルギー研究所 | 入力装置、入出力装置 |

| TWI655442B (zh) | 2014-05-02 | 2019-04-01 | 日商半導體能源研究所股份有限公司 | 輸入/輸出裝置 |

| US10497301B2 (en) | 2016-08-19 | 2019-12-03 | Innolux Corporation | Light-emitting device (LED) and LED displaying circuit |

| CN108492759B (zh) * | 2018-04-12 | 2021-04-06 | 京东方科技集团股份有限公司 | 一种感光器件、光学检测电路及驱动方法、显示装置 |

| CN109655877B (zh) | 2019-01-04 | 2020-12-01 | 京东方科技集团股份有限公司 | 平板探测器的像素结构、平板探测器及摄像系统 |

| KR102709961B1 (ko) | 2019-09-24 | 2024-09-27 | 삼성디스플레이 주식회사 | 표시 장치 |

| CN119916968A (zh) * | 2024-12-31 | 2025-05-02 | 重庆惠科金渝光电科技有限公司 | 显示面板的驱动电路、驱动方法和显示装置 |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2008156023A1 (ja) * | 2007-06-21 | 2008-12-24 | Sharp Kabushiki Kaisha | 光検出装置、及びそれを備えた表示装置 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS63160272A (ja) | 1986-12-23 | 1988-07-04 | Nec Corp | 固体撮像素子 |

| US6977684B1 (en) * | 1998-04-30 | 2005-12-20 | Canon Kabushiki Kaisha | Arrangement of circuits in pixels, each circuit shared by a plurality of pixels, in image sensing apparatus |

| NO316632B1 (no) * | 2001-11-16 | 2004-03-15 | Thin Film Electronics Asa | Matriseadresserbart optoelektronisk apparat og elektrodeanordning i samme |

| JP4167085B2 (ja) * | 2003-02-07 | 2008-10-15 | 株式会社 日立ディスプレイズ | 液晶表示装置 |

| KR20050106495A (ko) * | 2003-03-06 | 2005-11-09 | 소니 가부시끼 가이샤 | 고체촬상소자 및 그 제조방법과 고체촬상소자의 구동방법 |

| JP4737956B2 (ja) | 2003-08-25 | 2011-08-03 | 東芝モバイルディスプレイ株式会社 | 表示装置および光電変換素子 |

| JP4628693B2 (ja) * | 2004-03-31 | 2011-02-09 | 富士通株式会社 | 液晶表示装置用基板及びその製造方法並びにそれを備えた液晶表示装置 |

| CN100390840C (zh) * | 2004-06-30 | 2008-05-28 | 佳能株式会社 | 显示装置、电视装置、和驱动显示装置的方法 |

| JP2006079589A (ja) * | 2004-08-05 | 2006-03-23 | Sanyo Electric Co Ltd | タッチパネル |

| GB2439118A (en) | 2006-06-12 | 2007-12-19 | Sharp Kk | Image sensor and display |

| GB2439098A (en) | 2006-06-12 | 2007-12-19 | Sharp Kk | Image sensor and display |

| JP4793281B2 (ja) * | 2007-02-21 | 2011-10-12 | ソニー株式会社 | 撮像装置および表示装置 |

| WO2009025223A1 (ja) * | 2007-08-21 | 2009-02-26 | Sharp Kabushiki Kaisha | 表示装置 |

-

2010

- 2010-11-30 BR BR112012012809A patent/BR112012012809A2/pt not_active IP Right Cessation

- 2010-11-30 EP EP10833402.0A patent/EP2492781A4/en not_active Withdrawn

- 2010-11-30 WO PCT/JP2010/071327 patent/WO2011065558A1/ja not_active Ceased

- 2010-11-30 CN CN201080053932.2A patent/CN102630313B/zh not_active Expired - Fee Related

- 2010-11-30 JP JP2011543359A patent/JP5284487B2/ja not_active Expired - Fee Related

- 2010-11-30 RU RU2012127285/08A patent/RU2510931C2/ru not_active IP Right Cessation

- 2010-11-30 US US13/511,957 patent/US8803791B2/en not_active Expired - Fee Related

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2008156023A1 (ja) * | 2007-06-21 | 2008-12-24 | Sharp Kabushiki Kaisha | 光検出装置、及びそれを備えた表示装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN102630313B (zh) | 2015-04-29 |

| WO2011065558A1 (ja) | 2011-06-03 |

| EP2492781A4 (en) | 2013-06-05 |

| CN102630313A (zh) | 2012-08-08 |

| US20120261557A1 (en) | 2012-10-18 |

| EP2492781A1 (en) | 2012-08-29 |

| BR112012012809A2 (pt) | 2016-08-16 |

| RU2012127285A (ru) | 2014-01-10 |

| RU2510931C2 (ru) | 2014-04-10 |

| US8803791B2 (en) | 2014-08-12 |

| JPWO2011065558A1 (ja) | 2013-04-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5284487B2 (ja) | 表示装置 | |

| JP5068320B2 (ja) | 表示装置 | |

| JP4799696B2 (ja) | 表示装置 | |

| US8759739B2 (en) | Optical sensor and display apparatus | |

| JP5132771B2 (ja) | 表示装置 | |

| US20110122111A1 (en) | Display device | |

| WO2010092709A1 (ja) | 表示装置 | |

| JP5421355B2 (ja) | 表示装置 | |

| WO2010100785A1 (ja) | 表示装置 | |

| WO2010001929A1 (ja) | 表示装置 | |

| WO2010001652A1 (ja) | 表示装置 | |

| WO2010097984A1 (ja) | 光センサおよびこれを備えた表示装置 | |

| WO2011013631A1 (ja) | 光センサおよび表示装置 | |

| JPWO2011145682A1 (ja) | 表示装置 | |

| WO2011001878A1 (ja) | センサ回路及び表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130507 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130529 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5284487 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |