本発明は、家庭用電子機器や業務用電子機器に搭載されている音響増幅器や信号増幅器に用いられる増幅器(増幅回路)に関し、特に電子機器から発生する電磁妨害を抑制し、機器のコスト低減を可能とする増幅器(増幅回路)に関するものである。

従来、スイッチング技術を用いたD級増幅回路が一般に知られている。増幅素子の電流を中間状態に制御するアナログ増幅回路とは異なり、スイッチング増幅素子をON/OFFさせることにより、増幅素子での余分な発熱を大幅に低減できる利点があり、家庭用オーディオ機器等に使われてきている。

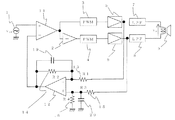

例えば、図29に示される特開平7−221564号公報に開示されたD級増幅器においては、入力信号源1aの信号電圧V

INをPWM(パルス幅変調)回路10aを介してパルス信号に変換した後、パルス増幅回路5aで増幅しLPF(低域通過フィルタ)7aでパルス成分を除去して元の入力信号の周波数成分を取り出してスピーカーなどの負荷9aに印加している。その際、パルス増幅回路5aに与えられた電源電圧を有効に活用して高出力を得るべく、PWM回路10aの出力パルスからインバーター61aを介して反転して得られた反転パルスを、パルス増幅回路6aとLPF8aを通して前記の負荷9aの他端子に印加するBTL(Bridged Transless)方式を用いる増幅回路が多用されている。BTL方式を用いることによって、負荷への実効印加電圧を2倍、出力電力を4倍にすることが可能である。例えば、図30(a)に示す信号電圧V

INが図29に示される従来回路に入力された場合、パルス増幅回路5aに与えられた電源電圧をVとすれば、図30(b)の実線に示す出力パルス電圧がパルス増幅回路5aとパルス増幅回路6aから負荷9aの両端子に向けて出力され、LPF7aとLPF8aを介して得られた信号周波数成分である出力電圧V

O1(破線で示される)が負荷9aに印加される。その際にLPF7aとLPF8aの間に印加される出力パルス電圧は、図示した通り+Vと−Vの2値となり電源電圧Vの2倍の電圧変化幅となる。この出力パルス電圧をLPF7aとLPF8aを介して負荷9aに加えることによって、図30(b)の破線に示される同じく電源電圧Vの2倍の電圧変化幅をもつ出力信号成分が負荷9aに印加される。

特開平7−221564号公報

一般にパルス電圧に伴って発生する電磁ノイズは、スピーカや電源ラインに電圧や電流として重畳される。従って、ノイズを低減するためには、これらのラインや回路、負荷であるスピーカーの回路部分を電磁シールド板で覆い尽くすか、ノイズ発生を阻止するフィルタ回路を回路の各部に挿入する必要がある。電磁シールド板は理想的には水も漏らさぬほどに密閉せねばならず、高価な板に加えてその実装人件費が大幅なコストアップを招いていた。フィルタ回路も発生のイズレベルが大きいほど、ノイズ周波数が高いほど高価な素子をふんだんに挿入せねばならず、大幅なコストアップの要因となっていた。

従来のD級増幅回路においては、図30(b)に示すように出力パルス電圧の振幅が電源電圧Vの2倍と大きく、パルス増幅回路5aとパルス増幅回路6aの後段、およびその電源回路への配線などから輻射される不要輻射が大きくなる。パルスは高い周波数成分を有しているので、図30(c)に示す如く、出力パルスの周波数成分は非常に高い周波数まで広がっている。たとえLPF7aとLPF8aを用いて、負荷9aに漏れ込むパルスの基本周波数成分から高調波成分を抑制しようとしても、LPFの周波数特性上、低次の高調波成分の抑制には限界がある。さらに、LPFやその前段の回路各部の電圧変化や電流変化に伴う輻射は抑制できず、高次の高調波成分ほどあらゆる空間経路を介して漏洩して、周辺機器や増幅器自体の誤動作やそれらにおけるノイズ発生の原因となる。また、パルス出力に伴う電磁不要輻射ノイズの発生を抑えるためには、パルス増幅回路の出力や電源系統、或いは増幅器全体に対してシールドを施したりフィルタ回路の挿入を多用せねばならず、このことが増幅器を大幅にコストアップさせる要因となっていた。

本発明の目的は、前述した従来技術の課題を解決し、電子機器から発生する電磁妨害を抑制しコスト低減を可能とする増幅器を提供することである。

前述した課題および目的を解決するために、本発明の増幅器では、入力信号源と基準信号源に接続された2つのパルス幅変調回路を備え、該第1のパルス幅変調回路は前記入力信号源に接続され、該第2のパルス幅変調回路は信号反転回路を介して前記入力信号源に接続されると共に、該第1および該第2のパルス幅変調回路の出力のそれぞれが一つの負荷の異なる端子に接続され、該第1および該第2のパルス幅変調回路のそれぞれの出力をフィルタ回路を介して前記負荷に接続し、前記第1および第2のパルス幅変調回路と前記フィルタ回路の間に第1および第2のパルス増幅回路を備え、前記第1および第2のパルス増幅回路の少なくとも一方は、第1および第2のパルス増幅回路の差動出力信号に残存する高周波を低減させるために、前記負荷の異なる端子に印加される信号の内の少なくとも一方の信号の、立ち上がり時間と立ち下がり時間との少なくとも一方の時間の信号変化速度を遅く又は速くすることにより、前記負荷の異なる端子に印加される信号の遷移時間の相異が減少するように調整するタイミング調整回路を有し、前記第1および第2のパルス増幅回路の少なくとも一方は、電源と、前記電源の一端に第1主電極が接続された第1の半導体素子と、前記第1の半導体素子の第2主電極に第1主電極が接続され、前記パルス増幅回路に対応する前記パルス幅変調回路の出力信号が制御電極に入力される第2の半導体素子とを備え、前記タイミング調整回路は、前記第2の半導体素子の制御電極と前記第1の半導体素子の制御電極とに接続される第1コンデンサと、前記第1の半導体素子の制御電極と前記第1の半導体素子の第1主電極とに接続される第2コンデンサとを有することを特徴とする。

また、本発明の増幅器では、さらに、第1の半導体素子の制御電極と第1の半導体素子の第1主電極とに接続される第2コンデンサを有することを特徴とする。

本発明に係る増幅器によれば、パルス出力の周波数成分の主体をなす奇数次高調波は理論上、排除でき、偶数次高調波と側波帯成分だけの電磁輻射となる。従って、発生ノイズが半減する。実際の出力電圧波形においては、パルス電圧振幅は半減し、信号の極性に応じてパルス極性も制御されることで、従来通りの出力パワーが確保できる。

パルス電圧に伴って発生する電磁ノイズは、スピーカや電源ラインに電圧や電流として重畳される。従って、ノイズを低減するためには、これらのラインや回路、負荷であるスピーカーの回路部分を電磁シールド板で覆い尽くすか、ノイズ発生を阻止するフィルタ回路を回路の各部に挿入する必要がある。電磁シールド板は理想的には水も漏らさぬほどに密閉せねばならず、高価な板に加えてその実装人件費が大幅なコストアップを招いていた。フィルタ回路も発生のイズレベルが大きいほど、ノイズ周波数が高いほど高価な素子をふんだんに挿入せねばならず、大幅なコストアップの要因となっていた。本発明に係る増幅器によれば、電磁シールド板を許容レベルで簡易形状に抑えられると共にその実装箇所も省略できる。また、フィルタ回路も大幅に削減できる。更にノイズ障害発生の面から見ても携帯電話やコンピュータ等の無線接続への妨害を大幅に低減できるので、情報化社会への適合性が極めて高い技術となり、本発明の工業上・社会上の効果は極めて高い。

さらに、入力信号を一つの基準信号に基づいてPWM変調して得られた第1のパルス信号と、入力信号の反転信号を上記と同一の基準信号に基づいてPWM変調して得られた第2のパルス信号をそれぞれ負荷の両端子に加える本発明に係る増幅器に於いては、両パルス信号の同相成分が相殺されて、電磁不要輻射が大幅に低減できる一方、増幅信号成分が含まれる両パルス信号の差動成分は従来通りに負荷に印加される。また、パルス信号を低域通過フィルタを経由して負荷に印加する場合には、増幅された信号成分のみを負荷に供給できる。更に低域通過フィルタを用いることによって、負荷からの負帰還制御を用いた低歪な増幅も可能となる。

さらに、入力信号を一つの基準信号に基づいてPWM変調して得られた第1のパルス信号と、入力信号の反転信号を前記と同一の基準信号に基づいてPWM変調して得られた第2のパルス信号とを論理回路において演算する本発明に係る増幅器に於いては、両パルス信号の同相成分を相殺すると共に、増幅信号成分が含まれる両パルス信号の差動成分を抽出することができる。また、論理回路によって得られた信号をパルス増幅を介して負荷の端子に印加することによって、単一の信号経路を経由するのみで負荷に電磁不要輻射を大幅に低減した増幅信号を供給することができる。

以下に本発明に係る増幅器を実施するための最良の形態につき、各実施例の図面を参照しながら具体的に説明する。なお、図面中同一構成部材については同一符号を付しその詳細な説明の重複説明を省略し、記載を簡潔化する。

図1は、本発明に係る増幅器の第1実施例の概略ブロック図であり、図2は、第1実施例の信号を示す波形図とスペクトラム図である。図1に示される実施例に於いては、入力信号源1の信号電圧VINをPWM回路3に入力すると共に、電圧利得−1の信号反転回路2を介してPWM回路3と同じ特性を有するPWM回路4に入力する。PWM回路3とPWM回路4には、パルス周波数と変調信号の入力ダイナミックレンジを決める3角波信号か鋸歯状波信号などの基準信号VREFを発生する単一の基準信号源31が接続されている。即ち、PWM回路3とPWM回路4はそれぞれの入力信号VINと入力信号−VINに加えて、基準信号VREFを共にもう一つの入力信号として共用している。PWM回路3とPWM回路4によってパルス幅変調された出力パルス信号は、従来回路と同様にパルス増幅回路5とパルス増幅回路6を介して増幅され、LPF7とLPF8を介してそのパルス周波数成分を除去される。従って、高域の周波数成分を減衰できる周波数特性を有していれば、LPF7とLPF8にはLC回路以外のRC回路やRL回路なども適用できる。さらに、もう一つのコンデンサや抵抗を入力端子と接地間に並列接続したπ型回路構成として、ノイズ低減効果を高めることもできる。残った元の入力信号の周波数成分のみの出力電圧がスピーカーなどの負荷9に印加される。前述した図29に示した従来回路と比較すると、パルス増幅回路5とパルス増幅回路6以降の後段回路に比べて回路規模やコストの小さい小信号回路部において、インバーター61aを削除して信号反転回路2とPWM回路を一つ追加しているのみであるので、図29に示される従来増幅器に比べほぼ同一の回路規模とコストで第1実施例の増幅器は実現できる。一般にこれらの小信号回路は安価で小形な集積回路中に収められる。

本発明の増幅器においては、図2(b)に示すように、パルス増幅回路5とパルス増幅回路6の出力間に得られる差動パルス電圧は常にグランドレベルを基準にして出力され、その振幅は常に電源電圧Vと同一の大きさに抑えられる。その際、図2(a)に示す入力信号の信号電圧VINの極性に応じて差動パルス電圧の極性も正と負に遷移する。この為、差動パルス電圧の振幅が従来に対して半減できるので、増幅器に起因する電磁妨害を大幅に抑制できると共に装置コストも大幅に低減できることは言うまでもない。さらに前記の差動パルス電圧波形を解析すると明らかなように、図2(c)に示す破線部に相当する、出力パルスの周波数スペクトラムの奇数次成分が消滅する。従って、本発明の適用によって、パルス増幅回路5とパルス増幅回路6の後段、およびその電源回路への配線などから輻射される不要輻射の周波数成分を半分以下に抑制できる。このことから、増幅器に設ける輻射対策と対策部品を大幅に軽減でき、周辺機器や増幅器自体への悪影響も抑えられると共に増幅器のコストを大幅に削減できる。

前記の本発明の原理をさらに詳しく説明する。本発明に係る増幅器の第1実施例による回路構成の具体例を図3と図4に示す。図3と図4には、図1中のPWM回路3とPWM回路4の内部回路の異なる具体例を示している。図3中のPWM回路3aは、パルス周波数と変調信号の入力ダイナミックレンジを決める3角波信号か鋸歯状波信号などの基準信号VREFを発生する基準信号源31からの基準信号と入力信号が入力され、コンパレータ32から構成される。図3中のPWM回路4aはPWM回路3aと共に基準信号源31を共用すると共に、コンパレータ41を構成要素に含んでいる。PWM回路3aとPWM回路4aの出力端子をそれぞれAとBとする。入力される信号電圧VINの交流成分が正のタイミングにおける、図3に示した回路の各部の電圧波形を図5に示す。この時、信号電圧VINと信号反転回路2の出力電圧−VIN,基準信号VREFとの電圧関係は図示したようになるので、PWM回路3aとPWM回路4aの出力電圧波形は、それぞれAの実線パルス波形とBの1点破線パルス波形になる。そのため、パルス増幅回路5とパルス増幅回路6の出力端子間の差動パルス電圧VO56は図示したように、正極性のパルス波形となる。反対に信号電圧VINの交流成分が負のタイミングにおいては、図6に示すように差動パルス電圧VO56も負極性パルス波形となる。その際、差動パルス電圧VO56はその正負に寄らず、パルスの重心が基準信号VREFの波形で定まる一定周期の交流波形となっている。従って、信号電圧VINが交流信号であれば差動パルス電圧VO56に含まれる奇数次の周波数成分は側波帯も含めて相殺しあって平均レベルは零になる。

図4に示したPWM回路3bとPWM回路4bの内部回路の具体例において、加算器33と加算器42で入力信号に基準信号VREFを加えた合成信号をコンパレータ32とコンパレータ41において比較電圧VCOMPと比較することによって、図3に示したPWM回路3aとPWM回路4aと同じ機能を実現している。

以上の実施例においては、負荷9としてスピーカーなどの例を図示してきたが、負荷としてはスピーカー以外にもモーターや照明デバイスなどの駆動部品が適用できることは言うまでもない。また、任意の用途の増幅器の負荷として、電子機器やシステムなどの電気パワーや増幅信号の供給を要する任意のものが想定できる。信号や電気エネルギーを増幅する任意の用途の増幅器であれば、本発明が適用できることは言うまでもない。また、増幅信号には最も単純な例として正弦波を図示してきたが、正弦波の多重信号と考えられる任意の交流波形は言うに及ばず、単発波形など任意の波形の信号や電気エネルギー(電流信号や電力信号など)にも本発明に係る増幅器の適用が可能である。

続いて、本発明に係る増幅器の第2の実施例の概略ブロック図を図7に示す。図7において、パルス増幅回路5とパルス増幅回路6の出力端子を一つのLPF7のみを介して負荷9に接続している。パルス増幅回路5とパルス増幅回路6の出力電圧がノイズ発生が問題になるほど大きな振幅や歪を伴っていない場合には、出力電流に含まれるノイズ成分のみを除去すればよい。その際には、出力電流の流れる回路経路に一つのLPF7を設けるだけでノイズ発生を抑制することができる。従って、図7に図示される実施例においてパルス増幅回路5と負荷9の間に設けられているLPF7は、パルス増幅回路6と負荷9の間のみに挿入し直しても構わない。

同様に、単一のLPFを用いた本発明に係る増幅器の第3の実施例を図8に示す。図8において、パルス増幅回路5とパルス増幅回路6の出力端子を一つのLPF10のみを介して負荷9に接続している。ただし、LPF10は図示した通り2端子対回路となっており、入力端子対がパルス増幅回路5とパルス増幅回路6の2出力端子に、出力端子対が負荷9の2端子に接続されている。LPF10のように接地端子の不要なフィルタ回路を用いることにより、ノイズ成分が接地点に漏洩する恐れがなくなり、ノイズ低減効果がより向上する。図8においてLPF10を構成する入力コイルを通過したノイズ成分は負荷9や接地点に到達することなく、コンデンサを介してパルス増幅回路5とパルス増幅回路6の出力端子間のみに封じ込まれる。このコンデンサは抵抗であっても構わない。LPF10がRC回路であってもRL回路であっても構わないことは言うまでもない。さらに、もう一つのコンデンサや抵抗を入力端子対に並列接続したπ型回路構成として、ノイズ低減効果を高めることもできる。

次に、増幅器の歪を抑制できる本発明に係る増幅器の第4の実施例の概略ブロック図を図9に示す。図9において、負荷9の端子間に現れる出力電圧Voを演算増幅器12から成る差動増幅回路を介して演算増幅器11に帰還する。演算増幅器11を用いて増幅器全体に入力信号VINを基準とした負帰還を施すことによって、歪を抑えた出力電圧Voを得ることができる。差動増幅回路の抵抗R1と抵抗R3、抵抗R2と抵抗R4をそれぞれ同じ抵抗値にすれば正確な差動増幅利得が得られる。差動増幅回路など含むため図示する回路規模が増大する都合上、これまで示してきた基準信号源31やこれに接続されるPWM回路3とPWM回路4の入力端子は省略してある。図9においては正確に出力電圧Voを帰還すべく、負荷9の両端子から差動増幅回路に向けて配線接続が設けられている。しかし、多くの場合には、負荷9の二つ端子電圧の間には信号経路に信号反転回路2が設けられていることのみの相異しかないので、両者の相似性を考慮して負荷9のどちらか片側の端子電圧のみを帰還信号に用いることもできる。

さらに、負帰還を施した場合にも単一のLPFを用いた本発明に係る増幅器の第5の実施例の概略ブロック図を図10に示す。図10において、図7に示した実施例と同様に、パルス増幅回路5とパルス増幅回路6の出力端子を一つのLPF7のみを介して負荷9に接続している。図10においてパルス増幅回路5と負荷9の間に設けられているLPF7は、パルス増幅回路6と負荷9の間のみに挿入し直しても構わない。負荷9のどちらか片側の端子電圧のみを帰還信号に用いることもできることは言うまでもない。

さらに、負帰還を施した場合にも単一の2端子対LPFを用いた本発明に係る増幅器の第6の実施例の概略ブロック図を図11に示す。図11において、図8に示した実施例と同様に、LPF10は図示した通り2端子対回路となっており、入力端子対がパルス増幅回路5とパルス増幅回路6の2出力端子に、出力端子対が負荷9の2端子に接続されている。負荷9のどちらか片側の端子電圧のみを帰還信号に用いることもできることは言うまでもない。

そして、負帰還性能をさらに向上できる本発明に係る増幅器の第7の実施例の概略ブロック図を図12に示す。図12において、追加したLPF17とLPF18を介して差動増幅回路に出力信号を帰還している。新たにLPF17とLPF18を設けることによって、負帰還の周波数特性や帰還利得がパルス除去用のLPF7とLPF8の特性によって制約されずに済む。新たに設けるLPF17とLPF18の遮断周波数はLPF7とLPF8とは異なっていても負帰還に適した周波数を自由に選ぶことができる。一般にLPF7とLPF8には負荷9に印加される電力も通過するすため、その設計の自由度は大きく制限されている。例えば、コスト削減のために、LPF7とLPF8にコイルに替えて用いる抵抗は、電力損失を考慮して極力低い抵抗値に抑えられる。新たに設けるLPF17とLPF18には帰還信号のみの伝送で済み大きな電力通過がないので、安価なRC回路を用いることができる。図示した差動増幅回路の入力側へのLPF17とLPF18の挿入に替えて、帰還信号の伝送経路であればどこでも別途にLPFを挿入できることは言うまでもない。例えば、演算増幅器11の反転入力端子と差動増幅回路の出力端子の間に新たに単一のLPFを挿入することができる。もちろん、LPF17とLPF18に替えて、図8に示したLPF10と同様の単一の2端子対LPFを設けることもできることは言うまでもない。また、負荷9の両端子からの帰還信号のどちらか一方のみを新規に設けたLPFを介して差動増幅回路に接続することもできる。さらには、負荷のどちらか片側の端子のみの電圧を帰還する場合には、新規に設けたLPFを介して信号帰還ができることは言うまでもない。

さらに、コストを抑えながらも負帰還性能をさらに向上できる本発明に係る増幅器の第8の実施例の概略ブロック図を図13に示す。図13の実施例では、差動増幅回路に少数の部品の追加をすることによって、差動増幅回路それ自体に上述のLPFに相当する周波数特性を持たせて帰還信号経路に設けたLPFを省略している。図13に示される実施例においては、コンデンサ19或いはコンデンサ20のうち少なくとも一方のコンデンサを抵抗に並列接続する。差動増幅回路の回路構成の改良方法は、コンデンサの並列付加に限られることなく無限に存在することは、当該エンジニアであれば容易に類推できる。新たに安価なコンデンサを接続することによって、差動増幅回路の電圧利得の周波数特性に低域遮断特性を持たせている。周波数特性に工夫を凝らす箇所は差動増幅回路に限定されるものでなく、演算増幅器11や演算増幅器12自体に対しても可能である。この場合にも、安価な改良で済むことは言うまでもない。

続いて、少しの工夫でノイズ低減効果を向上することができる極めて実用的な本発明に係る増幅器の第9の実施例の概略ブロック図を図14に示す。図14の実施例では、パルス増幅回路5とパルス増幅回路6のうちの少なくとも一方の出力スイッチング特性を調整することで、図5と図6に示した波形図で説明した高調波の相殺効果を著しく向上できる。一般的に図14中のパルス増幅回路5とパルス増幅回路6のそれぞれの出力電圧(電流であっても構わない)の波形21と波形22に示すように、パルス信号の立ち上がり時間と立ち下がり時間は破線のように異なっている。従って、厳密には波形21と波形22の関係から分かるように、立ち上がり波形と立ち下がり波形から発生するノイズの相殺は、特に高次の高調波において成立しない。そこで、波形21と波形22の実線波形に示すように、パルス増幅回路5とパルス増幅回路6のうちの少なくとも一方の立ち上がりか立ち下がりのうちの少なくとも一方の時間を長くしたり又は短くすれば、波形の相殺効果を向上することができる。この出力信号波形の改良の方法は、当該エンジニアであれば容易に類推できるものである。

本実施例におけるパルス増幅回路5とパルス増幅回路6の回路例を図15に示す。図15においては、PWM回路の出力に相当する入力信号源51からのパルス信号に基づいて、出力MOSFET52と出力MOSFET53が交互に開閉して、出力端子54からは電源55の電圧Vか、或いは接地電位である零Vが出力される。その際、例えば高圧側のMOSFET53には、電圧レベルシフト用の結合コンデンサ531や遮断用の抵抗532から成るRC回路が付加される。ここで、MOSFET53の入力端子となっているゲート・ソース間に新たにコンデンサを並列接続すれば、入力パルス電圧が鈍ってMOSFET53の導通が遅くなって、出力端子54に現れる出力電圧の立ち上がりが遅くなる。逆に、コンデンサ531の容量値を大きくすることによって、出力電圧の立ち上がりを速くすることもできる。図15に示した回路例の等価回路を図16に示す。基本的にMOSFET52とMOSFET53はそれぞれがスイッチ回路として動作しているので、図16においては入力信号源51によって制御されたスイッチ素子520とスイッチ素子530に相当する。スイッチ素子はその導通時に導通抵抗と見なせるが、その抵抗値はMOSFETの大きさやチャネル領域の形状によって自由に設計できる。従って、図15に示したMOSFET52の導通抵抗をMOSFET53に対して高めに設計することによって、図14に示した波形21と波形22の実線部分も実現できる。波形21と波形22を実現するためには、PWM回路3とPWM回路4を構成する比較器の出力特性を調整するなど、パルス信号経路上の回路であれば自由に設計可能である。さらには、LPF7とLPF8の設計改良によっても実現可能であり、パルス増幅回路5とパルス増幅回路6の後段でも負荷9の前段であれば本発明は実施可能である。

さらに、出力パルス信号の信号形態を変えることでノイズ低減効果を一層向上させることが可能な本発明に係る増幅器の第10の実施例の回路図を図17に示す。図17の実施例では、MOSFET52とMOSFET53のソース端子に電流制限抵抗521と電流制限抵抗533を接続している。本実施例の等価回路を図18に示す。図18に示されるように、図17に示すMOSFET52とMOSFET53はそれぞれ、入力信号源51によって制御された電流源522と電流源534に相当する。パルス増幅回路5とパルス増幅回路6の出力素子を電流源特性に代えることによって、出力素子の開閉時に電源55や接地点に流れるスイッチング電流を大幅に抑制して、電流性ノイズの発生を大幅に抑えることができる。図15に示したような電圧出力特性も備えた一般的なパルス増幅回路5とパルス増幅回路6においては、出力電圧の急峻な立ち上がりと立ち下がりに伴って回路各部の寄生容量の充放電電流は増大して、大きな電流性ノイズの発生は避けられなかった。電流性ノイズの低減によって、回路各部に必要であったノイズ対策部品を大幅に削除できる。また、負荷9の前に設けるLPFにも、よりノイズ抑制効果の高い回路を用いることができる。

図19に示した変形実施例においては、入力側にもコンデンサを付加してノイズ低減効果を高めたπ型回路のLPF71とLPF81を用いている。一般的な電圧出力特性を備えたパルス増幅回路5とパルス増幅回路6をLPF71とLPF81に接続すると、入力側コンデンサを介して接地点に大きなノイズ電流が流れてノイズ放射の原因となる場合もあった。続いて、図20に示す変形実施例においては、入力端子対にコンデンサ73が並列付加されたノイズ低減効果の大きい2端子対型のLPF72を介して負荷9を駆動している。一般的な電圧出力特性を備えたパルス増幅回路5とパルス増幅回路6にLPF72を接続した場合には、LPFでのノイズの接地点への漏れこみはなくても、パルス増幅回路5とパルス増幅回路6の出力端子に流れる大きなノイズ性電流がパルス増幅回路の電源や接地点を介して周囲に漏れこむ恐れがあった。

次に、BPF(帯域通過フィルタ)を用いることによってノイズ低減効果を高めた本発明に係る増幅器の第11の実施例の回路図を図21に示す。負荷9を駆動する出力信号の周波数帯域が狭い場合には、LPFに替えて、より高いQ特性によってノイズ成分を大幅に抑制できるBPF101を用いることができる。BPF101の例としては、図21に図示した如くコイル102とコンデンサ103から成る2端子対形のフィルタ回路も適用できる。しかし、コイル102とコンデンサ103の並列接続回路の一方の端子を接地したフィルタ回路を二つ或いは一つ設けて、それらの他の端子をそれぞれにパルス増幅回路5とパルス増幅回路6の出力の少なくともどちらか一方と負荷9の間に接続したBPFを用いることもできる。さらにLPFも挿入することによって、さらなるノイズ低減を図ることも可能である。

さらに、特定の周波数の出力信号に対する力率が高い共振性の負荷を用いることによって、ノイズ発生を抑えた本発明に係る増幅器の第12の実施例の回路図を図22に示す。図22においては、アンテナなどの並列共振特性を有する負荷91を使用する場合であり、この負荷91をインダクタンス92とキャパシタンス93の並列回路を用いて示している。用意された負荷94にコイルとコンデンサを並列付加することによって共振性特性を実現してもよい。同様な変形回路例である図23においては、圧電スピーカーなどといった直列共振特性を有する負荷95をインダクタンス96とキャパシタンス97の直列回路を用いて示している。駆動すべき負荷94にコイルとコンデンサを直列接続することによって共振性特性を実現してもよい。

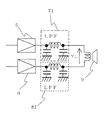

続いて、複数ではなく単一のパルス増幅回路を用いることによってもノイズを大幅に低減できる本発明に係る増幅器の第13の実施例の概略ブロック図を図24に示す。本実施例では図24に図示する如く、駆動電力を供給すべく電力素子を用いて構成されるためにコストが高くなるパルス増幅回路を57に示すように1回路のみ設けているため、増幅器の大幅なコスト削減が可能となる。パルス増幅回路57の出力端子は負荷9と単一のLPF7の直列接続を介して接地される。ただし、図示した通り、パルス増幅回路57には二つの入力端子が設けられ、それぞれの入力端子には二つのPWM回路3とPWM回路4のそれぞれの出力ラインAと出力ラインBが接続される。パルス増幅回路57の具体的な回路構成を図26に示す。図26において、MOSFET571を導通させて出力電圧をVとし、MOSFET574の導通により出力電圧を−Vとしている。また、MOSFET572とMOSFET573を同時に導通させることによって、出力電圧を接地電位にすると共に、吸い込み(シンク)と流し出し(ソース)の電流出力を可能としている。図26に示したそれぞれのMOSFETの入力端子Pと入力端子Gと入力端子Nの信号レベルを検討するために、図25に示した第1の実施例による増幅器の内部信号Aと内部信号Bと出力電圧VOの関係を再現する際の信号関係を表1に示す。

表1に示した信号関係を実現する論理回路の実施例が、図26に示すゲート回路5771からゲート回路5774より成る回路構成となる。図24に示すLPF7には前述のLPFの全ての実施例が適用可能である。また、出力信号V

Oに信号周波数における負帰還を掛けない場合であれば、パルス増幅回路57から負荷9までの信号経路が極めて短くノイズ発生が問題とならない場合や、或いは負荷9自体の帯域制約(スピーカーの振動板の機械的速度限界)や負荷9からの出力形態における周波数制限(聴覚の高域限界)がある場合には、LPF7を削除して直接にパルス増幅回路57と負荷9を接続することも可能である。

さらに、増幅器の歪を抑制しつつ単一のパルス増幅回路を用いてノイズを大幅に低減できる本発明に係る増幅器の第14の実施例の概略ブロック図を図27に示す。図27においては、パルス増幅回路57の出力をLPF7を介して負荷9に印加すると共に、負荷への印加電圧を帰還した演算増幅器11に負帰還を施している。本実施例においても、LPF7を短絡して削除することは可能である。従って、パルス増幅回路の出力を直接に演算増幅器11に接続することも可能である。或いは新たに信号帰還専用に設けたLPFを介してパルス増幅回路の出力を演算増幅器11に接続することも可能であることは言うまでもない。

さらに、回路規模を抑えて単一のパルス増幅回路によってもノイズを大幅に低減できる本発明に係る増幅器の第15の実施例の回路図を図28に示す。図28に示すパルス増幅回路おいては、出力電圧を接地レベルに固定するための出力素子を削除し、出力MOSFETには571と574のみ用いている。負荷9が通常の電磁スピーカーなどの低インピーダンス部品であると共にその片端子が接地されている場合には、パルス増幅回路の出力をハイインピーダンスにするだけで出力電圧も急速に接地レベルに収束するので、接地用の駆動素子は省略可能である。

以上、本発明に係る増幅器の実施例について詳述したが、説明に用いた回路は必要に応じて電圧や電流の向きを変えることができると共に構成素子の極性も変え得ることは言うまでもない。また、回路に用いた素子もMOSFETに限らず、バイポーラトランジスタや接合型FETやIGBTなど任意の能動素子や集積回路に置き換えられることも言うまでもない。

本発明の第1の実施例を示す概略ブロック図である。

本発明の第1の実施例の信号を示す波形図とスペクトラム図である。

本発明の第1の実施例の詳細を示すブロック図である。

本発明の第1の実施例の他の詳細を示すブロック図である。

本発明の第1の実施例の動作原理を示す波形図である。

本発明の第1の実施例の動作原理を示す他の波形図である。

本発明の第2の実施例を示す概略ブロック図である。

本発明の第3の実施例を示す概略ブロック図である。

本発明の第4の実施例を示す概略ブロック図である。

本発明の第5の実施例を示す概略ブロック図である。

本発明の第6の実施例を示す概略ブロック図である。

本発明の第7の実施例を示す概略ブロック図である。

本発明の第8の実施例を示す概略ブロック図である。

本発明の第9の実施例を示す概略ブロック図である。

本発明の第9の実施例を説明するための回路図である。

本発明の第9の実施例を説明する図15の回路図の等価回路図である。

本発明の第10の実施例を示す回路図である。

本発明の第10の実施例を説明する図17の回路図の等価回路図である。

本発明の第10の実施例の変形回路図である。

本発明の第10の実施例の変形を示す他の回路図である。

本発明の第11の実施例を示す回路図である。

本発明の第12の実施例を示す回路図である。

本発明の第12の実施例の他の回路図である。

本発明の第13の実施例を示す概略ブロック図である。

本発明の第1の実施例での内部信号を追加したブロック図である。

本発明の第13の実施例の表1の信号関係を実現する回路図である。

本発明の第14の実施例を示す概略ブロック図である。

本発明の第15の実施例を示す回路図である。

従来例を示す概略ブロック図である。

従来例の信号を示す波形図とスペクトラム図である。

符号の説明

1、1a 入力信号源

2 信号反転回路

3、3a、3b、4、4a、4b PWM回路,

5、5a、6、6a、57 パルス増幅回路

7、7a、8、8a、10、71、72、81 LPF(低域通過フィルタ)

9、91、95 負荷

11、12 演算増幅器

31 基準信号源

32、41 コンパレータ

61a インバーター

101 BPF(帯域通過フィルタ)