JP5276992B2 - 半導体デバイスの製造方法 - Google Patents

半導体デバイスの製造方法 Download PDFInfo

- Publication number

- JP5276992B2 JP5276992B2 JP2008550830A JP2008550830A JP5276992B2 JP 5276992 B2 JP5276992 B2 JP 5276992B2 JP 2008550830 A JP2008550830 A JP 2008550830A JP 2008550830 A JP2008550830 A JP 2008550830A JP 5276992 B2 JP5276992 B2 JP 5276992B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- dielectric

- applying

- electrode

- semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 42

- 238000004519 manufacturing process Methods 0.000 title claims description 21

- 239000000463 material Substances 0.000 claims description 83

- 238000000034 method Methods 0.000 claims description 72

- 229910052751 metal Inorganic materials 0.000 claims description 44

- 239000002184 metal Substances 0.000 claims description 44

- 239000010409 thin film Substances 0.000 claims description 42

- 239000003054 catalyst Substances 0.000 claims description 29

- 239000000758 substrate Substances 0.000 claims description 28

- 238000000151 deposition Methods 0.000 claims description 23

- 239000003989 dielectric material Substances 0.000 claims description 23

- -1 epoxide compound Chemical class 0.000 claims description 15

- 239000004020 conductor Substances 0.000 claims description 12

- 230000008021 deposition Effects 0.000 claims description 12

- 238000000059 patterning Methods 0.000 claims description 11

- 150000001412 amines Chemical class 0.000 claims description 5

- 125000002887 hydroxy group Chemical group [H]O* 0.000 claims description 4

- LSNNMFCWUKXFEE-UHFFFAOYSA-M Bisulfite Chemical compound OS([O-])=O LSNNMFCWUKXFEE-UHFFFAOYSA-M 0.000 claims description 3

- 150000002923 oximes Chemical class 0.000 claims description 3

- 150000003003 phosphines Chemical class 0.000 claims 1

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 23

- 230000008569 process Effects 0.000 description 21

- 238000007639 printing Methods 0.000 description 19

- 150000002118 epoxides Chemical class 0.000 description 17

- 239000000126 substance Substances 0.000 description 14

- 238000007772 electroless plating Methods 0.000 description 12

- 229910052763 palladium Inorganic materials 0.000 description 12

- 238000000813 microcontact printing Methods 0.000 description 10

- 229920000642 polymer Polymers 0.000 description 10

- 238000002174 soft lithography Methods 0.000 description 10

- BRLQWZUYTZBJKN-UHFFFAOYSA-N Epichlorohydrin Chemical compound ClCC1CO1 BRLQWZUYTZBJKN-UHFFFAOYSA-N 0.000 description 8

- 125000000217 alkyl group Chemical group 0.000 description 8

- IISBACLAFKSPIT-UHFFFAOYSA-N bisphenol A Chemical compound C=1C=C(O)C=CC=1C(C)(C)C1=CC=C(O)C=C1 IISBACLAFKSPIT-UHFFFAOYSA-N 0.000 description 8

- PXKLMJQFEQBVLD-UHFFFAOYSA-N bisphenol F Chemical compound C1=CC(O)=CC=C1CC1=CC=C(O)C=C1 PXKLMJQFEQBVLD-UHFFFAOYSA-N 0.000 description 8

- 239000000976 ink Substances 0.000 description 8

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 7

- 229910052737 gold Inorganic materials 0.000 description 7

- 239000010931 gold Substances 0.000 description 7

- 238000007650 screen-printing Methods 0.000 description 7

- 239000003153 chemical reaction reagent Substances 0.000 description 6

- 229920001577 copolymer Polymers 0.000 description 6

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical group [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 6

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 5

- 238000007641 inkjet printing Methods 0.000 description 5

- 238000009413 insulation Methods 0.000 description 5

- 238000007747 plating Methods 0.000 description 5

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Substances [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 5

- 229910052709 silver Inorganic materials 0.000 description 5

- 238000011282 treatment Methods 0.000 description 5

- STMDPCBYJCIZOD-UHFFFAOYSA-N 2-(2,4-dinitroanilino)-4-methylpentanoic acid Chemical compound CC(C)CC(C(O)=O)NC1=CC=C([N+]([O-])=O)C=C1[N+]([O-])=O STMDPCBYJCIZOD-UHFFFAOYSA-N 0.000 description 4

- HDPLHDGYGLENEI-UHFFFAOYSA-N 2-[1-(oxiran-2-ylmethoxy)propan-2-yloxymethyl]oxirane Chemical compound C1OC1COC(C)COCC1CO1 HDPLHDGYGLENEI-UHFFFAOYSA-N 0.000 description 4

- AOBIOSPNXBMOAT-UHFFFAOYSA-N 2-[2-(oxiran-2-ylmethoxy)ethoxymethyl]oxirane Chemical compound C1OC1COCCOCC1CO1 AOBIOSPNXBMOAT-UHFFFAOYSA-N 0.000 description 4

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 4

- CTKINSOISVBQLD-UHFFFAOYSA-N Glycidol Chemical compound OCC1CO1 CTKINSOISVBQLD-UHFFFAOYSA-N 0.000 description 4

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical compound Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 4

- CERQOIWHTDAKMF-UHFFFAOYSA-M Methacrylate Chemical compound CC(=C)C([O-])=O CERQOIWHTDAKMF-UHFFFAOYSA-M 0.000 description 4

- 239000011248 coating agent Substances 0.000 description 4

- 238000000576 coating method Methods 0.000 description 4

- 150000001875 compounds Chemical class 0.000 description 4

- 229910052802 copper Inorganic materials 0.000 description 4

- 239000010949 copper Substances 0.000 description 4

- 238000005516 engineering process Methods 0.000 description 4

- 239000003822 epoxy resin Substances 0.000 description 4

- 150000002148 esters Chemical class 0.000 description 4

- 239000011521 glass Substances 0.000 description 4

- 229910052759 nickel Inorganic materials 0.000 description 4

- RPQRDASANLAFCM-UHFFFAOYSA-N oxiran-2-ylmethyl prop-2-enoate Chemical compound C=CC(=O)OCC1CO1 RPQRDASANLAFCM-UHFFFAOYSA-N 0.000 description 4

- 238000000206 photolithography Methods 0.000 description 4

- 229920000647 polyepoxide Polymers 0.000 description 4

- 150000003839 salts Chemical class 0.000 description 4

- 239000004332 silver Substances 0.000 description 4

- 150000003573 thiols Chemical class 0.000 description 4

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 4

- MECNWXGGNCJFQJ-UHFFFAOYSA-N 3-piperidin-1-ylpropane-1,2-diol Chemical compound OCC(O)CN1CCCCC1 MECNWXGGNCJFQJ-UHFFFAOYSA-N 0.000 description 3

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 3

- IAYPIBMASNFSPL-UHFFFAOYSA-N Ethylene oxide Chemical compound C1CO1 IAYPIBMASNFSPL-UHFFFAOYSA-N 0.000 description 3

- KFZMGEQAYNKOFK-UHFFFAOYSA-N Isopropanol Chemical compound CC(C)O KFZMGEQAYNKOFK-UHFFFAOYSA-N 0.000 description 3

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 3

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 3

- 229920001940 conductive polymer Polymers 0.000 description 3

- 239000008367 deionised water Substances 0.000 description 3

- 229910021641 deionized water Inorganic materials 0.000 description 3

- 239000006185 dispersion Substances 0.000 description 3

- 238000007646 gravure printing Methods 0.000 description 3

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 3

- 229910052697 platinum Inorganic materials 0.000 description 3

- 239000002861 polymer material Substances 0.000 description 3

- 230000000379 polymerizing effect Effects 0.000 description 3

- 229910052710 silicon Inorganic materials 0.000 description 3

- 239000010703 silicon Substances 0.000 description 3

- 238000004528 spin coating Methods 0.000 description 3

- CSCPPACGZOOCGX-UHFFFAOYSA-N Acetone Chemical compound CC(C)=O CSCPPACGZOOCGX-UHFFFAOYSA-N 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- RTZKZFJDLAIYFH-UHFFFAOYSA-N Diethyl ether Chemical compound CCOCC RTZKZFJDLAIYFH-UHFFFAOYSA-N 0.000 description 2

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 2

- 239000000654 additive Substances 0.000 description 2

- 230000000996 additive effect Effects 0.000 description 2

- 238000000137 annealing Methods 0.000 description 2

- 230000009286 beneficial effect Effects 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- UHYPYGJEEGLRJD-UHFFFAOYSA-N cadmium(2+);selenium(2-) Chemical compound [Se-2].[Cd+2] UHYPYGJEEGLRJD-UHFFFAOYSA-N 0.000 description 2

- 229910052799 carbon Inorganic materials 0.000 description 2

- 150000001244 carboxylic acid anhydrides Chemical class 0.000 description 2

- 230000007797 corrosion Effects 0.000 description 2

- 238000005260 corrosion Methods 0.000 description 2

- 230000007547 defect Effects 0.000 description 2

- 238000005137 deposition process Methods 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 229920001971 elastomer Polymers 0.000 description 2

- 230000007613 environmental effect Effects 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- 238000010438 heat treatment Methods 0.000 description 2

- FFUAGWLWBBFQJT-UHFFFAOYSA-N hexamethyldisilazane Chemical compound C[Si](C)(C)N[Si](C)(C)C FFUAGWLWBBFQJT-UHFFFAOYSA-N 0.000 description 2

- 239000007788 liquid Substances 0.000 description 2

- 229910021645 metal ion Inorganic materials 0.000 description 2

- 238000001465 metallisation Methods 0.000 description 2

- 150000002739 metals Chemical group 0.000 description 2

- 238000000845 micromoulding in capillary Methods 0.000 description 2

- 239000000178 monomer Substances 0.000 description 2

- XYFCBTPGUUZFHI-UHFFFAOYSA-N phosphine group Chemical group P XYFCBTPGUUZFHI-UHFFFAOYSA-N 0.000 description 2

- 229920000767 polyaniline Polymers 0.000 description 2

- 239000002904 solvent Substances 0.000 description 2

- WLOQLWBIJZDHET-UHFFFAOYSA-N triphenylsulfonium Chemical class C1=CC=CC=C1[S+](C=1C=CC=CC=1)C1=CC=CC=C1 WLOQLWBIJZDHET-UHFFFAOYSA-N 0.000 description 2

- 238000001771 vacuum deposition Methods 0.000 description 2

- OCJBOOLMMGQPQU-UHFFFAOYSA-N 1,4-dichlorobenzene Chemical compound ClC1=CC=C(Cl)C=C1 OCJBOOLMMGQPQU-UHFFFAOYSA-N 0.000 description 1

- WUPHOULIZUERAE-UHFFFAOYSA-N 3-(oxolan-2-yl)propanoic acid Chemical compound OC(=O)CCC1CCCO1 WUPHOULIZUERAE-UHFFFAOYSA-N 0.000 description 1

- 239000004593 Epoxy Substances 0.000 description 1

- 229910021626 Tin(II) chloride Inorganic materials 0.000 description 1

- ZJCCRDAZUWHFQH-UHFFFAOYSA-N Trimethylolpropane Chemical compound CCC(CO)(CO)CO ZJCCRDAZUWHFQH-UHFFFAOYSA-N 0.000 description 1

- 238000003848 UV Light-Curing Methods 0.000 description 1

- 239000002253 acid Substances 0.000 description 1

- 230000002378 acidificating effect Effects 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 239000003513 alkali Substances 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- 239000012298 atmosphere Substances 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 229910052793 cadmium Inorganic materials 0.000 description 1

- BDOSMKKIYDKNTQ-UHFFFAOYSA-N cadmium atom Chemical compound [Cd] BDOSMKKIYDKNTQ-UHFFFAOYSA-N 0.000 description 1

- 229910052980 cadmium sulfide Inorganic materials 0.000 description 1

- 239000002041 carbon nanotube Substances 0.000 description 1

- 229910021393 carbon nanotube Inorganic materials 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 230000003197 catalytic effect Effects 0.000 description 1

- 150000004770 chalcogenides Chemical class 0.000 description 1

- 239000003638 chemical reducing agent Substances 0.000 description 1

- 239000003795 chemical substances by application Substances 0.000 description 1

- 239000000084 colloidal system Substances 0.000 description 1

- 238000002508 contact lithography Methods 0.000 description 1

- 238000001723 curing Methods 0.000 description 1

- 230000006378 damage Effects 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 230000000593 degrading effect Effects 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- SWXVUIWOUIDPGS-UHFFFAOYSA-N diacetone alcohol Natural products CC(=O)CC(C)(C)O SWXVUIWOUIDPGS-UHFFFAOYSA-N 0.000 description 1

- 229940117389 dichlorobenzene Drugs 0.000 description 1

- 125000005594 diketone group Chemical group 0.000 description 1

- 239000000806 elastomer Substances 0.000 description 1

- 239000010411 electrocatalyst Substances 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 239000010408 film Substances 0.000 description 1

- 229910002804 graphite Inorganic materials 0.000 description 1

- 239000010439 graphite Substances 0.000 description 1

- 238000013007 heat curing Methods 0.000 description 1

- 238000007654 immersion Methods 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 229910003437 indium oxide Inorganic materials 0.000 description 1

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 1

- 230000000977 initiatory effect Effects 0.000 description 1

- 238000013532 laser treatment Methods 0.000 description 1

- 238000002386 leaching Methods 0.000 description 1

- 229910052981 lead sulfide Inorganic materials 0.000 description 1

- 229940056932 lead sulfide Drugs 0.000 description 1

- 238000001459 lithography Methods 0.000 description 1

- 231100000053 low toxicity Toxicity 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 238000004377 microelectronic Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 239000002074 nanoribbon Substances 0.000 description 1

- 239000002073 nanorod Substances 0.000 description 1

- 229910000510 noble metal Inorganic materials 0.000 description 1

- SLIUAWYAILUBJU-UHFFFAOYSA-N pentacene Chemical compound C1=CC=CC2=CC3=CC4=CC5=CC=CC=C5C=C4C=C3C=C21 SLIUAWYAILUBJU-UHFFFAOYSA-N 0.000 description 1

- XHTJLMYQJHCUPE-UHFFFAOYSA-N phosphanylphosphonic acid Chemical compound OP(O)(P)=O XHTJLMYQJHCUPE-UHFFFAOYSA-N 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 230000010287 polarization Effects 0.000 description 1

- 229920000301 poly(3-hexylthiophene-2,5-diyl) polymer Polymers 0.000 description 1

- 229920000553 poly(phenylenevinylene) Polymers 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920002635 polyurethane Polymers 0.000 description 1

- 239000004814 polyurethane Substances 0.000 description 1

- 239000002243 precursor Substances 0.000 description 1

- 230000001603 reducing effect Effects 0.000 description 1

- 229920006395 saturated elastomer Polymers 0.000 description 1

- 229920002379 silicone rubber Polymers 0.000 description 1

- 239000004945 silicone rubber Substances 0.000 description 1

- 235000011150 stannous chloride Nutrition 0.000 description 1

- 239000012974 tin catalyst Substances 0.000 description 1

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 1

- 229910001887 tin oxide Inorganic materials 0.000 description 1

- AXZWODMDQAVCJE-UHFFFAOYSA-L tin(II) chloride (anhydrous) Chemical compound [Cl-].[Cl-].[Sn+2] AXZWODMDQAVCJE-UHFFFAOYSA-L 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- 229910052723 transition metal Inorganic materials 0.000 description 1

- 150000003623 transition metal compounds Chemical class 0.000 description 1

- 150000003624 transition metals Chemical class 0.000 description 1

- 238000005406 washing Methods 0.000 description 1

- 239000002699 waste material Substances 0.000 description 1

- 239000011787 zinc oxide Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K10/00—Organic devices specially adapted for rectifying, amplifying, oscillating or switching; Organic capacitors or resistors having potential barriers

- H10K10/80—Constructional details

- H10K10/82—Electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K71/00—Manufacture or treatment specially adapted for the organic devices covered by this subclass

- H10K71/60—Forming conductive regions or layers, e.g. electrodes

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y10/00—Nanotechnology for information processing, storage or transmission, e.g. quantum computing or single electron logic

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K10/00—Organic devices specially adapted for rectifying, amplifying, oscillating or switching; Organic capacitors or resistors having potential barriers

- H10K10/40—Organic transistors

- H10K10/46—Field-effect transistors, e.g. organic thin-film transistors [OTFT]

- H10K10/462—Insulated gate field-effect transistors [IGFETs]

- H10K10/466—Lateral bottom-gate IGFETs comprising only a single gate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K10/00—Organic devices specially adapted for rectifying, amplifying, oscillating or switching; Organic capacitors or resistors having potential barriers

- H10K10/40—Organic transistors

- H10K10/46—Field-effect transistors, e.g. organic thin-film transistors [OTFT]

- H10K10/462—Insulated gate field-effect transistors [IGFETs]

- H10K10/468—Insulated gate field-effect transistors [IGFETs] characterised by the gate dielectrics

- H10K10/471—Insulated gate field-effect transistors [IGFETs] characterised by the gate dielectrics the gate dielectric comprising only organic materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K71/00—Manufacture or treatment specially adapted for the organic devices covered by this subclass

- H10K71/10—Deposition of organic active material

- H10K71/12—Deposition of organic active material using liquid deposition, e.g. spin coating

- H10K71/13—Deposition of organic active material using liquid deposition, e.g. spin coating using printing techniques, e.g. ink-jet printing or screen printing

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66742—Thin film unipolar transistors

- H01L29/6675—Amorphous silicon or polysilicon transistors

- H01L29/66765—Lateral single gate single channel transistors with inverted structure, i.e. the channel layer is formed after the gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78681—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising AIIIBV or AIIBVI or AIVBVI semiconductor materials, or Se or Te

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Chemical & Material Sciences (AREA)

- Physics & Mathematics (AREA)

- Nanotechnology (AREA)

- Computer Hardware Design (AREA)

- Ceramic Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Theoretical Computer Science (AREA)

- Mathematical Physics (AREA)

- Crystallography & Structural Chemistry (AREA)

- Materials Engineering (AREA)

- Thin Film Transistor (AREA)

- Electrodes Of Semiconductors (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Junction Field-Effect Transistors (AREA)

Description

(i)前記デバイス内の支持層の選択されたエリアのみにパターン化材料を付与して、前記第1電極層の構成体を画成するステップと、

(ii)前記パターン化材料に応答する触媒を前記支持層に付与するステップと、

(iii)前記支持層に導電性材料を付与して、前記第1電極層を形成するステップと、

を備え、前記支持層、パターン化材料、及び触媒が協働して、この触媒が付与された前記支持層の選択されたエリアのみに前記導電性材料が堆積されるようにする方法、が新たに提案される。

(iv)誘電体層の少なくとも一部分に半導体材料を付与することにより半導体層を形成して、第1及び第2の金属電極との電気的接触をなす、

という更に別のステップを備えるのが効果的である。

(iv)基板層の少なくとも一部分に半導体材料を付与することにより半導体層を形成して、第1及び第2の金属電極との電気的接触をなし、

(v)半導体層に誘電体材料を付与して誘電体層を形成し、

(vi)誘電体層に実質的に導電性の電極を付与することにより第2電極層を形成する、

という更に別のステップを備えるのが便利である。

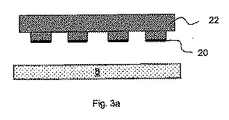

(i)実質的に導電性のゲート電極を準備するステップと、

(ii)前記ゲート電極の少なくとも一部分にエポキシドポリマーを堆積してゲート絶縁層を形成するステップと、

(iii)前記ゲート絶縁層の選択されたエリアのみにパターン化材料を印刷し、このパターン化材料がそこに接着して、その付与された領域においてその表面エネルギーを変調するようにするステップと、

(iv)前記パターン化材料に応答する触媒を前記ゲート絶縁層に付与するステップと、

(v)無電解堆積により前記ゲート絶縁層に金属材料を堆積し、前記触媒材料が付与された前記ゲート絶縁層の選択されたエリアのみにソース及びドレイン電極を形成するステップと、

を備えた方法、が新たに提案される。

(vi)前記ゲート絶縁層の少なくとも一部分に半導体層を設けて、それらの間にソース及びドレイン電極をサンドイッチすると共に、前記ソース及びドレイン電極を橋絡する、

というステップを更に含むのが便利である。

Claims (12)

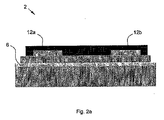

- 第1電極層が接触し且つ第2電極層が誘電体層(8)により分離されている半導体層(14)を含む多層半導体デバイスのための電極構造体を製造する方法において、

(i)支持層の選択されたエリアのみにパターン化材料(20)を付与して、前記第1電極層の構成体を画成するステップと、

(ii)前記パターン化材料(20)に応答するようにされた触媒(24)を前記支持層に付与するステップと、

(iii)前記支持層に導電性材料(26)を付与して、前記第1電極層を形成するステップと、

を備え、前記支持層、前記パターン化材料(20)、及び前記触媒(24)が協働して、前記触媒(24)が付与された前記支持層の選択されたエリアのみに前記導電性材料(26)が堆積されるようにし、前記支持層は、エポキシド化合物を含み、前記支持層に前記導電性材料(26)を付与するステップは、無電解堆積を含む方法。 - 前記支持層は、誘電体層(8)を含む、請求項1に記載の方法。

- 前記第2電極層を形成し、そこに誘電体材料を付与して、誘電体層(8)を形成する初期ステップを更に備えた、請求項2に記載の方法。

- 前記誘電体層(8)に導電性材料(26)を堆積して、第1及び第2の金属電極(12a,12b)を形成し、そして更に、

(iv)前記誘電体層(8)の少なくとも一部分に半導体材料を付与することにより前記半導体層(14)を形成して、前記第1及び第2の金属電極(12a, 12b)との電気的接触をなすステップ、

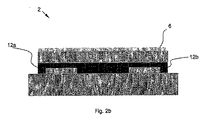

を備えた請求項3に記載の方法。 - 前記支持層は、基板層(4)を含む、請求項1に記載の方法。

- 前記基板層(4)に導電性材料(26)を堆積して、第1及び第2の金属電極(12a,12b)を形成し、そして更に、

(iv)前記基板層(4)の少なくとも一部分に半導体材料を付与することにより前記半導体層(14)を形成して、前記第1及び第2の金属電極(12a,12b)との電気的接触をなすステップと、

(v)前記半導体層(14)に誘電体材料を付与して誘電体層(8)を形成するステップと、

(vi)前記誘電体層(8)に実質的に導電性の電極(6)を付与することにより前記第2電極層を形成するステップと、

を備えた請求項5に記載の方法。 - 前記半導体デバイスは、前記第2電極層が実質的に導電性のゲート電極(6)を形成し、そして前記第1及び第2の金属電極(12a,12b)が各々ソース及びドレインを形成するような薄膜トランジスタ(2)として構成された、請求項1から6のいずれかに記載の方法。

- 前記誘電体材料は、エポキシド化合物を含む、請求項3、4、6又は7に記載の方法。

- 前記誘電体材料は、1ないし12の範囲の官能性を有するエポキシド化合物を含む、請求項8に記載の方法。

- 前記パターン化材料(20)は、表面ヒドロキシルグループに取り付けるようにされる、請求項1から9のいずれかに記載の方法。

- 前記パターン化材料(20)は、金属の無電解堆積に対して触媒作用する材料を結合するようにされる、請求項1から10のいずれかに記載の方法。

- 前記パターン化材料(20)は、スルフォン酸材料、トリハロシラン材料、及びトリアルコキシシラン材料の少なくとも1つを含み、トリアルコキシシランは、1つ以上のアミン、アミノカルボキシチオール、ジケトネート、オキシム又は置換ホスフィングループで置換されたものである、請求項1から11のいずれかに記載の方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| GB0601008.6 | 2006-01-18 | ||

| GBGB0601008.6A GB0601008D0 (en) | 2006-01-18 | 2006-01-18 | Method of fabricating a semicondutor device |

| PCT/GB2007/000080 WO2007083087A1 (en) | 2006-01-18 | 2007-01-12 | Method of fabricating a semiconductor device |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009524231A JP2009524231A (ja) | 2009-06-25 |

| JP2009524231A5 JP2009524231A5 (ja) | 2010-03-04 |

| JP5276992B2 true JP5276992B2 (ja) | 2013-08-28 |

Family

ID=36010525

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008550830A Expired - Fee Related JP5276992B2 (ja) | 2006-01-18 | 2007-01-12 | 半導体デバイスの製造方法 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US20100320463A1 (ja) |

| EP (1) | EP1974400B1 (ja) |

| JP (1) | JP5276992B2 (ja) |

| KR (1) | KR20080100195A (ja) |

| GB (1) | GB0601008D0 (ja) |

| TW (1) | TW200733207A (ja) |

| WO (1) | WO2007083087A1 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8608972B2 (en) | 2006-12-05 | 2013-12-17 | Nano Terra Inc. | Method for patterning a surface |

| JP2009111000A (ja) * | 2007-10-26 | 2009-05-21 | Konica Minolta Holdings Inc | 有機半導体素子の製造方法、及び有機半導体素子 |

| US9899339B2 (en) * | 2012-11-05 | 2018-02-20 | Texas Instruments Incorporated | Discrete device mounted on substrate |

| JP5656966B2 (ja) * | 2012-12-05 | 2015-01-21 | 独立行政法人科学技術振興機構 | 電界効果トランジスタ及びその製造方法 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2001033649A1 (en) * | 1999-11-02 | 2001-05-10 | Koninklijke Philips Electronics N.V. | Method of producing vertical interconnects between thin film microelectronic devices and products comprising such vertical interconnects |

| EP1276824A4 (en) * | 2000-04-21 | 2005-03-16 | Stc Unm | PROTOTYPING OF STRUCTURED, FUNCTIONAL NANOSTRUCTURES |

| US6586791B1 (en) * | 2000-07-19 | 2003-07-01 | 3M Innovative Properties Company | Transistor insulator layer incorporating superfine ceramic particles |

| DE10126860C2 (de) * | 2001-06-01 | 2003-05-28 | Siemens Ag | Organischer Feldeffekt-Transistor, Verfahren zu seiner Herstellung und Verwendung zum Aufbau integrierter Schaltungen |

| US6767828B2 (en) * | 2001-10-05 | 2004-07-27 | International Business Machines Corporation | Method for forming patterns for semiconductor devices |

| US6617609B2 (en) * | 2001-11-05 | 2003-09-09 | 3M Innovative Properties Company | Organic thin film transistor with siloxane polymer interface |

| US6946676B2 (en) * | 2001-11-05 | 2005-09-20 | 3M Innovative Properties Company | Organic thin film transistor with polymeric interface |

| US6949762B2 (en) * | 2002-01-11 | 2005-09-27 | Xerox Corporation | Polythiophenes and devices thereof |

| JP2005086147A (ja) * | 2003-09-11 | 2005-03-31 | Sony Corp | 金属単層膜形成方法、配線形成方法、及び、電界効果型トランジスタの製造方法 |

| JP4407311B2 (ja) * | 2004-02-20 | 2010-02-03 | セイコーエプソン株式会社 | 薄膜トランジスタの製造方法 |

| US20050279995A1 (en) * | 2004-06-21 | 2005-12-22 | Samsung Electronics Co., Ltd. | Composition for preparing organic insulating film and organic insulating film prepared from the same |

| KR100560796B1 (ko) * | 2004-06-24 | 2006-03-13 | 삼성에스디아이 주식회사 | 유기 박막트랜지스터 및 그의 제조방법 |

-

2006

- 2006-01-18 GB GBGB0601008.6A patent/GB0601008D0/en not_active Ceased

-

2007

- 2007-01-10 TW TW096100920A patent/TW200733207A/zh unknown

- 2007-01-12 EP EP07700370A patent/EP1974400B1/en not_active Not-in-force

- 2007-01-12 JP JP2008550830A patent/JP5276992B2/ja not_active Expired - Fee Related

- 2007-01-12 US US12/161,191 patent/US20100320463A1/en not_active Abandoned

- 2007-01-12 KR KR1020087020173A patent/KR20080100195A/ko not_active Application Discontinuation

- 2007-01-12 WO PCT/GB2007/000080 patent/WO2007083087A1/en active Application Filing

Also Published As

| Publication number | Publication date |

|---|---|

| US20100320463A1 (en) | 2010-12-23 |

| EP1974400B1 (en) | 2013-03-13 |

| JP2009524231A (ja) | 2009-06-25 |

| TW200733207A (en) | 2007-09-01 |

| GB0601008D0 (en) | 2006-03-01 |

| WO2007083087A1 (en) | 2007-07-26 |

| KR20080100195A (ko) | 2008-11-14 |

| EP1974400A1 (en) | 2008-10-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100707775B1 (ko) | 박막 트랜지스터, 배선 기판, 표시 장치, 전자 기기 및 박막 트랜지스터의 제조 방법 | |

| JP4636921B2 (ja) | 表示装置の製造方法、表示装置および電子機器 | |

| US7186634B2 (en) | Method for forming metal single-layer film, method for forming wiring, and method for producing field effect transistors | |

| EP2122672B1 (en) | Laminate structure and its manufacturing method | |

| JP2011216647A (ja) | パターン形成体の製造方法、機能性素子の製造方法および半導体素子の製造方法 | |

| JP5638565B2 (ja) | ポリマー薄膜における自己整合ビアホールの形成 | |

| JP5168845B2 (ja) | 積層構造体、積層構造体を用いた電子素子、これらの製造方法、電子素子アレイ及び表示装置 | |

| US10707079B2 (en) | Orthogonal patterning method | |

| JP5276992B2 (ja) | 半導体デバイスの製造方法 | |

| JP4730275B2 (ja) | 薄膜トランジスタおよび薄膜トランジスタの製造方法 | |

| KR100803426B1 (ko) | 기판 및 그 제조 방법과 표시 장치 및 그 제조 방법 | |

| JP2013016773A (ja) | 配線部材、および、電子素子の製造方法と、それを用いた配線部材、積層配線、電子素子、電子素子アレイ及び表示装置。 | |

| US9023683B2 (en) | Organic semiconductor transistor with epoxy-based organic resin planarization layer | |

| JP5325465B2 (ja) | 薄膜トランジスタおよびそれを用いた装置 | |

| KR101050588B1 (ko) | 유기절연막 패턴형성 방법 | |

| JP2011259001A (ja) | パターン形成体の製造方法、機能性素子の製造方法および半導体素子の製造方法 | |

| JP2006261528A (ja) | 有機薄膜トランジスタ、それを備えた表示装置および有機薄膜トランジスタの製造方法。 | |

| US20060240668A1 (en) | Semiconductor device with metallic electrodes and a method for use in forming such a device | |

| JP4691545B2 (ja) | 半導体装置の製造方法 | |

| CN111816767A (zh) | 有机半导体晶体管 | |

| JP5458296B2 (ja) | 微細加工構造及びその加工方法並びに電子デバイス及びその製造方法 | |

| CN117730406A (zh) | 金属布线的制造方法、晶体管的制造方法以及金属布线 | |

| KR20100075061A (ko) | 유기박막 트랜지스터 및 그 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100112 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100112 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101125 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120924 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121009 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20121211 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20121218 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130409 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130507 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130520 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |