JP5259333B2 - 波形等化量調整方法、波形等化量調整回路、半導体装置および情報ネットワーク装置 - Google Patents

波形等化量調整方法、波形等化量調整回路、半導体装置および情報ネットワーク装置 Download PDFInfo

- Publication number

- JP5259333B2 JP5259333B2 JP2008267825A JP2008267825A JP5259333B2 JP 5259333 B2 JP5259333 B2 JP 5259333B2 JP 2008267825 A JP2008267825 A JP 2008267825A JP 2008267825 A JP2008267825 A JP 2008267825A JP 5259333 B2 JP5259333 B2 JP 5259333B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- timing

- signal

- waveform equalization

- equalization amount

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Dc Digital Transmission (AREA)

- Cable Transmission Systems, Equalization Of Radio And Reduction Of Echo (AREA)

Description

特許文献1には、波形等化器の等化係数(タップ係数)を、パタン発生器を用いたトレーニングで求める発明が記載されている。

本発明の目的は、上記課題を解決する波形等化量調整方法および波形等化量調整回路ならびに半導体装置および情報ネットワーク装置を提供することにある。

Claims (4)

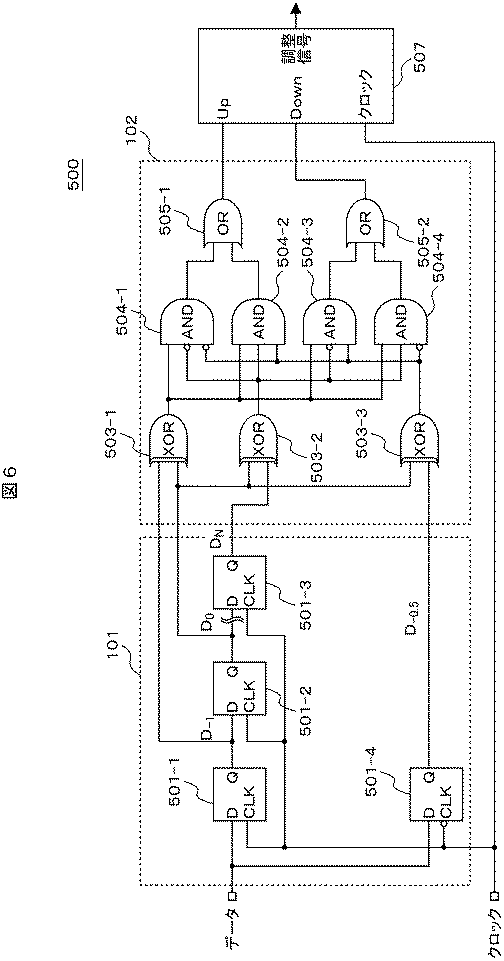

- 伝送損失による波形歪みを補正する波形等化回路の波形等化量調整方法であって、

受信データから再生されたクロックの第1のタイミングで第1のデータを取得するステップと、

前記第1のタイミングと1個のデータシンボル長遅れた第2のタイミングで第2のデータを取得するステップと、

前記第1のタイミングとN個のデータシンボル長早い第3のタイミングで第3のデータを取得するステップと、

前記第1のタイミングと半データシンボルより短い位相分を遅延した第4のタイミングで第4のデータを取得するステップと、

前記第1のタイミングと半データシンボルより長い位相分を遅延した第5のタイミングで第5のデータを取得するステップと、

取得した前記第1のデータないし前記第5のデータのデータセットのデータパタンを評価してUp信号とDown信号とを出力するステップと、

前記Up信号と前記Down信号との数をカウントするステップと、

前記データセットの数をカウントして所定のカウント数を満たしているかを評価するステップと、

カウントしたUp信号の数とDown信号の数との差分と所定の差分しきい値とを比較して波形等化量調整信号を出力するステップと、

を含み、

前記Up信号とDown信号とを出力するステップにおいて、前記第4のデータと、前記第5のデータとの間で符号が反転した場合、Up信号およびDown信号を出力しないことを特徴とする波形等化量調整方法。 - 受信データに係る波形等化量を調整するためのデータを取得するデータ取得部と、取得した前記データのデータパタンを評価してUp信号とDown信号とを出力するデータパタン評価部と、前記Up信号と前記Down信号との数をカウントするUp/Down信号カウント部と、前記データ取得部で取得したデータの数をカウントして所定のカウント数を満たしているかを評価する取得データ数判定部と、カウントしたUp信号の数とDown信号の数との差分と所定の差分しきい値とを比較して波形等化量調整信号を出力するUp/Down信号差分評価部と、を含んで構成され、

前記データ取得部は、

前記受信データから再生されたクロックの第1のタイミングで第1のデータを取得し、

前記第1のタイミングと1個のデータシンボル長遅れた第2のタイミングで第2のデータを取得し、

前記第1のタイミングとN個のデータシンボル長早い第3のタイミングで第3のデータを取得し、

前記第1のタイミングと半データシンボルより短い位相分を遅延した第4のタイミングで第4のデータを取得し、

前記第1のタイミングと半データシンボルより長い位相分を遅延した第5のタイミングで第5のデータを取得し、

前記データパタン評価部は、前記第4のデータと前記第5のデータとの間で符号が反転した場合、Up信号およびDown信号を出力しないことを特徴とする波形等化量調整回路。 - 通信用のインターフェースを備えた半導体装置において、

受信データに係る波形等化量を調整するためのデータを取得するデータ取得部と、取得した前記データのデータパタンを評価してUp信号とDown信号とを出力するデータパタン評価部と、前記Up信号と前記Down信号との数をカウントするUp/Down信号カウント部と、前記データ取得部で取得したデータの数をカウントして所定のカウント数を満たしているかを評価する取得データ数判定部と、カウントしたUp信号の数とDown信号の数との差分と所定の差分しきい値とを比較して波形等化量調整信号を出力するUp/Down信号差分評価部と、を含んで構成され、

前記データ取得部は、

前記受信データから再生されたクロックの第1のタイミングで第1のデータを取得し、

前記第1のタイミングと1個のデータシンボル長遅れた第2のタイミングで第2のデータを取得し、

前記第1のタイミングとN個のデータシンボル長早い第3のタイミングで第3のデータを取得し、

前記第1のタイミングと半データシンボルより短い位相分を遅延した第4のタイミングで第4のデータを取得し、

前記第1のタイミングと半データシンボルより長い位相分を遅延した第5のタイミングで第5のデータを取得し、

前記データパタン評価部は、前記第4のデータと前記第5のデータとの間で符号が反転した場合、Up信号およびDown信号を出力しない波形等化量調整回路を備えたことを特徴とする半導体装置。 - 通信用のインターフェースを備えた半導体装置を実装する第1および第2の実装基板と、前記第1の実装基板と前記第2の実装基板とを接続されたバックプレーン基板を含む情報ネットワーク装置において、

前記半導体装置は、受信データに係る波形等化量を調整するためのデータを取得するデータ取得部と、取得した前記データのデータパタンを評価してUp信号とDown信号とを出力するデータパタン評価部と、前記Up信号と前記Down信号との数をカウントするUp/Down信号カウント部と、前記データ取得部で取得したデータの数をカウントして所定のカウント数を満たしているかを評価する取得データ数判定部と、カウントしたUp信号の数とDown信号の数との差分と所定の差分しきい値とを比較して波形等化量調整信号を出力するUp/Down信号差分評価部と、を含んで構成され、

前記データ取得部は、

前記受信データから再生されたクロックの第1のタイミングで第1のデータを取得し、

前記第1のタイミングと1個のデータシンボル長遅れた第2のタイミングで第2のデータを取得し、

前記第1のタイミングとN個のデータシンボル長早い第3のタイミングで第3のデータを取得し、

前記第1のタイミングと半データシンボルより短い位相分を遅延した第4のタイミングで第4のデータを取得し、

前記第1のタイミングと半データシンボルより長い位相分を遅延した第5のタイミングで第5のデータを取得し、

前記データパタン評価部は、前記第4のデータと前記第5のデータとの間で符号が反転した場合、Up信号およびDown信号を出力しない波形等化量調整回路を備えたことを特徴とする情報ネットワーク装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008267825A JP5259333B2 (ja) | 2008-10-16 | 2008-10-16 | 波形等化量調整方法、波形等化量調整回路、半導体装置および情報ネットワーク装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008267825A JP5259333B2 (ja) | 2008-10-16 | 2008-10-16 | 波形等化量調整方法、波形等化量調整回路、半導体装置および情報ネットワーク装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010098532A JP2010098532A (ja) | 2010-04-30 |

| JP5259333B2 true JP5259333B2 (ja) | 2013-08-07 |

Family

ID=42259906

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008267825A Expired - Fee Related JP5259333B2 (ja) | 2008-10-16 | 2008-10-16 | 波形等化量調整方法、波形等化量調整回路、半導体装置および情報ネットワーク装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5259333B2 (ja) |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4331641B2 (ja) * | 2004-04-09 | 2009-09-16 | 富士通株式会社 | 等化回路を有する受信回路 |

| US7804894B2 (en) * | 2006-05-30 | 2010-09-28 | Fujitsu Limited | System and method for the adjustment of compensation applied to a signal using filter patterns |

| JP5540472B2 (ja) * | 2008-06-06 | 2014-07-02 | ソニー株式会社 | シリアルデータ受信機、利得制御回路および利得制御方法 |

-

2008

- 2008-10-16 JP JP2008267825A patent/JP5259333B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2010098532A (ja) | 2010-04-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8108710B2 (en) | Differential communication link with skew compensation circuit | |

| US7227375B2 (en) | DAC based driver with selectable pre-emphasis signal levels | |

| TWI564720B (zh) | 用於串列i/o接收器之未等化時脈資料恢復 | |

| US20090121761A1 (en) | Intra-pair differential skew compensation method and apparatus for high-speed cable data transmission systems | |

| WO2009113462A1 (ja) | 波形等化回路および波形等化方法 | |

| KR102938433B1 (ko) | 비트-레벨 모드 리타이머 | |

| US8929429B2 (en) | Adaptive pade filter and transceiver | |

| JP2010226406A (ja) | 伝送装置 | |

| US7924912B1 (en) | Method and apparatus for a unified signaling decision feedback equalizer | |

| US11936505B2 (en) | Decision feedback equalization with efficient burst error correction | |

| US20120014460A1 (en) | Compensation for Transmission Line Length Variation in a Serdes System | |

| US7965765B2 (en) | Adjustment method, circuit, receiver circuit and transmission equipment of waveform equalization coefficient | |

| JP5259333B2 (ja) | 波形等化量調整方法、波形等化量調整回路、半導体装置および情報ネットワーク装置 | |

| US7426235B1 (en) | Method of adaptive equalization for high-speed NRZ and multi-level signal data communications | |

| US7590176B2 (en) | Partial response transmission system and equalizing circuit thereof | |

| US12519680B2 (en) | Receiver and method for controlling equalization | |

| CN104579618A (zh) | 应用于互连系统的方法与相关处理模块 | |

| JP2014033347A (ja) | アダプティブイコライザ、イコライザ調整方法、それを用いた半導体装置および情報ネットワーク装置 | |

| CN119449544A (zh) | 具有快速采样相位和频率采集的接收器和方法 | |

| US7529296B2 (en) | Adaptive equalization method and circuit for continuous run-time adaptation | |

| US20140043097A1 (en) | Electronic device and noise reducing method | |

| TWI416920B (zh) | 一種資料恢復系統中電位門檻及取樣時機決定之隨機最佳化電路 | |

| Healey | Challenges and solutions for standards-based serial 10 Gb/s backplane Ethernet | |

| US7154972B2 (en) | Receiver-side adaptive equalization in source-synchronous chip-to-chip communication systems | |

| JP2012039229A (ja) | 受信装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20101220 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120525 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120605 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120730 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121113 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130109 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130409 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130424 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160502 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |