JP5259107B2 - 積層セラミック電子部品およびその製造方法 - Google Patents

積層セラミック電子部品およびその製造方法 Download PDFInfo

- Publication number

- JP5259107B2 JP5259107B2 JP2007075221A JP2007075221A JP5259107B2 JP 5259107 B2 JP5259107 B2 JP 5259107B2 JP 2007075221 A JP2007075221 A JP 2007075221A JP 2007075221 A JP2007075221 A JP 2007075221A JP 5259107 B2 JP5259107 B2 JP 5259107B2

- Authority

- JP

- Japan

- Prior art keywords

- ceramic

- layer

- ceramic laminate

- electrode

- pair

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000000919 ceramic Substances 0.000 title claims description 199

- 238000004519 manufacturing process Methods 0.000 title claims description 43

- 239000010410 layer Substances 0.000 claims description 128

- 239000004020 conductor Substances 0.000 claims description 83

- 238000007747 plating Methods 0.000 claims description 62

- 238000000605 extraction Methods 0.000 claims description 57

- 238000000034 method Methods 0.000 claims description 49

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 claims description 45

- 239000011247 coating layer Substances 0.000 claims description 43

- 239000005871 repellent Substances 0.000 claims description 28

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 claims description 15

- 239000010931 gold Substances 0.000 claims description 15

- 229910052737 gold Inorganic materials 0.000 claims description 15

- 239000000463 material Substances 0.000 claims description 13

- 125000003396 thiol group Chemical class [H]S* 0.000 claims description 7

- 238000005520 cutting process Methods 0.000 claims description 3

- 239000003985 ceramic capacitor Substances 0.000 description 42

- 239000010408 film Substances 0.000 description 42

- 239000011248 coating agent Substances 0.000 description 8

- 238000000576 coating method Methods 0.000 description 8

- 230000002940 repellent Effects 0.000 description 6

- 239000002002 slurry Substances 0.000 description 6

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 4

- 229910052731 fluorine Inorganic materials 0.000 description 4

- 239000011737 fluorine Substances 0.000 description 4

- 238000003475 lamination Methods 0.000 description 4

- 238000012986 modification Methods 0.000 description 4

- 230000004048 modification Effects 0.000 description 4

- 239000011347 resin Substances 0.000 description 4

- 229920005989 resin Polymers 0.000 description 4

- 238000010030 laminating Methods 0.000 description 3

- 238000000059 patterning Methods 0.000 description 3

- 229920000642 polymer Polymers 0.000 description 3

- JRPBQTZRNDNNOP-UHFFFAOYSA-N barium titanate Chemical compound [Ba+2].[Ba+2].[O-][Ti]([O-])([O-])[O-] JRPBQTZRNDNNOP-UHFFFAOYSA-N 0.000 description 2

- 229910002113 barium titanate Inorganic materials 0.000 description 2

- 239000002131 composite material Substances 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 238000009413 insulation Methods 0.000 description 2

- 229920001343 polytetrafluoroethylene Polymers 0.000 description 2

- 239000004810 polytetrafluoroethylene Substances 0.000 description 2

- 239000002904 solvent Substances 0.000 description 2

- 239000000654 additive Substances 0.000 description 1

- 230000000996 additive effect Effects 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 239000002003 electrode paste Substances 0.000 description 1

- 239000000839 emulsion Substances 0.000 description 1

- 230000007613 environmental effect Effects 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- -1 polytetrafluoroethylene Polymers 0.000 description 1

- 239000002994 raw material Substances 0.000 description 1

- 230000001846 repelling effect Effects 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

Images

Landscapes

- Ceramic Capacitors (AREA)

- Fixed Capacitors And Capacitor Manufacturing Machines (AREA)

Description

セラミック積層体中に、複数の導体層がセラミック層を介して積層され、かつ、前記複数の導体層が交互に、セラミック積層体の側面の一対の領域に配設された一対の外部電極のいずれか一方に、電気的に接続された構造を有する積層セラミック電子部品の製造方法であって、

前記複数の導体層がセラミック層を介して積層され、かつ、前記一対の領域に引き出された構造を有するセラミック積層体を形成する工程と、

前記一対の領域のうちの一方の領域に露出した前記導体層に、1層おきに撥水性を付与しためっき膜である引出電極を形成する工程と、

前記一対の領域の他方の領域に露出した前記導体層のうち、前記一方の領域で一層おきに撥水性を付与しためっき膜である引出電極が形成された導体層とは異なる導体層のそれぞれに撥水性を付与しためっき膜である引出電極を形成する工程と、

前記引出電極にはじかれる材料からなる被覆層により前記セラミック積層体を被覆して、前記引出電極が前記被覆層から露出するとともに、他の所定の領域が前記被覆層により被覆された被覆セラミック積層体を形成する工程と、

前記被覆セラミック積層体の前記一対の領域に、前記引出電極と電気的に接続する外部電極を形成する工程と

を具備することを特徴としている。

セラミック積層体中に、複数の導体層がセラミック層を介して積層され、かつ、前記複数の導体層が交互に、セラミック積層体の側面の一対の領域に配設された一対の外部電極のいずれか一方に、電気的に接続された構造を有する積層セラミック電子部品の製造方法であって、

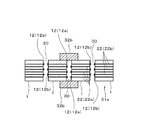

複数の導体層がセラミック層を介して積層されたマザーセラミック積層体を形成する工程と、

前記マザーセラミック積層体の所定の領域に、互いに平行な複数の溝を形成して、(a)隣り合う一対の溝に挟まれた領域の互いに対向する一対の側面が、個々の積層セラミック電子部品を構成するセラミック積層体の一対の側面となり、(b)前記側面に前記複数の導体層が露出し、(c)前記複数の導体層のそれぞれは、同一平面において、溝が形成されていない領域で導通した構造を有する溝付きマザーセラミック積層体を形成する工程と、

前記溝付きマザーセラミック積層体の前記一対の側面のうちの一方の側面に露出した前記導体層に、1層おきに撥水性を付与しためっき膜である引出電極を形成する工程と、

前記一対の側面の他方の側面に露出した前記導体層のうち、前記一方の側面で一層おきに撥水性を付与しためっき膜である引出電極が形成された導体層とは異なる導体層のそれぞれに撥水性を付与しためっき膜である引出電極を形成する工程と、

前記溝付きマザーセラミック積層体を所定の位置で切断して、個々のセラミック積層体に分割する工程と、

前記引出電極にはじかれる材料からなる被覆層により前記セラミック積層体を被覆して、前記引出電極が前記被覆層から露出するとともに、他の所定の領域が前記被覆層により被覆された被覆セラミック積層体を形成する工程と、

前記被覆セラミック積層体の、前記一対の側面に、前記引出電極と電気的に接続する外部電極を形成する工程と

を具備することを特徴としている。

セラミック積層体中に、複数の導体層がセラミック層を介して積層され、かつ、前記複数の導体層が交互に、セラミック積層体の側面の一対の領域に配設された一対の外部電極のいずれか一方に、電気的に接続された構造を有する積層セラミック電子部品であって、

セラミック積層体の、前記外部電極が配設されていない領域のうち、少なくとも前記導体層が露出した部分が被覆層により被覆されており、かつ、

前記内部電極と前記外部電極の接続部分には、撥水性を付与しためっき膜が存在していること

を特徴としている。

なお、本願発明によれば、引出電極に撥水性を持たせることにより、例えば、セラミック積層体を被覆層を構成する材料に浸漬して、引出電極を露出させた状態で、セラミック積層体の全面あるいは所定の領域に、例えば30μm以下というような薄い被覆層を形成することができる。さらに、被覆層の構成材料を調整することにより10μm程度の均一な被覆層を形成することもできる。

また、本願発明は、引出電極に被覆材をはじく作用を果たさせること意図するものであり、本願発明において、撥水性を有しているとは、被覆材をはじく作用を果たす性質を有していることを意味するものであり、本願発明でいう撥水性とは、文字どおりの、水をはじくという意味での撥水性に限らず、例えば油性の被覆材をはじくことができるような撥油性などの意味をも含む概念である。

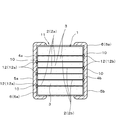

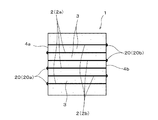

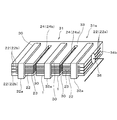

(1)一方主面に導体層が配設されたセラミックグリーンシートと、導体層(内部電極)が形成されていないセラミックグリーンシートを所定の順序で積層し、図2に示すように、複数の導体層2がセラミック層3を介して積層され、かつ、複数の導体層2が一対の側面4a,4bに引き出された構造を有する焼結済みのセラミック積層体1を用意する。

なお、このようなセラミック積層体は、通常の積層セラミック電子部品の製造工程で用いられる種々の方法、例えば、上述のようにセラミックグリーンシートを積層する工程を備えたいわゆるシート積層工法や、セラミックスラリーおよび電極ペーストを、図2に示すようなセラミック積層体1が形成されるように印刷してゆく、いわゆる逐次印刷工法などの方法により製造することが可能である。さらにその他の方法を適用することも可能である。

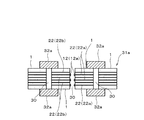

この実施例では、所定の導体層(内部電極)に引出電極を形成するにあたっては、一層おきに導体層(引出電極を形成しない方の導体層)の端部をシールしておき、シールされていない方の導体層に撥水めっきを行うことにより、引出電極を形成した。

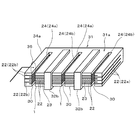

なお、セラミック積層体1を、撥水めっき膜にはじかれる材料からなる被覆層6により被覆する方法としては、例えば、絶縁樹脂原料の溶剤溶液などに浸漬した後、絶縁樹脂を硬化させる方法などを適用することができる。

また、後述のように、絶縁性のセラミック層を被覆層とする被覆セラミック積層体11を形成することも可能である。

上記の方法により、例えば、内部電極2の厚みが2μm、引出電極12(12a,12b)を構成する撥水めっき膜10の膜厚が3μm、セラミック層3の厚みが5μmというような条件の積層セラミックコンデンサを効率よく製造することができる。

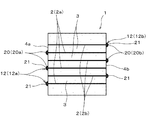

その場合、例えば、未焼成の状態のセラミック積層体1に、撥水性を有する引出電極12(12a,12b)を形成した後、セラミックスラリーに浸漬して、図5に示すように、引出電極12(12a,12b)が露出し、他の領域がセラミック層からなる被覆層6(6a)により被覆された被覆セラミック積層体11を形成し、これを一体的に焼成した後、図6に示すように、外部電極5a,5bを形成することにより、セラミック積層体1がセラミック層からなる被覆層6(6a)により被覆された構造を有する積層セラミックコンデンサを得ることができる。

例えば、セラミック積層体を構成するセラミックがチタン酸バリウム系セラミックである場合、同じくチタン酸バリウム系のセラミック原料を用い、これに有機ビヒクル、添加剤、および、溶剤を添加して混合し、粘度1〜10Pa・s(せん断速度100s−1での測定値)、セラミック固形分濃度10vol%のセラミックスラリーを準備する。

また、例えば、内部電極の厚み2μm、撥水メッキ厚3μm、セラミック層の厚み5μmの、積層数10層のセラミック積層体を用意し、所定の内部電極(導体層)に撥水めっきを施して引出電極(撥水めっき膜)を形成する。

それから、このセラミック積層体を、上述のセラミックスラリーに浸漬した後、引き上げて、被覆層が固着しないようにフッ素樹脂コーティングしたポットに取り出し、30分間、回転させながら十分に乾燥させて、20μm厚の被覆層により被覆された、未焼成の被覆セラミック積層体11(図5参照)を得る。

上記実施例1では、導体層の露出端部に撥水めっき膜を形成することにより引出電極を形成するようにしているが、導体層の露出端部に金めっきを施し、形成された金めっき膜の表面にフッ素変性チオールを塗布することによっても撥水性を有する引出電極を形成することができる。

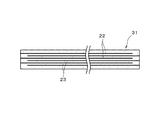

(a)隣り合う一対の溝30に挟まれた領域の互いに対向する一対の側面24(24a,24b),が、図1に示す個々の積層セラミック電子部品を構成するセラミック積層体1の一対の側面4(4a,4b)となる、

(b)この一対の側面24(24a,24b)に複数の導体層22が露出している。

(c)複数の導体層22のそれぞれは、同一平面において、溝が形成されていない領域(基部)33(図10)で導通している。

したがって、本願発明は、積層セラミックコンデンサや積層LC複合部品などの積層セラミック電子部品、その製造に関する技術分野に広く利用することが可能である。

2(2a,2b) 内部電極(導体層)

3 セラミック層

4a,4b セラミック積層体の側面

5a,5b 外部電極

6,6a 被覆層

10 撥水めっき膜

11 被覆セラミック積層体

12(12a,12b) 引出電極

20(20a,20b) 金めっき膜

21 フッ素変性チオール

22 導体層

23 セラミック層(セラミックグリーンシート)

24(24a,24b) 溝の側面

30 溝

31 未焼成のマザーセラミック積層体

31a 溝付きマザーセラミック積層体

32a,32b マスク

33 マザーセラミック積層体の溝が形成されていない領域(基部)

34a,34b 溝付きマザーセラミック積層体の端面

36 電極

Claims (5)

- セラミック積層体中に、複数の導体層がセラミック層を介して積層され、かつ、前記複数の導体層が交互に、セラミック積層体の側面の一対の領域に配設された一対の外部電極のいずれか一方に、電気的に接続された構造を有する積層セラミック電子部品の製造方法であって、

前記複数の導体層がセラミック層を介して積層され、かつ、前記一対の領域に引き出された構造を有するセラミック積層体を形成する工程と、

前記一対の領域のうちの一方の領域に露出した前記導体層に、1層おきに撥水性を付与しためっき膜である引出電極を形成する工程と、

前記一対の領域の他方の領域に露出した前記導体層のうち、前記一方の領域で一層おきに撥水性を付与しためっき膜である引出電極が形成された導体層とは異なる導体層のそれぞれに撥水性を付与しためっき膜である引出電極を形成する工程と、

前記引出電極に弾かれる材料からなる被覆層により前記セラミック積層体を被覆して、前記引出電極が前記被覆層から露出するとともに、他の所定の領域が前記被覆層により被覆された被覆セラミック積層体を形成する工程と、

前記被覆セラミック積層体の前記一対の領域に、前記引出電極と電気的に接続する外部電極を形成する工程と

を具備することを特徴とする積層セラミック電子部品の製造方法。 - セラミック積層体中に、複数の導体層がセラミック層を介して積層され、かつ、前記複数の導体層が交互に、セラミック積層体の側面の一対の領域に配設された一対の外部電極のいずれか一方に、電気的に接続された構造を有する積層セラミック電子部品の製造方法であって、

複数の導体層がセラミック層を介して積層されたマザーセラミック積層体を形成する工程と、

前記マザーセラミック積層体の所定の領域に、互いに平行な複数の溝を形成して、(a)隣り合う一対の溝に挟まれた領域の互いに対向する一対の側面が、個々の積層セラミック電子部品を構成するセラミック積層体の一対の側面となり、(b)前記側面に前記複数の導体層が露出し、(c)前記複数の導体層のそれぞれは、同一平面において、溝が形成されていない領域で導通した構造を有する溝付きマザーセラミック積層体を形成する工程と、

前記溝付きマザーセラミック積層体の前記一対の側面のうちの一方の側面に露出した前記導体層に、1層おきに撥水性を付与しためっき膜である引出電極を形成する工程と、

前記一対の側面の他方の側面に露出した前記導体層のうち、前記一方の側面で一層おきに撥水性を付与しためっき膜である引出電極が形成された導体層とは異なる導体層のそれぞれに撥水性を付与しためっき膜である引出電極を形成する工程と、

前記溝付きマザーセラミック積層体を所定の位置で切断して、個々のセラミック積層体に分割する工程と、

前記引出電極にはじかれる材料からなる被覆層により前記セラミック積層体を被覆して、前記引出電極が前記被覆層から露出するとともに、他の所定の領域が前記被覆層により被覆された被覆セラミック積層体を形成する工程と、

前記被覆セラミック積層体の、前記一対の側面に、前記引出電極と電気的に接続する外部電極を形成する工程と

を具備することを特徴とする積層セラミック電子部品の製造方法。 - 撥水性を付与した前記めっき膜が、撥水めっき膜、または金めっき膜の表面にフッ素変性チオールを塗布して形成したものであることを特徴とする請求項1または2記載の積層セラミック電子部品の製造方法。

- 導電性ペーストを塗布し、焼き付けることにより、前記外部電極を形成することを特徴とする請求項1〜3のいずれかに記載の積層セラミック電子部品の製造方法。

- セラミック積層体中に、複数の導体層がセラミック層を介して積層され、かつ、前記複数の導体層が交互に、セラミック積層体の側面の一対の領域に配設された一対の外部電極のいずれか一方に、電気的に接続された構造を有する積層セラミック電子部品であって、

セラミック積層体の、前記外部電極が配設されていない領域のうち、少なくとも前記導体層が露出した部分が被覆層により被覆されており、かつ、

前記内部電極と前記外部電極の接続部分には、撥水性を付与しためっき膜が存在していること

を特徴とする積層セラミック電子部品。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007075221A JP5259107B2 (ja) | 2007-03-22 | 2007-03-22 | 積層セラミック電子部品およびその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007075221A JP5259107B2 (ja) | 2007-03-22 | 2007-03-22 | 積層セラミック電子部品およびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008235698A JP2008235698A (ja) | 2008-10-02 |

| JP5259107B2 true JP5259107B2 (ja) | 2013-08-07 |

Family

ID=39908118

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007075221A Expired - Fee Related JP5259107B2 (ja) | 2007-03-22 | 2007-03-22 | 積層セラミック電子部品およびその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5259107B2 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5768471B2 (ja) * | 2010-05-19 | 2015-08-26 | 株式会社村田製作所 | セラミック電子部品の製造方法 |

| DE102012101351A1 (de) | 2012-02-20 | 2013-08-22 | Epcos Ag | Vielschichtbauelement und Verfahren zum Herstellen eines Vielschichtbauelements |

| JP6015781B2 (ja) * | 2015-01-06 | 2016-10-26 | Tdk株式会社 | 圧電素子 |

| KR102827670B1 (ko) | 2019-07-17 | 2025-07-02 | 삼성전기주식회사 | 적층 세라믹 전자 부품 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60196981A (ja) * | 1984-03-21 | 1985-10-05 | Nec Corp | 電歪効果素子の製造方法 |

| JPS61234580A (ja) * | 1985-04-11 | 1986-10-18 | Jgc Corp | 積層型電歪あるいは圧電素子 |

| JP3292009B2 (ja) * | 1995-10-20 | 2002-06-17 | 株式会社村田製作所 | 電極一体型グリーンシート及び積層セラミック電子部品の製造方法 |

| JP3067698B2 (ja) * | 1997-06-27 | 2000-07-17 | 松下電器産業株式会社 | 積層セラミック電子部品の製造方法 |

| JP2002005174A (ja) * | 2000-06-19 | 2002-01-09 | Nippon Densan Corp | 流体動圧軸受部品及びその製造方法、並びにそれを用いたモータ及びディスク装置 |

| JP4573956B2 (ja) * | 2000-06-30 | 2010-11-04 | 京セラ株式会社 | 積層型電子部品およびその製法 |

| JP2003109841A (ja) * | 2001-10-01 | 2003-04-11 | Murata Mfg Co Ltd | 積層型電子部品の製造方法 |

| JP2006093532A (ja) * | 2004-09-27 | 2006-04-06 | Matsushita Electric Ind Co Ltd | 電子部品 |

-

2007

- 2007-03-22 JP JP2007075221A patent/JP5259107B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2008235698A (ja) | 2008-10-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4992523B2 (ja) | 積層セラミック電子部品およびその製造方法 | |

| KR102112107B1 (ko) | 전자부품 및 전자부품의 제조 방법 | |

| US11145460B2 (en) | Multilayer ceramic electronic component | |

| JP5332475B2 (ja) | 積層セラミック電子部品およびその製造方法 | |

| KR101681358B1 (ko) | 적층 세라믹 커패시터 및 그 제조방법 | |

| US11049657B2 (en) | Multilayer ceramic electronic component | |

| KR20190044535A (ko) | 고체 전해 콘덴서의 제조 방법 및 고체 전해 콘덴서 | |

| CN1134800C (zh) | 电子元件 | |

| US12131871B2 (en) | Electronic component and method for manufacturing electronic component | |

| KR101397835B1 (ko) | 적층 세라믹 전자부품 및 이의 제조방법 | |

| US11232912B2 (en) | Solid electrolytic capacitor | |

| KR20120104955A (ko) | 적층 세라믹 전자부품의 제조방법 | |

| JP5259107B2 (ja) | 積層セラミック電子部品およびその製造方法 | |

| JP4574267B2 (ja) | 積層型電子部品の製法および積層型電子部品 | |

| KR101659208B1 (ko) | 적층 세라믹 전자 제품 및 그 제조 방법 | |

| KR102727245B1 (ko) | 전자부품의 제조 방법 및 전자부품의 제조 장치 | |

| CN114503229A (zh) | 电解电容器以及电解电容器的制造方法 | |

| JP2009239204A (ja) | 電子部品の製造方法 | |

| JP2000306763A (ja) | 積層セラミックコンデンサとその製造方法 | |

| JP5879913B2 (ja) | セラミック電子部品の製造方法 | |

| CN222168164U (zh) | 层叠陶瓷电容器 | |

| CN114746968B (zh) | 固体电解电容器 | |

| KR20230122970A (ko) | 적층 세라믹 콘덴서 및 적층 세라믹 콘덴서의 제조 방법 | |

| KR100739491B1 (ko) | 고유전율 캐패시터 및 그 제조방법 | |

| JP2009130151A (ja) | 積層型圧電アクチュエータ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100217 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20111128 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111213 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120209 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120327 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130424 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160502 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5259107 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |