JP5224924B2 - 通信制御装置 - Google Patents

通信制御装置 Download PDFInfo

- Publication number

- JP5224924B2 JP5224924B2 JP2008159156A JP2008159156A JP5224924B2 JP 5224924 B2 JP5224924 B2 JP 5224924B2 JP 2008159156 A JP2008159156 A JP 2008159156A JP 2008159156 A JP2008159156 A JP 2008159156A JP 5224924 B2 JP5224924 B2 JP 5224924B2

- Authority

- JP

- Japan

- Prior art keywords

- communication

- slave

- communication control

- control means

- clock signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Communication Control (AREA)

- Synchronisation In Digital Transmission Systems (AREA)

Description

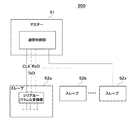

3a,3b,3x スレーブ用通信制御部

4 CPU

7 発振器

8 マスター用通信制御部

10 クロック信号変調部

100 通信制御システム

Claims (7)

- 主制御手段と、

前記主制御手段からの信号に基づき負荷を制御する第1及び第2従制御手段と、

前記第1及び第2従制御手段のそれぞれと前記主制御手段とがシリアル通信を行うための第1及び第2通信手段とを有し、

前記主制御手段は、

前記第1及び第2通信手段を用いて前記第1及び第2従制御手段のそれぞれと通信し、前記第1及び第2従制御手段のそれぞれとの通信結果に基づき、前記第1及び第2従制御手段のそれぞれとの通信で使用する第1周波数及び該第1周波数と異なる第2周波数を設定する設定手段と、

前記設定手段によって設定された前記第1及び第2周波数のそれぞれに応じた第1及び第2クロック信号を生成する生成手段と、

前記第1通信手段を用いて前記第1クロック信号に基づく通信を前記第1従制御手段と行い、前記第2通信手段を用いて前記第2クロック信号に基づく通信を前記第2従制御手段と行う通信制御手段とを有することを特徴とする通信制御装置。 - 前記設定手段は、前記第1及び第2周波数を設定するために、所定周波数の初期クロック信号に基づき前記第1及び第2従制御手段のそれぞれと通信することを特徴とする請求項1記載の通信制御装置。

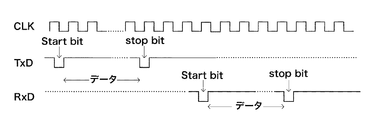

- 前記シリアル通信は、全二重方式のシリアル通信であることを特徴とする請求項1又は2に記載の通信制御装置。

- 前記生成手段は、基準クロック信号を逓倍し、前記第1及び第2クロック信号を生成することを特徴とする請求項1乃至3のいずれか1項に記載の通信制御装置。

- 前記設定手段は、

前記第1及び第2通信手段を用いて前記第1及び第2従制御手段のそれぞれと通信し、前記第1及び第2従制御手段のそれぞれの識別情報を取得し、

前記第1及び第2従制御手段のそれぞれの識別情報に基づき、前記第1及び第2周波数を設定することを特徴とする請求項1乃至4のいずれか1項に記載の通信制御装置。 - 前記設定手段は、

前記第1及び第2通信手段を用いて前記第1及び第2従制御手段のそれぞれと通信し、前記第1及び第2従制御手段のそれぞれの通信データ量を示すデータを取得し、

前記第1及び第2従制御手段のそれぞれの通信データ量を示すデータに基づき、前記第1及び第2周波数を設定することを特徴とする請求項1乃至3のいずれか1項に記載の通信制御装置。 - 前記設定手段は、通信データ量が多い従制御手段に対して高い周波数を設定することを請求項6記載の通信制御装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008159156A JP5224924B2 (ja) | 2008-06-18 | 2008-06-18 | 通信制御装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008159156A JP5224924B2 (ja) | 2008-06-18 | 2008-06-18 | 通信制御装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010004123A JP2010004123A (ja) | 2010-01-07 |

| JP2010004123A5 JP2010004123A5 (ja) | 2011-08-04 |

| JP5224924B2 true JP5224924B2 (ja) | 2013-07-03 |

Family

ID=41585504

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008159156A Expired - Fee Related JP5224924B2 (ja) | 2008-06-18 | 2008-06-18 | 通信制御装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5224924B2 (ja) |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS57183154A (en) * | 1981-05-06 | 1982-11-11 | Toshiba Corp | Multispeed transmission system |

| JPH02308356A (ja) * | 1989-05-24 | 1990-12-21 | Nec Corp | 並列処理装置 |

| JP3323719B2 (ja) * | 1995-12-14 | 2002-09-09 | 富士通株式会社 | スター型通信装置 |

| JP4266477B2 (ja) * | 2000-02-25 | 2009-05-20 | キヤノン株式会社 | 情報処理装置及びその制御方法 |

| JP2001320390A (ja) * | 2000-05-11 | 2001-11-16 | Matsushita Electric Ind Co Ltd | シリアルバス制御装置及び制御方法 |

| JP2006106331A (ja) * | 2004-10-05 | 2006-04-20 | Sharp Corp | 負荷駆動装置およびそれを備えてなるled表示装置 |

| JP2006293138A (ja) * | 2005-04-13 | 2006-10-26 | Canon Inc | 画像形成装置 |

| JP5408844B2 (ja) * | 2006-07-04 | 2014-02-05 | キヤノン株式会社 | バスシステム |

-

2008

- 2008-06-18 JP JP2008159156A patent/JP5224924B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2010004123A (ja) | 2010-01-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9141890B2 (en) | Data processing apparatus, data processing method, data processing program for implementing the method, and image processing apparatus | |

| JP2013203003A (ja) | プリンタ | |

| JP2011087259A (ja) | 通信集中制御システムおよび通信集中制御方法 | |

| JP4550059B2 (ja) | 無線タグ読取システム、無線タグ読取装置および無線タグ | |

| JP5224924B2 (ja) | 通信制御装置 | |

| JP2006343815A (ja) | 通信装置、通信方法、通信システム | |

| JP5245561B2 (ja) | 画像処理装置および省エネ復帰方法 | |

| JP6013440B2 (ja) | マルチチップシステムにおける各チップ間のクロック信号の位相差補償方法及び装置 | |

| JP4933393B2 (ja) | 通信装置及びその通信方法 | |

| JP2008009910A (ja) | Icカードおよびicカード読み取りシステム | |

| EP2876970B1 (en) | Communication device | |

| US8803714B2 (en) | Transmitting device and receiving device | |

| JP2004064616A (ja) | ボーレート設定方法、ボーレート設定プログラム、可読記録媒体、通信システムおよび通信方法 | |

| JP5683142B2 (ja) | 情報処理装置又は情報処理方法 | |

| JP2009112006A (ja) | 重複信号を用いたコグニティブ無線通信装置およびその方法 | |

| US20070134961A1 (en) | Apparatus and method for interfacing XFP optical transceiver with 300-pin MSA optical transponder | |

| KR102261924B1 (ko) | 멀티 홉 릴레이 협력 통신 네트워크에서 데이터 수신 노드 장치와의 통신을 수행하기 위한 통신 스케줄링 방식을 결정할 수 있는 데이터 전송 노드 장치 및 그 동작 방법 | |

| US20250227635A1 (en) | Phase offset compensation device and method | |

| JP2011151609A (ja) | スペクトラム拡散方式のクロック伝達システム | |

| JP5458193B2 (ja) | 電子機器およびリモートアクセス処理方法 | |

| JP7367346B2 (ja) | 機器、データ生成プログラム、およびデータ生成方法 | |

| JP2003110565A (ja) | 通信システム、送信装置、通信方法、通信プログラム、および通信プログラムを記録したコンピュータ読取可能な記録媒体 | |

| JP2005217653A (ja) | 電子機器 | |

| KR20240044310A (ko) | 위상 옵셋 보상 장치 및 방법 | |

| JP2008234631A (ja) | ネットワーク上にあるサービスを実行する方法及びフロー処理装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110617 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110617 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120524 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120605 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120806 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121002 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130212 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130312 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160322 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |