JP5222029B2 - 撮像装置、撮像システム、および、撮像装置の制御方法 - Google Patents

撮像装置、撮像システム、および、撮像装置の制御方法 Download PDFInfo

- Publication number

- JP5222029B2 JP5222029B2 JP2008148315A JP2008148315A JP5222029B2 JP 5222029 B2 JP5222029 B2 JP 5222029B2 JP 2008148315 A JP2008148315 A JP 2008148315A JP 2008148315 A JP2008148315 A JP 2008148315A JP 5222029 B2 JP5222029 B2 JP 5222029B2

- Authority

- JP

- Japan

- Prior art keywords

- signal

- column

- reference signal

- amplification

- units

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/60—Noise processing, e.g. detecting, correcting, reducing or removing noise

- H04N25/62—Detection or reduction of noise due to excess charges produced by the exposure, e.g. smear, blooming, ghost image, crosstalk or leakage between pixels

- H04N25/627—Detection or reduction of inverted contrast or eclipsing effects

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/60—Noise processing, e.g. detecting, correcting, reducing or removing noise

- H04N25/63—Noise processing, e.g. detecting, correcting, reducing or removing noise applied to dark current

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/60—Noise processing, e.g. detecting, correcting, reducing or removing noise

- H04N25/67—Noise processing, e.g. detecting, correcting, reducing or removing noise applied to fixed-pattern noise, e.g. non-uniformity of response

- H04N25/671—Noise processing, e.g. detecting, correcting, reducing or removing noise applied to fixed-pattern noise, e.g. non-uniformity of response for non-uniformity detection or correction

- H04N25/677—Noise processing, e.g. detecting, correcting, reducing or removing noise applied to fixed-pattern noise, e.g. non-uniformity of response for non-uniformity detection or correction for reducing the column or line fixed pattern noise

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/71—Charge-coupled device [CCD] sensors; Charge-transfer registers specially adapted for CCD sensors

- H04N25/75—Circuitry for providing, modifying or processing image signals from the pixel array

Description

本発明の第4側面に係る撮像装置の制御方法は、複数の画素が行方向及び列方向に配列された画素配列と、複数の列増幅部と、前記画素配列における複数の列に対して共通な第1の参照信号と第2の参照信号とを異なるタイミングで前記画素配列の列信号線へそれぞれ出力する複数の参照信号供給部と、を備える撮像装置の制御方法であって、前記複数の列増幅部のそれぞれが、前記第1の参照信号と前記第2の参照信号との差分を増幅して出力し、あるいは、前記第1の参照信号と前記第2の参照信号とをそれぞれ増幅して出力するステップと、前記複数の列増幅部のそれぞれから出力された信号に応じて前記複数の列増幅部のそれぞれにおける増幅率のばらつきを低減するようにそれぞれ決定された増幅率を前記複数の列増幅部のそれぞれに設定するステップと、前記複数の列増幅部のそれぞれへの増幅率の設定後に前記画素配列における各列の画素から前記列信号線へ異なるタイミングで出力されてくる第1の信号と第2の信号との差分を増幅する、あるいは、前記第1の信号と前記第2の信号とをそれぞれ増幅するステップと、

を含むことを特徴とする。

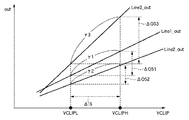

γ1=ΔOS1/(ΔIS)・・・数式1

と求まる。第2の列Line2の列増幅部における増幅率は、

γ2=ΔOS2/(ΔIS)・・・数式2

と求まる。第3の列Line3の列増幅部における増幅率は、

γ3=ΔOS3/(ΔIS)・・・数式3

と求まる。そして、複数の列増幅部における増幅率のばらつきを低減するように、各列(Line1〜3)の列増幅部における増幅率を設定するための係数を、例えば、次のように決定する。すなわち、第1の列Line1の列増幅部に対する係数を、

K1=γ1/γ1=1・・・数式4

に決定し、第2の列Line2の列増幅部に対する係数を、

K2=γ1/γ2・・・数式5

に決定し、第1の列Line1の列増幅部に対する係数を、

K3=γ1/γ3・・・数式6

に決定する。出力処理回路119は、例えば、増幅率を設定するための係数を、上述の決定した増幅率に関する情報として全体制御・演算部120へ供給する。

S1、S2 撮像システム

Claims (8)

- 複数の画素が行方向及び列方向に配列された画素配列と、

増幅率を設定するための設定部をそれぞれ含む複数の列増幅部と、

第1の参照信号と第2の参照信号とを異なるタイミングで前記画素配列の列信号線へそれぞれ出力する複数の参照信号供給部と、

を備え、

前記第1の参照信号と前記第2の参照信号とは、前記画素配列における複数の列に対して共通であり、

前記複数の列増幅部のそれぞれは、前記複数の列増幅部のそれぞれの増幅率を設定するための期間において、前記第1の参照信号と前記第2の参照信号との差分を増幅して出力し、あるいは、前記第1の参照信号と前記第2の参照信号とをそれぞれ増幅して出力するように構成され、

前記設定部は、前記期間において前記複数の列増幅部のそれぞれから出力された信号に応じて前記複数の列増幅部のそれぞれにおける増幅率のばらつきを低減するようにそれぞれ決定された増幅率を前記複数の列増幅部のそれぞれに設定し、

前記複数の列増幅部は、前記設定部による増幅率の設定後に前記画素配列における各列の画素から前記列信号線へ異なるタイミングで出力されてくる第1の信号と第2の信号との差分を増幅する、あるいは、前記第1の信号と前記第2の信号とをそれぞれ増幅する

ことを特徴とする撮像装置。 - 前記複数の列増幅部のそれぞれは、前記第1の参照信号と前記第2の参照信号との差分を増幅することにより、第1の画像信号を生成して出力し、

前記複数の列増幅部のそれぞれの前記設定部は、前記第1の画像信号に応じて前記複数の列増幅部における増幅率のばらつきを低減するように決定された増幅率を設定し、

前記複数の列増幅部は、それぞれの前記設定部により設定された増幅率で、前記第1の信号と前記第2の信号との差分を増幅することにより、第2の画像信号を生成して出力する

ことを特徴とする請求項1に記載の撮像装置。 - 前記複数の列増幅部のそれぞれは、

入力端子と出力端子とを有する演算増幅器と、

前記画素配列における各列の画素又は前記参照信号供給部から前記列信号線を介して伝達された信号が入力される第1の電極と、前記演算増幅器の前記入力端子に接続された第2の電極とを含む入力容量と、

前記演算増幅器の前記入力端子と前記出力端子とに接続され、容量値が可変の帰還容量と、

前記演算増幅器の前記入力端子と前記出力端子とに接続され、前記演算増幅器をリセットするリセットスイッチと、

をさらに含み、

前記複数の列増幅部のそれぞれの前記設定部は、前記第1の画像信号に応じて前記複数の列増幅部のそれぞれにおける増幅率のばらつきを低減するように決定された増幅率に応じた容量値に前記帰還容量を制御する

ことを特徴とする請求項2に記載の撮像装置。 - 前記複数の列増幅部のそれぞれは、前記第1の参照信号と前記第2の参照信号とをそれぞれ増幅して出力し、

前記複数の列増幅部のそれぞれの前記設定部は、前記増幅された前記第1の参照信号と前記増幅された前記第2の参照信号とに応じて前記複数の列増幅部のそれぞれにおける増幅率のばらつきを低減するように決定された増幅率を前記列増幅部に設定し、

前記複数の列増幅部は、それぞれの前記設定部により設定された増幅率で、前記第1の信号と前記第2の信号とをそれぞれ増幅して出力する

ことを特徴とする請求項1に記載の撮像装置。 - 前記複数の列増幅部のそれぞれは、前記画素配列における各列の画素又は前記参照信号供給部から前記列信号線を介して伝達された信号が入力される増幅器をさらに含み、

前記複数の列増幅部のそれぞれの前記設定部は、前記増幅された前記第1の参照信号と前記増幅された前記第2の参照信号とに応じて前記複数の列増幅部のそれぞれにおける増幅率のばらつきを低減するように決定された増幅率を前記増幅器に設定する

ことを特徴とする請求項4に記載の撮像装置。 - 請求項1から3のいずれか1項に記載の撮像装置と、

前記撮像装置の撮像面へ像を形成する光学系と、

前記撮像装置から出力された信号を処理して画像データを生成する信号処理部と、

を備え、

前記複数の列増幅部のそれぞれは、前記第1の参照信号と前記第2の参照信号との差分を増幅することにより第1の画像信号を生成して出力し、

前記信号処理部は、前記第1の画像信号を受けて、受けた前記第1の画像信号に応じて、前記複数の列増幅部における増幅率のばらつきを低減するように、前記複数の列増幅部のそれぞれの増幅率を決定し、決定した増幅率を設定するように前記複数の列増幅部のそれぞれの前記設定部を制御し、

前記複数の列増幅部のそれぞれは、前記信号処理部に制御されることにより、前記複数の列増幅部のそれぞれの前記設定部により設定された増幅率で、前記第1の参照信号と前記第2の参照信号との差分を増幅することにより第2の画像信号を生成して出力する

ことを特徴とする撮像システム。 - 請求項1、4及び5のいずれか1項に記載の撮像装置と、

前記撮像装置の撮像面へ像を形成する光学系と、

前記撮像装置から出力された信号を処理して画像データを生成する信号処理部と、

を備え、

前記複数の列増幅部のそれぞれは、前記第1の参照信号と前記第2の参照信号とをそれぞれ増幅して出力し、

前記信号処理部は、前記増幅された前記第1の参照信号と前記増幅された前記第2の参照信号とをそれぞれ受けて、それぞれ受けた前記増幅された前記第1の参照信号と前記増幅された前記第2の参照信号との差分をとることにより第1の画像信号を生成し、生成された前記第1の画像信号に応じて前記複数の列増幅部のそれぞれにおける増幅率のばらつきを低減するように、前記複数の列増幅部のそれぞれの増幅率を決定し、決定した増幅率を設定するように前記設定部を制御し、

前記複数の列増幅部のそれぞれは、前記信号処理部に制御されることにより、前記複数の列増幅部のそれぞれの前記設定部により設定された増幅率で、前記第1の信号と前記第2の信号とをそれぞれ増幅して出力し、

前記信号処理部は、前記増幅された前記第1の信号と前記増幅された前記第2の信号とを受けて、前記増幅された前記第1の信号と前記増幅された前記第2の信号との差分をとることにより第2の画像信号を生成する

ことを特徴とする撮像システム。 - 複数の画素が行方向及び列方向に配列された画素配列と、複数の列増幅部と、前記画素配列における複数の列に対して共通な第1の参照信号と第2の参照信号とを異なるタイミングで前記画素配列の列信号線へそれぞれ出力する複数の参照信号供給部と、を備える撮像装置の制御方法であって、

前記複数の列増幅部のそれぞれが、前記第1の参照信号と前記第2の参照信号との差分を増幅して出力し、あるいは、前記第1の参照信号と前記第2の参照信号とをそれぞれ増幅して出力するステップと、

前記複数の列増幅部のそれぞれから出力された信号に応じて前記複数の列増幅部のそれぞれにおける増幅率のばらつきを低減するようにそれぞれ決定された増幅率を前記複数の列増幅部のそれぞれに設定するステップと、

前記複数の列増幅部のそれぞれへの増幅率の設定後に前記画素配列における各列の画素から前記列信号線へ異なるタイミングで出力されてくる第1の信号と第2の信号との差分を増幅する、あるいは、前記第1の信号と前記第2の信号とをそれぞれ増幅するステップと、

を含むことを特徴とする撮像装置の制御方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008148315A JP5222029B2 (ja) | 2008-06-05 | 2008-06-05 | 撮像装置、撮像システム、および、撮像装置の制御方法 |

| US12/477,499 US8067720B2 (en) | 2008-06-05 | 2009-06-03 | Image sensing device and imaging system |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008148315A JP5222029B2 (ja) | 2008-06-05 | 2008-06-05 | 撮像装置、撮像システム、および、撮像装置の制御方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009296358A JP2009296358A (ja) | 2009-12-17 |

| JP2009296358A5 JP2009296358A5 (ja) | 2011-07-21 |

| JP5222029B2 true JP5222029B2 (ja) | 2013-06-26 |

Family

ID=41399439

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008148315A Expired - Fee Related JP5222029B2 (ja) | 2008-06-05 | 2008-06-05 | 撮像装置、撮像システム、および、撮像装置の制御方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8067720B2 (ja) |

| JP (1) | JP5222029B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4958666B2 (ja) * | 2007-07-12 | 2012-06-20 | キヤノン株式会社 | 撮像装置及びその制御方法 |

| WO2010023903A1 (ja) * | 2008-09-01 | 2010-03-04 | 株式会社ニコン | 撮像素子および撮像装置 |

| WO2018181723A1 (ja) * | 2017-03-29 | 2018-10-04 | 株式会社ニコン | 撮像素子および電子カメラ |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08289204A (ja) * | 1995-04-13 | 1996-11-01 | Sony Corp | 固体撮像装置 |

| JP3466886B2 (ja) | 1997-10-06 | 2003-11-17 | キヤノン株式会社 | 固体撮像装置 |

| JP2002044370A (ja) * | 2000-07-28 | 2002-02-08 | Mitsubishi Electric Corp | イメージセンサ |

| GB0020280D0 (en) * | 2000-08-18 | 2000-10-04 | Vlsi Vision Ltd | Modification of column fixed pattern column noise in solid image sensors |

| US7408577B2 (en) * | 2003-04-09 | 2008-08-05 | Micron Technology, Inc. | Biasing scheme for large format CMOS active pixel sensors |

| JP2005217771A (ja) * | 2004-01-29 | 2005-08-11 | Canon Inc | 撮像装置 |

| JP4517660B2 (ja) | 2004-02-09 | 2010-08-04 | ソニー株式会社 | 固体撮像装置、画像入力装置および固体撮像素子の駆動方法 |

| JP4804254B2 (ja) * | 2006-07-26 | 2011-11-02 | キヤノン株式会社 | 光電変換装置及び撮像装置 |

-

2008

- 2008-06-05 JP JP2008148315A patent/JP5222029B2/ja not_active Expired - Fee Related

-

2009

- 2009-06-03 US US12/477,499 patent/US8067720B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20090302200A1 (en) | 2009-12-10 |

| US8067720B2 (en) | 2011-11-29 |

| JP2009296358A (ja) | 2009-12-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10021321B2 (en) | Imaging device and imaging system | |

| JP5852324B2 (ja) | 撮像装置及びその制御方法、プログラム | |

| JP5959834B2 (ja) | 撮像装置 | |

| US9930273B2 (en) | Image pickup apparatus, image pickup system, and control method for the image pickup apparatus for controlling transfer switches | |

| US9979910B2 (en) | Image capturing apparatus and control method thereof, and storage medium | |

| JP5222068B2 (ja) | 撮像装置 | |

| JP4931546B2 (ja) | 固体撮像装置及び撮像装置 | |

| JP5222029B2 (ja) | 撮像装置、撮像システム、および、撮像装置の制御方法 | |

| JP4991494B2 (ja) | 撮像装置 | |

| JP2008109264A5 (ja) | ||

| JP2016167773A (ja) | 撮像装置及び撮像装置の処理方法 | |

| US20170078598A1 (en) | Imaging apparatus and imaging method thereof using correlated double sampling | |

| JP2008042673A (ja) | 光電変換装置及びその駆動方法 | |

| JP6245856B2 (ja) | 光電変換装置、光電変換システム | |

| JP2012235193A (ja) | 撮像素子、撮像装置、およびその制御方法、並びに制御プログラム | |

| JP5627728B2 (ja) | 撮像装置及び撮像システム | |

| JP2014107739A (ja) | 撮像装置及びその制御方法 | |

| JP2020092346A (ja) | 撮像装置およびその制御方法 | |

| JP2011009834A (ja) | 撮像装置及び撮像方法 | |

| JP2020057883A (ja) | 撮像装置 | |

| JP5129650B2 (ja) | 撮像装置 | |

| JP2012044307A (ja) | 撮像装置 | |

| JP2018019268A (ja) | 撮像装置、撮像システムおよび撮像装置の駆動方法 | |

| JP5376966B2 (ja) | 撮像素子及び撮像装置 | |

| JP2018093301A (ja) | 撮像素子及び撮像素子の制御方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110606 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110606 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120821 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120827 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121022 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130208 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130308 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160315 Year of fee payment: 3 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5222029 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160315 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |